## **MSPM0 C-Series 24-MHz Microcontrollers**

Technical Reference Manual

Literature Number: SLAU893 OCTOBER 2023

## **Table of Contents**

| Read This First                        | 9  |

|----------------------------------------|----|

| About This Manual                      |    |

| Notational Conventions                 |    |

| Glossary                               |    |

| Related Documentation                  | 9  |

| Support Resources                      | 9  |

| 1 Architecture                         | 11 |

| 1.1 Architecture Overview              | 12 |

| 1.2 Bus Organization                   | 12 |

| 1.3 Platform Memory Map                | 14 |

| 1.3.1 Code Region                      | 14 |

| 1.3.2 SRAM Region                      |    |

| 1.3.3 Peripheral Region                | 15 |

| 1.3.4 Subsystem Region                 | 15 |

| 1.3.5 System PPB Region                | 15 |

| 1.4 Boot Configuration                 |    |

| 1.4.1 Configuration Memory (NONMAIN)   | 15 |

| 1.4.2 Boot Configuration Routine (BCR) | 16 |

| 1.5 NONMAIN Registers                  | 21 |

| 1.6 Factory Constants                  | 26 |

| 1.6.1 FACTORYREGION Registers          | 27 |

| 2 PMCU                                 | 33 |

| 2.1 PMCU Overview                      | 34 |

| 2.1.1 Power Domains                    | 35 |

| 2.1.2 Operating Modes                  | 35 |

| 2.2 Power Management (PMU)             |    |

| 2.2.1 Power Supply                     | 39 |

| 2.2.2 Core Regulator                   | 40 |

| 2.2.3 Supply Supervisors               |    |

| 2.2.4 Bandgap Reference                | 41 |

| 2.2.5 Temperature Sensor               |    |

| 2.2.6 Peripheral Power Enable Control  |    |

| 2.3 Clock Module (CKM)                 |    |

| 2.3.1 Oscillators                      |    |

| 2.3.2 Clocks                           | 46 |

| 2.3.3 Clock Tree                       |    |

| 2.3.4 Clock Monitors                   |    |

| 2.3.5 Frequency Clock Counter (FCC)    | 52 |

| 2.4 System Controller (SYSCTL)         |    |

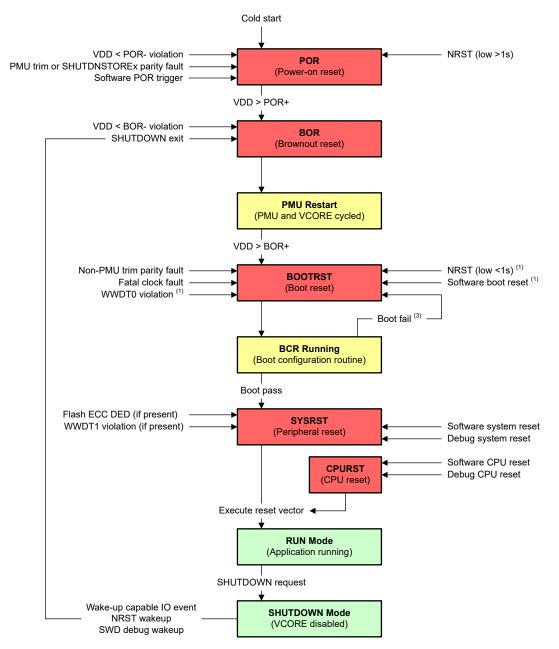

| 2.4.1 Resets and Device Initialization |    |

| 2.4.2 Operating Mode Selection         |    |

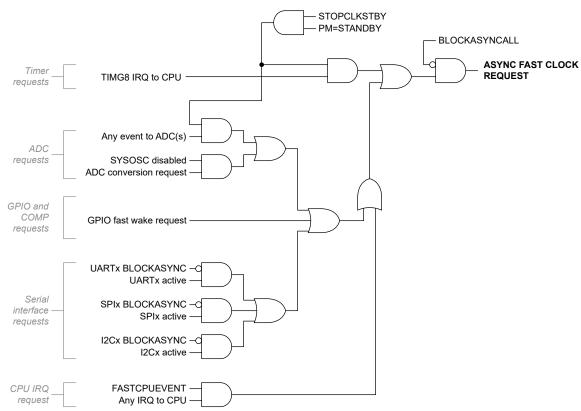

| 2.4.3 Asynchronous Fast Clock Requests |    |

| 2.4.4 SRAM Write Protection            |    |

| 2.4.5 Flash Wait States                |    |

| 2.4.6 Shutdown Mode Handling           |    |

| 2.4.7 Configuration Lockout            |    |

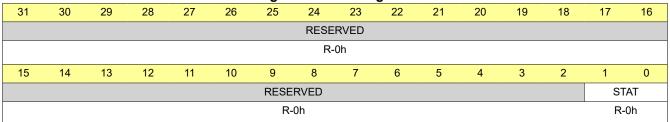

| 2.4.8 System Status                    |    |

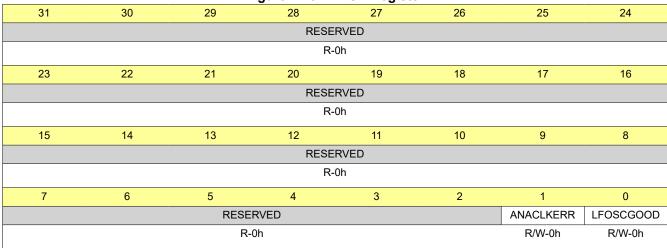

| 2.4.9 Error Handling                   |    |

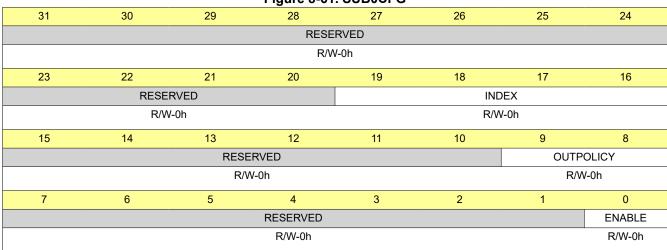

| 2.4.10 SYSCTL Events                   | 68 |

Table of Contents www.ti.com

| 2.5 Quick Start Reference                                                       | 69                |

|---------------------------------------------------------------------------------|-------------------|

| 2.5.1 Default Device Configuration                                              |                   |

| 2.5.2 Leveraging MFCLK                                                          |                   |

| 2.5.2 Developing MFCLK                                                          |                   |

| 2.5.4 Optimizing Power Consumption in STANDBY Mode.                             |                   |

| 2.5.5 Optimizing for Lowest Wakeup Latency                                      |                   |

| 2.5.6 Optimizing for Lowest Wakeup Laterity                                     |                   |

| 2.5.6 Optimizing for Lowest Feak Current in Roll/SLEEF Mode                     |                   |

| 3 CPU                                                                           |                   |

| 3.1 Overview                                                                    |                   |

| 3.2 Arm Cortex-M0+ CPU                                                          |                   |

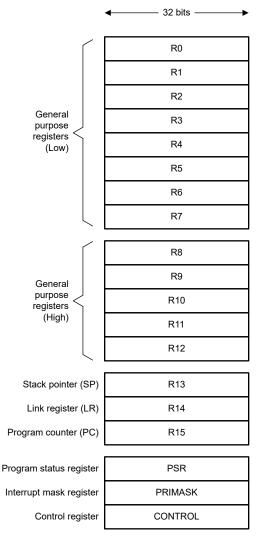

| 3.2.1 CPU Register File                                                         |                   |

| 3.2.2 Stack Behavior                                                            |                   |

| 3.2.3 Execution Modes and Privilege Levels.                                     |                   |

| 3.2.4 Address Space and Supported Data Sizes.                                   |                   |

| 3.2.4 Address Space and Supported Data Sizes                                    |                   |

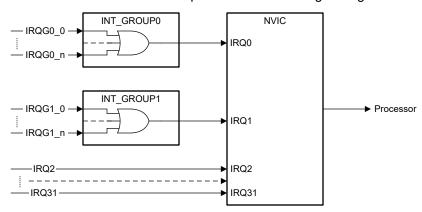

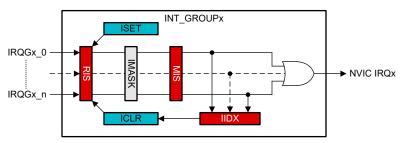

| 3.3.1 Peripheral Interrupts (IRQs).                                             |                   |

| 3.3.2 Interrupt and Exception Table                                             |                   |

| 3.3.3 Processor Lockup Scenario.                                                |                   |

| 3.3 Processor Lockup Scenario.                                                  |                   |

| 3.4.1 System Control Block (SCB)                                                |                   |

| 3.5 Read-Only Memory (ROM)                                                      |                   |

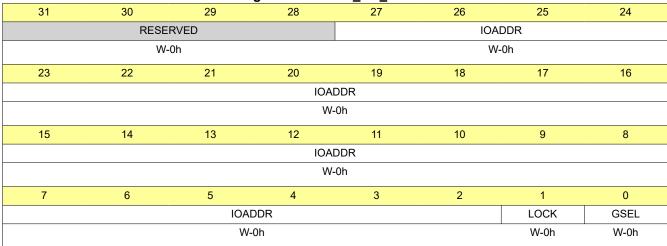

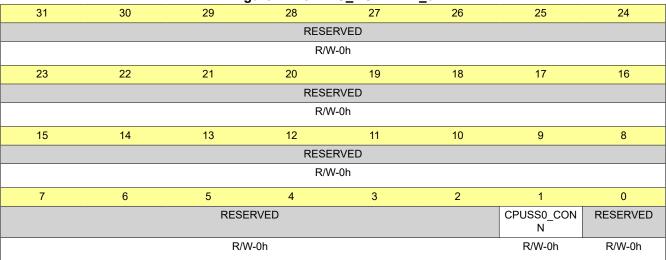

| 3.6 CPUSS Registers                                                             |                   |

| 3.7 WUC Registers                                                               |                   |

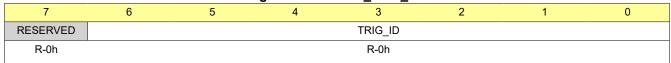

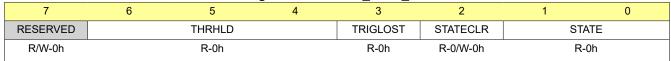

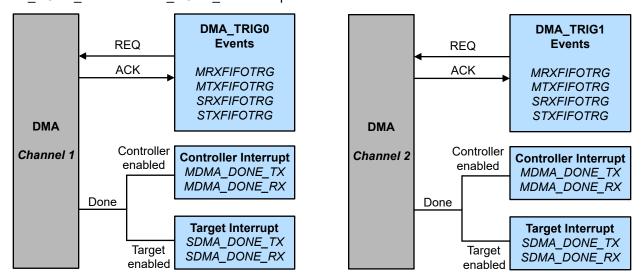

| 4 DMA                                                                           |                   |

| 4.1 DMA Overview.                                                               |                   |

| 4.2 DMA Operation                                                               |                   |

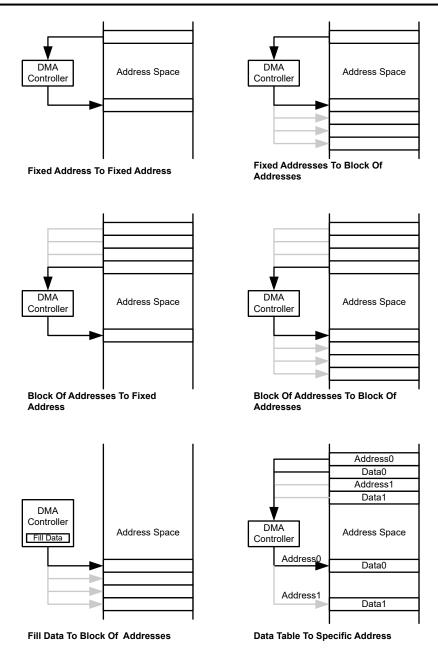

| 4.2.1 Addressing Modes.                                                         |                   |

| 4.2.2 Channel Types                                                             |                   |

| 4.2.3 Transfer Modes                                                            |                   |

| 4.2.4 Extended Modes                                                            |                   |

| 4.2.5 Initiating DMA Transfers                                                  |                   |

| 4.2.6 Stopping DMA Transfers                                                    |                   |

| 4.2.7 Channel Priorities.                                                       |                   |

| 4.2.8 Burst Block Mode                                                          |                   |

| 4.2.9 Using DMA with System Interrupts.                                         |                   |

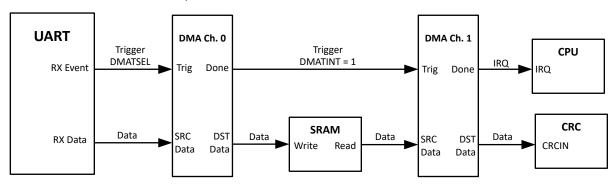

| 4.2.10 DMA Controller Interrupts.                                               |                   |

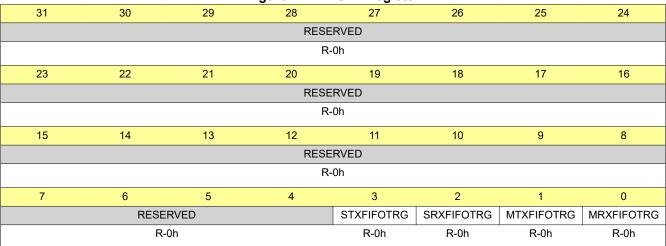

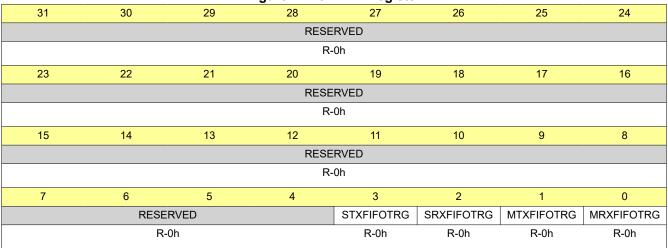

| 4.2.11 DMA Trigger Event Status                                                 |                   |

| 4.2.12 DMA Operating Mode Support                                               |                   |

| 4.2.13 DMA Address and Data Errors.                                             |                   |

| 4.2.14 Interrupt and Event Support.                                             |                   |

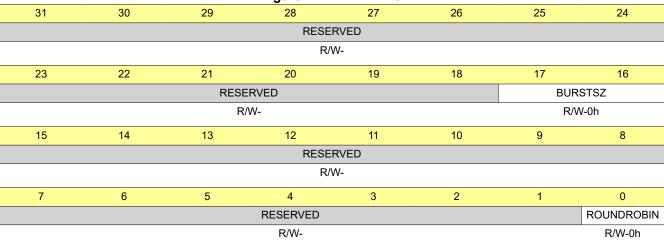

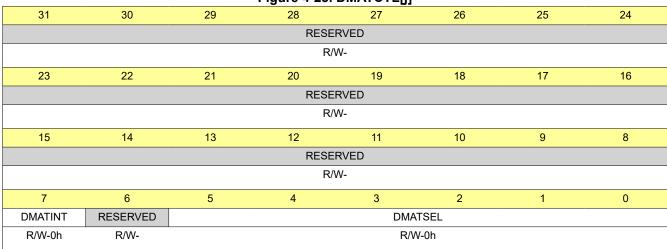

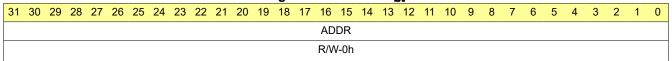

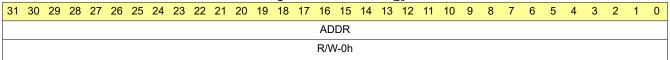

| 4.3 DMA Registers                                                               |                   |

| 5 NVM (Flash)                                                                   |                   |

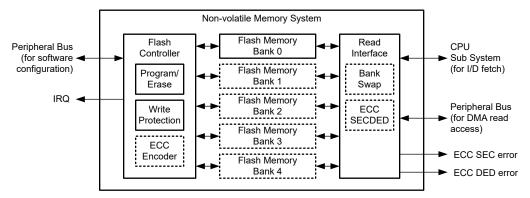

| 5.1 NVM Overview                                                                |                   |

| 5.1.1 Key Features                                                              |                   |

| 5.1.2 System Components                                                         |                   |

| 5.1.3 Terminology                                                               |                   |

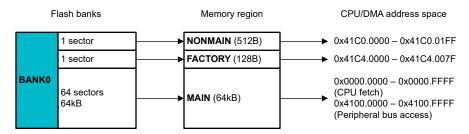

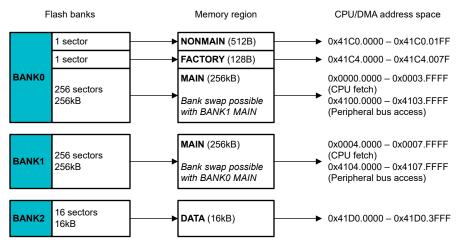

| 5.2 Flash Memory Bank Organization                                              |                   |

| 5.2.1 Banks                                                                     |                   |

| 5.2.2 Flash Memory Regions                                                      | <mark>20</mark> 1 |

| 5.2.3 Addressing                                                                | 201               |

| 5.2.4 Memory Organization Examples                                              |                   |

| 5.3 Flash Controller                                                            | 203               |

| 5.3.1 Overview of Flash Controller Commands                                     |                   |

| 5.3.2 NOOP Command                                                              |                   |

| 5.3.3 PROGRAM Command                                                           | 204               |

| 5.3.4 ERASE Command                                                             |                   |

| 5.3.5 READVERIFY Command                                                        | 209               |

| 5.3.6 BLANKVERIFY Command                                                       | 210               |

| 5.3.7 Command Diagnostics                                                       |                   |

| 5.3.8 Overriding the System Address With a Bank ID, Region ID, and Bank Address | <mark>211</mark>  |

www.ti.com Table of Contents

| 5.3.9 FLASHCTL Events                                 |     |

|-------------------------------------------------------|-----|

| 5.4 Write Protection                                  |     |

| 5.4.1 Write Protection Resolution                     |     |

| 5.4.2 Static Write Protection                         |     |

| 5.4.3 Dynamic Write Protection                        |     |

| 5.5 Read Interface                                    |     |

| 5.5.1 Bank Address Swapping                           |     |

| 5.6 FLASHCTL Registers                                | 215 |

| 6 Events                                              |     |

| 6.1 Events Overview                                   |     |

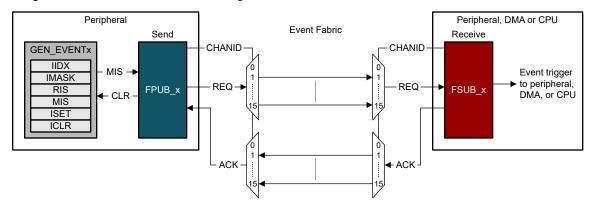

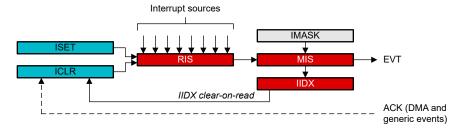

| 6.1.1 Event Publisher                                 |     |

| 6.1.2 Event Subscriber                                |     |

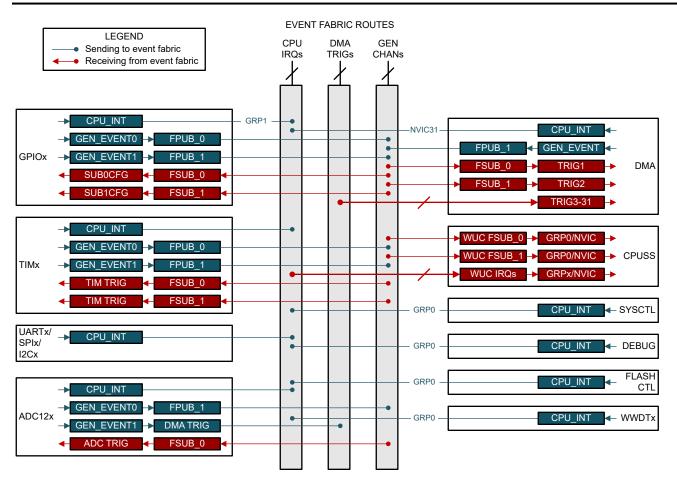

| 6.1.3 Event Fabric Routing                            |     |

| 6.1.4 Event Routing Map                               |     |

| 6.1.5 Event Propagation Latency                       |     |

| 6.2 Events Operation                                  |     |

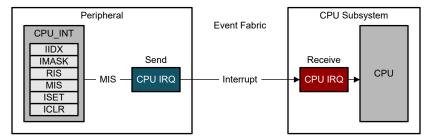

| 6.2.1 CPU Interrupt                                   | 285 |

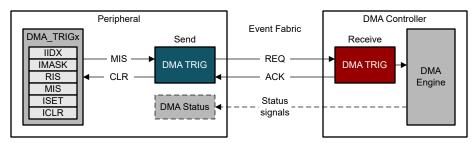

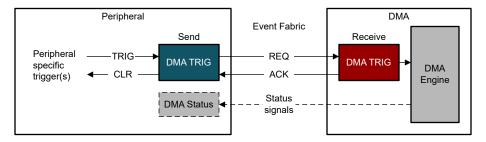

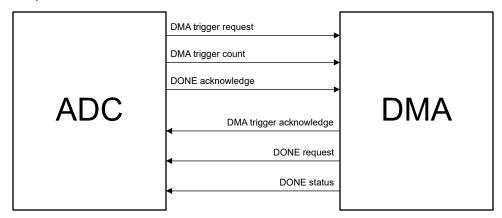

| 6.2.2 DMA Trigger                                     |     |

| 6.2.3 Peripheral to Peripheral Event                  |     |

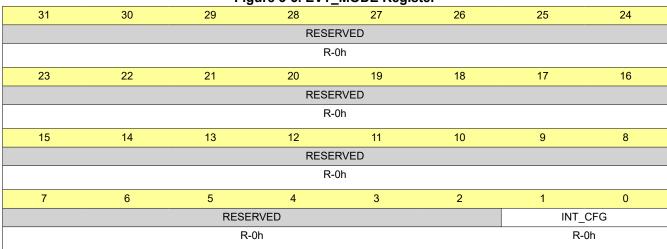

| 6.2.4 Extended Module Description Register            |     |

| 6.2.5 Using Event Registers                           |     |

| 7 IOMUX                                               |     |

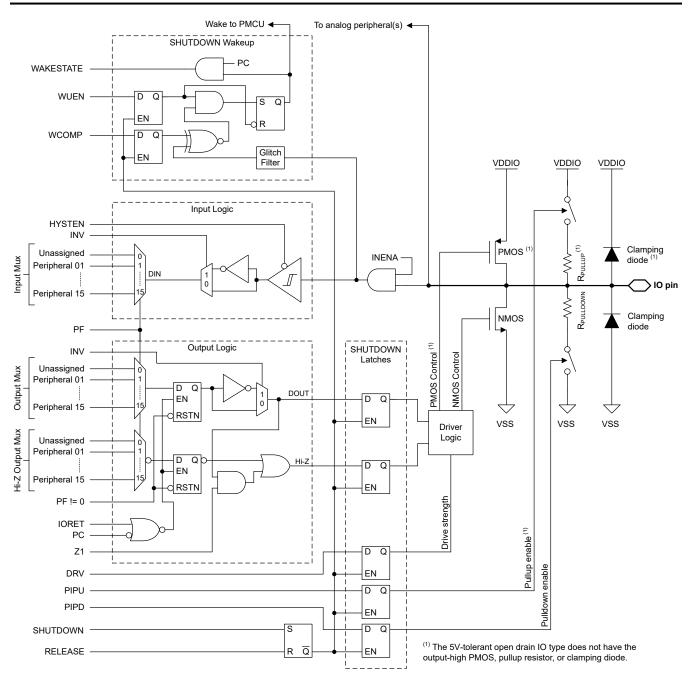

| 7.1 IOMUX Overview                                    |     |

| 7.1.1 IO Types and Analog Sharing                     |     |

| 7.2 IOMUX Operation                                   |     |

| 7.2.1 Peripheral Function (PF) Assignment             |     |

| 7.2.2 Logic High to Hi-Z Conversion                   | 295 |

| 7.2.3 Logic Inversion                                 |     |

| 7.2.4 SHUTDOWN Mode Wakeup Logic                      |     |

| 7.2.5 Pullup/Pulldown Resistors                       |     |

| 7.2.6 Drive Strength Control                          |     |

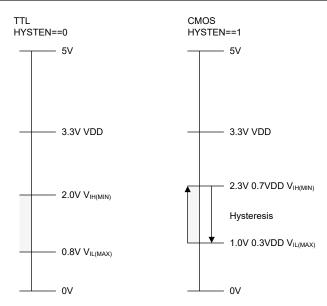

| 7.2.7 Hysteresis and Logic Level Control              |     |

| 7.3 IOMUX (PINCMx) Register Format                    |     |

| 7.4 IOMUX Registers                                   | 301 |

| 8 GPIO                                                | 305 |

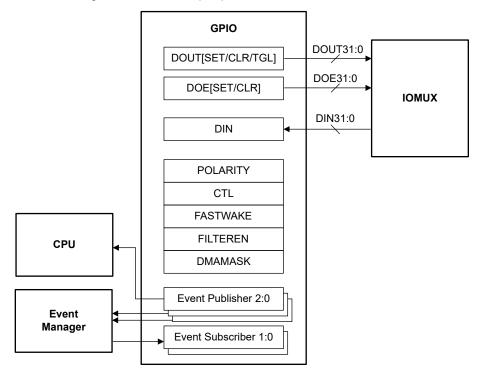

| 8.1 GPIO Overview                                     |     |

| 8.2 GPIO Operation                                    | 306 |

| 8.2.1 GPIO Ports                                      |     |

| 8.2.2 GPIO Read/Write Interface                       |     |

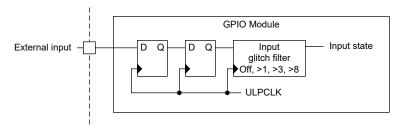

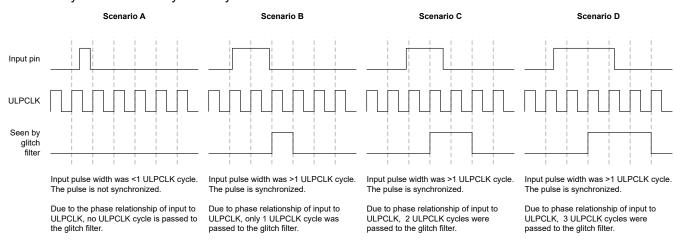

| 8.2.3 GPIO Input Glitch Filtering and Synchronization |     |

| 8.2.4 GPIO Fast Wake                                  |     |

| 8.2.5 GPIO DMA Interface                              |     |

| 8.2.6 Event Publishers and Subscribers                |     |

| 8.3 GPIO Registers                                    |     |

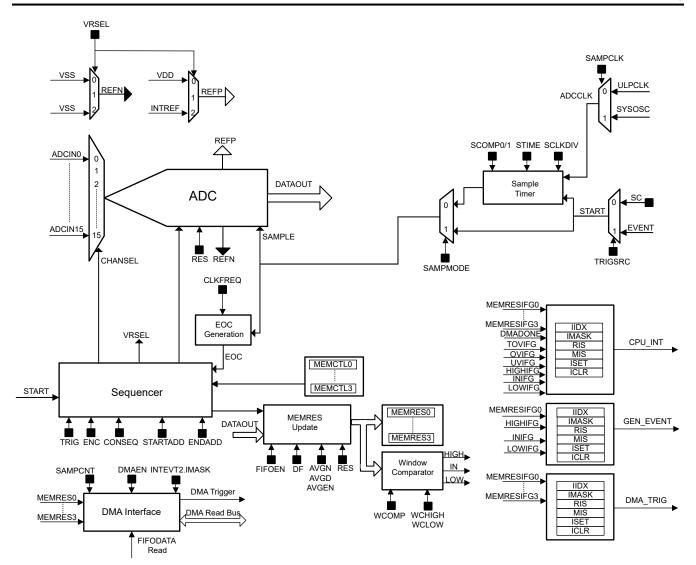

| 9 ADC                                                 |     |

| 9.1 ADC Overview                                      |     |

| 9.2 ADC Operation                                     |     |

| 9.2.1 ADC Core                                        |     |

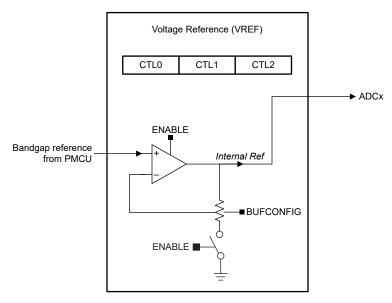

| 9.2.2 Voltage Reference Options                       |     |

| 9.2.3 Generic Resolution Modes.                       |     |

| 9.2.4 Hardware Averaging                              |     |

| 9.2.5 ADC Clocking                                    |     |

| 9.2.6 Common ADC Use Cases                            |     |

| 9.2.7 Power Down Behavior                             |     |

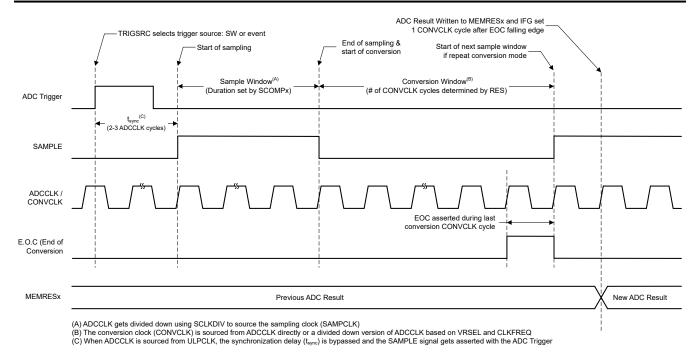

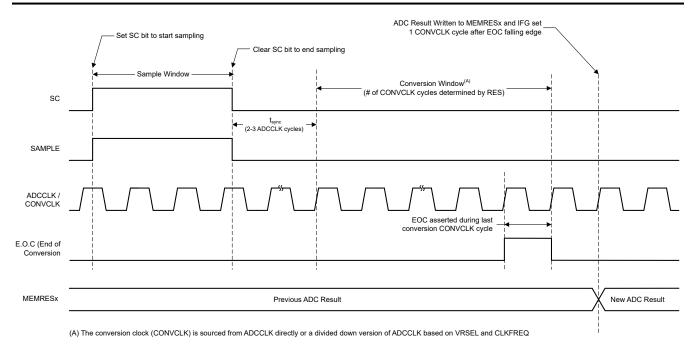

| 9.2.8 Sampling Trigger Sources and Sampling Modes     |     |

| 9.2.9 Sampling Period                                 |     |

| 9.2.10 Conversion Modes                               |     |

| 9.2.11 Data Format                                    |     |

| 9.2.12 Advanced Features                              |     |

| 9.2.13 Status Register                                |     |

| 9.2.14 ADC Events                                     | 433 |

Table of Contents www.ti.com

| 9.3 ADC0 Registers                                  | 436 |

|-----------------------------------------------------|-----|

| 10 VREF                                             |     |

| 10.1 VREF Overview                                  |     |

| 10.2 VREF Operation                                 |     |

| 10.2 VNEF Operation                                 |     |

|                                                     |     |

| 10.3 VREF Registers                                 |     |

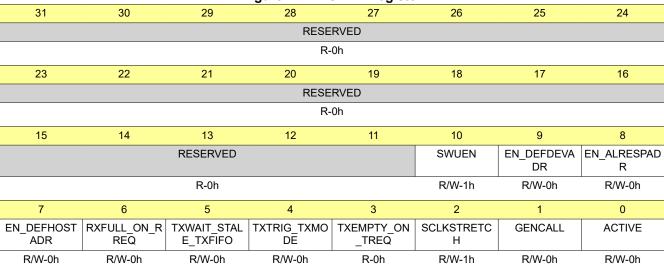

| 11 UART                                             |     |

| 11.1 UART Overview                                  |     |

| 11.1.1 Purpose of the Peripheral                    |     |

| 11.1.2 Features                                     |     |

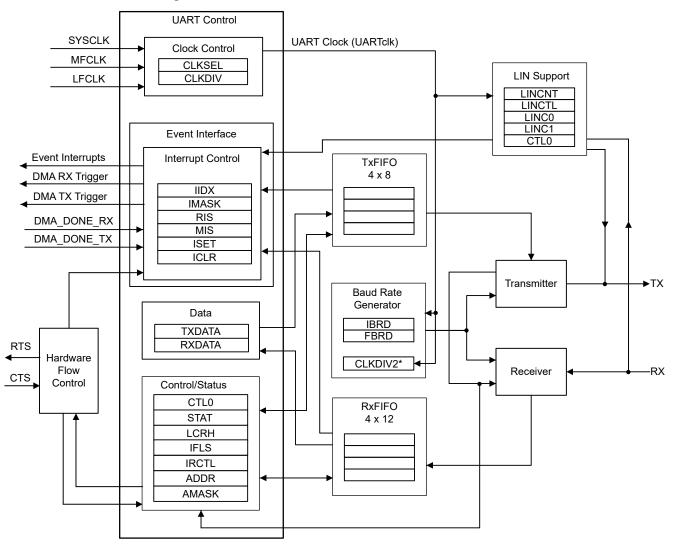

| 11.1.3 Functional Block Diagram                     |     |

| 11.2 UART Operation                                 |     |

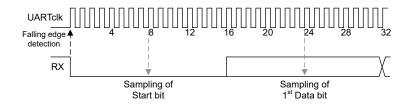

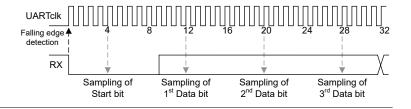

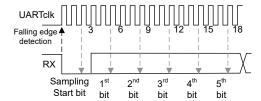

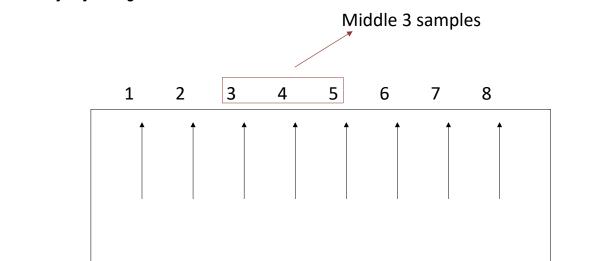

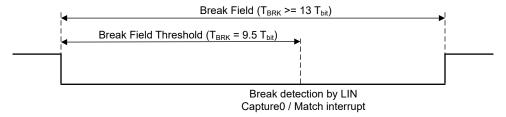

| 11.2.1 Clock Control                                | 498 |

| 11.2.2 Signal Descriptions                          |     |

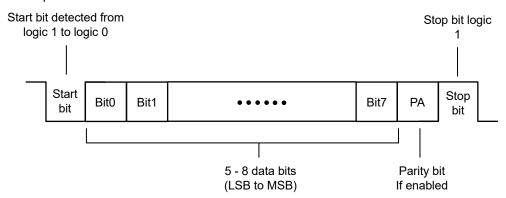

| 11.2.3 General Architecture and Protocol            | 498 |

| 11.2.4 Low Power Operation                          |     |

| 11.2.5 Reset Considerations                         |     |

| 11.2.6 Initialization                               |     |

| 11.2.7 Interrupt and Events Support.                |     |

| 11.2.8 Emulation Modes.                             |     |

| 11.3 UART0 Registers                                |     |

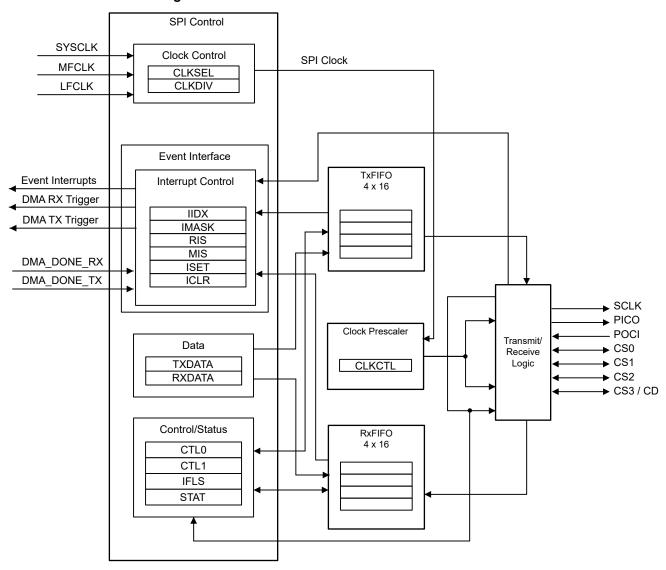

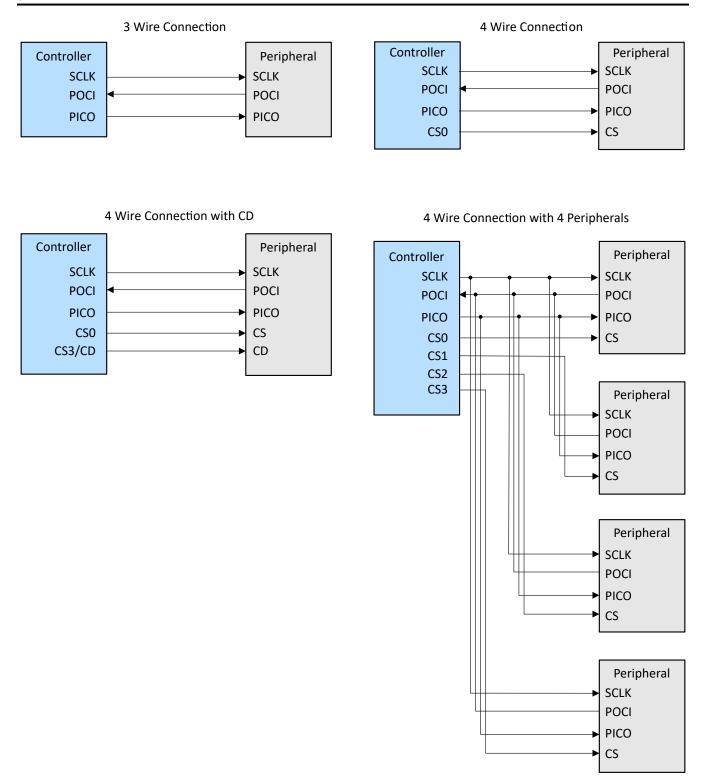

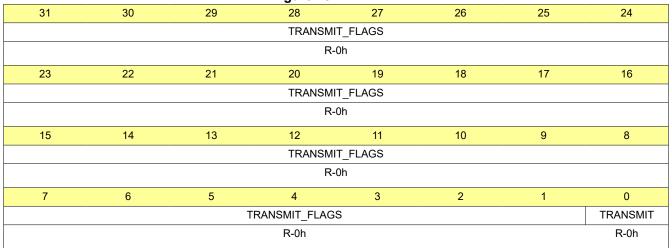

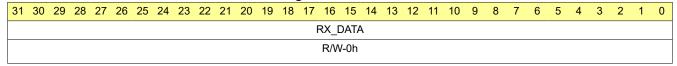

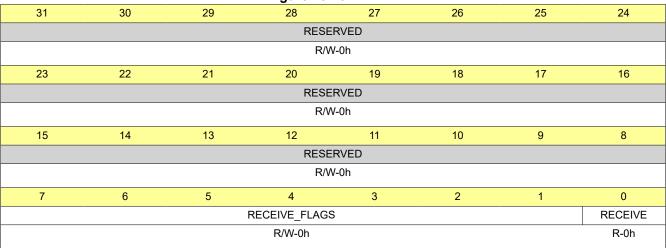

| 12 SPI                                              |     |

| 12.1 SPI Overview.                                  |     |

|                                                     |     |

| 12.1.1 Purpose of the Peripheral                    |     |

| 12.1.2 Features                                     |     |

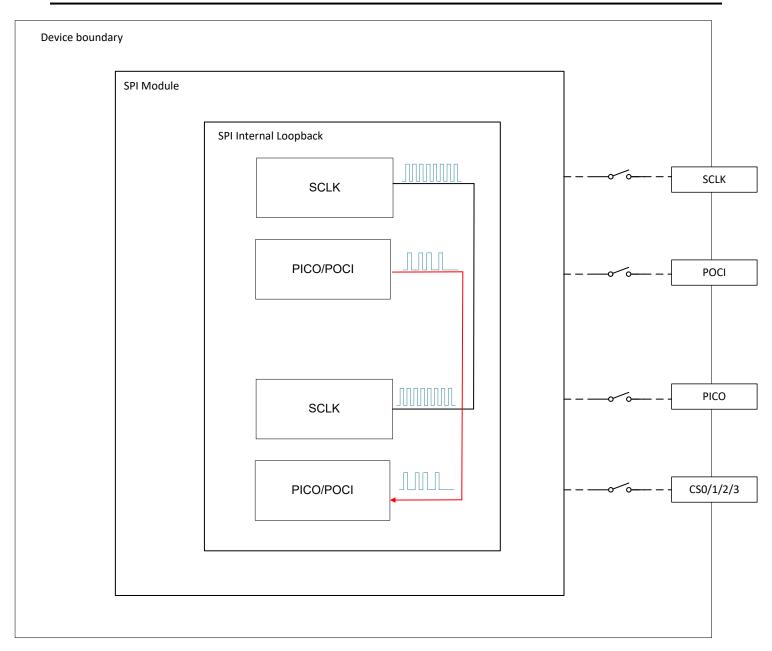

| 12.1.3 Functional Block Diagram                     |     |

| 12.1.4 External Connections and Signal Descriptions |     |

| 12.2 SPI Operation                                  |     |

| 12.2.1 Clock Control                                |     |

| 12.2.2 General Architecture                         |     |

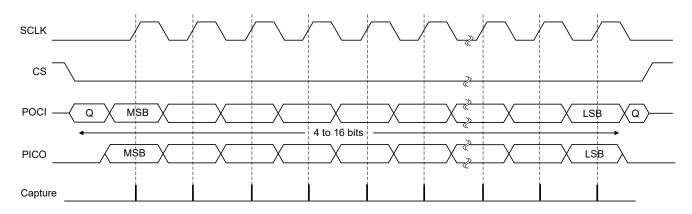

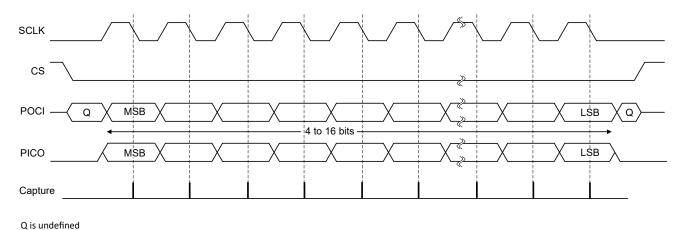

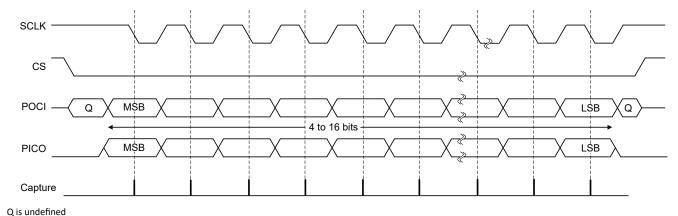

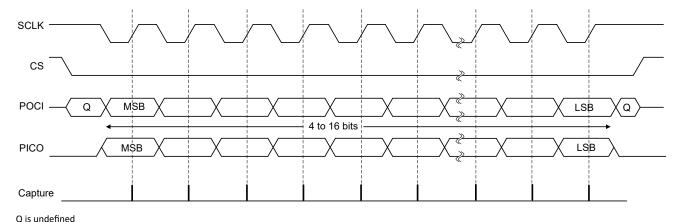

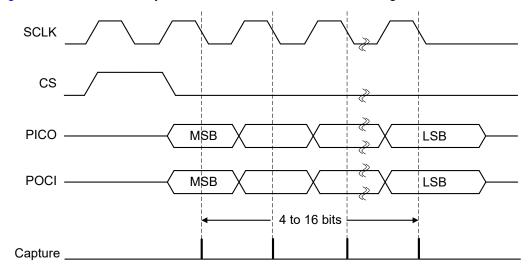

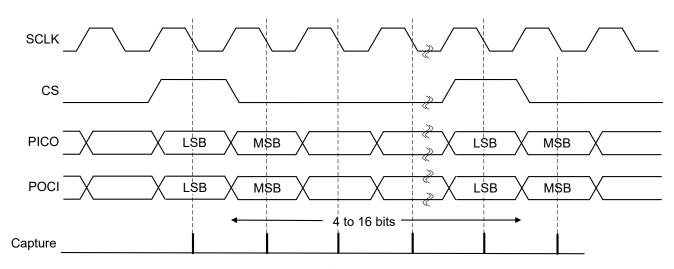

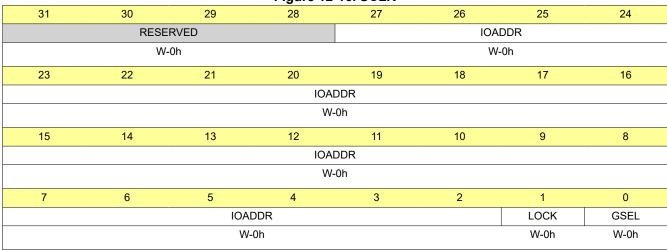

| 12.2.3 Protocol Descriptions                        | 564 |

| 12.2.4 Reset Considerations                         | 569 |

| 12.2.5 Initialization                               | 569 |

| 12.2.6 Interrupt and Events Support                 | 569 |

| 12.2.7 Emulation Modes                              | 571 |

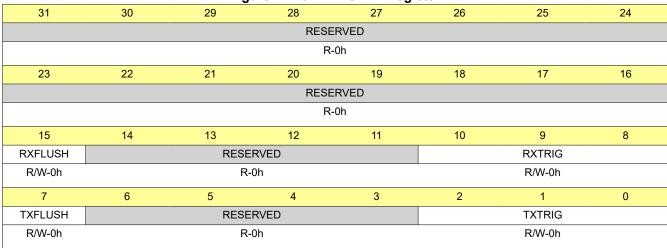

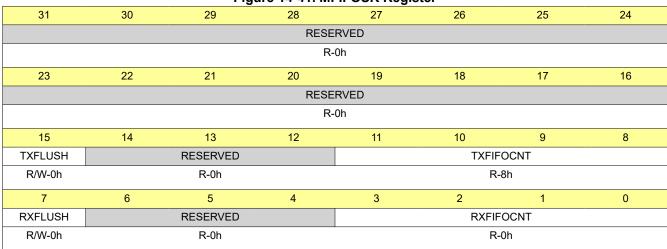

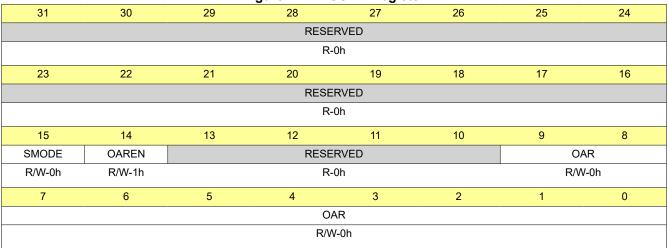

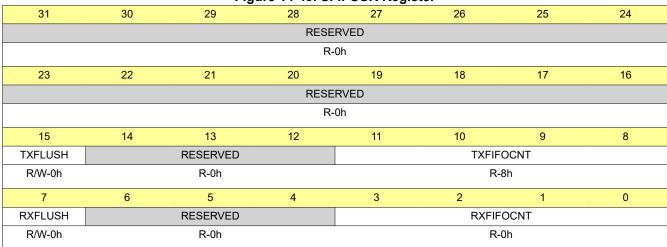

| 12.3 SPI Registers                                  |     |

| 13 I <sup>2</sup> C                                 |     |

| 13.1 I <sup>2</sup> C Overview                      |     |

| 13.1.1 Purpose of the Peripheral                    |     |

| 13.1.2 Features                                     |     |

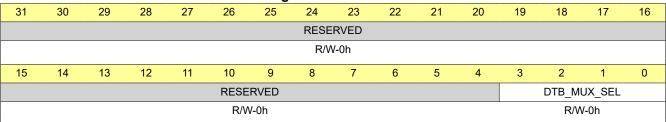

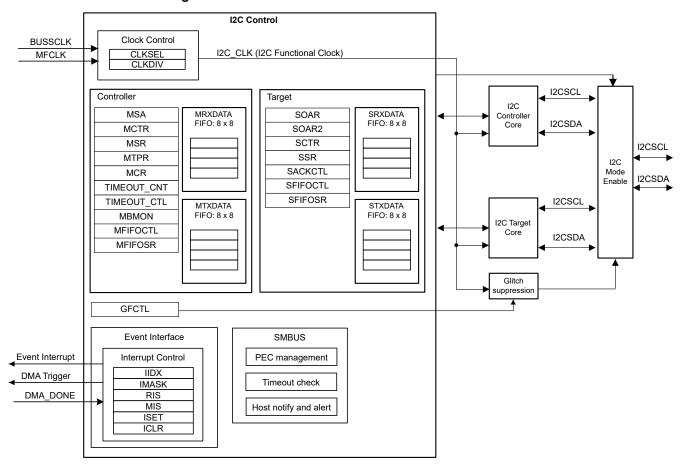

| 13.1.3 Functional Block Diagram                     |     |

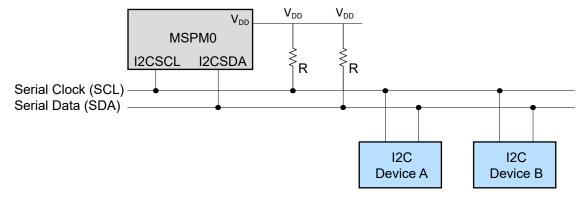

| 13.1.4 Environment and External Connections.        |     |

| 13.2 I <sup>2</sup> C Operation.                    |     |

| 13.2.1 Clock Control.                               |     |

|                                                     |     |

| 13.2.2 Signal Descriptions                          |     |

|                                                     |     |

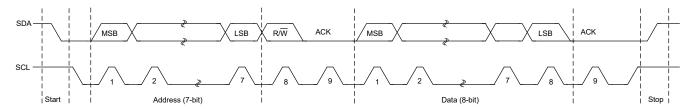

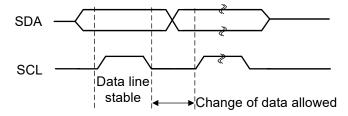

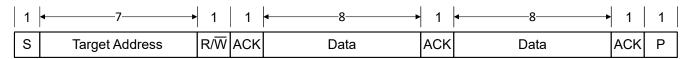

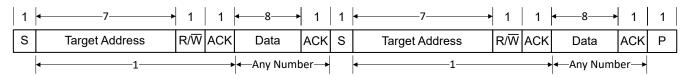

| 13.2.4 Protocol Descriptions.                       |     |

| 13.2.5 Reset Considerations                         |     |

| 13.2.6 Initialization                               |     |

| 13.2.7 Interrupt and Events Support                 |     |

| 13.2.8 Emulation Modes                              |     |

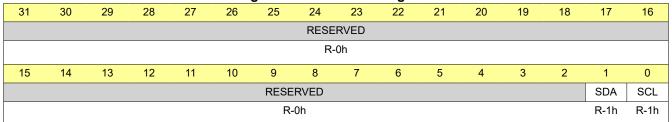

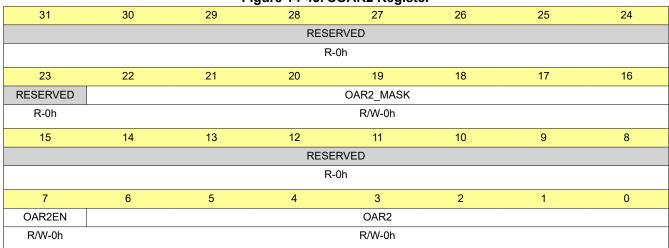

| 14 I2C Registers                                    |     |

| 15 CRC                                              |     |

| 15.1 CRC Overview                                   |     |

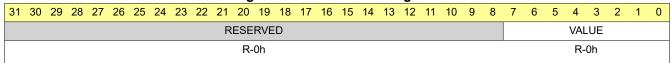

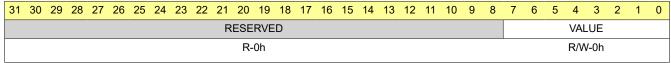

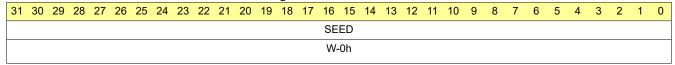

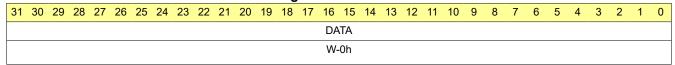

| 15.1.1 CRC16-CCITT                                  | 740 |

| 15.2 CRC Operation                                  | 740 |

| 15.2.1 CRC Generator Implementation                 | 740 |

| 15.2.2 Configuration                                |     |

| 15.3 CRC Registers                                  |     |

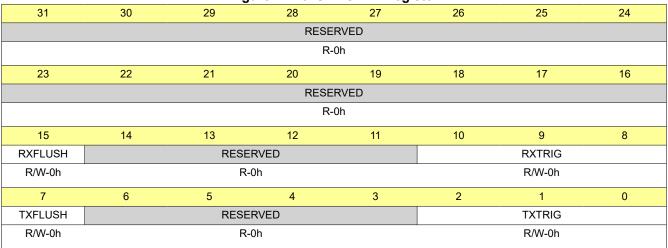

| 16 Timers (TIMx)                                    |     |

| 16.1 TIMx Overview                                  |     |

|                                                     |     |

www.ti.com Table of Contents

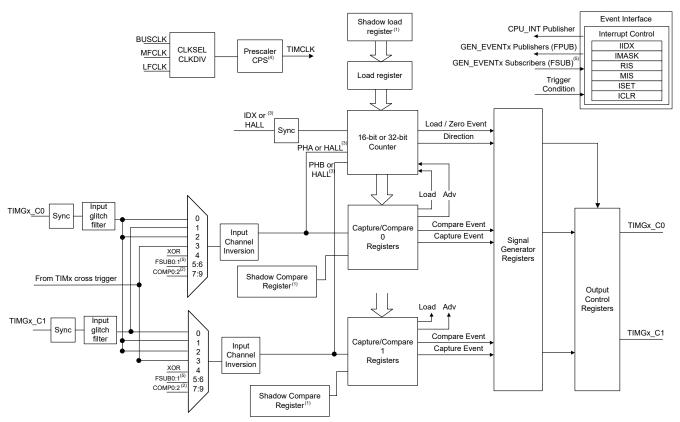

| 16.1.1 TIMG Overview                      | 756 |

|-------------------------------------------|-----|

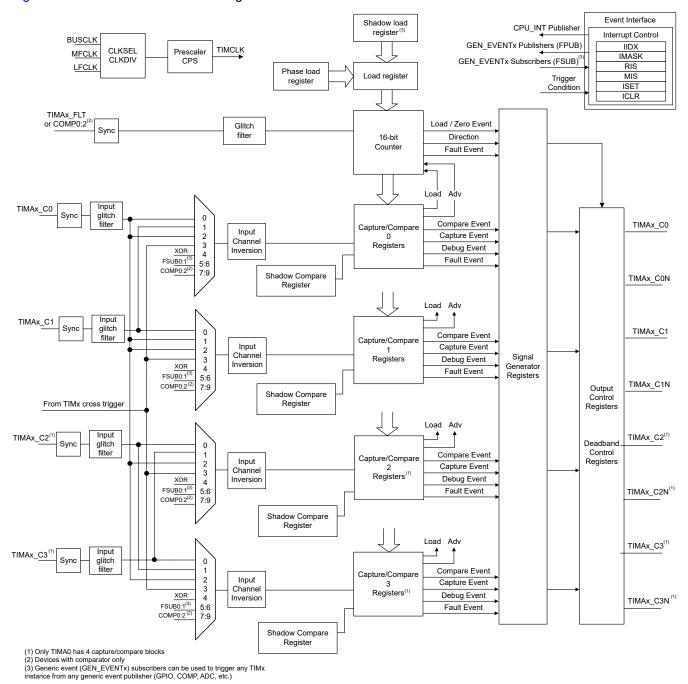

| 16.1.2 TIMA Overview                      | 757 |

| 16.1.3 TIMx Instance Configuration        |     |

| 16.2 TIMx Operation                       | 759 |

| 16.2.1 Timer Counter                      | 760 |

| 16.2.2 Counting Mode Control              |     |

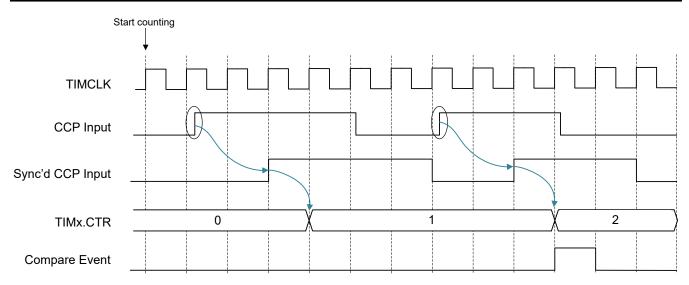

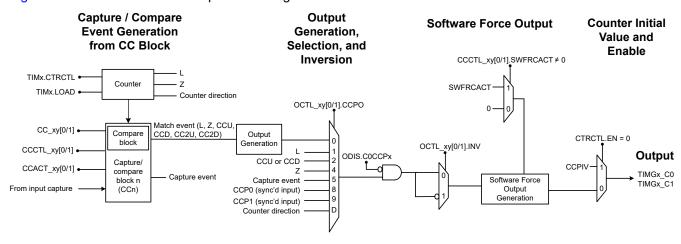

| 16.2.3 Capture/Compare Module             | 768 |

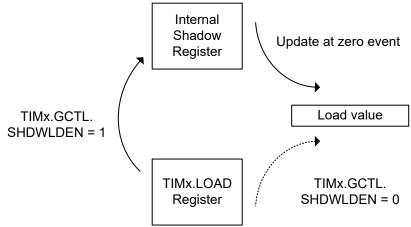

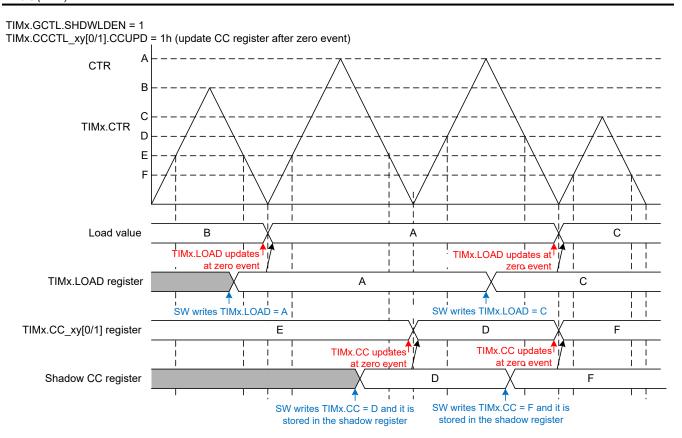

| 16.2.4 Shadow Load and Shadow Compare     |     |

| 16.2.5 Output Generator                   |     |

| 16.2.6 Fault Handler (TIMA only)          | 794 |

| 16.2.7 Synchronization With Cross Trigger | 800 |

| 16.2.8 Low Power Operation                |     |

| 16.2.9 Interrupt and Event Support        | 802 |

| 16.2.10 Debug Handler (TIMA only)         | 806 |

| 16.3 Timers (TIMx) Registers              | 807 |

| 17 WWDT                                   | 901 |

| 17.1 WWDT Overview                        | 902 |

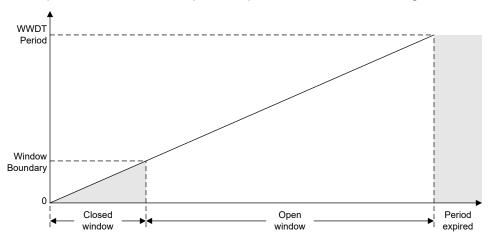

| 17.1.1 Watchdog Mode                      | 902 |

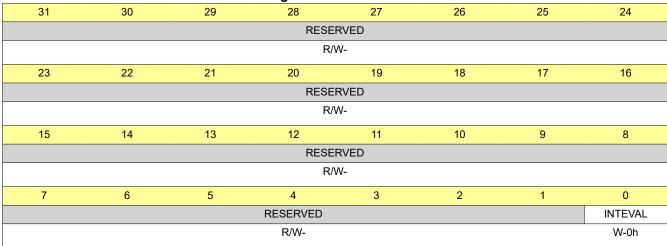

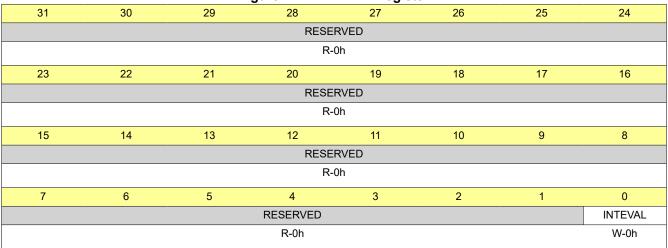

| 17.1.2 Interval Timer Mode                | 903 |

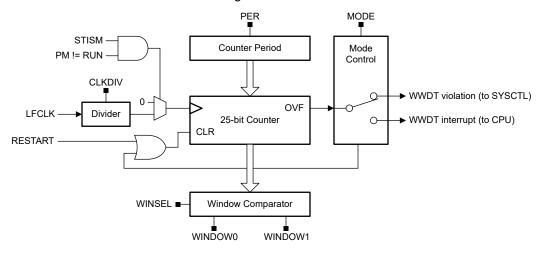

| 17.2 WWDT Operation                       | 903 |

| 17.2.1 Mode Selection                     | 903 |

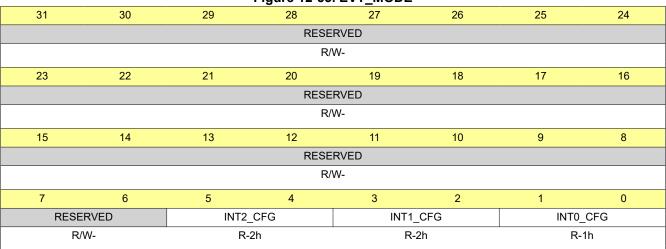

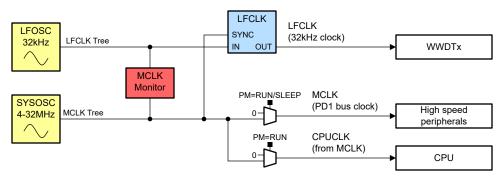

| 17.2.2 Clock Configuration                |     |

| 17.2.3 Low-Power Mode Behavior            | 905 |

| 17.2.4 Debug Behavior                     | 905 |

| 17.2.5 WWDT Events                        |     |

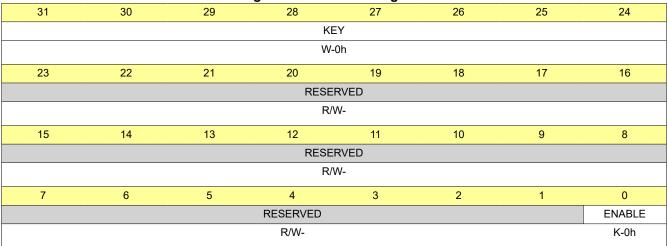

| 17.3 WWDT Registers                       |     |

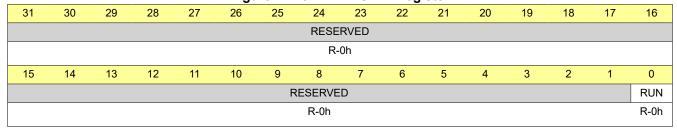

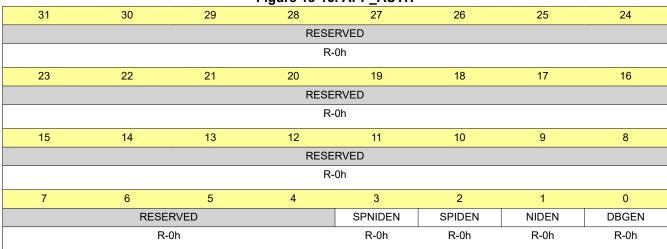

| 18 Debug                                  | 925 |

| 18.1 Overview                             | 926 |

| 18.1.1 Debug Interconnect                 |     |

| 18.1.2 Physical Interface                 |     |

| 18.1.3 Debug Access Ports                 |     |

| 18.2 Debug Features                       | 928 |

| 18.2.1 Processor Debug                    |     |

| 18.2.2 Peripheral Debug                   |     |

| 18.2.3 EnergyTrace Technology             |     |

| 18.3 Behavior in Low Power Modes          |     |

| 18.4 Restricting Debug Access             |     |

| 18.5 Mailbox (DSSM)                       |     |

| 18.5.1 DSSM Events                        |     |

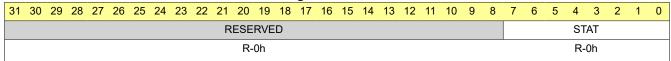

| 18.5.2 DEBUGSS Registers                  |     |

| 19 Revision History                       | 949 |

Table of Contents www.ti.com

This page intentionally left blank.

#### **About This Manual**

This manual describes the modules and peripherals of the MSPM0C family of devices. Each description presents the module or peripheral in a general sense. Not all features and functions of all modules or peripherals are present on all devices. In addition, modules or peripherals can differ in their exact implementation on different devices. Pin functions, internal signal connections, and operational parameters differ from device to device. See the device-specific data sheet for these details.

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers can be shown with the suffix h or the prefix 0x. For example, the following number is 40 hexadecimal (decimal 64): 40h or 0x40.

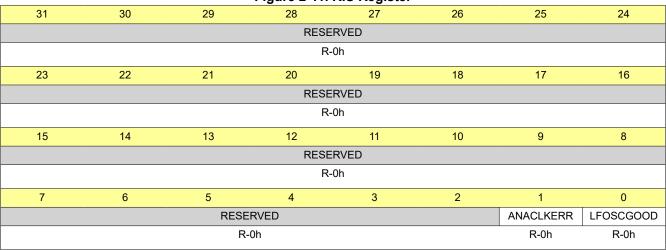

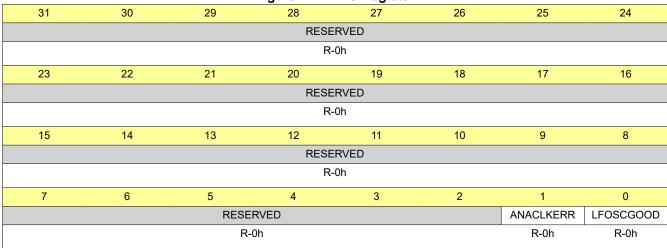

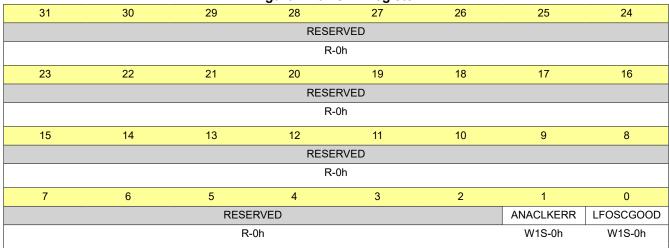

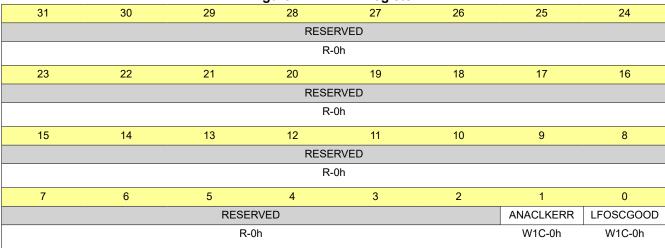

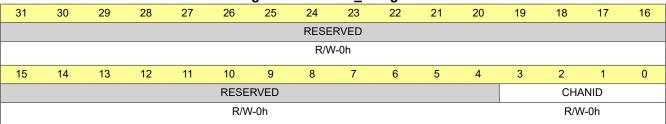

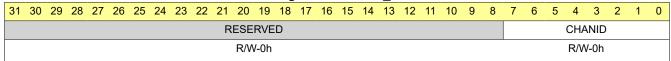

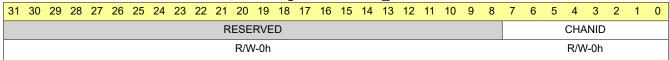

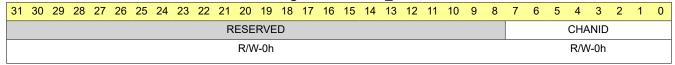

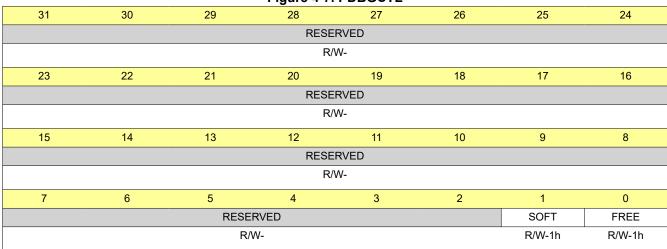

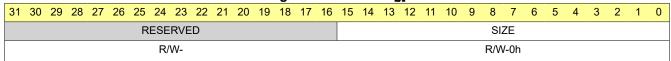

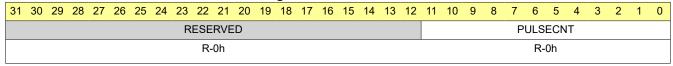

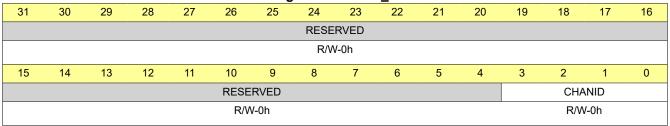

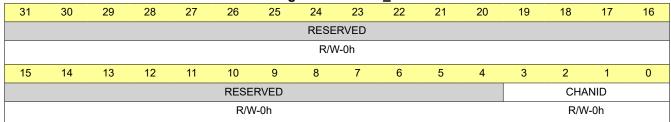

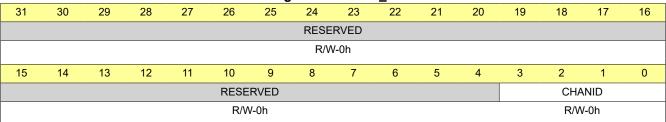

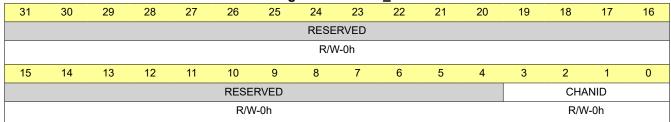

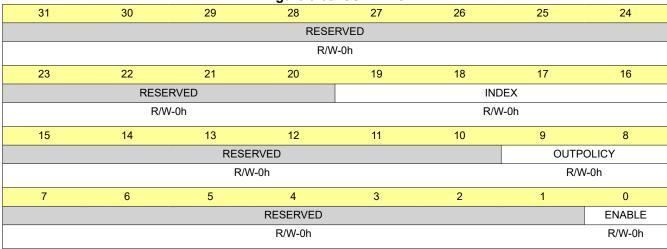

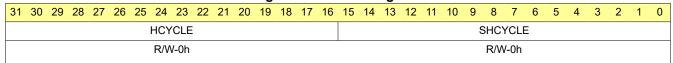

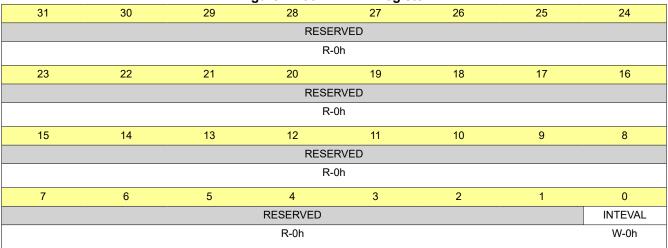

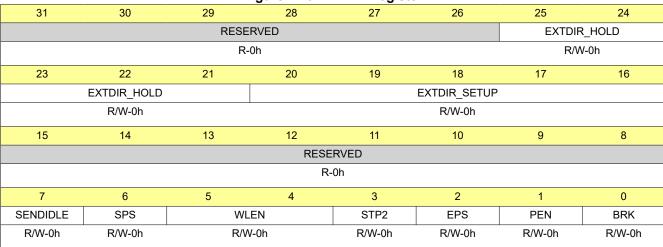

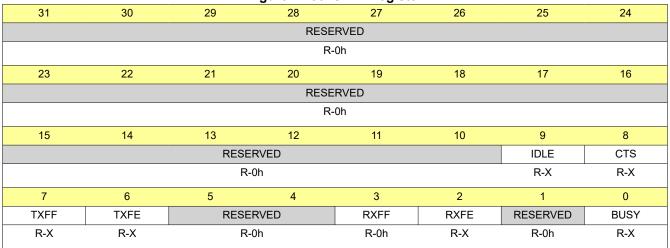

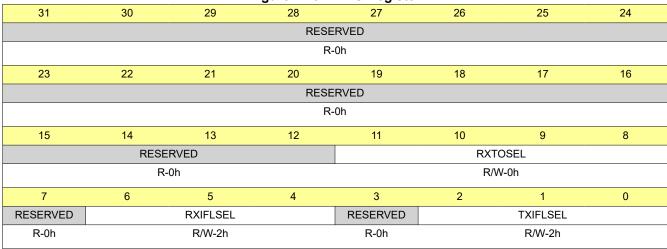

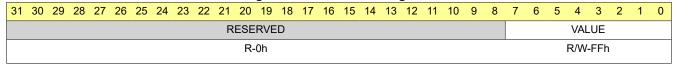

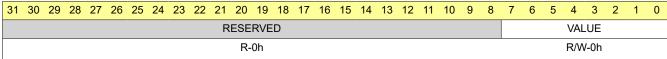

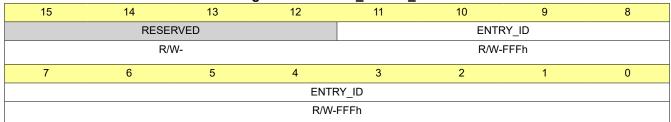

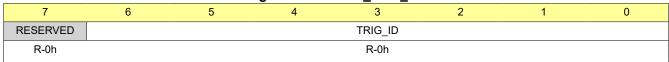

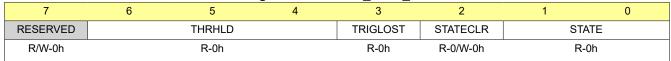

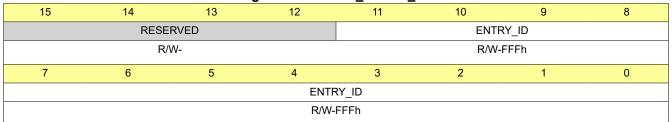

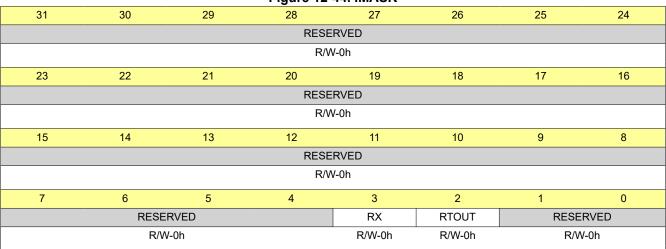

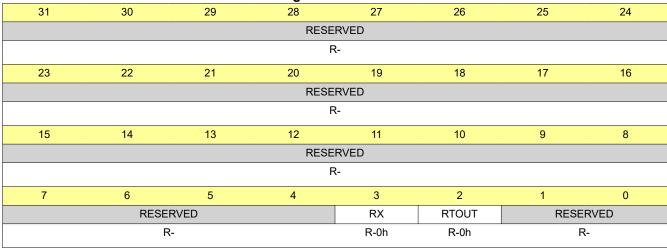

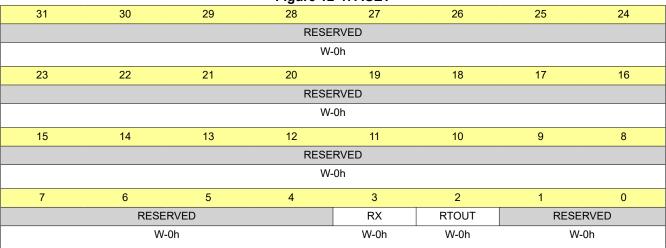

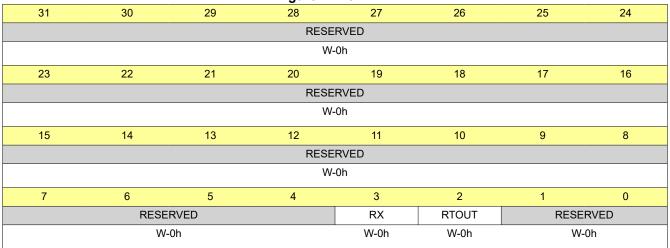

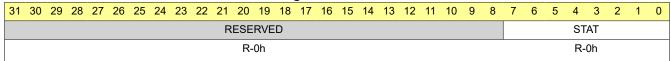

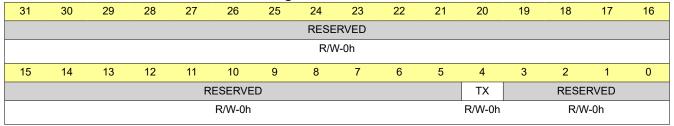

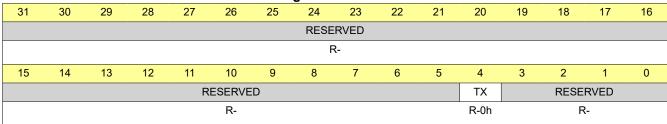

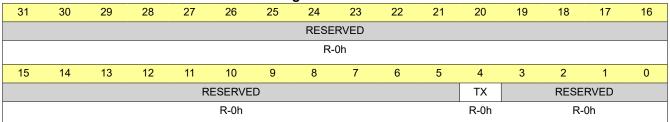

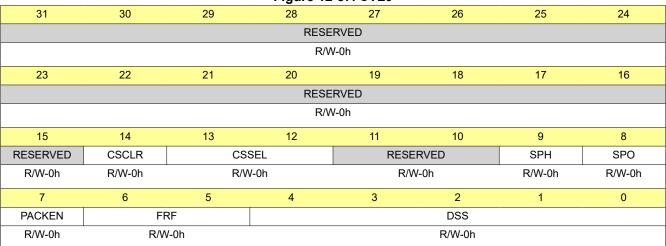

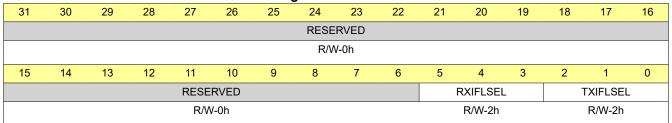

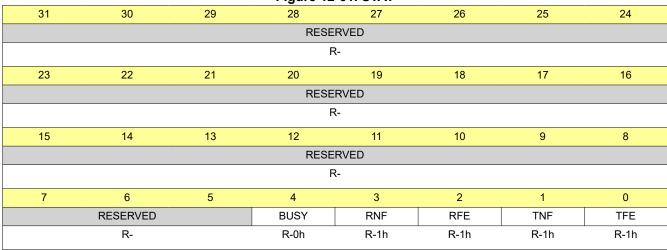

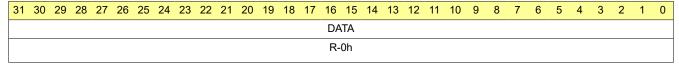

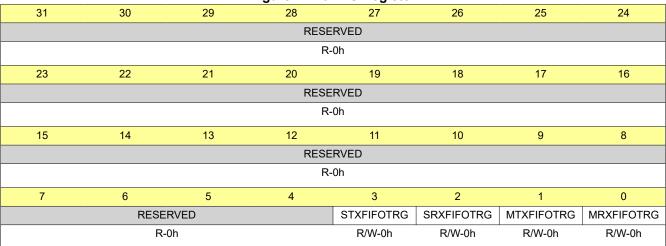

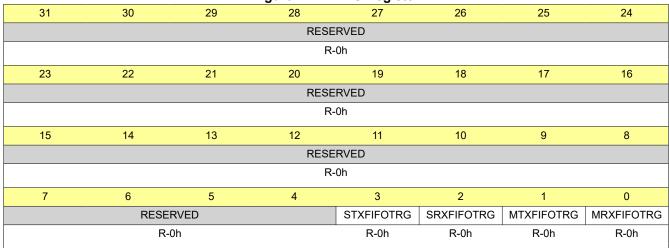

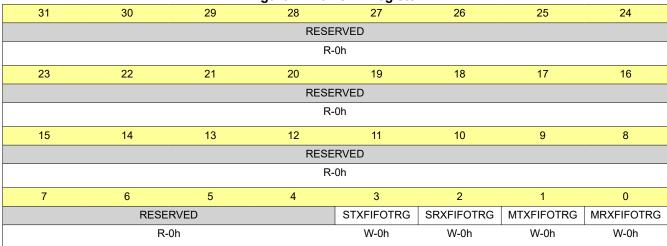

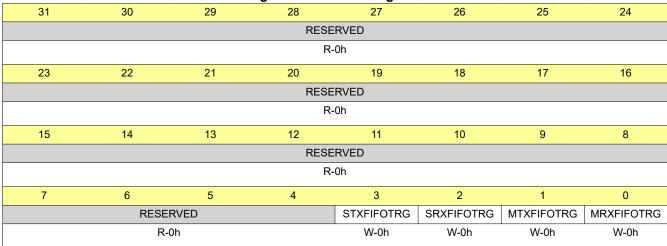

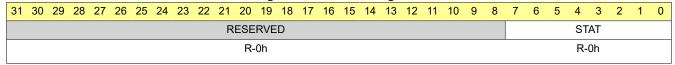

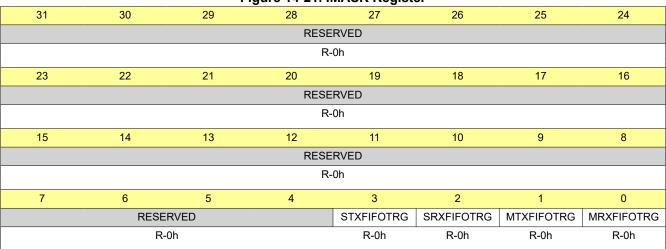

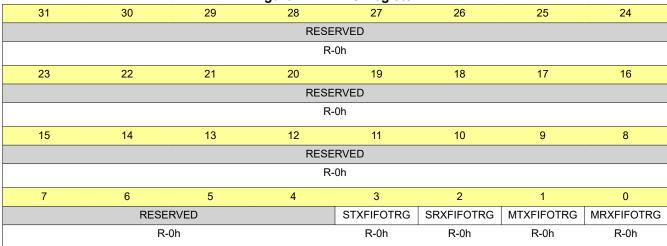

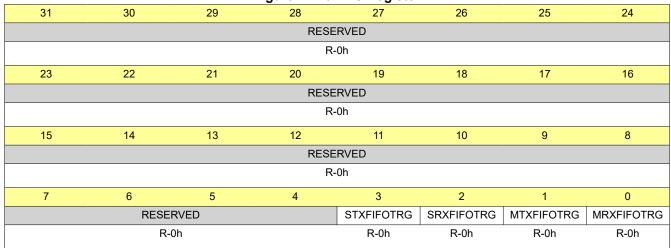

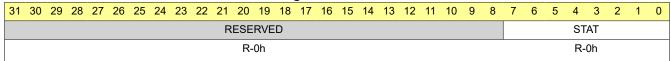

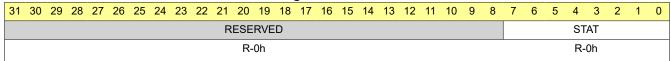

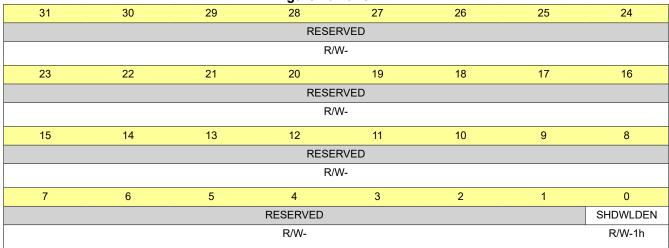

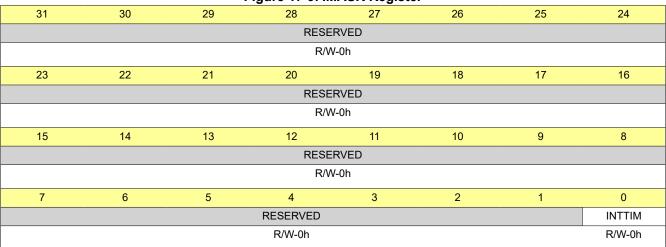

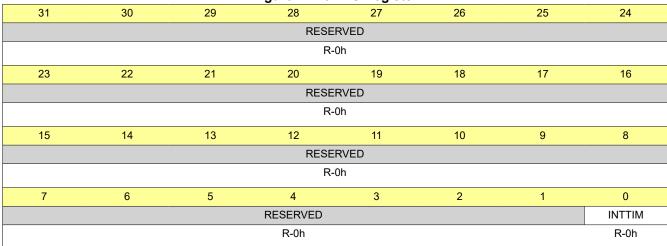

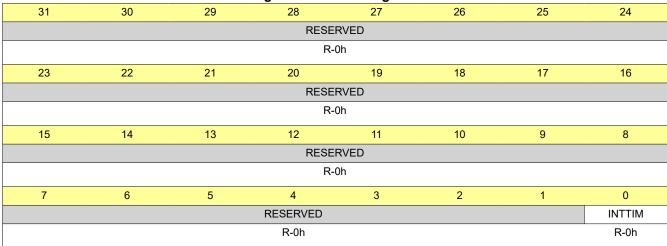

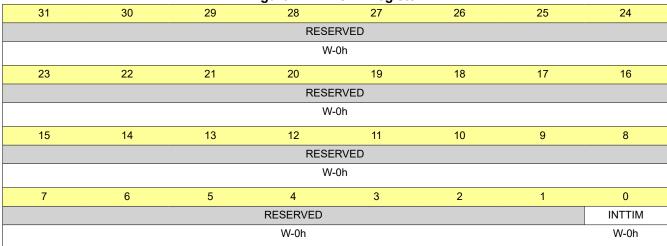

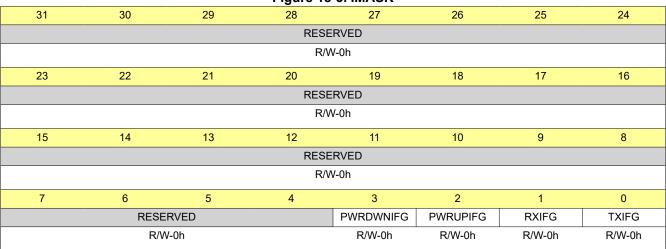

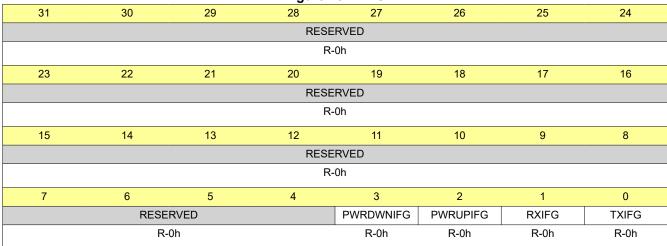

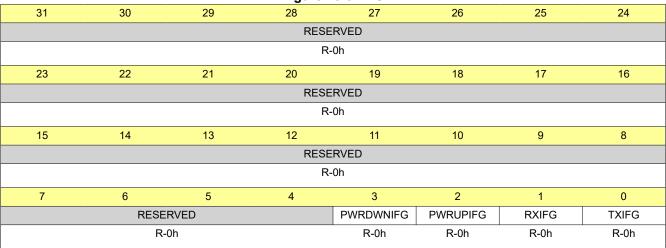

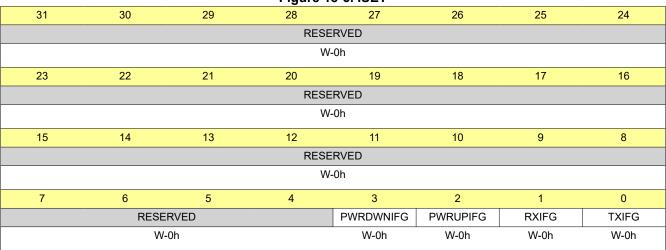

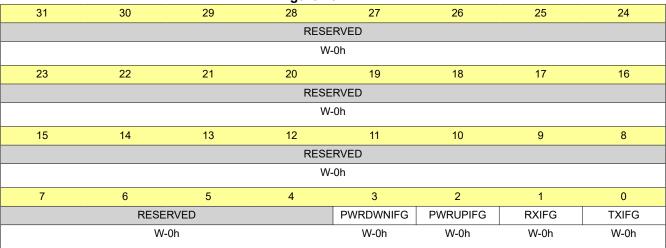

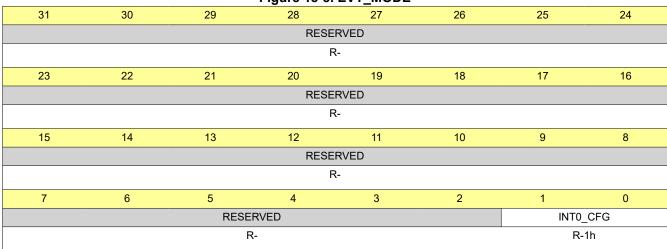

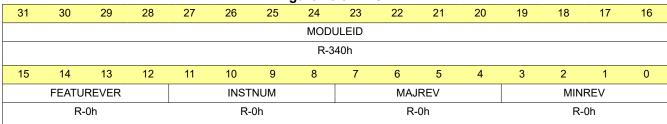

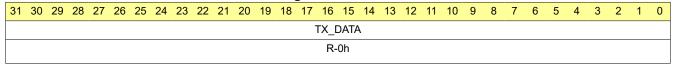

- · Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register. Each field

is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties with

default reset value below. A legend explains the notation used for the properties.

- Reserved bits in a register figure can have one of multiple meanings:

- · Not implemented on the device

- · Reserved for future device expansion

- Reserved for TI testing

- Reserved configurations of the device that are not supported

- Writing nondefault values to the Reserved bits could cause unexpected behavior and should be avoided.

#### **Glossary**

TI Glossary This glossary lists and explains terms, acronyms, and definitions.

## **Related Documentation**

#### **Support Resources**

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### **Trademarks**

TI E2E<sup>™</sup> and EnergyTrace<sup>™</sup> are trademarks of Texas Instruments. Arm<sup>®</sup> and Cortex<sup>®</sup> are registered trademarks of Arm Limited. All trademarks are the property of their respective owners.

Read This First www.ti.com

This page intentionally left blank.

# Chapter 1 **Architecture**

The device architecture includes the bus organization, the platform memory map, and the boot configuration.

| 1.1 Architecture Overview | 12 |

|---------------------------|----|

| 1.2 Bus Organization      |    |

| 1.3 Platform Memory Map   |    |

| 1.4 Boot Configuration    | 15 |

| 1.5 NONMAIN Registers     |    |

|                           |    |

| 1.6 Factory Constants     | 26 |

#### 1.1 Architecture Overview

MSPM0 C-series MCUs (MSPM0Cxx) combine 32-bit compute performance together with precision analog to enable a wide variety of sensing, interface, control, and housekeeping applications. The device architecture supports both general-purpose and low-cost applications through a simple, easy-to-use device with the low development cost.

MSPM0 C-series devices also offer support for 125°C ambient temperature and AEC-Q100 Grade 1 qualification.

This chapter introduces the device architecture, including an overview of the power domains and bus organization, the platform memory map, and the device boot configuration.

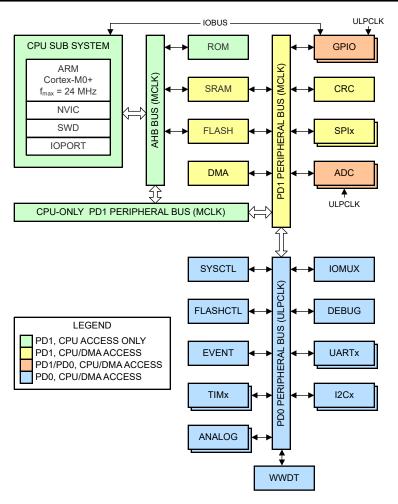

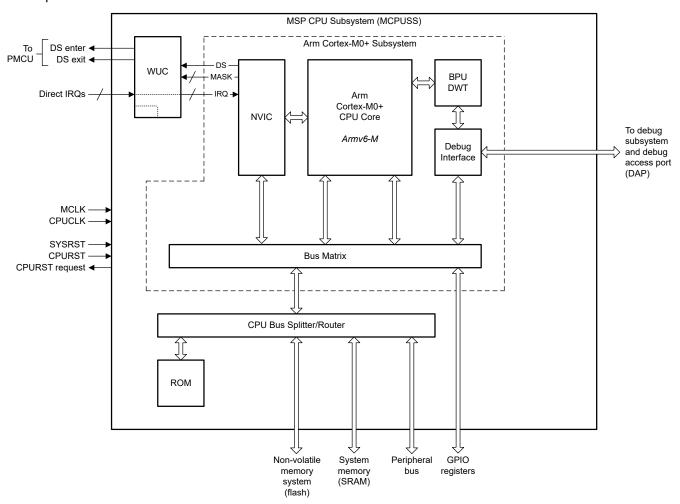

## 1.2 Bus Organization

There are three main power domains on MSPM0Cxx devices:

- PD1 (power domain 1) which contains the CPU subsystem, memory interfaces, and high-speed peripherals

- PD0 (power domain 0) which contains the low-speed low-power peripherals

- The supply voltage (VDD) which powers IOs, analog modules, and limited logic directly from the supply

The PD1 domain is disabled in certain operating modes to minimize power consumption. The PD0 domain supports ultra-low-power performance and is always enabled in operating modes in which the core regulator is operating.

There are four main data buses on MSPM0Cxx devices:

- The AHB bus matrix, which interfaces the CPU to the device memory systems (ROM, SRAM, and flash memory) and the peripheral buses

- The PD1 (power domain 1) CPU-only peripheral bus, clocked from MCLK

- The PD1 (power domain 1) peripheral bus, clocked from MCLK

- The PD0 (power domain 0) peripheral bus, clocked from ULPCLK

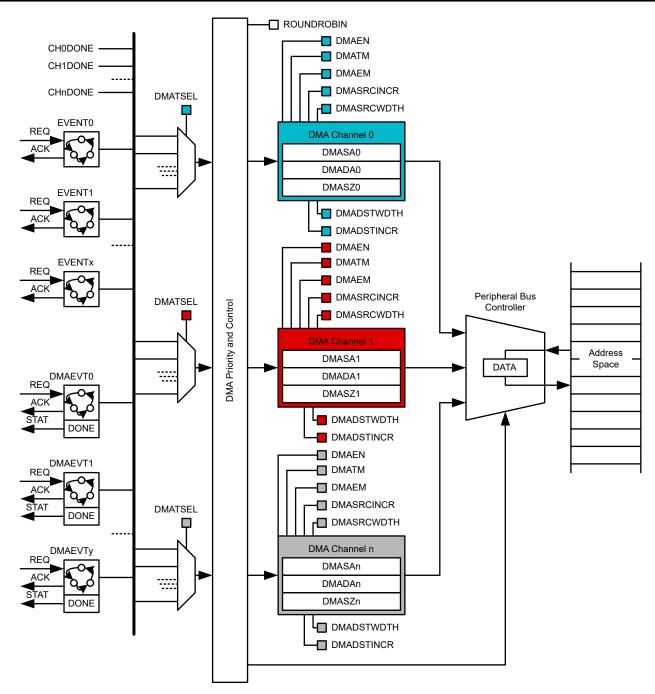

The CPU and the DMA controller are the only two bus controllers in the device. Arbitration between the CPU and the DMA for shared peripherals happens between the CPU-only PD1 peripheral bus and the CPU/DMA PD1 peripheral bus. The DMA does not have access to peripherals on the CPU-only PD1 peripheral bus or the CPU bus matrix (the green components in the bus diagram). As such, the CPU can access peripherals on the CPU-only PD1 peripheral bus at the same time that the DMA is processing a transaction on the PD1 or PD0 bus.

Likewise, the CPU can access SRAM or flash memory through the AHB bus matrix at the same time that the DMA is processing a transaction, so long as the DMA is not accessing the same memory that the CPU is attempting to access. Arbitration between the CPU and the DMA for memory systems (SRAM or flash memory) happens at the memory interface itself. All arbitration between the CPU and DMA is done on a round-robin basis.

Figure 1-1. MSPM0Cxx Bus Organization

#### Note

This is a generic diagram of the typical peripherals on an MSPM0Cxx device and their respective bus locations. Not all devices have all peripheral options shown here. To determine the peripherals which are available on a given device, see the device-specific data sheet.

The GPIO and ADC peripherals (the orange components in the bus diagram) have special capabilities to enable both fast register access from the CPU and operation in low power operating modes.

- GPIO peripherals interface to the system through two mechanisms: the PD1 peripheral bus, and the Arm<sup>®</sup>

Cortex<sup>®</sup>-M0+ single-cycle high-speed IO bus.

- Accesses from the CPU to any GPIO registers are transacted through the single-cycle IO bus for best performance, enabling fast toggling of IO under software control.

- The GPIO DOUT registers (data out) are also available on the PD1 peripheral bus, primarily so that the DMA can be used to load values to the GPIO DOUT registers.

- While the bus interfaces to the GPIO peripherals are in the PD1 power domain (for best read/write performance), the GPIO logic itself is in the PD0 power domain so that it is available in all operating modes in which the core regulator is active.

- ADC peripherals interface to the system through the PD1 peripheral bus but contain functional logic in the PD0 power domain.

- ADC peripheral register accesses are processed through the PD1 peripheral bus (for best read/write performance)

The the ADC conversion logic is in the PD0 power domain to enable running timer-triggered ADC conversions without CPU interaction in certain low-power modes when PD1 is disabled.

## 1.3 Platform Memory Map

All MSPM0Cxx devices share a common platform memory map. Peripherals are assigned a fixed address space and have the same address space on all devices within the family. The memory map is compliant with the standard Arm Cortex-M memory regions.

Table 1-1. Top Level Memory Map

| Memory Region | Start Address | End Address | Description                                                                     |

|---------------|---------------|-------------|---------------------------------------------------------------------------------|

| Code          | 0x0000.0000   | 0x1FFF.FFFF | Flash memory and ROM                                                            |

| SRAM          | 0x2000.0000   | 0x3FFF.FFFF | SRAM                                                                            |

| Peripheral    | 0x4000.0000   | 0x5FFF.FFFF | Global peripheral memory-mapped registers and global non-executable data memory |

| Subsystem     | 0x6000.0000   | 0x7FFF.FFFF | Local CPU subsystem memory-mapped registers                                     |

| System PPB    | 0xE000.0000   | 0xE00F.FFFF | Arm private peripheral bus                                                      |

#### 1.3.1 Code Region

The code region contains the flash memory used to store executable code and data. Accesses to the flash memory from the CPU through the code region are processed through the AHB bus matrix to the flash read interface directly. See Section 5.2.3.1 for the detailed flash memory map.

The code region also contains the read-only memory (ROM) used for the TI device boot code and the bootstrap loader. Note that not all MSPM0Cxx devices have the bootstrap loader. See the device-specific data sheet to determine if the bootstrap loader is present. The ROM is only available during the initial device boot process.

## 1.3.2 SRAM Region

The SRAM region contains the system memory (SRAM). The SRAM supports zero wait state access at the maximum MCLK frequency (24 MHz). Accesses to the SRAM from the CPU are processed through the AHB bus matrix to the SRAM interface directly. The SRAM region supports devices with up to 1MB of SRAM. See the device-specific data sheet for the amount of SRAM present on a given device.

## **Aliased Subregions**

The physical SRAM on a device is aliased into multiple address subregions in the overall SRAM region, as shown in the following table. The default, parity checked, and unchecked address subregions all map to the same physical SRAM memory. The difference between each aliased subregion is in the type of integrity checks which are applied to the access. For example, writing data to address 0x2000.0000 (the default subregion) will cause the same data to appear at address 0x2020.0000 (the unchecked subregion).

Table 1-2. SRAM Region Memory Map

| Table 1-2. SRAW Region Memory Map |             |             |                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-----------------------------------|-------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Subregion                         | Start       | End         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Default                           | 0x2000.0000 | 0x200F.FFFF | The highest available integrity check on the device is always applied to accesses in this subregion:  If the device supports ECC, this subregion is ECC checked.  If the device only supports parity (no ECC), this subregion is parity checked and accesses are equivalent to accesses to the parity checked subregion.  If the device does not support ECC or parity, no checks are applied to accesses in this subregion and the region is |  |  |

|                                   |             |             | equivalent to the unchecked subregion. This applies for all the MSPM0C devices since no ECC or parity supported in MSPM0C series.                                                                                                                                                                                                                                                                                                             |  |  |

Table 1-2. SRAM Region Memory Map (continued)

| Subregion | Start       | End         | Description                                                        |

|-----------|-------------|-------------|--------------------------------------------------------------------|

| Unchecked | 0x2020.0000 | 0x202F.FFFF | No ECC or parity checks are applied to accesses in this subregion. |

#### 1.3.3 Peripheral Region

The peripheral region contains the memory-mapped peripherals on the three peripheral buses. The flash memory is also aliased in the peripheral region.

Table 1-3. Peripheral Region Memory Map

| Туре                 | Start       | End         | Description                                                    |

|----------------------|-------------|-------------|----------------------------------------------------------------|

| Peripherals          | 0x4000.0000 | 0x40FF.FFFF | Memory-mapped registers of peripherals on the peripheral buses |

| Aliased flash memory | 0x4100.0000 | 0x41FF.FFFF | See Section 5.2.3.1                                            |

#### 1.3.4 Subsystem Region

The subsystem region contains memory-mapped registers which are specific to the CPU subsystem and do not need to be accessed globally. See the CPU subsystem chapter for the memory-mapped registers in the subsystem region.

## 1.3.5 System PPB Region

The system PPB region contains memory-mapped registers on the Arm private peripheral bus. These registers are tightly coupled to the CPU and are the interface for peripherals such as the memory protection unit (MPU), and CPU power management and reset functions.

## 1.4 Boot Configuration

After a BOOTRST, the device executes the start-up boot routines to configure the device for operation before starting the main application. Boot routines are executed from read-only memory (ROM) before the main application is started. There are two boot routines: the boot configuration routine (BCR). The boot configuration routine sets up the device security policies, configures the device for operation, and optionally starts the BSL if it presents.

After the start-up routines have successfully completed execution, the CPU is reset and the application is started by unconditionally fetching the stack pointer (SP) and reset vector from 0x0000.0000 and 0x0000.0004 of the flash memory. To enable secure boot, this single point of entry into the application code is enforced by the boot sequence. It is not possible to boot into a different memory location.

#### 1.4.1 Configuration Memory (NONMAIN)

The NONMAIN is a dedicated region of flash memory which stores the configuration data used by the BCR and BSL to boot the device. The region is not used for any other purpose. The BCR has configuration policies which can be left at their default values (as is typical during development and evaluation), or modified for specific purposes (as is typical during production programming) by altering the values programmed into the NONMAIN flash region.

The BCR configuration data structures are both contained within a single flash sector in the NONMAIN flash memory region. To change any parameter in the boot configuration, it is necessary to erase the entire NONMAIN sector and re-program both the BCR configuration structures with the desired settings.

The configuration data in the NONMAIN flash region is not affected by a mass erase command, but it is erased and re-programmed to factory defaults by a factory reset command sent to the BCR via the debug sub system mailbox (DSSM) over SWD.

The address ranges for the NONMAIN data structures are given in Table 1-4. A detailed breakdown of the NONMAIN region is provided at the end of this section.

#### Table 1-4. NONMAIN Region Overview

| NONMAIN Section       | Start Address | End Address |

|-----------------------|---------------|-------------|

| BCR Configuration     | 41C0.0000h    | 41C0.005Bh  |

| BCR Configuration CRC | 41C0.005Ch    | 41C0.005Fh  |

#### 1.4.1.1 CRC-Backed Configuration Data

The BCR configuration data for TI factory trim in the NONMAIN memory includes a CRC32 value corresponding to the CRC32 digest of the respective structure. During the device boot process, the BCR will compute the CRC digest of the data structures and compare it with the stored CRC values before the data contained within the structures is trusted for use.

#### TI Factory Trim Data CRC Fail Handling

If the TI factory trim fails its CRC check during boot, a catastrophic boot error will also result with the following limitations:

- The error cause will be logged in the CFG-AP as a boot diagnostic

- · The user application is not started

- No application debug access is enabled

- · A pending TI failure analysis flow entry, if enabled, is honored

- The boot process will re-attempt up to 3 times

- If the 2nd or 3rd attempt pass, the device boots normally

- If the 3rd attempt does not pass, no further boot attempts are made until the next BOR or POR

#### 1.4.1.2 16-bit Pattern Match for Critical Fields

Critical policies in the BCR configuration memory, such as the SWD security policies, are implemented as 16-bit pattern-match fields in the NONMAIN memory, with the following characteristics:

- An exact pattern match is required to enable lower security states

- Any value in the 16-bit field not matching the exact defined patterns results in a maximally secure state for the respective parameter

This behavior prevents single bit flips from causing the device to enter a lower security state than that which was originally specified.

#### 1.4.2 Boot Configuration Routine (BCR)

The boot configuration routine is the first firmware to run on the device after a BOOTRST. The BCR manages the following at boot time:

- Configuring the debug interface security policy

- Optionally executing a mass erase

- Optionally executing a factory reset

- Configuring the flash memory static write protection policy

#### 1.4.2.1 Serial Wire Debug Related Policies

The serial wire debug related policies configure the functionality which is available through the device's physical debug interface (SWD). By default, MSPM0 devices come from TI in an unrestricted state. This state allows for easy production programming, evaluation, and development. However, this unrestricted state is not recommended for mass production, as it leaves a large attack surface present. To accommodate a variety of needs while keeping the configuration process simple, MSPM0 devices support three generic security levels: no restrictions (Level 0), custom restrictions (Level 1), and fully restricted (Level 2). Table 1-5 shows the three generic security levels, from least restrictive to most restrictive.

There are 2 main uses of the SWD interface for which protection needs to be considered:

Application debug access, which includes:

- Full access to the processor, memory map, and peripherals through the AHB-AP

- Access to the device EnergyTrace+ state information through the ET-AP

- Access to the device power state controls for debug through the PWR-AP

- · Factory reset access, which includes:

- Ability to send a command through SWD to erase the MAIN memory region and reset the NONMAIN device configuration memory to TI factory defaults (Level 0)

| Table 1- | 5. Gener | ic Security | Levels |

|----------|----------|-------------|--------|

|----------|----------|-------------|--------|

| Level | Scenario            | SW-DP Policy | App Debug<br>Policy | Mass Erase<br>Policy | Factory Reset<br>Policy | TI FA Policy             |

|-------|---------------------|--------------|---------------------|----------------------|-------------------------|--------------------------|

| 0     | No restrictions     | EN           | EN                  | DIS                  | EN                      | DIS                      |

| 1     | Custom restrictions | EN           | EN, DIS             | DIS                  | EN, DIS                 | DIS                      |

| 2     | Fully restricted    | DIS          | Don't care          | (access not poss     | ible with SW-DP d       | lisabled) <sup>(1)</sup> |

<sup>(1)</sup> When the SW-DP policy is SW-DP disabled, the mass erase and factory reset policies are a don't care from the point of view of the SWD interface.

#### 1.4.2.1.1 SWD Security Level 0

SWD security level 0 is the least restrictive SWD security state. This is the default state of a new device from TI, and it is also the state of a device following a successful factory reset. There are no restrictions on application debug access, mass erase, factory reset, for failure analysis in this state.

#### When to Use This State

Level 0 is well suited for prototyping and development, as it allows programming of the device memory and debug of the processor and peripherals.

#### When to Not Use this State

Level 0 should not be used in mass production. An attacker would have full freedom to read the contents of the device memory, manipulate the execution of the device, and possibly change the flash memory contents (depending on the flash memory write protection scheme).

## 1.4.2.1.2 SWD Security Level 1

SWD security level 1 allows for a customized security configuration. The physical debug port (SW-DP) is left enabled, and each function (application debug, mass erase command, factory reset command, and TI failure analysis) may be individually enabled, disabled, or (in some cases) enabled through password authentication, providing considerable flexibility to tailor the device behavior to specific use-cases.

#### When to Use This State

Level 1 is well suited for restricted prototyping/development scenarios and for mass production scenarios where the desire is to retain certain SWD functions (such as factory reset and TI failure analysis) while disabling other functions (such as application debug). Common examples of Level 1 customized configurations are given in Table 1-6.

Table 1-6. Examples of Level 1 Configurations

|                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Configuration |            |                  |       |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------|------------------|-------|--|

| Level 1 Scenario                                                                                                                                                                                                                                                                                                                                                                                                                                     | App Debug     | Mass Erase | Factory<br>Reset | TI FA |  |

| This scenario restricts debug access with a user-specified password, but it leaves the factory reset and TI failure analysis available. This configuration allows field debug (with password), and it also allows the device to be brought back to the default "Level 0" state through factory reset.                                                                                                                                                | EN with PW    | DIS        | EN               | EN    |  |

| This scenario does not allow debug. It does allow factory reset, but only with a user-specified password. This provides a way to open up a device in the field by clearing the MAIN memory contents and bringing the device back to a "Level 0" state if the password is known. Importantly, even if the factory reset password were compromised, it would not be possible for an attacker to read proprietary information in the MAIN flash memory. | DIS           | DIS        | EN with PW       | EN    |  |

Table 1-6. Examples of Level 1 Configurations (continued)

|                                                                                                                                                                                                                                                                                                |           | Configuration |                  |       |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------|------------------|-------|--|

| Level 1 Scenario                                                                                                                                                                                                                                                                               | App Debug | Mass Erase    | Factory<br>Reset | TI FA |  |

| This scenario does not allow debug and it does not allow TI failure analysis. This prevents TI from performing a factory reset and further FA activities on the device, unless the user executes a factory reset with their user-specified password before returning the devices to TI for FA. | DIS       | DIS           | EN with PW       | DIS   |  |

#### Note

Level 1 is the recommended configuration for most standard production use-cases. For applications which do not require secure boot, TI recommends using Level 1 in production with factory reset left enabled (with password) and TI failure analysis left enabled. In such a configuration, the device may be recovered to a less restrictive state after provisioning either by the user (with password) or by TI (through the failure analysis return flow). In use-cases requiring maximum secure boot assurance, a more restrictive Level 1 or Level 2 may be used for production, with the trade-off that devices may not be recoverable to a less restrictive state once provisioned.

#### When to Not Use this State

Level 1 should not be used during prototyping if complete access to the device is desired; in such a case, Level 0 should be used instead.

Level 1 should also not be used in a mass production scenario where a maximally restrictive state is desired and no SWD functions are to be enabled; in such a case, Level 2 should be used instead as it directly disables the complete SWD physical interface and minimizes the possibility of misconfiguration.

#### Note

If a device is configured with application debug and factory reset disabled, the only way for a user to restore debug access to the device is if the user application code provides a mechanism to change the NONMAIN configuration to a less restrictive state. If the NONMAIN is locked through static write protection then the state is not reversible and there is no way for a user to re-gain debug access.

#### 1.4.2.1.3 SWD Security Level 2

SWD security level 2 configures the device in a maximally restrictive state. The physical debug port (SW-DP) is completely disabled, and all of the SWD-accessible functions (application debug, mass erase, factory reset, and TI failure analysis) are not accessible through SWD, regardless of their individual configuration.

When level 2 is selected (SW-DP disabled), the application debug configuration and TI failure analysis configuration fields are don't care fields which do not impact the device configuration.

If the BSL is disabled, then the mass erase and factory reset configuration fields are also don't care fields. However, if the BSL is enabled, then the mass erase and factory reset configuration fields are still used by the BSL to authorize mass erase or factory reset commands originating from the BSL interface.

#### When to Use This State

Use Level 2 only for mass production when no further access to any SWD functions is required and a maximally secure state is desired for the device.

#### When to Not Use this State

Do not use Level 2 in the following cases:

- Future application debug or reprogramming through SWD is required

- So that TI can perform failure analysis on the device

- To remove proprietary information from the flash memory by sending a mass erase or factory reset command through SWD

#### Note

After a device is configured for level 2 (SW-DP disabled), further access to the device through SWD **is not possible**. The only way to bring a device back to a level 0 or level 1 state with SWD access restored is if a mechanism in the user application code is included which can change the NONMAIN configuration to a less restrictive state. If the NONMAIN is locked through static write protection then the level 2 state is not reversible and there is no way to re-gain SWD access.

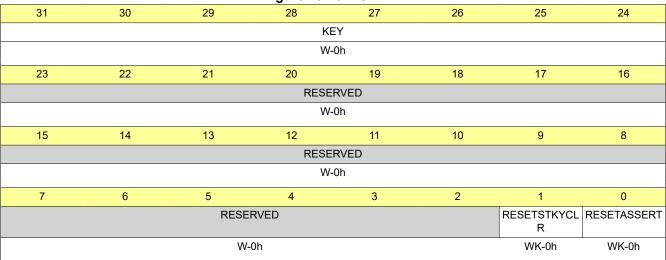

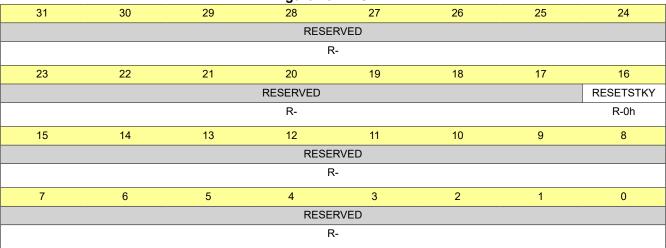

#### 1.4.2.2 SWD Factory Reset Commands

The BCR provides mass erase and factory reset functionality through commands sent to the device over SWD from a debug probe using the debug subsystem mailbox (DSSM). These commands are not available in SWD security level 2, but they are optionally available in security level 0 and 1. When the device is not configured for SWD security level 2, the factory reset command can be individually configured to be enabled, enabled with a unique 128-bit password, or disabled. By default, both commands are enabled.

The SWD factory reset DSSM commandsuperseded any static write protection policies. For example, if SWD factory reset is configured to be enabled or enabled, the BCR configuration data can be reset even if it is statically write protected.

## **SWD Factory Reset**

A SWD factory reset is an erase of the MAIN flash regions followed by a reset of the NONMAIN flash region to default values. Such an erase is useful for completely resetting the BCR and BSL device boot policies while also erasing the application code and data.

To set the factory reset command mode, configure the BOOTCFG3.FACTORYRESETCMDACCESS fieldfieldin the NONMAIN memory.

## 1.4.2.3 Flash Memory Protection and Integrity Related Policies

The flash memory protection and integrity policies specify which sectors of flash memory are locked from modification, as well as which sectors are to be checked for integrity during the boot process before the user application is started.

## 1.4.2.3.1 Locking the Application (MAIN) Flash Memory

MSPM0 MCUs implement a static write protection scheme to lock out user defined sectors in the MAIN flash region from any program or erase operations at runtime. The desired static write protection scheme is configured as a part of the boot security policies in the NONMAIN flash region.

#### **Purpose**

Static write protection enables placement of a fixed, user-defined, application in the flash memory that has the following characteristics:

- Once programmed and locked, the application is not modifiable by the application code or ROM bootloader

- If placed at the beginning of the flash memory, the application is the first code that executes when the ROM boot configuration routine transfers execution to the user application

MSPM0 static write protection supports both characteristics, which must be satisfied to implement a secure boot image manager.

#### **Capabilities**

Any sector that is configured in the NONMAIN to be write-locked is functionally immutable when the boot configuration routine transfers execution to either the bootstrap loader or the user application code in MAIN flash. Any attempt to program or erase a statically protected sector by the application code or the bootstrap loader results in a hardware flash operation error, and the sector is not modified.

While static write protection prevents any modification by application code or the bootloader, a mass erase or factory reset command sent through the SWD interface is honored. If this behavior is not desired, the factory reset SWD commandcan be protected or disabled(see the SWD policies). To completely remove any means

of modifying statically write protected MAIN flash sectors, the mass erase and factory reset command (or the SW-DP) must be disabled, and the NONMAIN boot configuration memory must also be statically write protected to prevent application code from changing the underling write protection scheme by modifying the contents NONMAIN region. This is discussed in the following section.

#### 1.4.2.3.2 Locking the Configuration (NONMAIN) Flash Memory

MSPM0 MCUs implement a static write protection scheme to lock out the NONMAIN flash region from any program/erase operations at runtime. The write protection scheme is configured as a part of the boot security policies in the NONMAIN flash region.

#### **Purpose**

By default from TI, the NONMAIN configuration memory (which contains the user-specified boot security policies and bootstrap loader policies) is not write protected. This enables the NONMAIN to be erased by the user during provisioning and re-programmed with the user-specified policies which will be used in mass production.

In many cases, it is desirable for the configuration memory to be locked once it has been provisioned. Locking the configuration memory has the benefit of preventing any unauthorized modification of the security policies, bootstrap loader policies, and static write protection policies by either the bootstrap loader or the application code itself. In most applications, devices in mass production do not require modification of the configuration memory, even when the device firmware is updated.

#### Capabilities

When configured to be protected, the entire NONMAIN region will be write-locked and will be functionally immutable when the boot configuration routine transfers execution to either the bootstrap loader or the user application code in MAIN flash. Any attempt to program or erase the NONMAIN by the application code or the bootstrap loader will result in a hardware flash operation error, and the sector will not be modified.

While static write protection prevents any modification by application code or the boot loader, a factory reset command sent through the SWD interface would still be honored. If this behavior is not desired, the factory reset SWD command may be protected or disabled altogether (see the SWD policies). To completely remove any means of modifying the NONMAIN configuration memory, the factory reset command and TI FA (or the SW-DP) must be disabled.

#### Note

When the NONMAIN is statically write protected, and the factory reset command and TI FA (or the SW-DP) are disabled, the NONMAIN is equivalent to immutable read-only memory, and it is no longer possible to change the device configuration by any means. Further, if any MAIN memory region sectors are configured with static protection, these sectors also can not be modified by any means and may be considered as immutable.

#### 1.4.2.3.3 Static Write Protection NONMAIN Fields

Write protection may be enabled on a per-sector basis for the first 32 sectors of the MAIN flash memory. For the remaining sectors of flash memory, if present, write protection may be enabled per 8 sectors. To set a static write protection policy, configure the FLASHSWP0 and FLASHSWP1 fields in the NONMAIN memory.

#### Note

Mass erase and factory reset commands Factory reset commandsent to the BCR via the debug sub system mailbox (DSSM) will override the specified static write protection policy. If this behavior is not desired, configure the factory reset commandto be enabled with password or disabled.

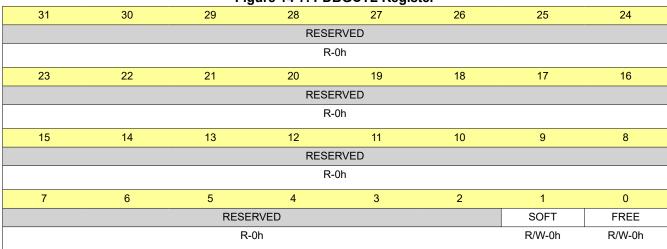

## 1.5 NONMAIN Registers

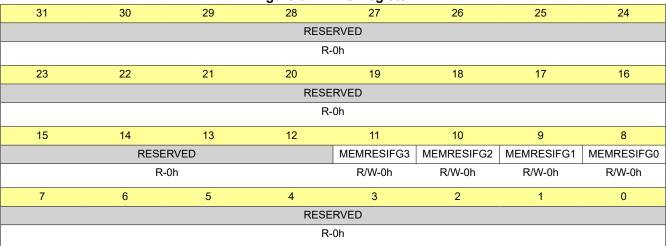

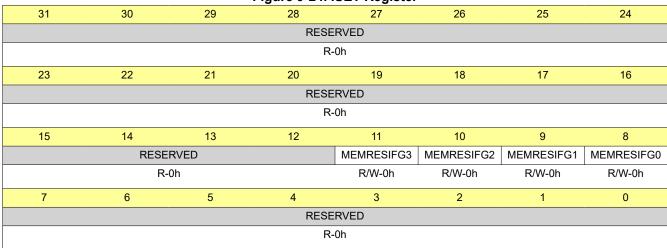

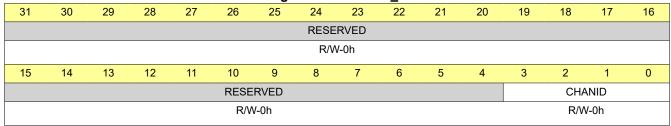

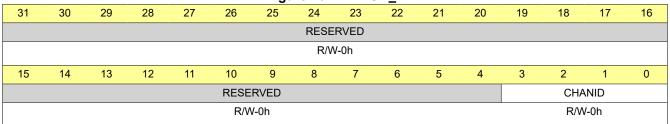

Table 1-7 lists the memory-mapped registers for the NONMAIN registers. All register offset addresses not listed in Table 1-7 should be considered as reserved locations and the register contents should not be modified.

**Table 1-7. NONMAIN Registers**

| Offset    | Acronym     | Register Name                                        | Section       |

|-----------|-------------|------------------------------------------------------|---------------|

| 41C00000h | BCRCONFIGID | Configuration ID of BCR Structure                    | Section 1.5.1 |

| 41C00004h | BOOTCFG0    | Serial wire debug (SWD) lock policy.                 | Section 1.5.2 |

| 41C00008h | BOOTCFG3    | Factory reset mode policies.                         | Section 1.5.3 |

| 41C0000Ch | SWPMAINLOW  | Programs Static write protection of first 32K bytes. | Section 1.5.4 |

| 41C00010h | SWPMAINHIGH | Programs Static write protection of first 32K bytes. | Section 1.5.5 |

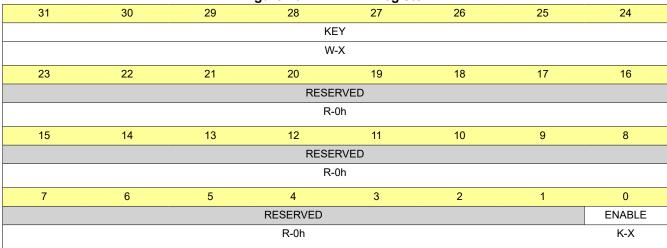

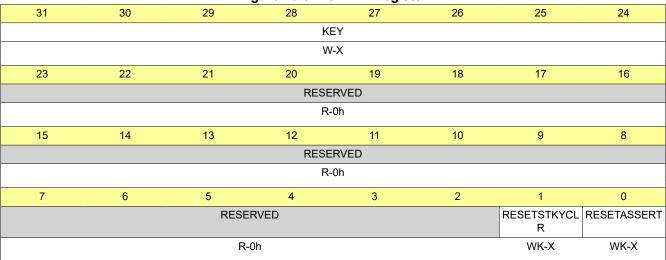

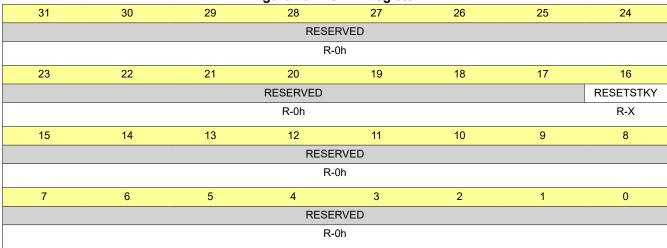

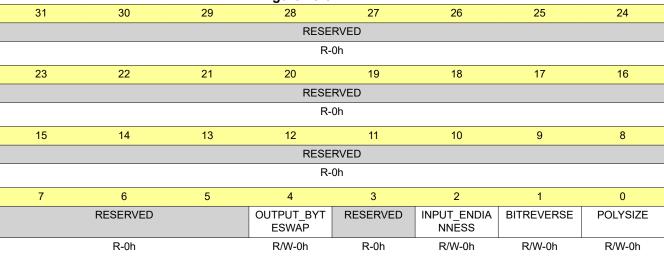

Complex bit access types are encoded to fit into small table cells. Table 1-8 shows the codes that are used for access types in this section.

**Table 1-8. NONMAIN Access Type Codes**

| Access Type            | Code | Description                            |  |  |  |  |  |  |

|------------------------|------|----------------------------------------|--|--|--|--|--|--|

| Read Type              |      |                                        |  |  |  |  |  |  |

| R                      | R    | Read                                   |  |  |  |  |  |  |

| Write Type             |      |                                        |  |  |  |  |  |  |

| W                      | W    | Write                                  |  |  |  |  |  |  |

| Reset or Default Value |      |                                        |  |  |  |  |  |  |

| -n                     |      | Value after reset or the default value |  |  |  |  |  |  |

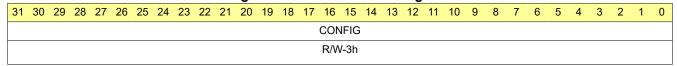

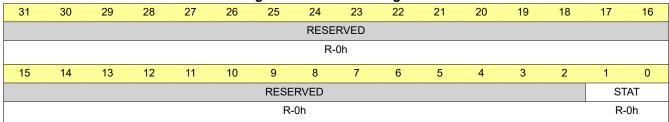

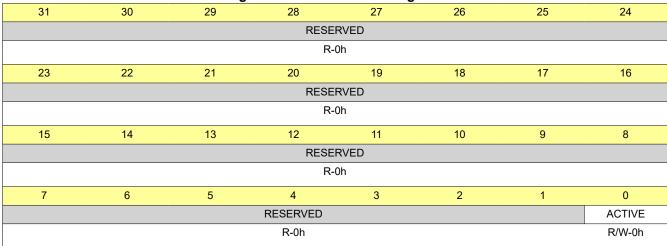

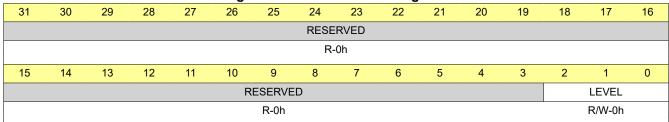

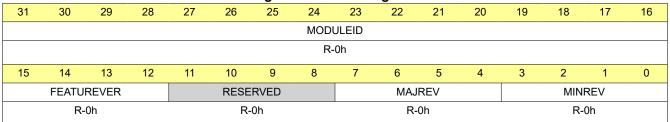

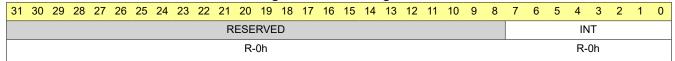

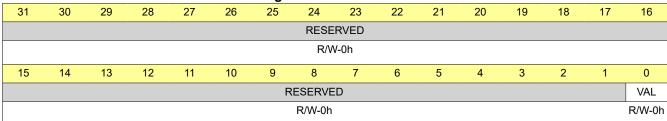

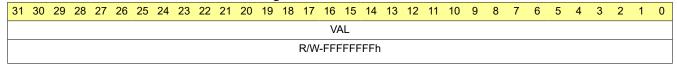

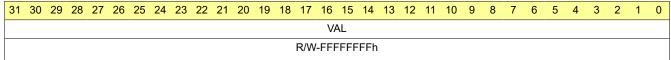

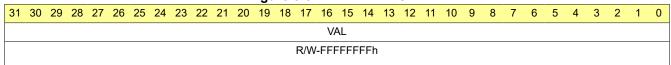

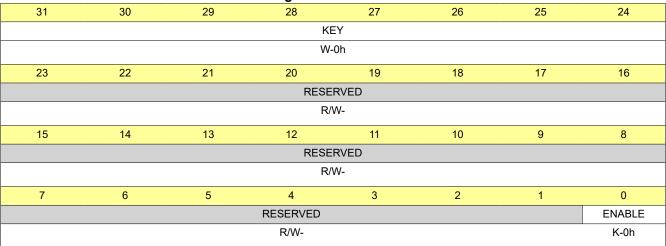

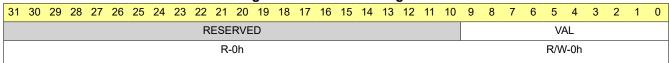

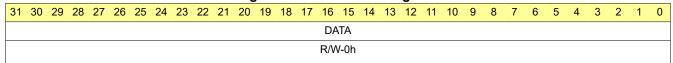

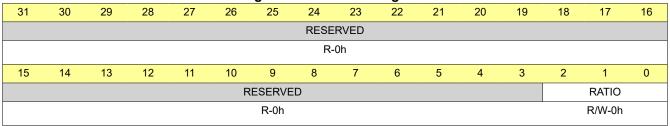

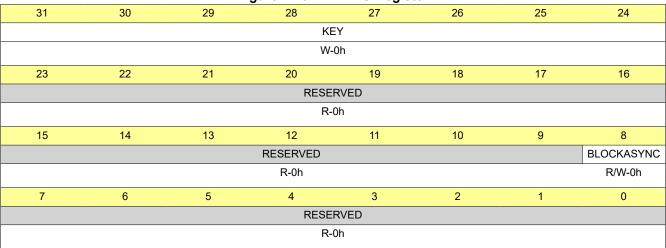

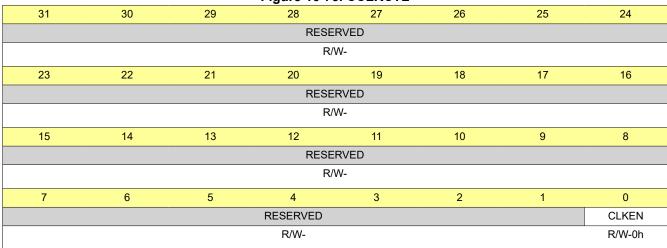

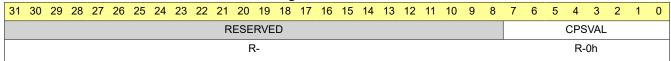

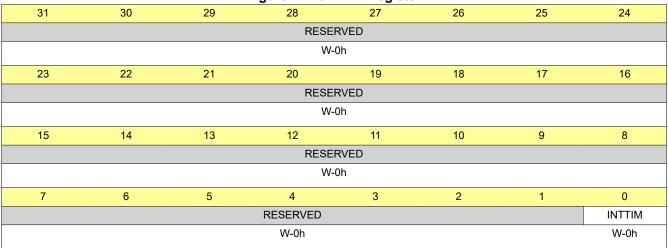

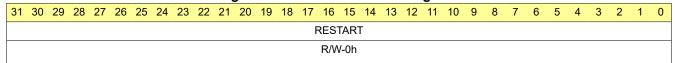

## 1.5.1 BCRCONFIGID Register (Offset = 41C00000h) [Reset = 00000003h]

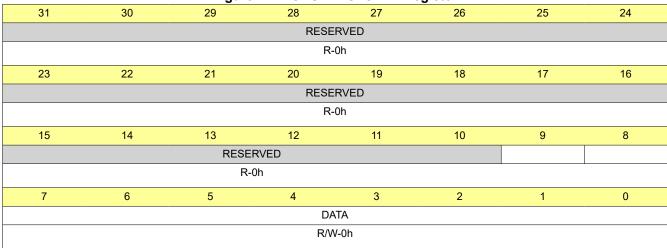

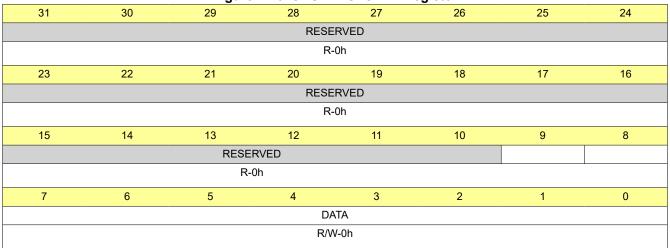

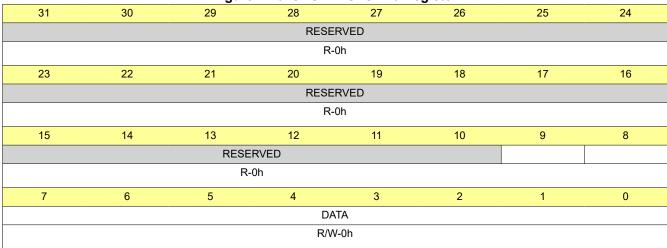

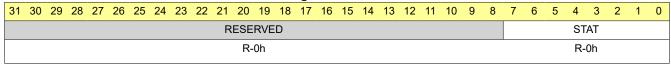

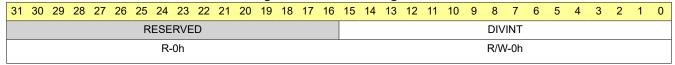

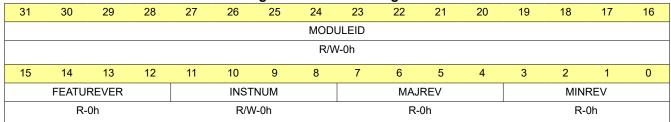

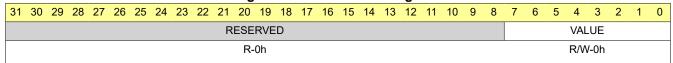

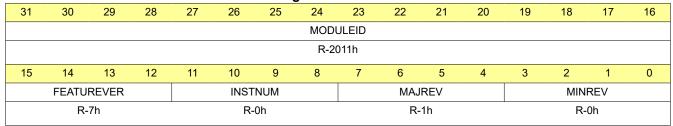

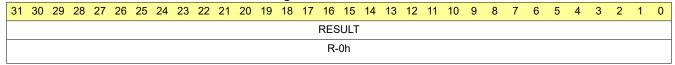

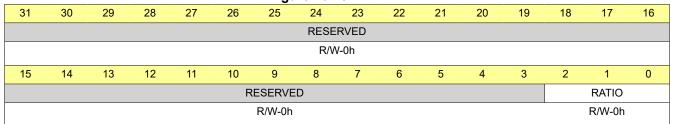

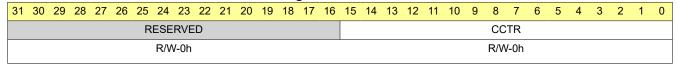

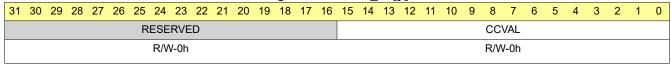

BCRCONFIGID is shown in Figure 1-2 and described in Table 1-9.

Return to the Summary Table.

Configuration ID of BCR Structure

## Figure 1-2. BCRCONFIGID Register

## Table 1-9. BCRCONFIGID Register Field Descriptions

| Bit  | Field  | Туре | Reset | Description                     |

|------|--------|------|-------|---------------------------------|

| 31-0 | CONFIG | R/W  | 3h    | Configuration ID of the BOOTCFG |

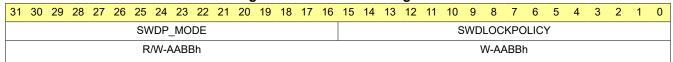

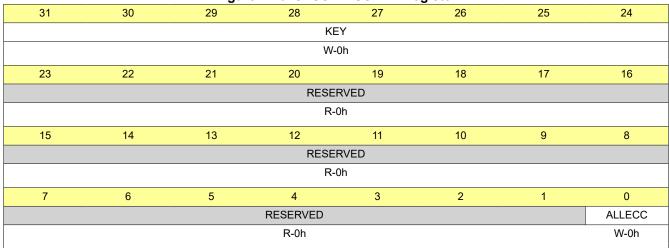

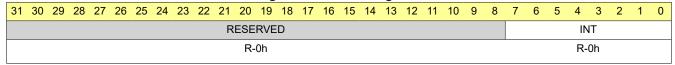

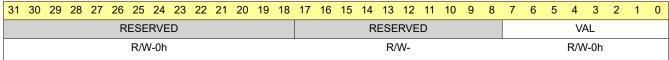

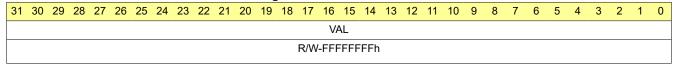

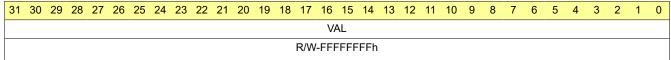

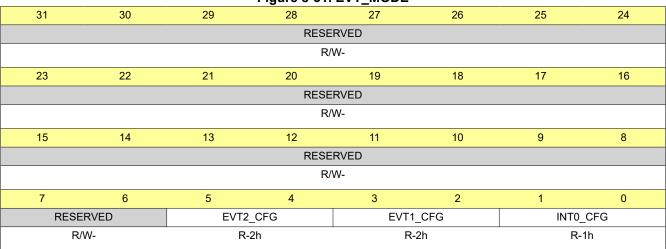

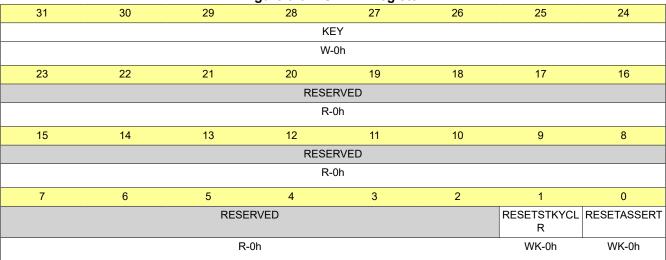

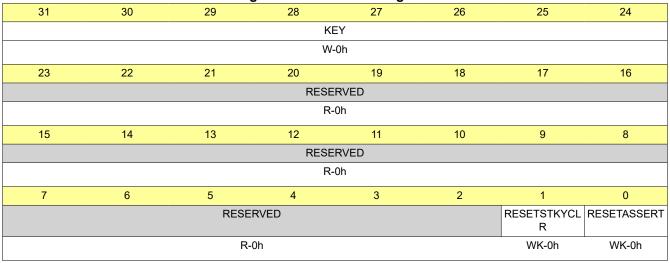

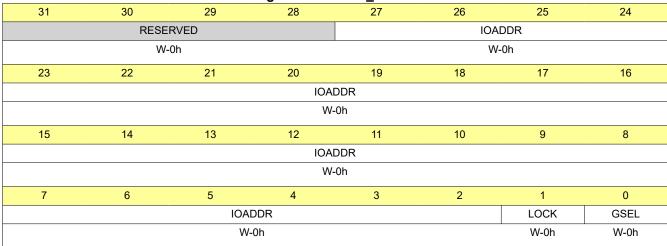

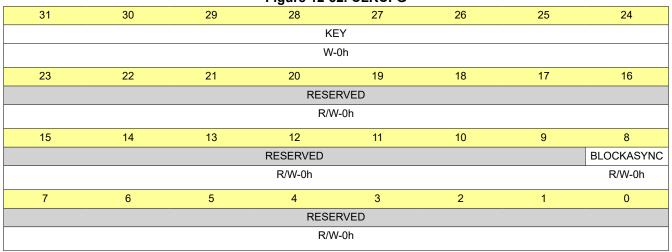

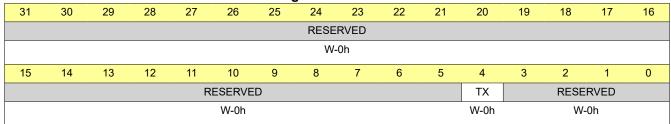

## 1.5.2 BOOTCFG0 Register (Offset = 41C00004h) [Reset = AABBAABBh]

BOOTCFG0 is shown in Figure 1-3 and described in Table 1-10.

Return to the Summary Table.

Serial wire debug (SWD) lock policy.

## Figure 1-3. BOOTCFG0 Register

## Table 1-10. BOOTCFG0 Register Field Descriptions

| Bit   | Field         | Туре | Reset | Description                                                                                                                                                                                                                                                       |

|-------|---------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-16 | SWDP_MODE     | R/W  | AABBh | Used to enable/ disable SWD port access.  AABBh = Enabled; FFFFh = Disabled (all other values).                                                                                                                                                                   |

| 15-0  | SWDLOCKPOLICY | W    | AABBh | The serial wire debug (SWD) lockout may be configured to one of three policies: no restrictions, core debug access, and maximally restrictive.  AABBh = Access to all debug APs via SWD is enabled; FFFFh = SWD access is completely disabled (all other values); |

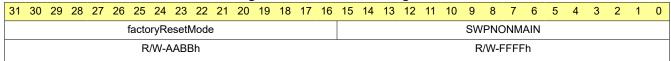

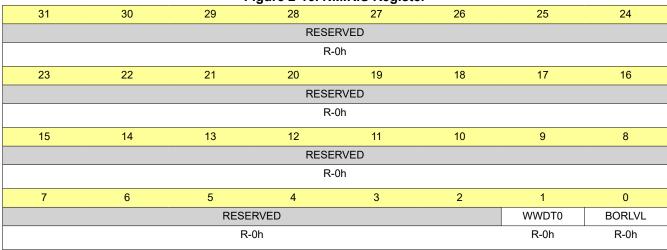

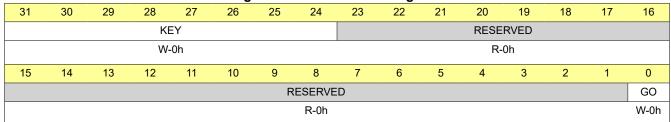

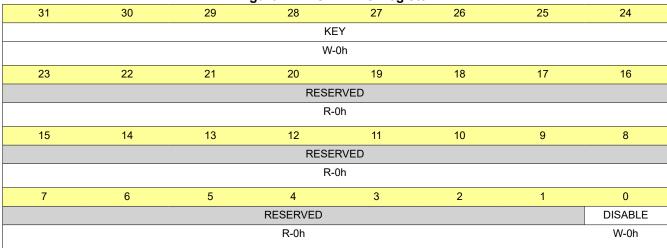

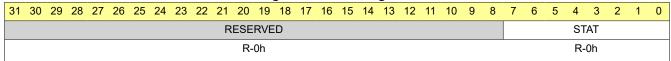

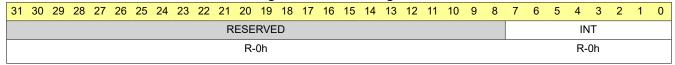

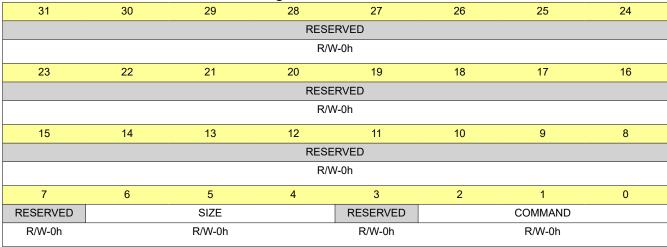

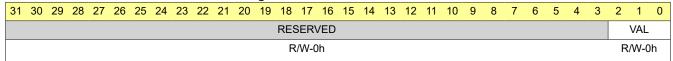

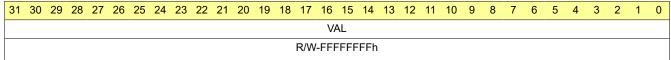

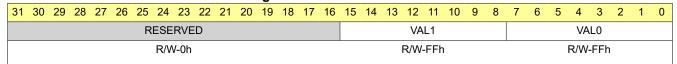

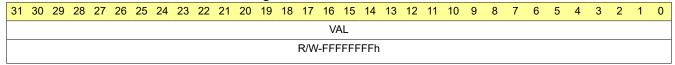

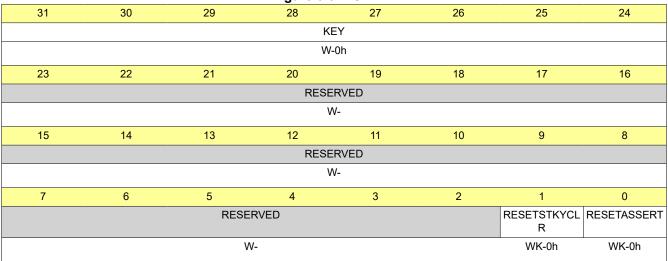

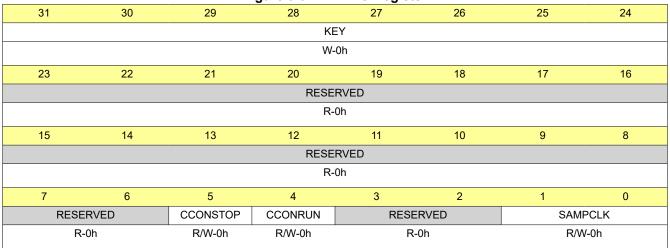

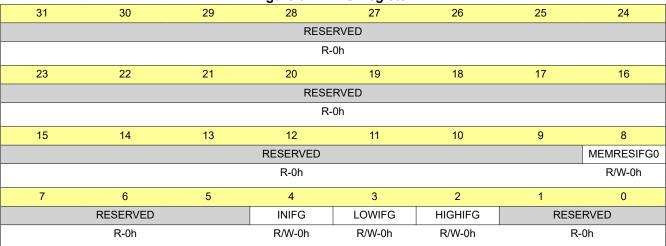

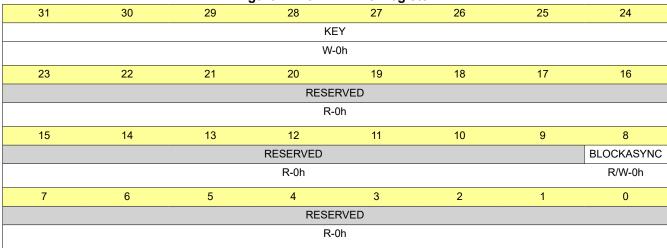

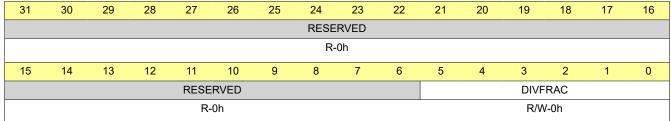

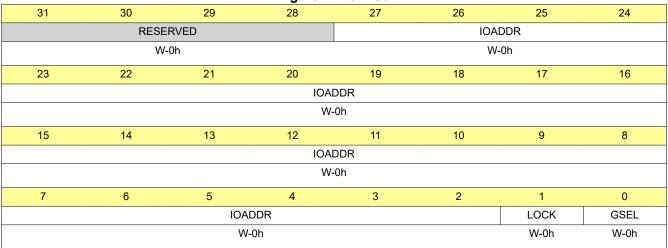

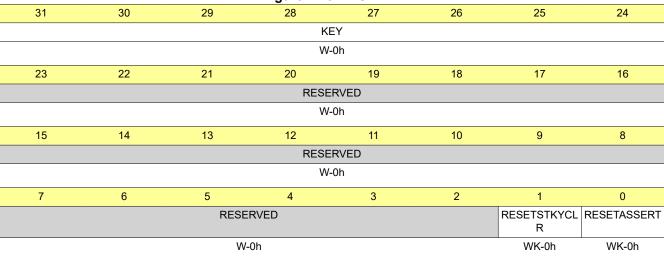

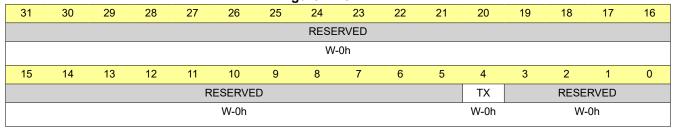

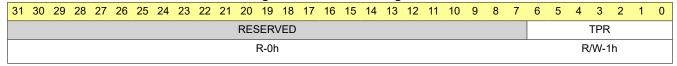

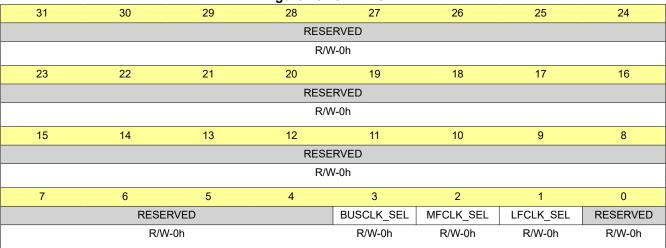

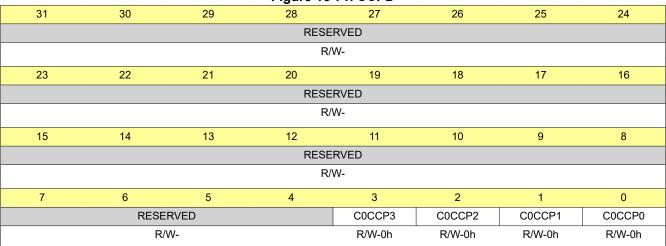

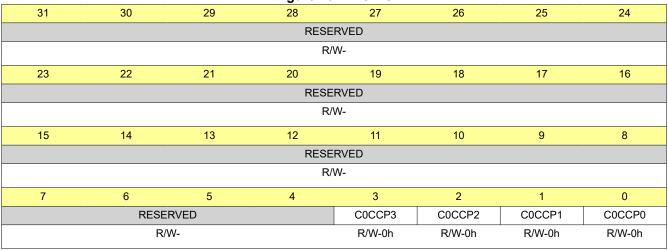

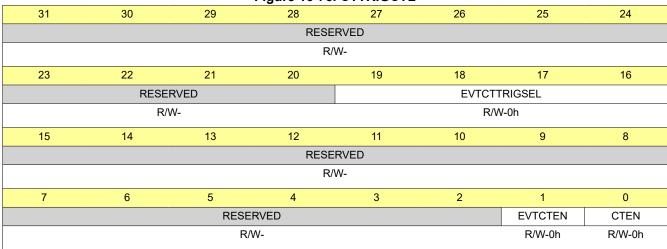

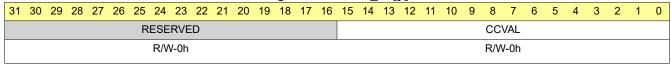

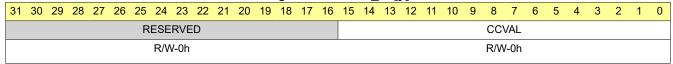

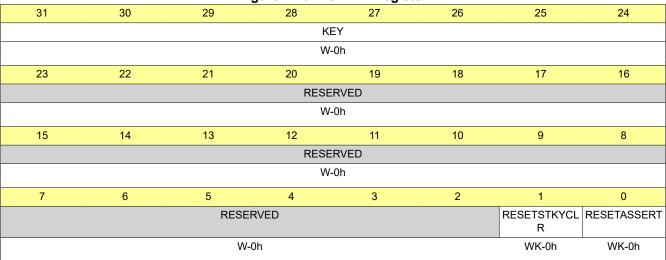

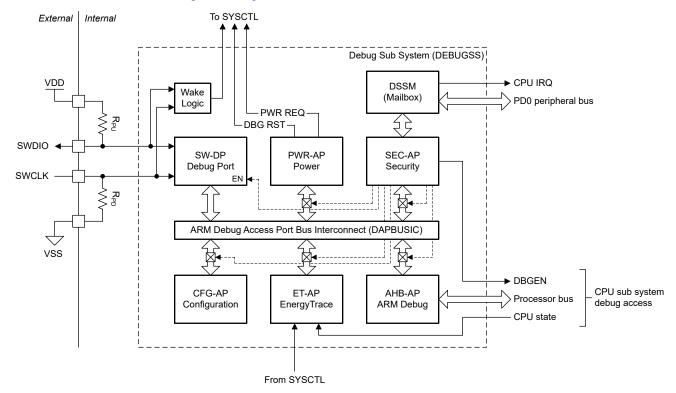

## 1.5.3 BOOTCFG3 Register (Offset = 41C00008h) [Reset = AABBFFFFh]

BOOTCFG3 is shown in Figure 1-4 and described in Table 1-11.

Return to the Summary Table.

Factory reset mode policies.

## Figure 1-4. BOOTCFG3 Register

## Table 1-11. BOOTCFG3 Register Field Descriptions

| Bit   | Field            | Туре | Reset | Description                                                                                                               |

|-------|------------------|------|-------|---------------------------------------------------------------------------------------------------------------------------|

| 31-16 | factoryResetMode | R/W  | AABBh | AABBh = Enabled;<br>FFFFh = Disabled (all other values).                                                                  |

| 15-0  | SWPNONMAIN       | R/W  | FFFFh | Static Write Protection configuration for Non-Main. Only one LSB used (Setting bit to 0 disables write, 1 enables write). |

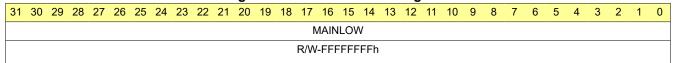

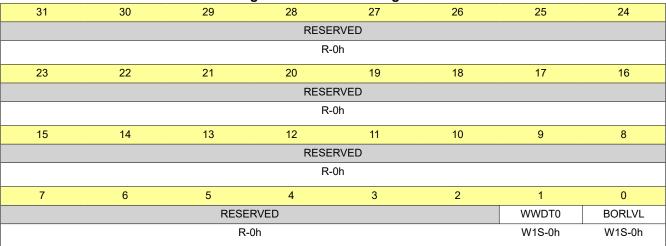

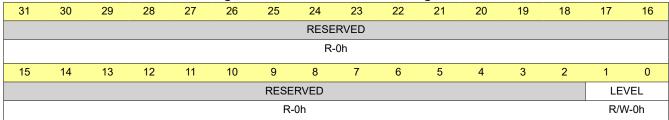

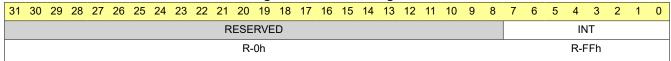

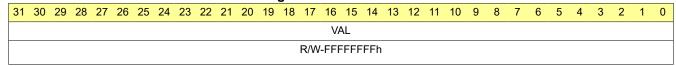

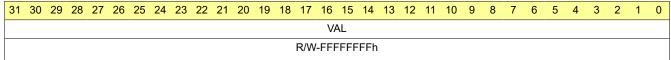

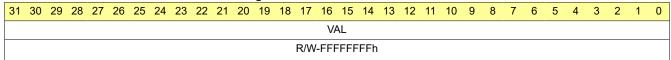

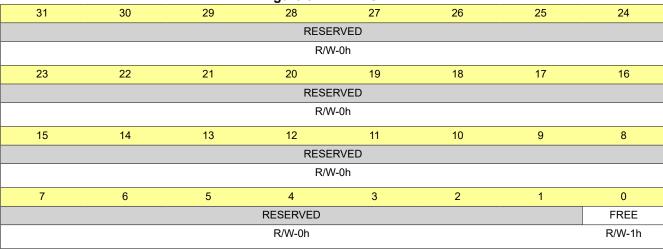

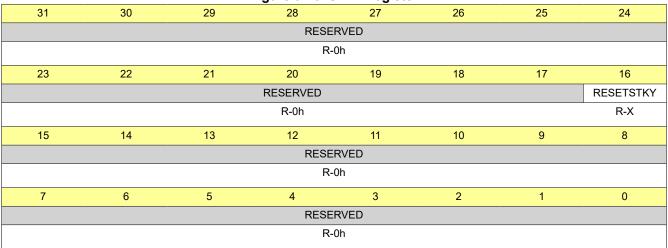

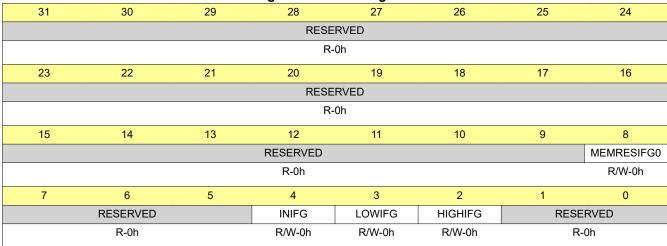

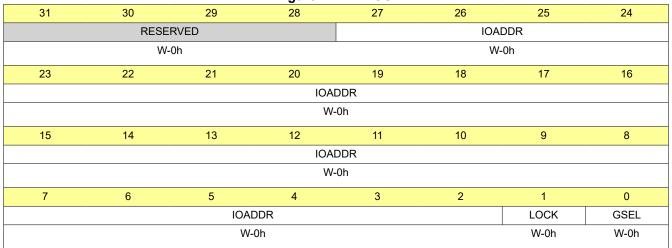

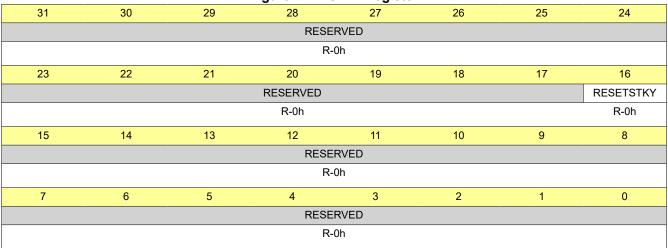

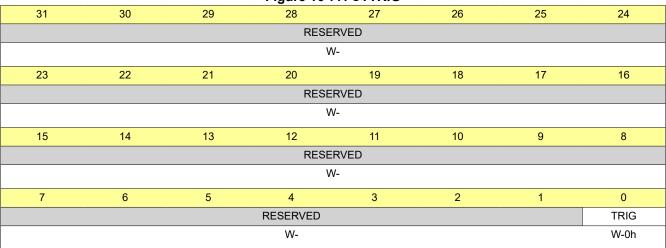

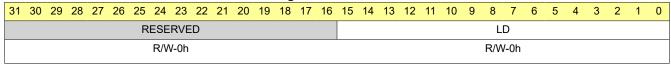

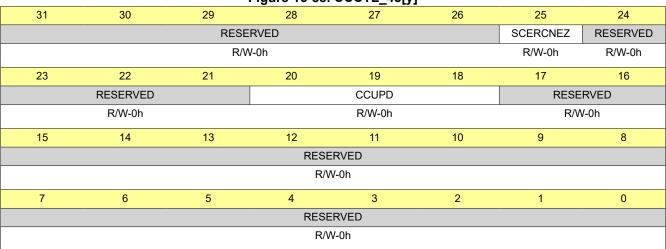

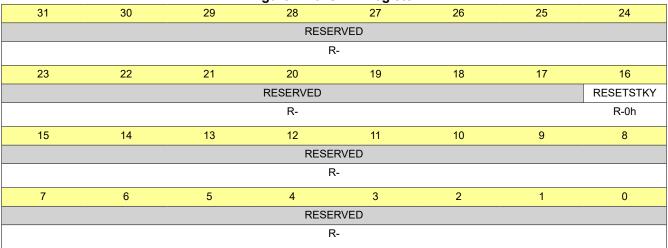

## 1.5.4 SWPMAINLOW Register (Offset = 41C0000Ch) [Reset = FFFFFFFh]

SWPMAINLOW is shown in Figure 1-5 and described in Table 1-12.

Return to the Summary Table.

Programs Static write protection of first 32K bytes.

## Figure 1-5. SWPMAINLOW Register

## **Table 1-12. SWPMAINLOW Register Field Descriptions**

| Bit  | Field   | Туре | Reset    | Description                                                            |

|------|---------|------|----------|------------------------------------------------------------------------|

| 31-0 | MAINLOW | R/W  | FFFFFFFh | 1 bit per sector (Setting a bit to 0 disables write, 1 enables write). |

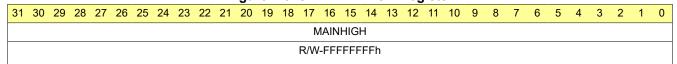

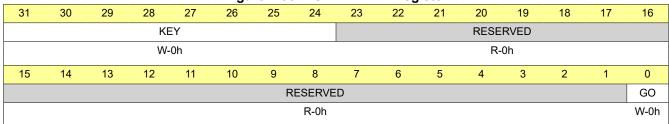

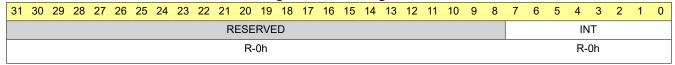

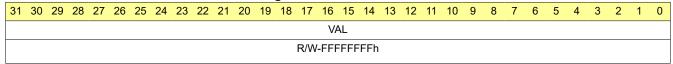

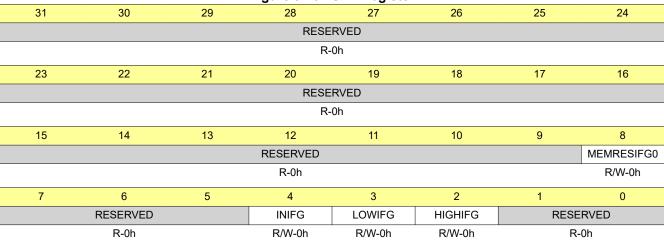

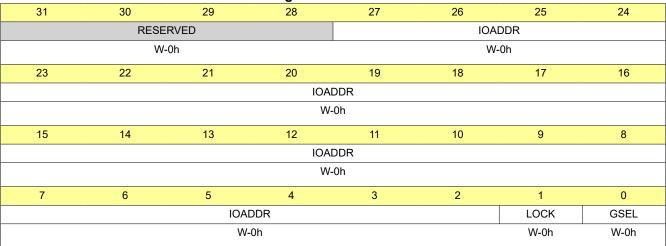

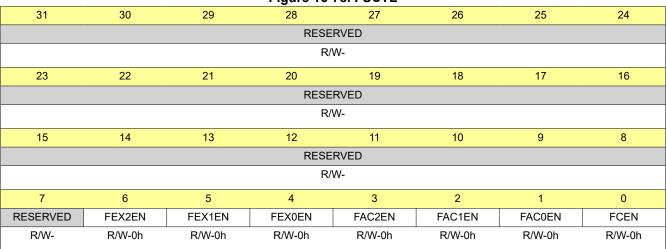

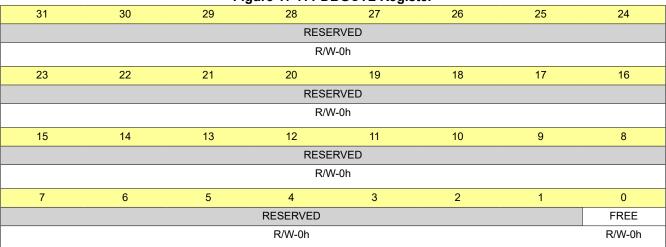

## 1.5.5 SWPMAINHIGH Register (Offset = 41C00010h) [Reset = FFFFFFFh]

SWPMAINHIGH is shown in Figure 1-6 and described in Table 1-13.

Return to the Summary Table.

Programs Static write protection of first 32K bytes.

## Figure 1-6. SWPMAINHIGH Register

## Table 1-13. SWPMAINHIGH Register Field Descriptions

| Bit  | Field    | Туре | Reset | Description                                                                                                        |

|------|----------|------|-------|--------------------------------------------------------------------------------------------------------------------|

| 31-0 | MAINHIGH | R/W  |       | 1 bit per 8 sectors. Bits 3:0, not used as covered with above.(Setting a bit to 0 disables write, 1 enables write) |

## **1.6 Factory Constants**

All devices include a memory-mapped FACTORY region which provides read-only data describing the capabilities of a device as well as any factory-provided trim information for use by application software.

Key data provided in the FACTORY memory region includes:

- The device unique 96-bit identity

- The total MAIN region flash memory size (in KB)

- The total DATA region flash memory size (in KB), if present

- · The flash bank count

- The total SRAM memory size (in KB)

- The temperature sensor calibration value

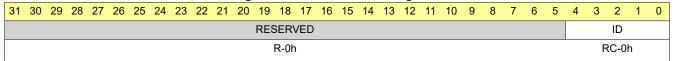

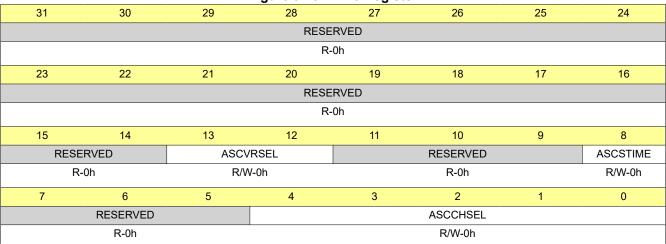

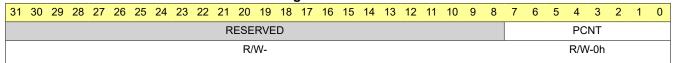

## 1.6.1 FACTORYREGION Registers

Table 1-14 lists the memory-mapped registers for the FACTORYREGION registers. All register offset addresses not listed in Table 1-14 should be considered as reserved locations and the register contents should not be modified.

**Table 1-14. FACTORYREGION Registers**

| Offset    | Acronym     | Register Name                                                                                                              | Section         |

|-----------|-------------|----------------------------------------------------------------------------------------------------------------------------|-----------------|

| 41C40000h | TRACEID     | Trace identifier                                                                                                           | Section 1.6.1.1 |

| 41C40004h | DEVICEID    | Device identifier                                                                                                          | Section 1.6.1.2 |

| 41C40008h | USERID      | Device variant identifier                                                                                                  | Section 1.6.1.3 |

| 41C40018h | SRAMFLASH   | The encoding of memory size and flash bank number                                                                          | Section 1.6.1.4 |

| 41C4003Ch | TEMP_SENSE0 | Temperature sensor room temperature calibration code. This is ADC conversion results of temperature sensor output voltage. | Section 1.6.1.5 |

Complex bit access types are encoded to fit into small table cells. Table 1-15 shows the codes that are used for access types in this section.

**Table 1-15. FACTORYREGION Access Type Codes**

| Access Type            | Code | Description                            |  |  |  |

|------------------------|------|----------------------------------------|--|--|--|

| Read Type              |      |                                        |  |  |  |

| R                      | R    | Read                                   |  |  |  |

| Reset or Default Value |      |                                        |  |  |  |

| -n                     |      | Value after reset or the default value |  |  |  |

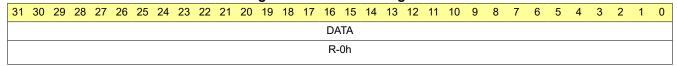

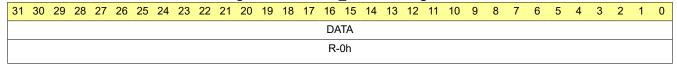

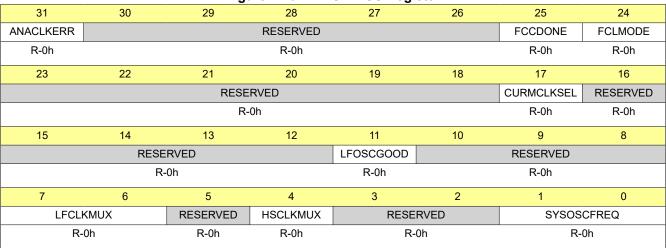

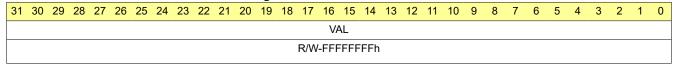

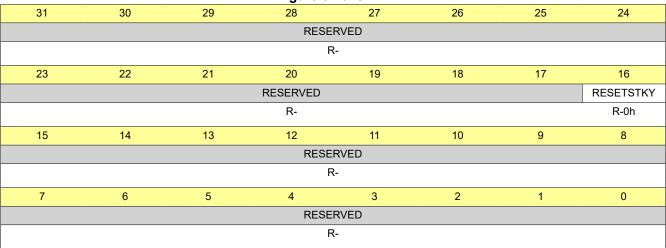

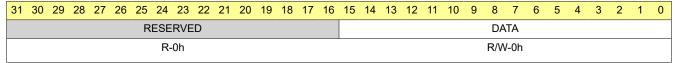

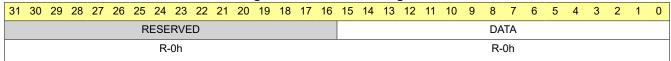

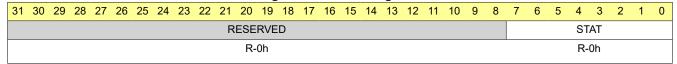

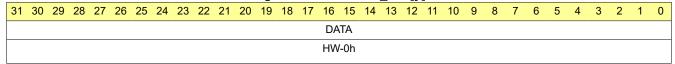

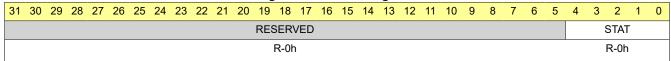

## 1.6.1.1 TRACEID Register (Offset = 41C40000h) [Reset = 00000000h]

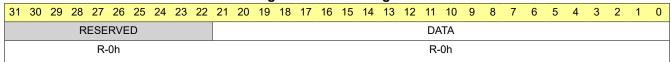

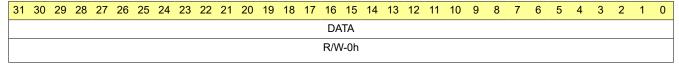

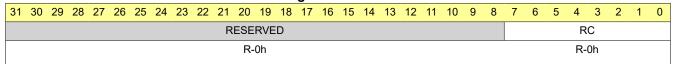

TRACEID is shown in Figure 1-7 and described in Table 1-16.

Return to the Summary Table.

Unique value per device shipped

## Figure 1-7. TRACEID Register

Table 1-16. TRACEID Register Field Descriptions

| Bit  | Field | Туре | Reset | Description |

|------|-------|------|-------|-------------|

| 31-0 | DATA  | R    | 0h    |             |

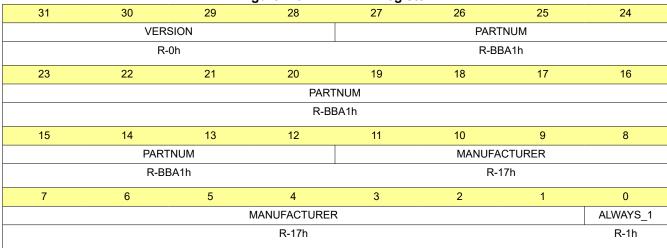

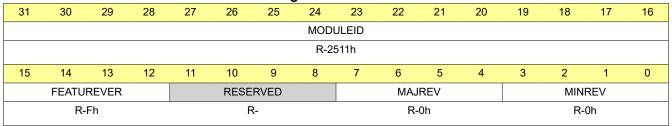

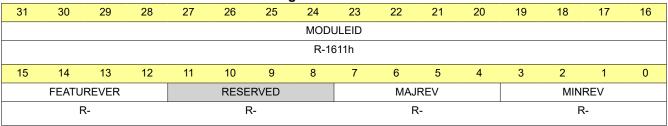

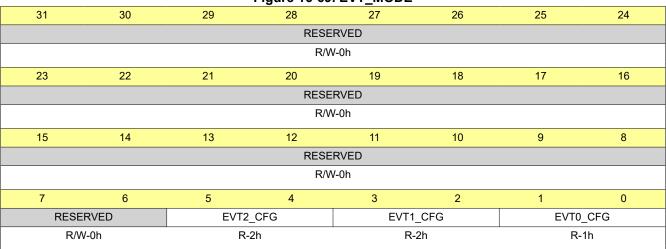

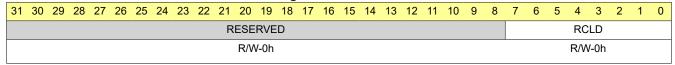

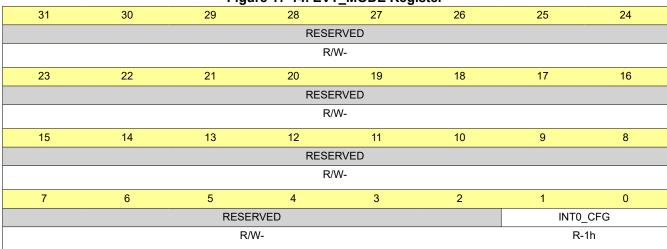

## 1.6.1.2 DEVICEID Register (Offset = 41C40004h) [Reset = 0BBA102Fh]

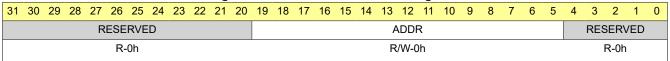

DEVICEID is shown in Figure 1-8 and described in Table 1-17.

Return to the Summary Table.

Device identifier (die revision specific)

## Figure 1-8. DEVICEID Register

## Table 1-17. DEVICEID Register Field Descriptions

|   | Bit   | Field        | Туре | Reset | Description                      |

|---|-------|--------------|------|-------|----------------------------------|

|   | 31-28 | VERSION      | R    | 0h    | Revision of the device           |

|   | 27-12 | PARTNUM      | R    | BBA1h | Part number of the device        |

|   | 11-1  | MANUFACTURER | R    | 17h   | TI's JEDEC bank and company code |

| Ī | 0     | ALWAYS_1     | R    | 1h    | This is always 1                 |

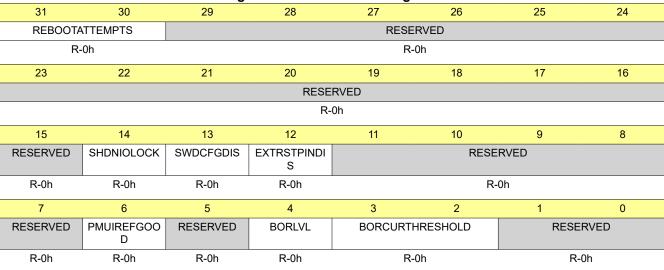

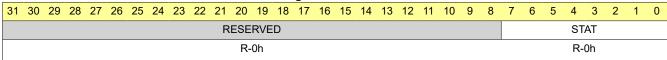

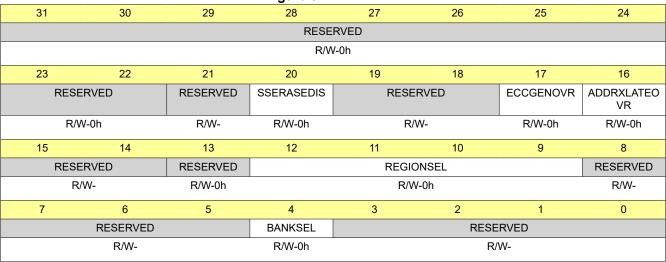

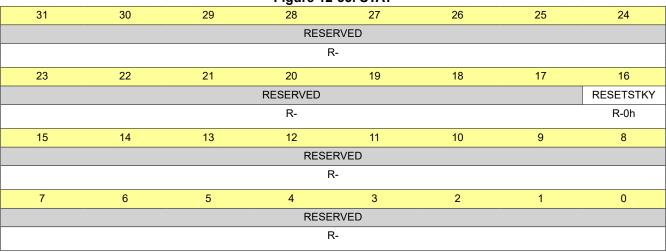

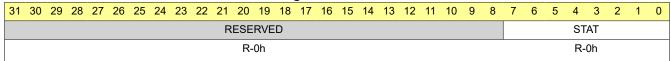

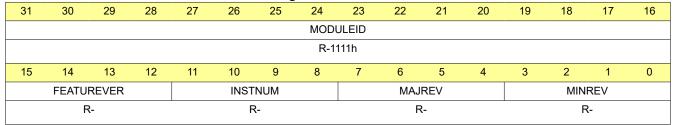

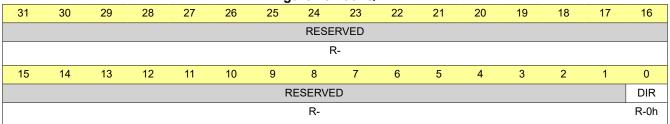

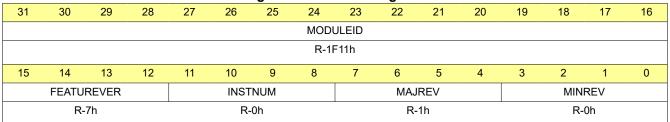

## 1.6.1.3 USERID Register (Offset = 41C40008h) [Reset = X0000000h]

USERID is shown in Figure 1-9 and described in Table 1-18.

Return to the Summary Table.

The variant feature set

## Figure 1-9. USERID Register

|       |          |    | J   | - 3 |      |      |    |  |

|-------|----------|----|-----|-----|------|------|----|--|

| 31    | 30       | 29 | 28  | 27  | 26   | 25   | 24 |  |

| START | MAJORREV |    |     |     | MINO | RREV |    |  |

| R-X   | R-0h     |    |     |     | R-0h |      |    |  |

| 23    | 22       | 21 | 20  | 19  | 18   | 17   | 16 |  |

|       |          |    | VAR | ANT |      |      |    |  |

| R-0h  |          |    |     |     |      |      |    |  |

| 15    | 14       | 13 | 12  | 11  | 10   | 9    | 8  |  |

| PART  |          |    |     |     |      |      |    |  |

| R-0h  |          |    |     |     |      |      |    |  |

| 7     | 6        | 5  | 4   | 3   | 2    | 1    | 0  |  |

| PART  |          |    |     |     |      |      |    |  |

| R-0h  |          |    |     |     |      |      |    |  |

|       |          |    |     |     |      |      |    |  |

## Table 1-18. USERID Register Field Descriptions

| Table 1-10. GOLIND Register Field Descriptions |          |      |       |                                                                                                                                                                                                                                                     |  |  |  |

|------------------------------------------------|----------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit                                            | Field    | Туре | Reset | Description                                                                                                                                                                                                                                         |  |  |  |

| 31                                             | START    | R    | X     |                                                                                                                                                                                                                                                     |  |  |  |

| 30-28                                          | MAJORREV | R    | 0h    | Monotonic increasing value indicating a new revision significant enough that users of the device may have to revise PCB or or software design                                                                                                       |  |  |  |

| 27-24                                          | MINORREV | R    | 0h    | Monotonic increasing value indicating a new revision that preserves compatibility with lesser minorrev values. New capability may be introduced such that lesser minorrev numbers may not be compatible with greater if the new capability is used. |  |  |  |

| 23-16                                          | VARIANT  | R    | 0h    | Bit pattern uniquely identifying the variant of a part                                                                                                                                                                                              |  |  |  |

| 15-0                                           | PART     | R    | 0h    | Bit pattern that uniquely identifying a part                                                                                                                                                                                                        |  |  |  |

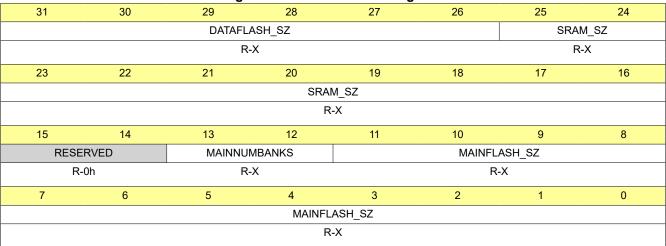

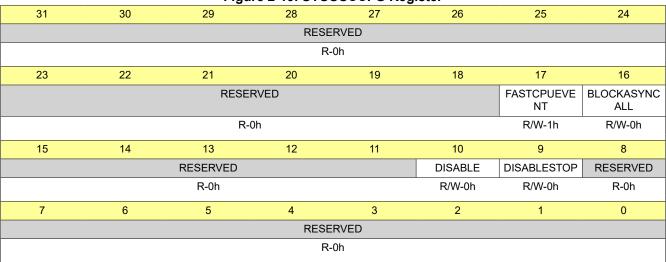

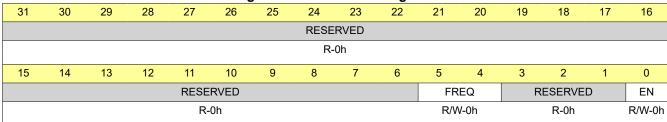

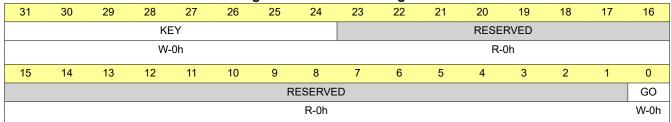

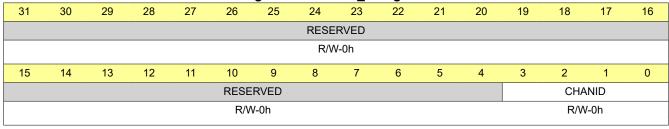

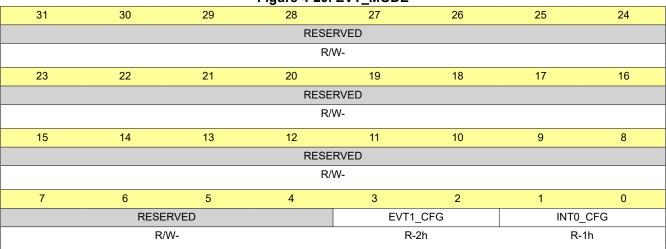

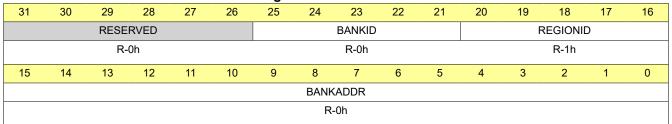

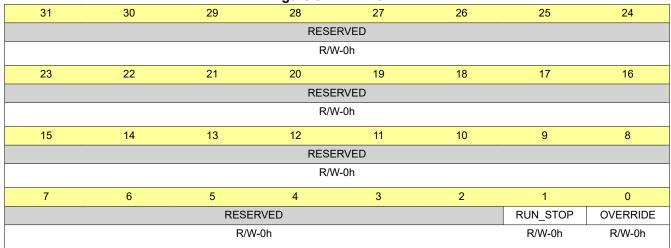

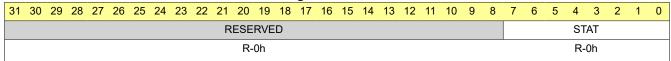

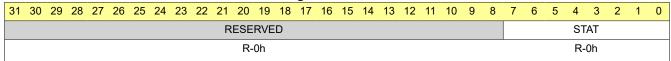

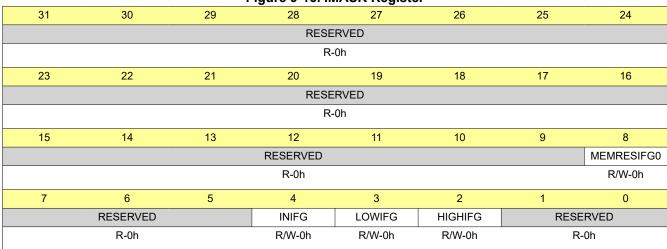

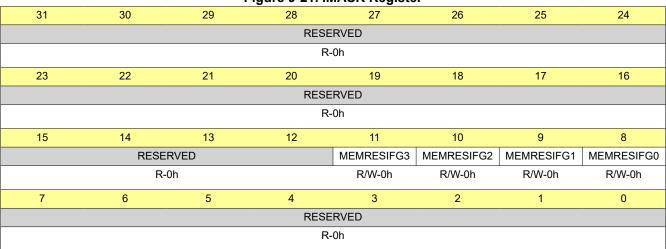

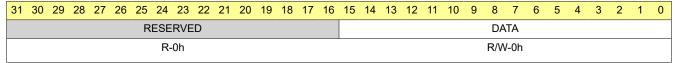

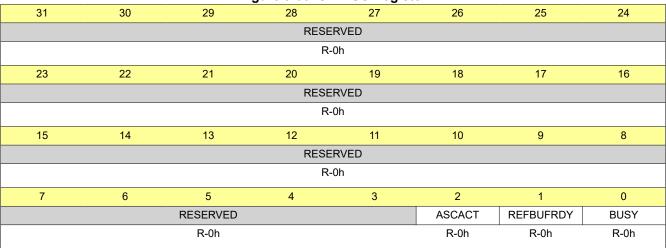

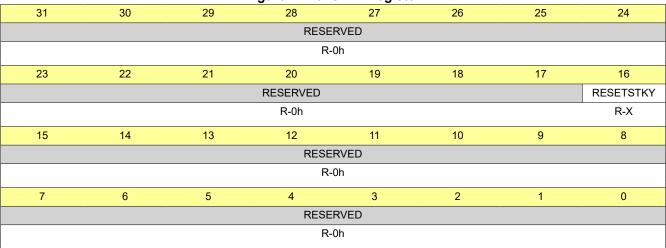

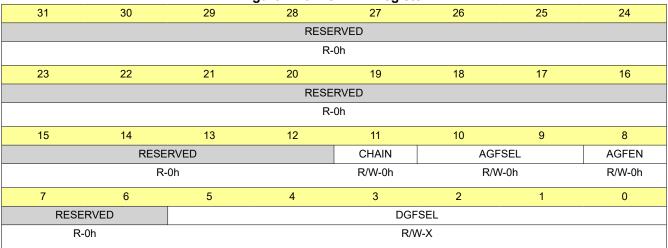

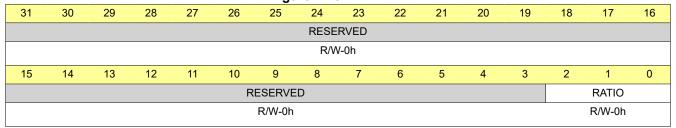

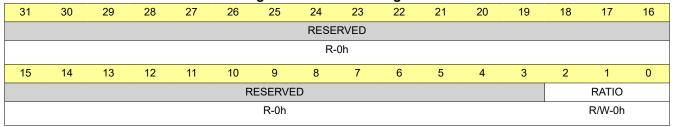

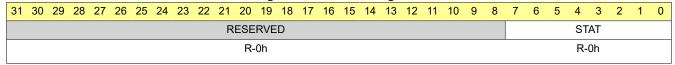

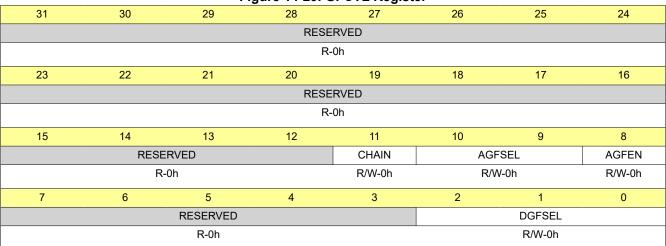

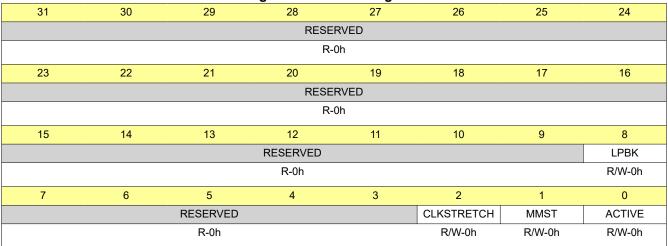

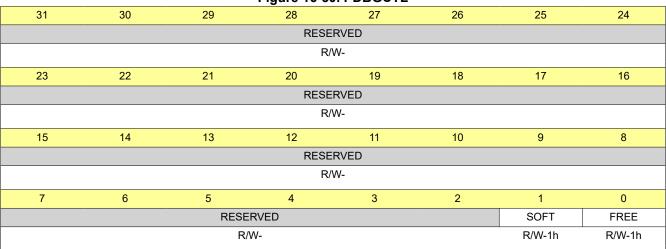

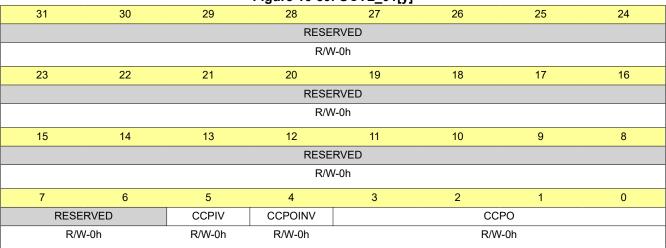

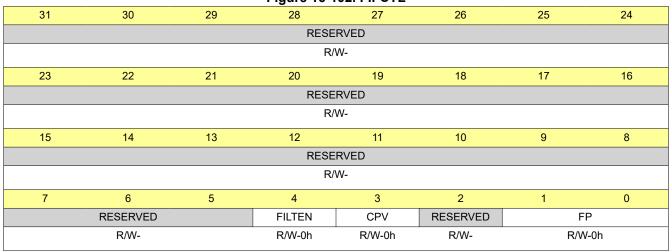

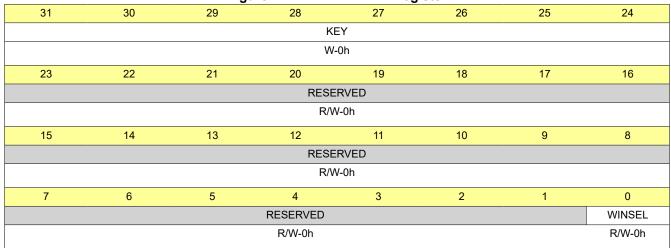

## 1.6.1.4 SRAMFLASH Register (Offset = 41C40018h) [Reset = XXXXXXXXh]

SRAMFLASH is shown in Figure 1-10 and described in Table 1-19.

Return to the Summary Table.

The encoding of memory size and flash bank number

## Figure 1-10. SRAMFLASH Register

## Table 1-19. SRAMFLASH Register Field Descriptions

| Bit   | Field        | Туре | Reset | Description                                                                                                                                                                                                     |

|-------|--------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-26 | DATAFLASH_SZ | R    | X     | The encoding of the field is that the value of the field is an integer to be interpreted as number of KBs.  For eg: if the value of the field id 4, then it is 4KB, if the value is 32, then 32KB, and so on.   |

| 25-16 | SRAM_SZ      | R    | X     | The encoding of the field is that the value of the field is an integer to be interpreted as number of KBs. For eg: if the value of the field id 4, then it is 4KB, if the value is 32, then 32KB, and so on.    |

| 15-14 | RESERVED     | R    | 0h    |                                                                                                                                                                                                                 |

| 13-12 | MAINNUMBANKS | R    | X     | The encoding of the field is that the value of the field is an integer to be interpreted as number of banks.  0 is one bank, 1 is two banks, 2 is three banks and 3 is 4 banks.  0h = 0  1h = 1  2h = 2  3h = 3 |

| 11-0  | MAINFLASH_SZ | R    | X     | The encoding of the field is that the value of the field is an integer to be interpreted as number of KBs. For eg: if the value of the field id 4, then it is 4KB, if the value is 32, then 32KB, and so on.    |

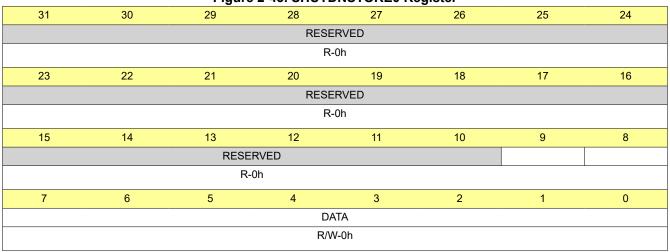

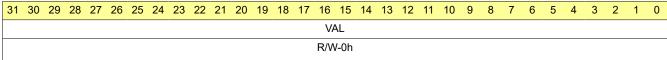

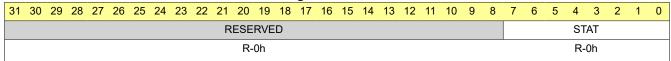

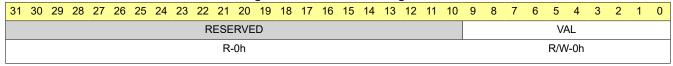

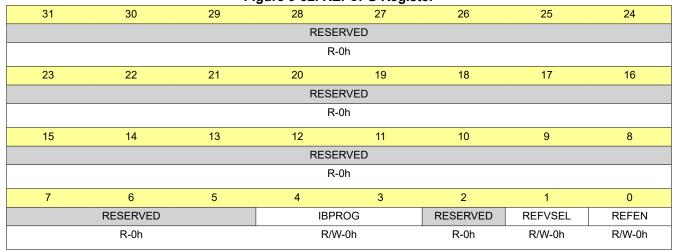

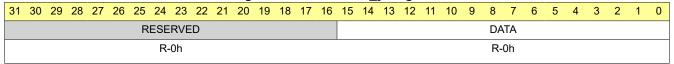

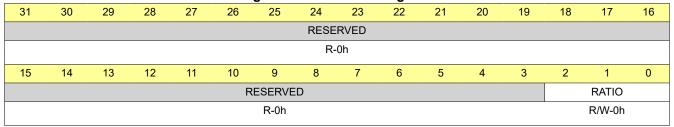

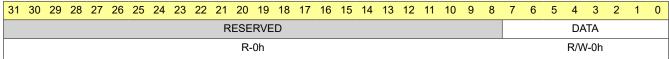

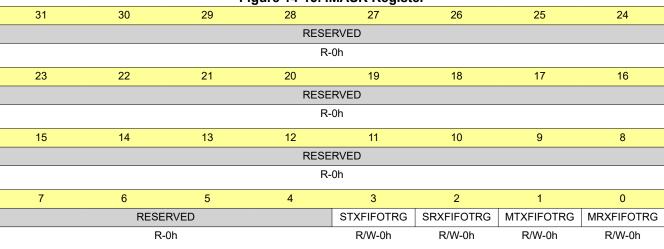

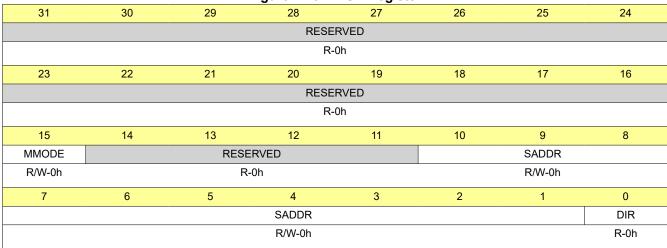

## 1.6.1.5 TEMP\_SENSE0 Register (Offset = 41C4003Ch) [Reset = 00000000h]

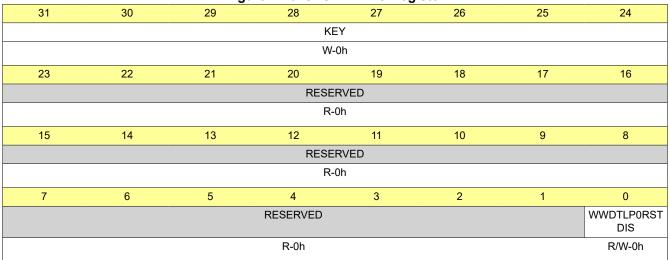

TEMP\_SENSE0 is shown in Figure 1-11 and described in Table 1-20.

Return to the Summary Table.

Temperature sensor room temperature calibration code. This is ADC conversion results of temperature sensor output voltage.

## Figure 1-11. TEMP\_SENSE0 Register

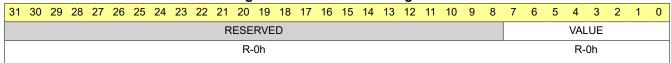

## Table 1-20. TEMP\_SENSE0 Register Field Descriptions

| Bit  | Field | Туре | Reset | Description |

|------|-------|------|-------|-------------|

| 31-0 | DATA  | R    | 0h    |             |

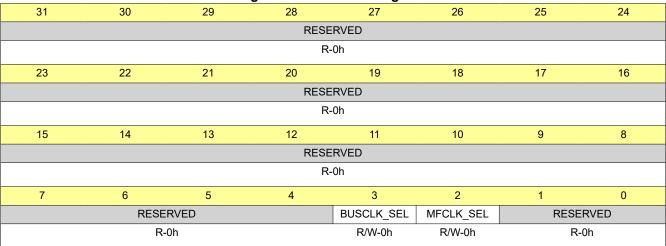

# Chapter 2 **PMCU**

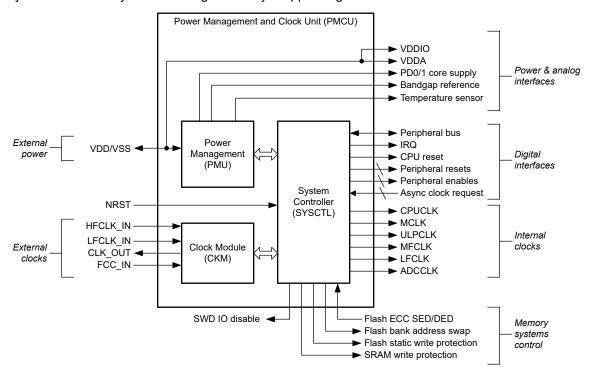

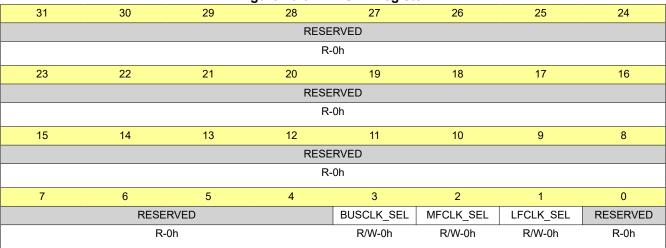

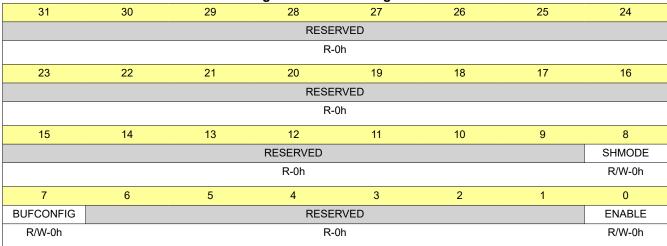

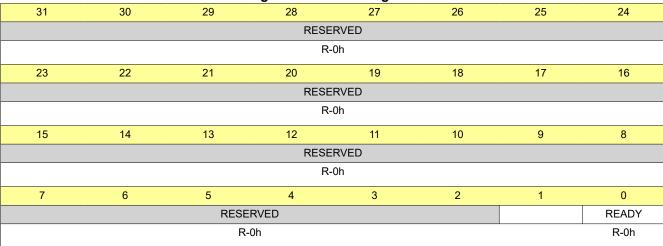

The power management and clock unit (PMCU) is a unified system module which provides all power management, clock configuration, and reset control functionality for the device. All power management unit (PMU) and clock module (CKM) policies for device operation are configured through memory-mapped registers in the system controller (SYSCTL).

| 2.4 DMOU Oceanies              | 24              |

|--------------------------------|-----------------|

| 2.1 PMCU Overview              |                 |

| 2.2 Power Management (PMU)     | <mark>39</mark> |

| 2.3 Clock Module (CKM)         | 43              |

| 2.4 System Controller (SYSCTL) |                 |

| 2.5 Quick Start Reference      |                 |

| 2.6 SYSCTL Registers           | 71              |

|                                |                 |

PMCU www.ti.com

#### 2.1 PMCU Overview

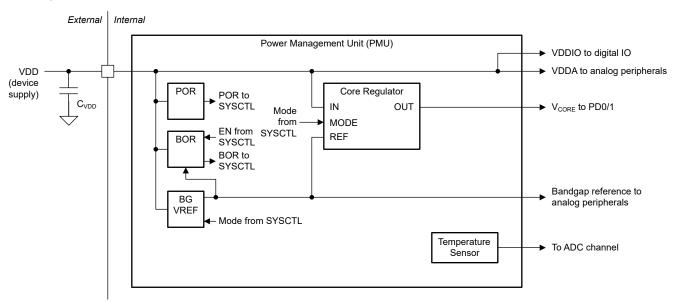

The power management and clock unit (PMCU) provides all power, clocking, reset, and system control services for the device. The PMCU contains three submodules to provide this functionality: the power management unit (PMU), the clock module (CKM), and the system controller (SYSCTL).

The PMU is an analog submodule that generates the internal regulated supplies for the device and supervises the condition of the external supply. The PMU also contains voltage and current reference circuits used by the on-chip regulators and analog peripherals.

The CKM is an analog submodule that provides clock sources (internal oscillators) and presents these clock sources to SYSCTL. SYSCTL distributes these clock sources to the CPU, buses, and peripherals on the device.

The SYSCTL is a digital submodule that provides the control logic for all functions in the PMCU. In addition, SYSCTL contains the memory-mapped registers used by software to configure power management and clocks, assess the status of the device, and control resets. SYSCTL also provides 4 bytes of general-purpose memory that is retained in SHUTDOWN mode and can be used to store status information in SHUTDOWN mode when SRAM and register contents are lost.

#none#

Note

shows the interfaces between the PMCU and the device supplies, clocks, and signals. Configuration of the PMCU by software is always done through memory-mapped registers in the SYSCTL submodule.

Figure 2-1. MSPM0Cxx PMCU Top Level

#### Note

Not all devices have all of the PMCU features shown in . See the device-specific data sheet to understand the features present on a given device.

## **Using this Guide**

www.ti.com PMCU

The PMU, CKM, and SYSCTL sections of this chapter describe the functionality provided by each submodule in detail.

The quick start section describes overall system level operation of the PMCU and how to configure the PMCU for different application scenarios.

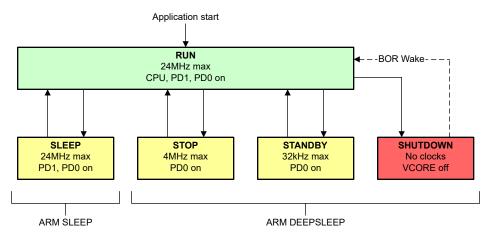

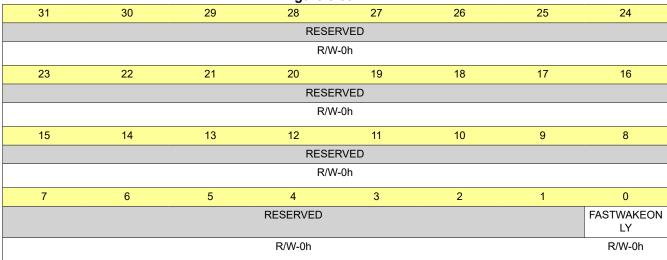

#### 2.1.1 Power Domains

Two core power domains are provided on the device: PD1 and PD0. PD1 is always powered in RUN and SLEEP modes, but is disabled in all other modes. PD0 is always powered in RUN, SLEEP, STOP and STANDBY modes. PD1 and PD0 are both disabled in SHUTDOWN mode.

- The PD1 domain includes the CPU subsystem, the SRAM memory, PD1 peripherals, and the PD1 peripheral

bus, which runs from MCLK (including the DMA) with a maximum frequency of 24 MHz. While PD1 is

disabled in STOP and STANDBY mode, the CPU registers, SRAM, and peripheral MMR configuration

registers are maintained in retention such that they are available to resume operation immediately when

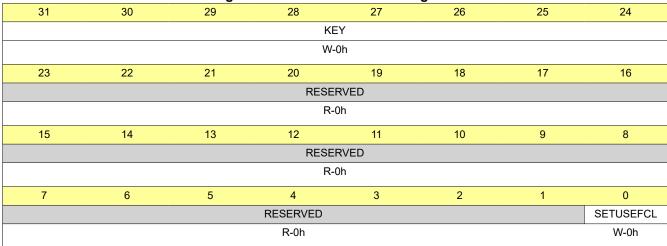

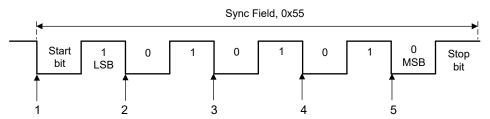

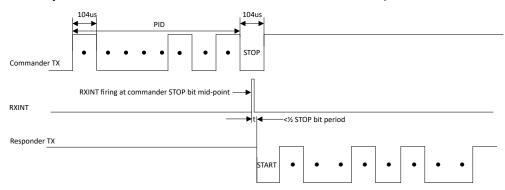

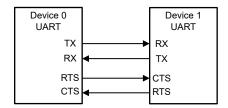

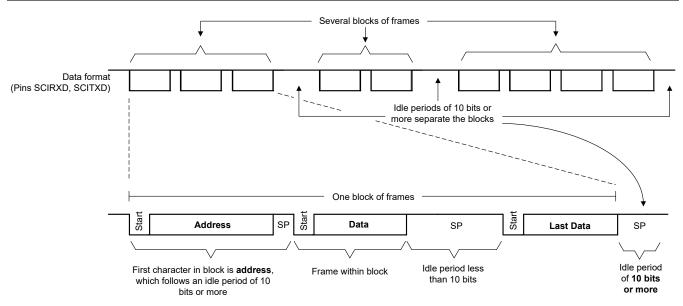

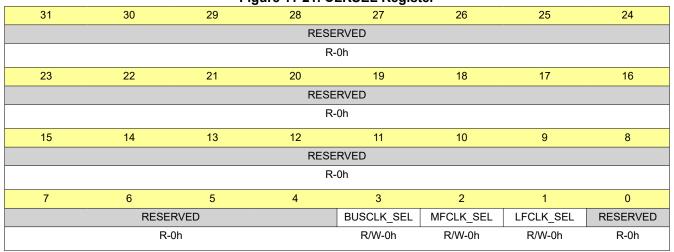

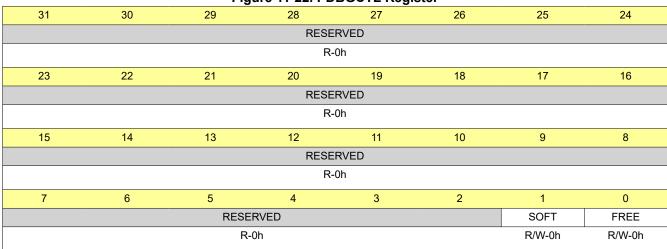

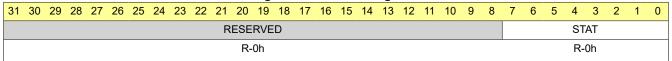

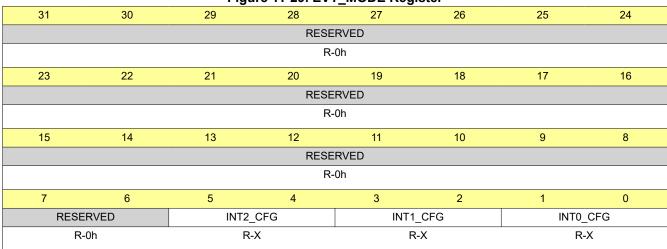

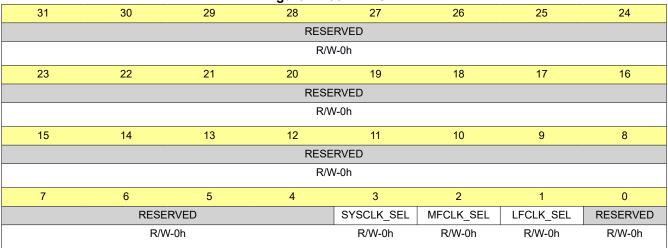

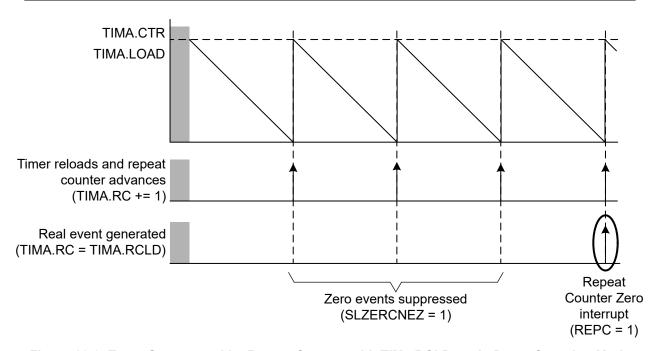

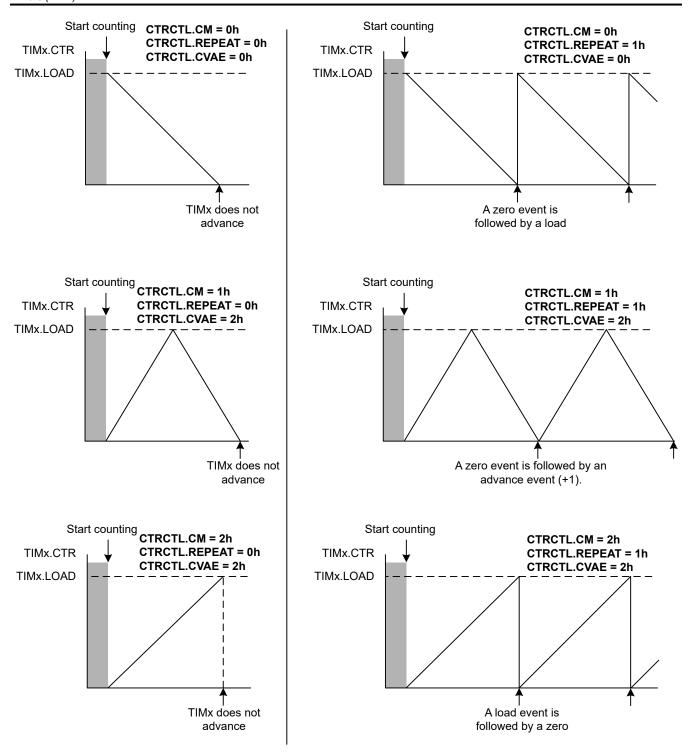

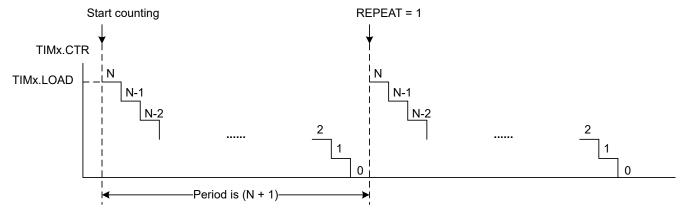

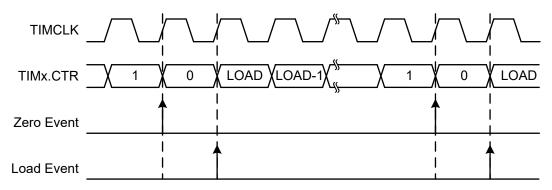

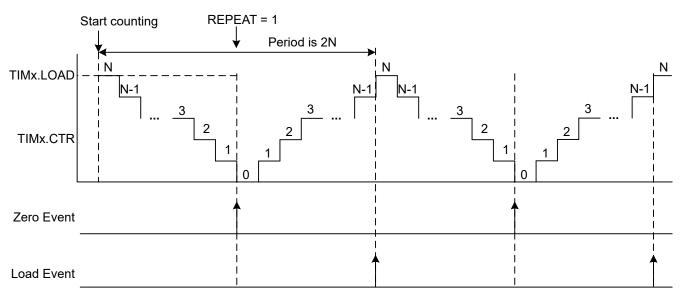

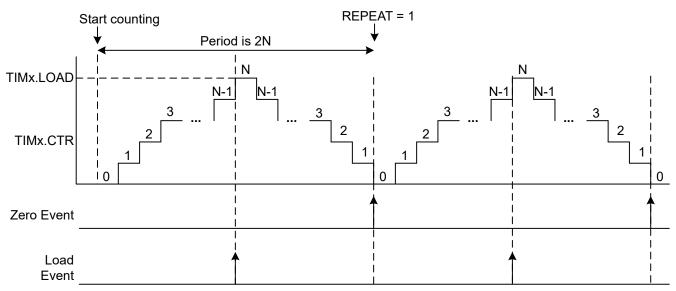

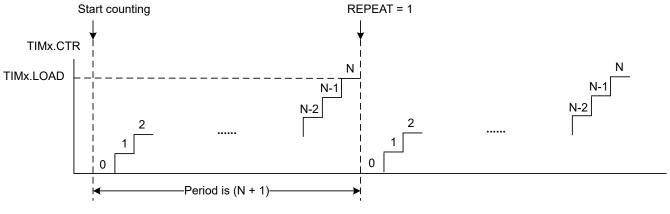

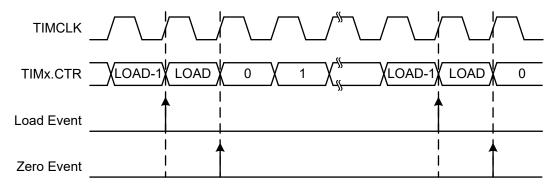

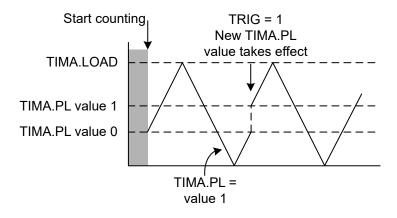

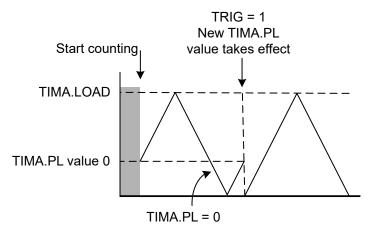

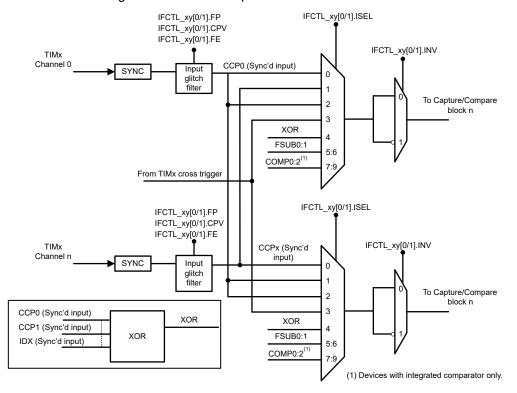

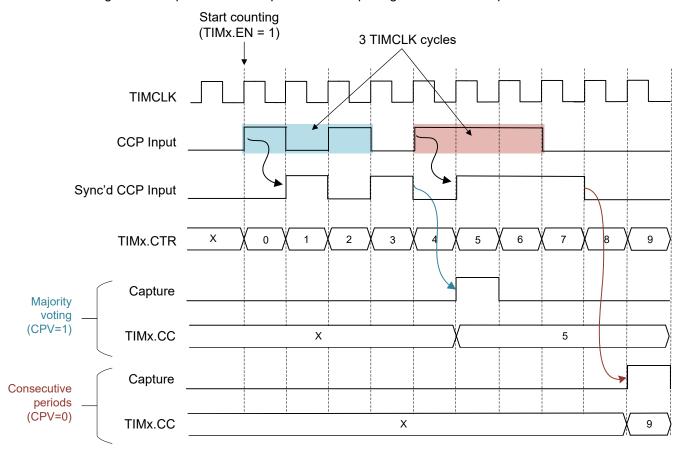

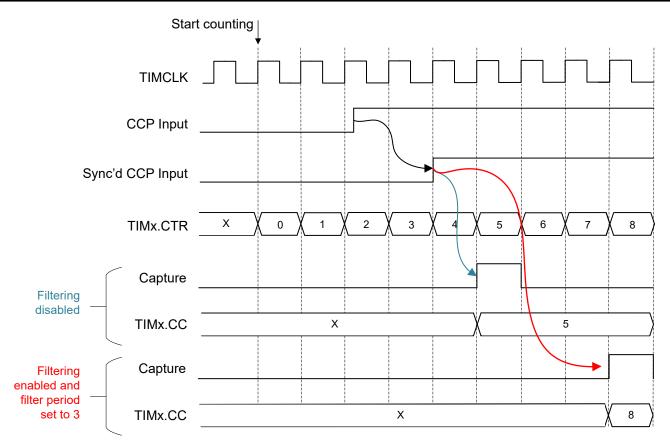

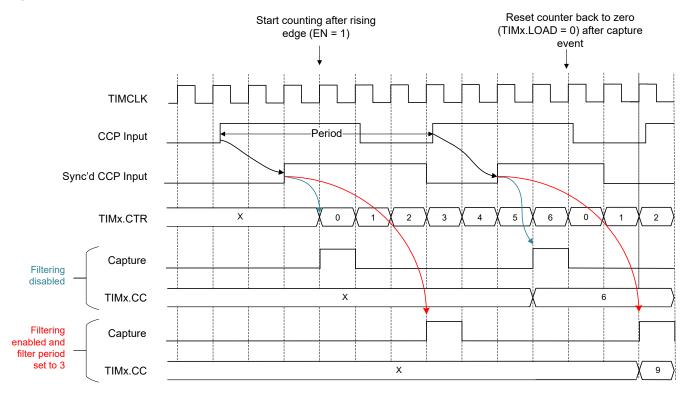

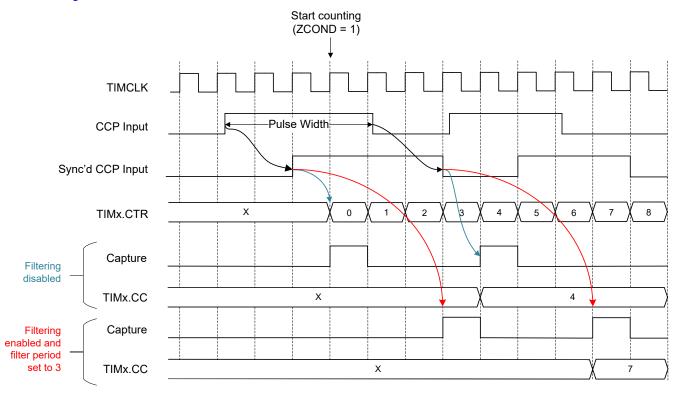

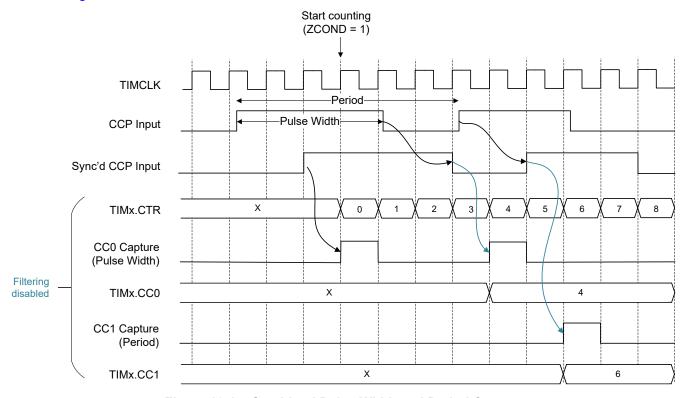

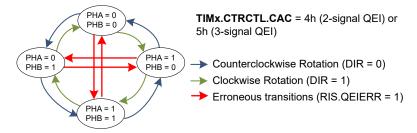

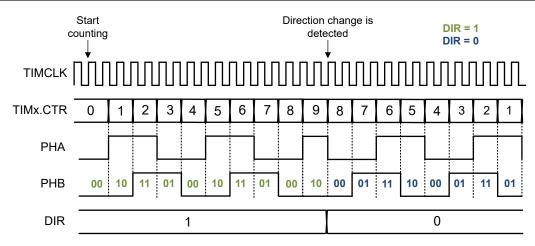

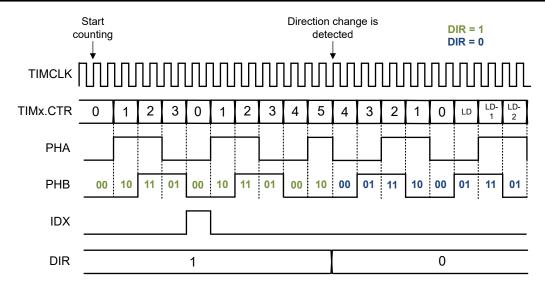

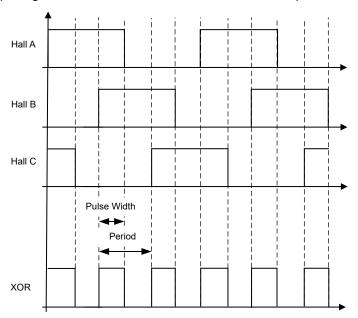

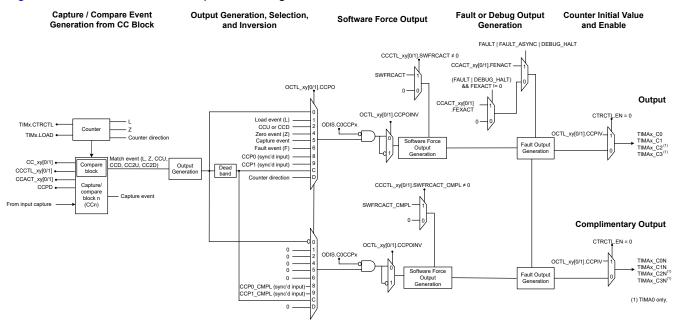

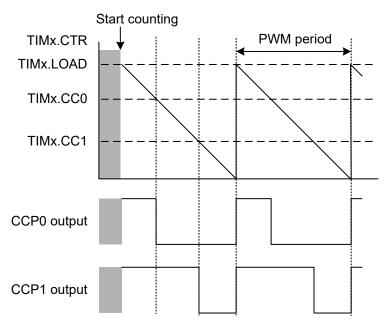

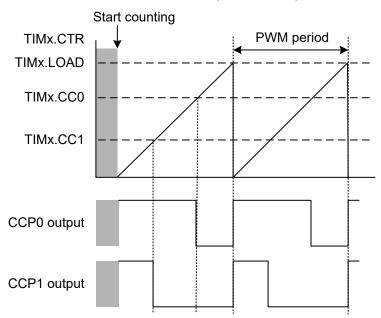

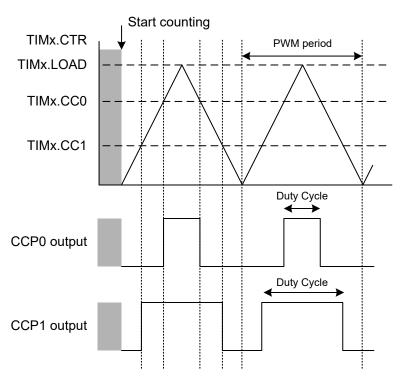

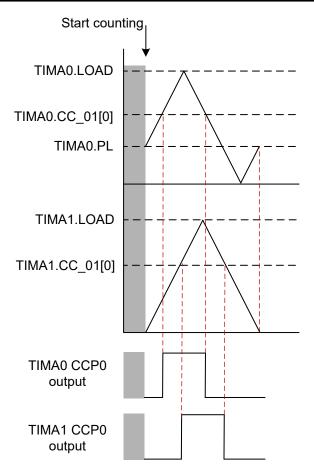

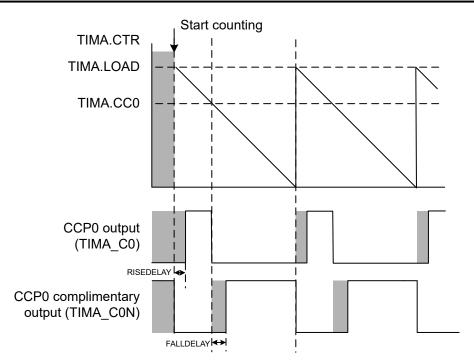

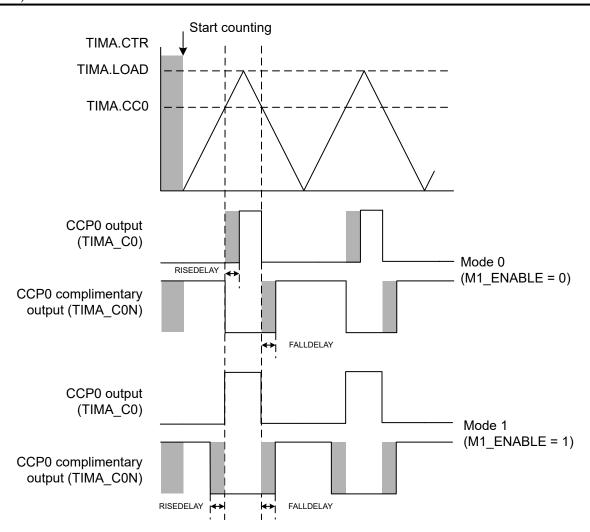

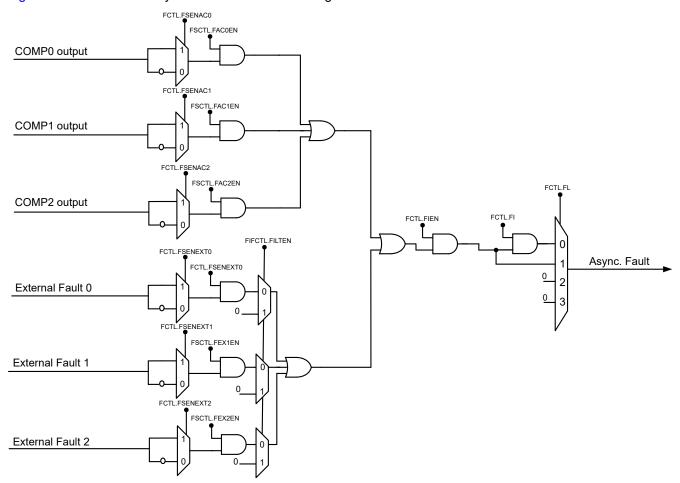

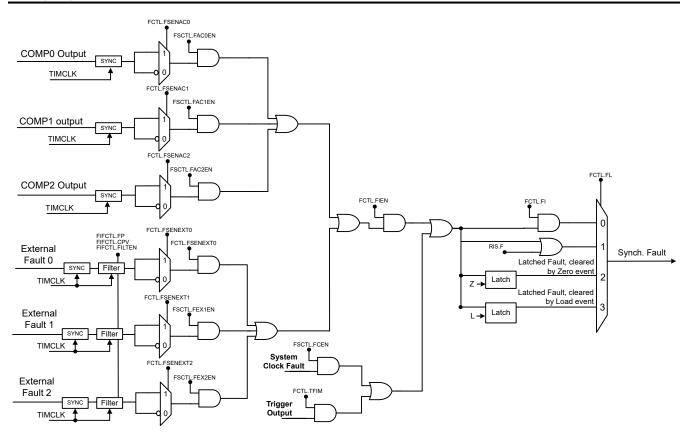

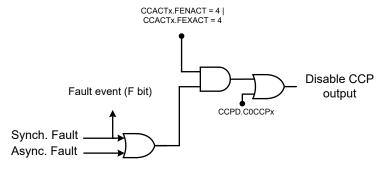

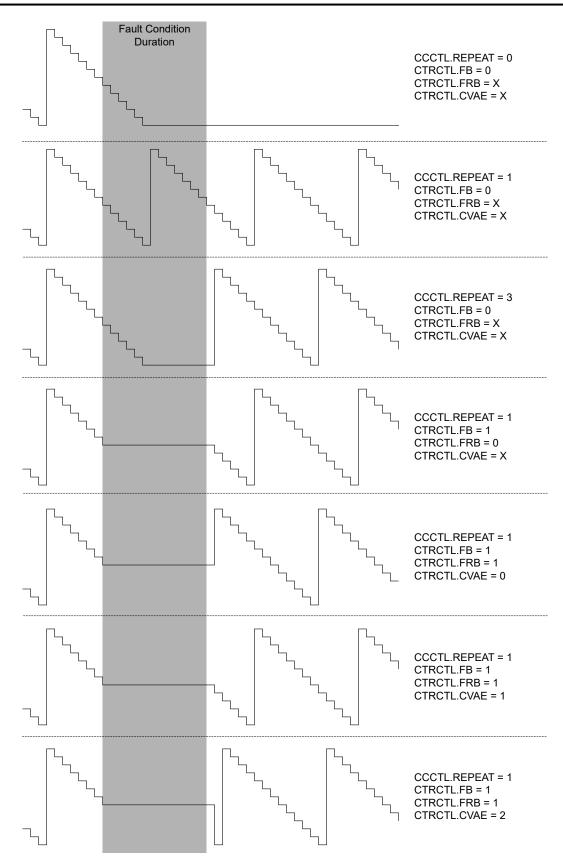

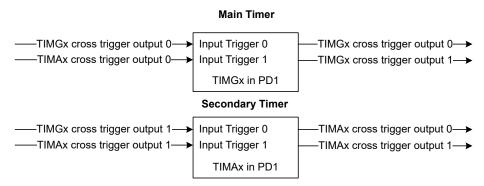

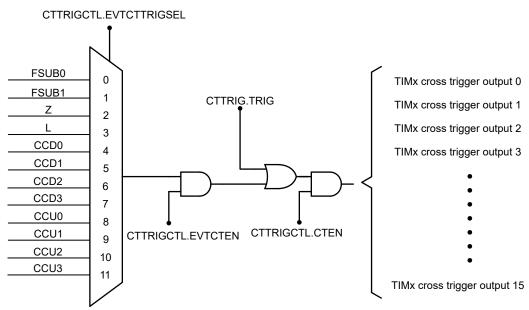

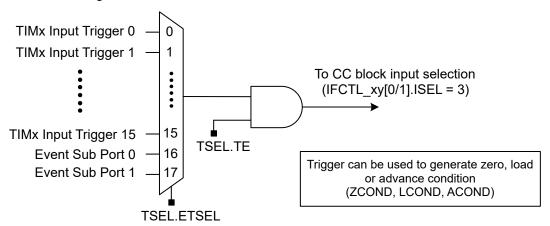

STOP or STANDBY modes are exited.