# EVM User's Guide: AFE532A3WEVM **AFE532A3W Evaluation Module**

# Description

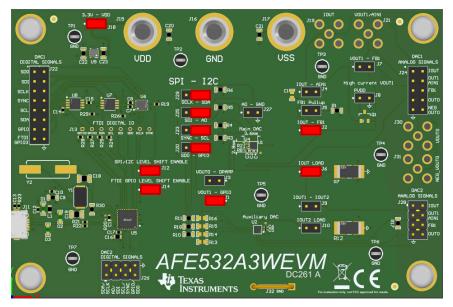

The AFE532A3WEVM is an easy-to-use platform to evaluate the functionality and performance of the AFEx32A3W commercial devices. The AFE532A3WEVM has optional circuits and jumpers to configure the AFE for different applications. The AFE532A3WEVM features two AFEx32A3W devices, referred to in this document as primary AFEx32A3W and auxiliary AFEx32A3W.

The 10-bit AFE532A3W, and 8-bit AFE432A3W are a pin-compatible family of three-channel, buffered, voltage-output (VOUT) and current-output (IOUT) smart analog front ends (AFEs). The AFE has two integrated digital-to-analog converters (DACs) and one channel that can be configured as a DAC or an analog-to-digital converter (ADC). The current output DAC has a 300-mA full scale range. The AFEx32A3W supports Hi-Z power-down mode and Hi-Z output during power-off conditions.

# **Get Started**

- 1. Order the EVM on ti.com.

- Download and install the AFE532A3WEVM software.

- 3. Configure the hardware jumper settings.

- 4. Connect the USB and external AFE532A3WEVM supplies.

- 5. Launch the AFE532A3WEVM GUI.

### **Features**

- Onboard 3.3-V VDD supply

- · Jumpers to evaluate different AFE configurations

- Output voltage inverter circuit

- Onboard FT4222 controller for SPI or I<sup>2</sup>C communication

# Applications

- Optical module

- High performance computing

- Standard notebook PC

1

# **1 Evaluation Module Overview**

# **1.1 Introduction**

The multi-functional GPIO, function generation, and nonvolatile memory (NVM) enable these smart AFEs for use in applications and design reuse without the need for runtime software. These devices also automatically detect I<sup>2</sup>C, SPI, and PMBus interfaces, and contain an internal reference.

This user's guide describes the characteristics, operation, and use of the AFE532A3WEVM evaluation module (EVM). This EVM is designed to evaluate the performance of the AFE532A3W and AFE432A3W commercial, buffered current and voltage output DACs in a variety of configurations. Throughout this document, all these devices are referred to as the AFEx32A3W, and the terms evaluation board, evaluation module, and EVM are synonymous with the AFE532A3WEVM. This document includes a schematic, printed-circuit board (PCB) layouts, and a complete bill of materials (BOM).

# 1.2 Kit Contents

Table 1-1 details the contents of the EVM kit. Contact the nearest TI Product Information Center if any component is missing. Make sure to verify the latest versions of the related software at the Texas Instruments website, www.ti.com.

| Item                                 | Quantity |

|--------------------------------------|----------|

| AFE532A3WEVM evaluation board PCB    | 1        |

| USB micro-B plug to USB-A plug cable | 1        |

Table 1-1. Contents of AFE532A3WEVM Kit

# **1.3 Specification**

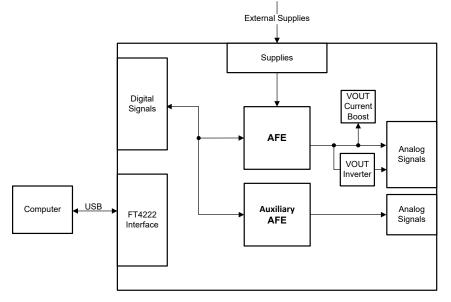

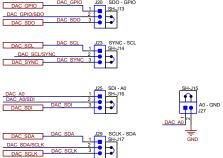

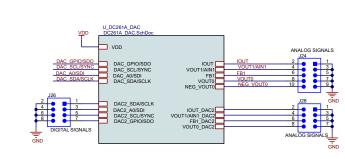

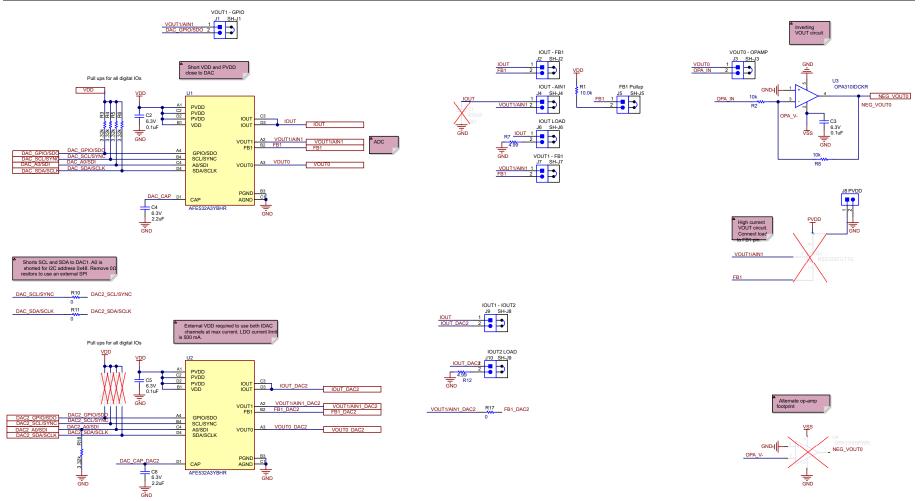

Figure 1-1 shows a simplified schematic of the AFE532A3WEVM board. There are three connectors that provide access to all of the digital and analog signals on the EVM. The GPIO, I<sup>2</sup>C, and SPI signals from the onboard controller are connected to the AFEx32A3W through two level translators. The level translators can be disabled to disconnect the onboard controller GPIO, I<sup>2</sup>C, and SPI signals from the AFEx32A3W.

Figure 1-1. AFE532A3WEVM Simplified Schematic

# **1.4 Device Information**

The following document provides information regarding Texas Instruments integrated circuits used in the assembly of the AFE532A3WEVM. This user's guide is available from the TI web site under literature number SLAU900. Any letter appended to the literature number corresponds to the document revision that is current at the time of the writing of this document. Newer revisions are available from the TI web site at www.ti.com, or call the Texas Instruments Literature Response Center at (800) 477-8924 or the Product Information Center at (972) 644-5580. When ordering, identify the document by both title and literature number.

| Document               | Literature Number |

|------------------------|-------------------|

| AFE532A3W product page | SLASFB2           |

| AFE432A3W product page |                   |

### Table 1-2. Related Documentation

# 2 Hardware

# 2.1 Hardware Setup

This section describes the overall system setup for the EVM. A computer runs the software that provides an interface to the AFE532A3WEVM through the onboard controller.

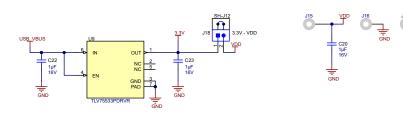

The USB connection generates a 5-V supply for the EVM. The onboard controller generates 3.3 V of power for the input/output (IO) signals generated by the onboard controller. These IO signals are level translated to the VDD voltage of the AFEx32A3W. An onboard, 3.3-V voltage regulator generates 3.3 V for use as the AFEx32A3W supply voltage (VDD).

# 2.1.1 Electrostatic Discharge Caution

CAUTION

Many of the components on the AFE532A3WEVM are susceptible to damage by electrostatic discharge (ESD). Observe proper ESD handling precautions when unpacking and handling the EVM, including the use of a grounded wrist strap at an approved ESD workstation.

# 2.1.2 Power Configurations and Jumper Settings

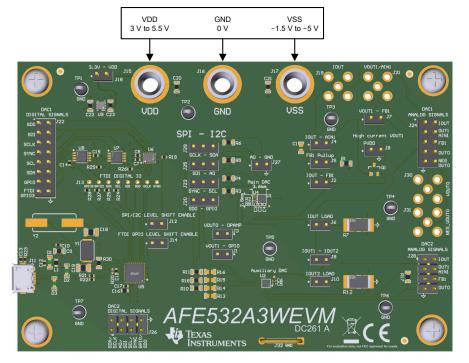

The AFE532A3WEVM provides electrical connections to the device supply pins. Table 2-1 and Figure 2-1 shows the power supply connections.

| AFE532A3WEVM<br>Connector | Supply Name | Voltage Range                                                              |

|---------------------------|-------------|----------------------------------------------------------------------------|

| J15                       | VDD         | 3 V to 5.5 V; remove jumper J18 if applying an external VDD to the device. |

| J16                       | GND         | 0 V                                                                        |

| J17                       | VSS         | -1.5 V to -5 V; required to use the inverting op-amp circuit.              |

| J8                        | PVDD        | PVDD supply for the VOUT1 current boost circuit                            |

Figure 2-1. AFE532A3WEVM Power Supply Inputs

Table 2-2 provides the details of the configurable jumper settings on the AFE532A3WEVM.

4

| Jumper | Default Position                                  | Available Option                               | Description                                                 |

|--------|---------------------------------------------------|------------------------------------------------|-------------------------------------------------------------|

| J1     | Open: VOUT1 disconnected from<br>GPIO/SDO         | Closed: VOUT1 connected to GPIO/SDO            | Connects VOUT1 to GPIO/SDO                                  |

| J2     | Open: IOUT disconnected from FB1                  | Closed: IOUT connected to FB1                  | Connects IOUT to FB1 (comparator input)                     |

| J3     | Open: VOUT0 disconnected from op-amp input        | Closed: VOUT0 connected to op-amp input        | Connects VOUT0 to the op-amp input pin                      |

| J4     | Open: IOUT disconnected from AIN1                 | Closed: IOUT connected to AIN1                 | Connects IOUT to AIN1 (ADC input)                           |

| J5     | Open: FB1 disconnected from 10-kΩ pullup resistor | Closed: FB1 connected to 10-kΩ pullup resistor | Connect FB1 to a 10-k $\Omega$ pullup resistor              |

| J6     | Open: IOUT disconnected from 4.99-Ω load          | Closed: IOUT connected to 4.99-Ω load          | Connects IOUT to a 4.99-Ω load                              |

| J7     | Closed: VOUT1 connected to FB1                    | Open: VOUT1 disconnected to FB1                | Connects VOUT1 to FB1                                       |

| J9     | Open: IOUT disconnected from IOUT2                | Closed: IOUT connected to IOUT2                | Connects IOUT to IOUT2                                      |

| J10    | Open: IOUT2 disconnected from 4.99-Ω load         | Closed: IOUT2 connected to 4.99-Ω load         | Connects IOUT2 to a 4.99-Ω load                             |

| J12    | Closed: FTDI SPI and I <sup>2</sup> C enabled     | Open: FTDI SPI and I <sup>2</sup> C disabled   | Enables the FTDI SPI and I <sup>2</sup> C level translators |

| J14    | Closed: FTDI GPIOs enabled                        | Open: FTDI GPIOs disabled                      | Enables the FTDI GPIO level translators                     |

| J18    | Closed: 3.3-V supply connected to VDD             | Open: 3.3-V supply disconnected from VDD       | AFE VDD supply selection                                    |

| J20    | 1-2: GPIO connected to AFE                        | 2-3: SDO connected to AFE                      | I <sup>2</sup> C or SPI selection                           |

| J23    | 1-2: SCL connected to AFE                         | 2-3: SYNC connected to AFE                     | I <sup>2</sup> C or SPI selection                           |

| J25    | 1-2: A0 connected to AFE                          | 2-3: SDI connected to AFE                      | I <sup>2</sup> C or SPI selection                           |

| J29    | 1-2: SDA connected to AFE                         | 2-3: SCLK connected to AFE                     | I <sup>2</sup> C or SPI selection                           |

### Table 2-2. AFE532A3WEVM Jumper Settings

If an external supply is applied to J15, then remove jumper J18 to disconnect the 3.3-V regulator supply from the AFEx32A3W VDD pin.

GPIO2 and GPIO3 from the onboard controller are configured as outputs when the AFE532A3WEVM is controlled with the GUI. GPIO2 from the onboard controller is connected to the GPIO/SDO pin of the AFEx32A3W. If the AFE SDO pin is configured as an output, then remove jumper J14 to disable the GPIOs from the onboard controller.

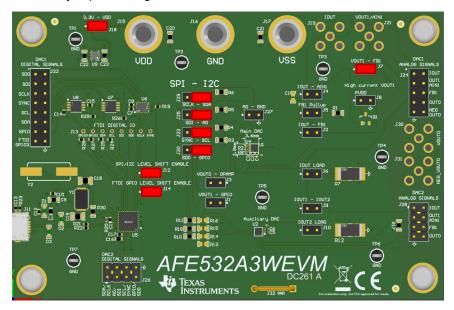

Figure 2-2 shows the default jumper settings on the AFE532A3WEVM.

Figure 2-2. AFE532A3WEVM Default Jumper Settings

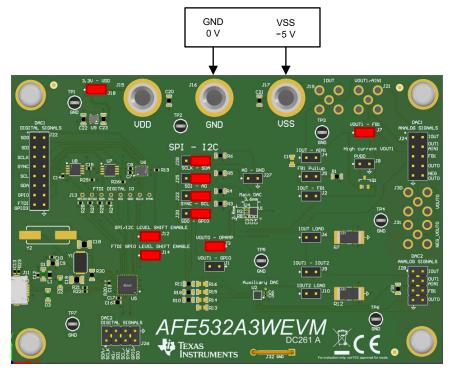

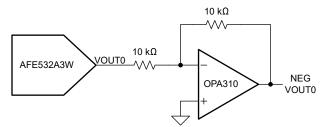

The AFE532A3WEVM has an optional inverting op-amp circuit that can be used to invert the VOUT0 output of the primary AFEx32A3W. Figure 2-3 shows how to configure the jumpers to enable the inverting op-amp circuit. VSS is connected to the negative supply of the inverting op-amp. Connect a –1.5-V to –5-V supply to J17 before closing jumper J3. The positive supply of the inverting op-amp is connected to ground.

Figure 2-3. AFE532A3WEVM Inverting Op-amp Jumper Settings

The IOUTs of the primary and auxiliary AFEx32A3W devices can be connected in parallel to increase the total current output. Figure 2-4 shows the jumper configuration to connect the IOUTs in parallel. Close jumper J6 and/or jumper J10 to connect the resistive load to the parallel IOUT. An external VDD needs to be used if the combined current output exceeds the current limit of the USB port and/or the 500-mA current rating of the onboard regulator.

Figure 2-4. AFE532A3WEVM Parallel IOUT Jumper Settings

The AFEx32A3W can be used to monitor signals using the integrated programmable comparator. Figure 2-5 shows how to configure the AFE532A3WEVM jumpers to connect the IOUT pin to the comparator input and connect the comparator output to the GPIO/SDO pin. When the voltage across the 4.99- $\Omega$  load crosses a programmed threshold, the comparator output connected to the GPIO/SDO pin can be used to trigger alarm conditions or enter power-down mode.

Figure 2-5. AFE532A3WEVM Comparator Input Jumper Settings

Figure 2-6 shows the jumper configuration to connect the IOUT pin to the ADC input. The ADC can be used to monitor the IOUT when the IOUT is connected to the  $4.99-\Omega$  load.

Figure 2-6. AFE532A3WEVM ADC Input Jumper Settings

# 2.1.3 Connecting the Hardware

After the power and jumper configurations are set up as per Section 2.1.2, connect the USB cable from the AFE532A3WEVM USB port to the computer.

7

# 2.2 Hardware Description

The following sections provide detailed information on the EVM hardware.

### 2.2.1 Signal Definitions

The AFE532A3WEVM provides access to all AFEx32A3W pins through connectors J22, J24, J26, and J28. J22 and J24 provide access to the pins of the primary AFEx32A3W. Table 2-3 and Table 2-4 list the J22 and J24 pin definitions.

| Pin# | Signal     | Description                             |  |

|------|------------|-----------------------------------------|--|

|      |            | •                                       |  |

| 1    | SDO        | SPI SDO                                 |  |

| 2    | GND        | Ground                                  |  |

| 3    | SDI        | SPI SDI                                 |  |

| 4    | GND        | Ground                                  |  |

| 5    | SCLK       | SPI SCLK                                |  |

| 5    | GND        | Ground                                  |  |

| 7    | SYNC       | SPI SYNC                                |  |

| 6    | GND        | Ground                                  |  |

| 9    | SCL        | I <sup>2</sup> C SCL                    |  |

| 10   | GND        | Ground                                  |  |

| 11   | SDA        | I <sup>2</sup> C SDA                    |  |

| 12   | GND        | Ground                                  |  |

| 13   | GPIO       | AFE GPIO                                |  |

| 14   | GND        | Ground                                  |  |

| 15   | FTDI_GPIO3 | GPIO3 output of the on-board controller |  |

### Table 2-3. AFE532A3WEVM J22 Pin Definitions

#### Table 2-4. AFE532A3WEVM J24 Pin Definitions

| Pin# | Signal         | Description                      |

|------|----------------|----------------------------------|

| 1    | GND            | Ground                           |

| 2    | IOUT           | Primary AFEx32A3W IOUT           |

| 3    | GND            | Ground                           |

| 4    | VOUT1/AIN1     | Primary AFEx32A3W VOUT1/AIN1     |

| 5    | GND            | Ground                           |

| 6    | FB1            | Primary AFEx32A3W FB1            |

| 7    | GND            | Ground                           |

| 8    | VOUT0          | Primary AFEx32A3W VOUT0          |

| 9    | GND            | Ground                           |

| 10   | Negative VOUT0 | Primary AFEx32A3W negative VOUT0 |

J26 and J28 provide access to the pins of the auxiliary AFEx32A3W. Table 2-5 and Table 2-6 list the J26, and J28 pin definitions.

| Pin# | Signal   | Description                  |

|------|----------|------------------------------|

| 1    | SDA/SCLK | Auxiliary AFEx32A3W SDA/SCLK |

| 2    | GND      | Ground                       |

| 3    | A0/SDI   | Auxiliary AFEx32A3W A0/SDI   |

| 4    | GND      | Ground                       |

| 5    | SCL/SYNC | Auxiliary AFEx32A3W SCL/SYNC |

| 6    | GND      | Ground                       |

| 7    | GPIO/SDO | Auxiliary AFEx32A3W GPIO/SDO |

| 8    | GND      | Ground                       |

### Table 2-5. AFE532A3WEVM J26 Pin Definitions

#### Table 2-6. AFE532A3WEVM J28 Pin Definitions

| Pin# | Signal     | Description                    |

|------|------------|--------------------------------|

| 1    | GND        | Ground                         |

| 2    | IOUT       | Auxiliary AFEx32A3W SDA/SCLK   |

| 3    | GND        | Ground                         |

| 4    | VOUT1/AIN1 | Auxiliary AFEx32A3W VOUT1/AIN1 |

| 5    | GND        | Ground                         |

| 6    | FB1        | Auxiliary AFEx32A3W FB1        |

| 7    | GND        | Ground                         |

| 8    | VOUT0      | Auxiliary AFEx32A3W VOUT0      |

### 2.2.2 Optional Circuitry

The AFE532A3WEVM has optional circuitry that can be used to evaluate the AFEx32A3W.

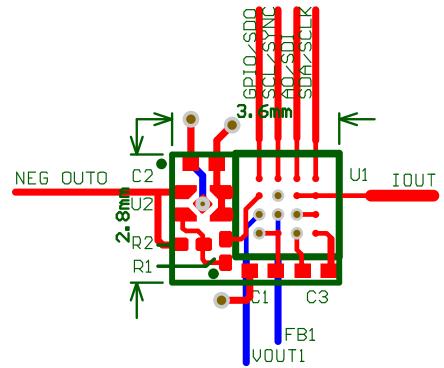

The AFEx32A3W can be used in optical module applications that require up to a 300 mA current source and a negative bias voltage. The negative bias voltage is generated by connecting the voltage output of the AFEx32A3W to an inverting op-amp. Figure 2-7 shows the block diagram for the negative bias circuit.

Figure 2-7. AFE532A3WEVM Negative Bias Circuit Block Diagram

Figure 2-8 shows the 2.8-mm × 3.6-mm negative bias circuit layout. The layout consists of the AFEx32A3W, OPA310, two size-0201 resistors, and three size-0201 capacitors.

Figure 2-8. AFE532A3WEVM Negative Bias Circuit Layout

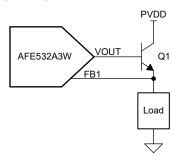

The output current capability of the AFEx32A3W VOUT channels can be increased with an external current boost circuit. Figure 2-7 shows the block diagram for the high current, voltage output circuit. Q1 is not populated on the AFE532A3WEVM. Remove the shunt from J7 before populating Q1. Connect PVDD to pin 1 of J8 and connect the load to the AFEx32A3W FB1 pin on pin 6 of J24.

Figure 2-9. AFE532A3WEVM High Current Output Stage Block Diagram

# 3 Software

# 3.1 Software Setup

This section provides the procedure for EVM software installation.

### 3.1.1 Operating Systems

The EVM software is compatible with the Windows<sup>™</sup> 10 operating system.

### 3.1.2 Software Installation

Make sure that the AFE532A3WEVM is not connected to the computer during the software installation.

The AFE532A3WEVM software can be downloaded from the device product folders or AFE532A3WEVM tool folder. After the software is downloaded, navigate to the download folder, and run the SMART-DAC-EVM-GUI installer executable.

When the AFE532A3WEVM software is launched, an installation dialog window opens and prompts the user to select an installation directory. Figure 3-1 shows that the software path defaults to C:\Program Files (x86)\Texas Instruments\SMART-DAC-EVM-GUI.

| 🐙 SMART-DAC-EVM-GUI                                                                                              |                |        | —      |       | ×  |

|------------------------------------------------------------------------------------------------------------------|----------------|--------|--------|-------|----|

| <b>Destination Directory</b><br>Select the installation directories.                                             |                |        |        |       |    |

| All software will be installed in the following locations different location, click the Browse button and select |                |        |        |       |    |

| Directory for SMART-DAC-EVM-GUI                                                                                  |                |        |        |       |    |

| C:\Program Files (x86)\Texas Instruments\SMAR                                                                    | T-DAC-EVM-GUI\ |        | Browse | в     |    |

| Directory for National Instruments products<br>C:\Program Files (x86)\National Instruments\                      |                |        | Browse | 8     |    |

|                                                                                                                  | << Back        | Next>> |        | Cance | el |

Figure 3-1. Software Installation Path

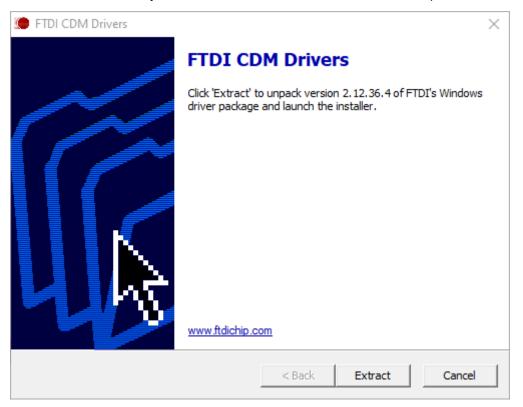

The software installation also installs the FTDI USB drivers, and automatically copies the required LabVIEW<sup>™</sup> software files and drivers to the computer. The FTDI USB drivers install in a second executable. Figure 3-2 shows the window that is automatically launched after the software installation is complete.

Figure 3-2. FTDI USB Drivers

# 3.2 Software Description

This section describes the features of the AFE532A3WEVM software, and discusses how to use these features. The software provides basic control of all the AFEx32A3W registers and functions.

### 3.2.1 Starting the Software

To launch the software, navigate to the SMART-DAC-EVM folder in the *Start* menu, and select the SMART-DAC-EVM icon.

Figure 3-3 shows the *Device Selector* window that pops up on start up. This window contains a drop-down menu to select which device register map is loaded into the GUI. Select the AFE532A3W when using the AFE532A3WEVM.

| SMAR                        | Device Setting                                                         |

|-----------------------------|------------------------------------------------------------------------|

|                             | Device Choice                                                          |

|                             | 🐺 Texas Instruments                                                    |

| Initializing Register class | Copyright © 2023. Texas Instruments Incorporated. All rights reserved. |

Figure 3-3. Device Selector

Figure 3-4 shows that if the onboard controller is connected correctly, the status bar at the bottom of the screen displays *CONNECTED*. If the controller is not properly connected or not connected at all, the status displays *DEMO*. If the GUI is not displaying the *CONNECTED* status while the EVM is connected, unplug and reconnect the EVM, and then relaunch the GUI software. If the display continues to display DEMO, uncheck the *Demo Mode* checkbox (see Figure 3-6, upper-right corner).

| Idle | 🐺 Texas Instruments |

|------|---------------------|

|      |                     |

Figure 3-4. GUI Connection Detection

Figure 3-5 shows the *Interface Settings* window. When the GUI starts, the *Interface Settings* window pops up. This window contains drop-down menus that select protocol (SPI or I<sup>2</sup>C) and, if I<sup>2</sup>C protocol is selected, the I<sup>2</sup>C device address. The menu does not pop up if the GUI starts in Demo mode. In this case, uncheck the *Demo Mode* checkbox. If the interface must be updated again, toggle the *Demo Mode* checkbox for the menu to reappear.

| I2C 🔻    | A0 = VDD                              |                      | •   | × 49     | CON      |

|----------|---------------------------------------|----------------------|-----|----------|----------|

| FTDI     |                                       |                      |     |          |          |

|          | I <sup>2</sup> C                      | ]                    |     | SPI      |          |

| SP]      | [ - I2                                |                      | SPI | - 12     |          |

| J29      |                                       | <b></b> R6           | J29 | -        | R        |

| ه<br>125 | SCLK - SDA                            | [ . R5 <sup>19</sup> | 125 | lk - SDA | <b>R</b> |

| 5.       | SDI - AO                              | E ER4                |     | DI - AO  | E R      |

| J23      | SYNC - SCL                            |                      | J23 | NC - SCL |          |

| 20       | • • • • • • • • • • • • • • • • • • • |                      | 2   |          |          |

|          | SDO - GPIO                            | c                    | SD  | 0 - GPIO |          |

Figure 3-5. Interface Settings

### 3.2.2 Software Features

The AFE532A3WEVM GUI incorporates interactive functions that help configure an individual AFEx32A3W device using I<sup>2</sup>C or SPI communication. These functions are built into several GUI pages, as shown in the following subsections. The menu bar on the far left of the GUI allows the user to switch between pages. The menu bar displays the *High Level Configuration* page, with the *Basic DAC* subpage, and the *Low Level Configuration* page.

Before using the GUI, see the respective device data sheet for detailed AFEx32A3W programming instructions.

### 3.2.2.1 High Level Configuration Page

Figure 3-6 shows the *High Level Configuration* page that provides an interface to quickly configure the parameters and relevant register settings for the respective AFEx32A3W device. The *High Level Configuration* page consists of the *Basic DAC* subpage.

| ile Debug Tools Help                                                            | ⊠ Demo Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | G |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| ages                                                                            | AFE532A3W - Basic DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | U |

| ♦ High Level Configuration<br>AFE532A3W + Basic DA<br>< Low Level Configuration | Device Settings     Internal Reference Enable   Disabled     Disabled   Disabled     DAC Settings   DACO Settings     DACO Clear Select   DACO Sync Config     DAC1 Clear Select   DAC0 Sync Config     DAC1 Clear Select   DAC1 Sync Config     DAC1 Clear Select   DAC1 Sync Config     DAC1 Clear Select   DAC1 Sync Config     DAC2 Corescale   DASynchronous     DAC2 Clear Select   DAC2 Sync Config     DAC2 Settings   DAC2 Sync Config     DAC2 Clear Select   DAC2 Sync Config     DAC2 Settings   DAC2 Sync Config     DAC2 Settings   DAC2 Sync Config     DAC2 Settings   DAC3 Settings     DAC2 Settings   DAC3 Settings     DAC2 Settings   DAC3 Settings     DAC2 Settings   DAC3 Settings |   |

|                                                                                 | DAC0 Power Down   DAC0 Gain   DAC0 Data   ADC Enable   CMP1 Input Type     DAC0   Power-down VOUT with<br>Hi-Z   Gain = 1x, VDD as reference   000   DAC1 Data   ADC Averaging   Invert CMP1     DAC1   Power-down VOUT with<br>Hi-Z   DAC1 Gain   DAC1 Data   ADC Averaging   Invert CMP1     DAC1   Power-down VOUT with<br>Hi-Z   DAC1 Gain   DAC1 Data   ADC Reserved Bits   Disabled   Disabled     DAC2 Power Down   DAC2 Gain   DAC2 Data   ADC Power Disabled   Disabled   Disabled     DAC2   Power-down IOUT with<br>Hi-Z   DAC2 Gain   DAC2 Data   ADC Trigger   ADC Data     ADC Trigger   ADC Data   Not Triggered   ADC Data   ADC Trigger   ADC Data                                        |   |

| *                                                                               | Device ID NVM Settings GPIO Controls   × 1 READ Program NVM Reload NVM DAC_GPIO Ø GPIO3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

Figure 3-6. High Level Configuration Page

### 3.2.2.1.1 Basic DAC Subpage

Figure 3-7 shows the *Basic DAC* subpage that provides an interface to quickly power up, select the reference and output span, program the output voltage or current, and configure the ADC for the respective AFEx32A3W device. The *Basic DAC* subpage also provides controls to configure the GPIO pin on the respective AFEx32A3W device, and control the two GPIO outputs of the AFE532A3WEVM onboard controller. The register settings can be programmed or retrieved using the *Program NVM* or *Reload NVM* checkboxes, respectively.

| SMART-DAC-EVM-GUI                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                                     |         | ×   |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------|-----|

| File Debug Tools Help                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |         |     |

|                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 🗹 Dem                                 | no Mode | ?   |

| Pages<br>⇒ High Level Configuration<br>↓ AFE532A3W- Basic DA<br>⇒ Low Level Configuration | AFE532A3W - Basic DAC     Device Settings   SDO Enable     Disabled   Disabled     DAC Settings   DAC0 Sync Config     DAC0 Clear Select   DAC0 Sync Config     DAC1 Clear Select   DAC1 Sync Config     DAC2 Even-scale   DAC3 sync Config     DAC2 Clear Select   DAC3 Sync Config     DAC2 Strings   DAC2 Sync Config     DAC2 Clear Select   DAC3 Sync Config     DAC2 Clear Select   DAC3 Sync Config     DAC2 Clear Select   DAC2 Sync Config     DAC2 Clear Select   DAC2 Sync Config     DAC2 Clear Select   DAC2 Sync Config     DAC2 Clear Select   DAC3 Sync Config     DAC2 Draver down VOUT with   Gain = 1x, VDD as reference     DAC0 Power down   DAC0 Gain     DAC1 Power down VOUT with   DAC1 Gain     DAC2 Power down   DAC1 Gain     DAC2 Power down VOUT with   DAC2 Gain     DAC2 Power down VOUT with   DAC2 Gain     DAC2 Power down NOUT with   DAC2 Gain     DAC2 Power down NOUT with   DAC2 Gain     DAC2 Power down NOUT with   DAC2 Gain     DAC2 Clear Bits   CMP Output I< | 2 Enable<br>led<br>ype<br>d<br>Enable |         |     |

|                                                                                           | × 1 READ Program NVM Reload NVM DAC_GPIO GPI03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       |         |     |

|                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |         |     |

| Idle                                                                                      | 🔵 DEMO MODE 🐺 TE:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | xas Ins                               | TRUME   | NTS |

Figure 3-7. Basic DAC Subpage

### 3.2.2.2 Low Level Configuration Page

Figure 3-8 shows the *Low Level Configuration* page. This subpage allows access to low-level communication directly with the respective AFEx32A3W device registers. Select a register on the *Register Map* list to show a description of the values in that register, as well as information on the register address, default value, size, and current value. Data are written to the registers by entering a value in the value column of the GUI.

| s A High Level Configuration                    | Write Selected Write Modified Read Selected Read All Update Mode Immediate |              |                  |            |          |                  |    |      |      |    |    |   |     |            |             |

|-------------------------------------------------|----------------------------------------------------------------------------|--------------|------------------|------------|----------|------------------|----|------|------|----|----|---|-----|------------|-------------|

| AFE532A3W - Basic DA<br>Low Level Configuration | Register Map                                                               |              |                  |            |          |                  |    |      |      |    |    |   |     | Field View |             |

|                                                 | Register Name                                                              | Address      | Default          | Mode       | Size     | Value            | 15 | 14 1 | 3 12 | 11 | 10 | 9 | 8 🔺 | Field Name | Field Value |

|                                                 | Registers                                                                  |              |                  |            |          |                  |    |      |      |    |    |   |     |            |             |

|                                                 | NOP                                                                        | 0x00         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | DAC_2_MARGIN_HIGH                                                          | 0x01         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | DAC_2_MARGIN_LOW                                                           | 0x02         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | DAC_2_GAIN_CONFIG                                                          | 0x03         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | DAC_2_FUNC_CONFIG                                                          | 0x06         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | DAC_2_FUNC_CONFIG                                                          | 0x06         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | DAC_0_MARGIN_HIGH                                                          | 0x0D         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | DAC_0_MARGIN_LOW                                                           | 0x0E         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | DAC_0_GAIN_CONFIG                                                          | 0x0F         | 0x0000           | R/W        | 16       | 0x0000           |    |      |      |    | 0  |   | 0   |            |             |

|                                                 | DAC_0_FUNC_CONFIG                                                          | 0x12         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | DAC_0_FUNC_CONFIG                                                          | 0x12         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | DAC_1_MARGIN_HIGH                                                          | 0x13         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | DAC_1_MARGIN_LOW                                                           | 0x14         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      | 0  | 0  |   | 0   |            |             |

|                                                 | DAC_1_GAIN_CMP_CC                                                          | 0x15         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | DAC_1_CMP_MODE_C                                                           | 0x17         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | DAC_1_FUNC_CONFIG                                                          | 0x18         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | DAC_1_FUNC_CONFIG                                                          | 0x18         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | DAC_2_DATA                                                                 | 0x19         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | DAC_0_DATA                                                                 | 0x1B         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | DAC_1_DATA                                                                 | 0x1C         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | ADC_CONFIG_TRIG                                                            | 0x1D         | 0x03C0           | R/W        | 16       | 0x03C0           |    | 0 0  |      |    | 0  |   |     |            |             |

|                                                 | ADC_DATA                                                                   | 0x1E         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | COMMON_CONFIG                                                              | 0x1F         | 0x0FFF           | R/W        | 16       | 0x0FFF           |    | 0 0  |      |    | 1  |   | 1   |            |             |

|                                                 | COMMON_TRIGGER                                                             | 0x20         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | COMMON_DAC_TRIGG                                                           | 0x21         | 0x0000           | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | GENERAL_STATUS                                                             | 0x22         | 0x0004           | R          | 16       | 0x0004           |    | 0 0  |      |    | 0  |   |     |            |             |

|                                                 | CMP_STATUS                                                                 | 0x23         | 0x0000           | R<br>R/W   | 16       | 0x0000           |    |      |      |    | 0  |   | 0   |            |             |

|                                                 | GPIO_CONFIG                                                                | 0x24<br>0x25 | 0x0000<br>0x0000 | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | DEVICE_MODE_CONFI<br>INTERFACE_CONFIG                                      |              | 0x0000<br>0x0000 | R/W        | 16       | 0x0000           |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 |                                                                            | 0x26         |                  |            | 16       | 0x0000           |    |      |      |    |    |   |     |            |             |

|                                                 | SRAM_CONFIG                                                                | 0x2B<br>0x2C | 0x0000<br>0x0000 | R/W<br>R/W | 16<br>16 | 0x0000<br>0x0000 |    | 0 0  |      |    | 0  |   | 0   |            |             |

|                                                 | SRAM_DATA                                                                  | 0x2C         | 0x0000           | R/W        | 10       | 000000           | 0  | 0 0  | 0 0  | 0  | 0  | 0 |     |            |             |

|                                                 | Register Description                                                       |              |                  |            |          |                  |    |      |      |    |    |   |     |            |             |

|                                                 | Register Description                                                       |              |                  |            |          |                  |    |      |      |    |    |   |     |            |             |

|                                                 |                                                                            |              |                  |            |          |                  |    |      |      |    |    |   |     |            |             |

|                                                 |                                                                            |              |                  |            |          |                  |    |      |      |    |    |   |     |            |             |

|                                                 |                                                                            |              |                  |            |          |                  |    |      |      |    |    |   |     |            |             |

Figure 3-8. Low Level Configuration Page

To store the values of the register map locally, select *Save Configuration* under the *File* menu option. The stored configuration files can be recalled and loaded by selecting *Open Configuration*.

Figure 3-9 shows the four configuration buttons provided on the *Low Level Configuration* page that allow the user to read from and write to the device registers:

- Write Selected

- Write Modified

- Read Selected

- Read All

The **Write Modified** button is enabled only in *Deferred Update Mode*. *Deferred Update Mode* initiates a write operation only when the **Write Selected** or **Write Modified** buttons are pressed. By default, *Immediate Update Mode* is selected for the *Low Level Configuration* page write operations.

| Write Selected | Write Modified | Read Selected | Read All | Update Mode Immediate | ▼ |

|----------------|----------------|---------------|----------|-----------------------|---|

|                |                |               |          |                       |   |

# **4 Hardware Design Files**

4.1 Schematics

J20 SDO - GPIO

Interface selection I2C / SPI

DAC GPIO

C21 1µF 16V

U\_DC261A\_Hardware DC261A Hardware.SchDo

Figure 4-1. AFE532A3WEVM Schematic Page 1

Figure 4-2. AFE532A3WEVM Schematic Page 2

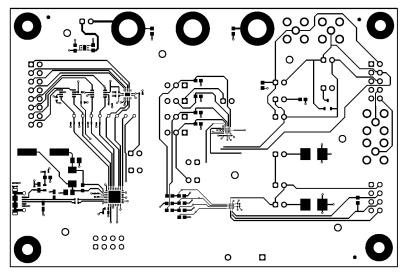

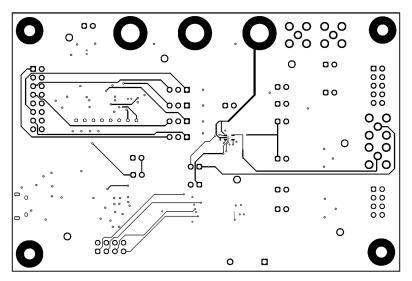

# 4.2 PCB Layout

Figure 4-3. AFE532A3WEVM PCB Layer 1

Figure 4-4. AFE532A3WEVM PCB Layer 2

# 4.3 Bill of Materials

### Table 4-1. AFE532A3WEVM Bill of Materials

| Designator                                                     | Quantity | Value   | Description                                                                           | Package Reference                               | Part Number         | Manufacturer                   |  |

|----------------------------------------------------------------|----------|---------|---------------------------------------------------------------------------------------|-------------------------------------------------|---------------------|--------------------------------|--|

| !PCB1                                                          | 1        |         | Printed Circuit Board                                                                 |                                                 | DC261               | Any                            |  |

| C2, C3, C5                                                     | 3        | 0.1 µF  | CAP, CERM, 0.1 µF, 6.3 V, +/- 10%, X5R, 0201                                          | 0201                                            | GRM033R60J104KE19D  | MuRata                         |  |

| C4, C6                                                         | 2        | 2.2 µF  | CAP, CERM, 2.2 µF, 6.3 V, +/- 20%, X5R, 0201                                          | Samsung Electro-<br>Mechanics                   |                     |                                |  |

| C7, C8, C10, C12, C13,<br>C14, C15, C17                        | 8        | 0.1 µF  | CAP, CERM, 0.1 µF, 25 V,+/- 10%, X7R, 0402                                            | Yageo                                           |                     |                                |  |

| C9, C16                                                        | 2        | 4.7 µF  | CAP, CERM, 4.7 µF, 10 V, +/- 20%, X7R, 0603                                           |                                                 |                     |                                |  |

| C11                                                            | 1        | 100 pF  | CAP, CERM, 100 pF, 50 V, +/- 10%, X7R, 0402                                           | 0402                                            | 885012205055        | Wurth Elektronik               |  |

| C18, C19                                                       | 2        | 18 pF   | CAP, CERM, 18 pF, 50 V, +/- 5%, C0G/NP0, 0805                                         | 0805                                            | 08055A180JAT2A      | AVX                            |  |

| C20, C21, C22, C23                                             | 4        | 1 µF    | CAP, CERM, 1 µF, 16 V, +/- 10%, X7R, 0603                                             | 0603                                            | 885012206052        | Wurth Elektronik               |  |

| D1, D2, D3                                                     | 3        | 24 V    | PulseGuard ESD Suppressor, 24VDC, SMT                                                 | 0603 TVS Diode                                  | PGB1010603MR        | Littelfuse                     |  |

| H1, H2, H3, H4                                                 | 4        |         | Machine Screw, Round, #4-40 x 1/4, Nylon,<br>Philips panhead Screw NY PMS 440 0025 PH |                                                 | B&F Fastener Supply |                                |  |

| H5, H6, H7, H8                                                 | 4        |         | Standoff, Hex, 0.5"L #4-40 Nylon                                                      | Standoff                                        | 1902C               | Keystone                       |  |

| J1, J2, J3, J4, J5, J6, J7, J8,<br>J9, J10, J12, J14, J18, J27 | 14       |         | Header, 100mil, 2x1, Gold, TH                                                         | 2x1 Header                                      | TSW-102-07-G-S      | Samtec                         |  |

| J11                                                            | 1        |         | Receptacle, USB 2.0, Micro-USB Type B,<br>R/A, SMT                                    | USB-micro B USB 2.0,<br>0.65mm, 5 Pos, R/A, SMT |                     | FCI                            |  |

| J15, J16, J17                                                  | 3        |         | Standard Banana Jack, Uninsulated, 5.5mm                                              | Keystone_575-4 575-4 K                          |                     | Keystone                       |  |

| J20, J23, J25, J29                                             | 4        |         | Header, 100mil, 3x1, Gold, TH                                                         | PBC03SAAN                                       | PBC03SAAN           | Sullins Connector<br>Solutions |  |

| J22                                                            | 1        |         | Header, 100mil, 8x2, Gold, TH                                                         |                                                 |                     | Sullins Connector<br>Solutions |  |

| J24                                                            | 1        |         | Header, 100mil, 5x2, Gold, TH                                                         | 5x2 Header                                      | TSW-105-07-G-D      | Samtec                         |  |

| J26, J28                                                       | 2        |         | Header, 2.54mm, 4x2, Gold, TH                                                         | Header, 2.54mm, 4x2, TH                         | TSW-104-08-L-D      | Samtec                         |  |

| J32                                                            | 1        |         |                                                                                       | JUMPER2                                         | D3082-05            | Harwin                         |  |

| L1                                                             | 1        | 600 Ω   | Ferrite Bead, 600 ohm @ 100 MHz, 1 A, 0603 782633601                                  |                                                 | Wurth Elektronik    |                                |  |

| R1                                                             | 1        | 10.0 kΩ | RES, 10.0 kΩ, 1%, 0.1 W, 0603                                                         | 0603                                            | RCG060310K0FKEA     | Vishay Draloric                |  |

| R2, R8                                                         | 2        | 10 kΩ   | 10 kΩ ±1% 0.05W, 1/20W Chip Resistor<br>0201 (0603 Metric) - Thick Film               | 0201                                            | RMCF0201FT10K0      | Stackpole                      |  |

| R3, R4, R5, R6, R18                                            | 5        | 3.32 kΩ | RES, 3.32 kΩ, 1%, 0.1 W, 0603                                                         | 0603                                            | RC0603FR-073K32L    | Yageo                          |  |

### Table 4-1. AFE532A3WEVM Bill of Materials (continued)

| Designator                           | Quantity | Value   | Description                                                                                                                 | Package Reference                                         | Part Number               | Manufacturer              |  |

|--------------------------------------|----------|---------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------|---------------------------|--|

| R7, R12                              | 2        | 4.99 Ω  | $4.99 \ \Omega \pm 1\%$ 2W Chip Resistor 2512 (6432 Metric) Moisture Resistant Thick Film                                   | 2512                                                      | RHC2512FT4R99             | Stackpole Electronics Inc |  |

| R10, R11, R17                        | 3        | 0 Ω     | RES, 0 Ω, 0%, 0.25 W, AEC-Q200 Grade 0, 0603                                                                                | 0603                                                      | RCS06030000Z0EA           | Vishay-Dale               |  |

| R19, R26, R29                        | 3        | 10.0 kΩ | RES, 10.0 kΩ, 1%, 0.063 W, AEC-Q200<br>Grade 0, 0402                                                                        | RMCF0402FT10K0                                            | Stackpole Electronics Inc |                           |  |

| R20                                  | 1        | 12 kΩ   | $12\ k\Omega\ \pm 1\%\ 0.1W,\ 1/10W$ Chip Resistor 0402 (1005 Metric) Automotive AEC-Q200 Thick Film                        | 1005 Metric) Automotive AEC-Q200 Thick 0402 ERJ-2RKF1202X |                           |                           |  |

| R21, R22                             | 2        | 10 Ω    | RES, 10.0 Ω, 1%, 0.063 W, 0402                                                                                              | 0402                                                      | RK73H1ETTP10R0F           | KOA Speer                 |  |

| R23                                  | 1        | 330 Ω   | RES, 330 Ω, 1%, 0.1 W, AEC-Q200 Grade 0, 0402                                                                               | 0402                                                      | ERJ-2RKF3300X             | Panasonic                 |  |

| R24, R25, R27, R28                   | 4        | 3.30 kΩ | RES, 3.30 kΩ, 1%, 0.063 W, AEC-Q200<br>Grade 0, 0402                                                                        | 0402                                                      | RK73H1ETTP3301F           | KOA Speer                 |  |

| R30                                  | 1        | 1.00 MΩ | RES, 1.00 MΩ, 1%, 0.1 W, AEC-Q200<br>Grade 0, 0603                                                                          |                                                           |                           |                           |  |

| TP1, TP2, TP3, TP4, TP5,<br>TP6, TP7 | 7        |         | Test Point, Compact, Black, TH Black Compact Testpoint 5006                                                                 |                                                           | Keystone Electronics      |                           |  |

| U1, U2                               | 2        |         | AFE532A3YBHR                                                                                                                | DSBGA16                                                   | AFE532A3YBHR              | Texas Instruments         |  |

| U3                                   | 1        |         | Single, 5.5-V, 3-MHz high-output-current<br>(150 mA) fast-shutdown (1 µs) operational<br>amplifier 5-SC70 -40 to 125        |                                                           | Texas Instruments         |                           |  |

| U5                                   | 1        |         | USB Bridge, USB to I <sup>2</sup> C/SPI USB 2.0 I <sup>2</sup> C,<br>SPI 32-VQFN (5x5) VQFN32 FT4222HQ-D-R                  |                                                           | FTDI                      |                           |  |

| U6                                   | 1        |         | 4-Bit Fixed Direction Voltage-Level<br>Translator with Schmitt- Trigger Inputs, and<br>Tri-State Outputs, WQFN14 TXU0304BQA |                                                           | Texas Instruments         |                           |  |

| U7, U8                               | 2        |         | Voltage Level Translator Bidirectional 1<br>Circuit 2 Channel 24Mbps SM8                                                    |                                                           |                           | Texas Instruments         |  |

| U9                                   | 1        |         | 500 mA LDO, DRV0006A (WSON-6)                                                                                               | DRV0006A                                                  | TLV75533PDRVR             | Texas Instruments         |  |

| Y1                                   | 1        |         | Crystal, 12 MHz, 18 pF, SMD                                                                                                 | ABM3                                                      | ABM3-12.000MHZ-B2-T       | Abracon Corporation       |  |

| C1                                   | 0        | 0.47 µF | CAP, CERM, 0.47 μF, 16 V, +/- 10%, X7R, 0603     0603     C0603C474K4RACTU                                                  |                                                           | Kemet                     |                           |  |

| J13                                  | 0        |         | Header, 2.54mm, 8x1, Gold, TH                                                                                               | Header, 2.54mm, 8x1, TH                                   | TS-108-G-AA               | Samtec                    |  |

| J19, J21, J30, J31                   | 0        |         | SMA                                                                                                                         | SMA                                                       | 142-0701-201              | Cinch Connectivity        |  |

| Q1                                   | 0        | 12 V    | Transistor, NPN, 12 V, 2 A, SOT-23                                                                                          | SOT-23                                                    | NSS12201LT1G              | ON Semiconductor          |  |

| R13, R14, R15, R16                   | 0        | 3.32 kΩ | RES, 3.32 kΩ, 1%, 0.1 W, 0603                                                                                               | 0603                                                      | RC0603FR-073K32L          | Yageo                     |  |

| U4                                   | 0        |         | 5-MHz, 15-V/µs High Slew-Rate, RRIO Op<br>Amp                                                                               | X2SON5                                                    | OPA310IDPWR               | Texas Instruments         |  |

# Table 4-1. AFE532A3WEVM Bill of Materials (continued)

| Designator | Quantity | Value | Description                         | Package Reference | Part Number           | Manufacturer        |

|------------|----------|-------|-------------------------------------|-------------------|-----------------------|---------------------|

| Y2         | 0        |       | Crystal, 12 MHz, 30 ppm, 18 pF, SMD | 11.4x4.7mm        | ABLS2-12.000MHZ-D4Y-T | Abracon Corporation |

# TEXAS INSTRUMENTS www.ti.com

# **5** Additional Information

# Trademarks

Windows<sup>™</sup> is a trademark of Microsoft Corporation. LabVIEW<sup>™</sup> is a trademark of National Instruments. All trademarks are the property of their respective owners.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated