# TAS3103AEVM

### **Evaluation Module for the TAS3103A Digital Audio Signal Processor**

# **User's Guide**

Literature Number: SLEU087 February 2007

## Contents

| Prefa | ace      |                                                  | 5  |

|-------|----------|--------------------------------------------------|----|

| 1     | Over     | view                                             | 7  |

|       | 1.1      | TAS3103A EVM Features                            | 8  |

|       | 1.2      | PCB Configuration                                | 9  |

| 2     | Quic     | k Setup Guide                                    | 11 |

|       | 2.1      | Electrostatic Discharge Warning                  | 12 |

|       | 2.2      | Default EVM Configuration                        | 12 |

|       | 2.3      | Load Configuration from EEPROM                   | 14 |

|       | 2.4      | Analog Input Configuration                       | 15 |

|       | 2.5      | Initializing the TAS3103A                        | 16 |

| 3     | Syste    | em Interfaces                                    | 17 |

|       | 3.1      | Digital Audio Interface: Input (J2), Output (J5) |    |

|       | 3.2      | Jumper Settings                                  | 18 |

|       |          | 3.2.1 Over Sample Rate (JP1)                     | 18 |

|       |          | 3.2.2 Clock Jumpers                              | 18 |

|       |          | 3.2.3 Clk1 Jumper – Master Clock Selection       | 19 |

|       |          | 3.2.4 Data Jumpers                               | 19 |

|       |          | 3.2.5 Clock Control                              | 19 |

|       |          | 3.2.6 Device Address                             | 20 |

|       |          | 3.2.7 I <sup>2</sup> C Master/Slave              | 20 |

| 4     | Sche     | matics                                           | 21 |

| Impo  | ortant N | lotices                                          | 27 |

### List of Figures

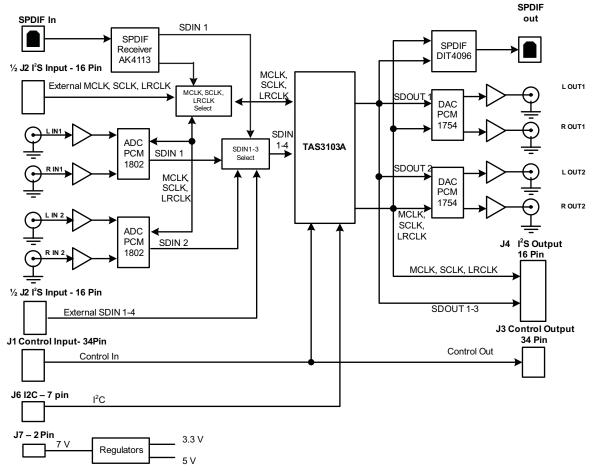

| TAS3103A EVM Block Diagram                                   | . 8                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TAS3103A EVM Components                                      | 10                                                                                                                                                                                                                                                                                                                                                                                                           |

| Default Configuration                                        | 13                                                                                                                                                                                                                                                                                                                                                                                                           |

| Load Configuration Data From EEPROM                          | 14                                                                                                                                                                                                                                                                                                                                                                                                           |

| Enable Analog Input Configuration                            | 15                                                                                                                                                                                                                                                                                                                                                                                                           |

| TAS3103A EVM Schematic – S/PDIF Input                        | 22                                                                                                                                                                                                                                                                                                                                                                                                           |

| TAS3103A EVM Schematic – Reset/I <sup>2</sup> C              | 23                                                                                                                                                                                                                                                                                                                                                                                                           |

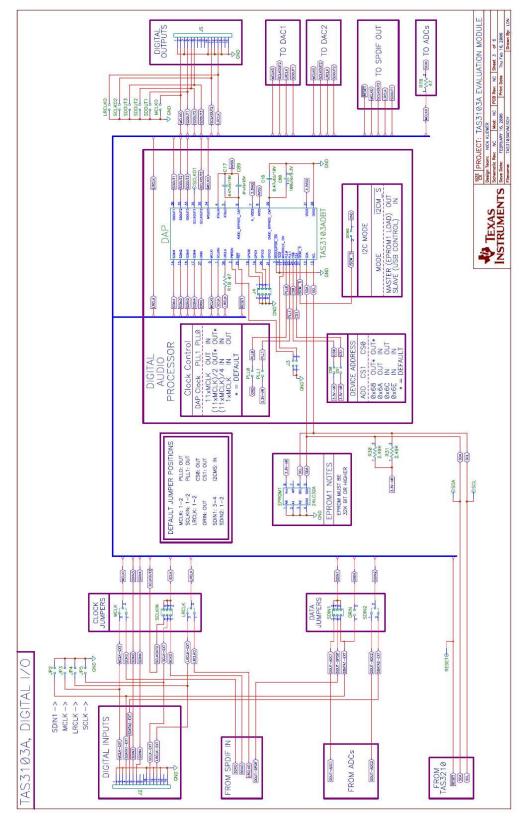

| TAS3103A EVM Schematic – TAS3103A, Digital I/O               | 24                                                                                                                                                                                                                                                                                                                                                                                                           |

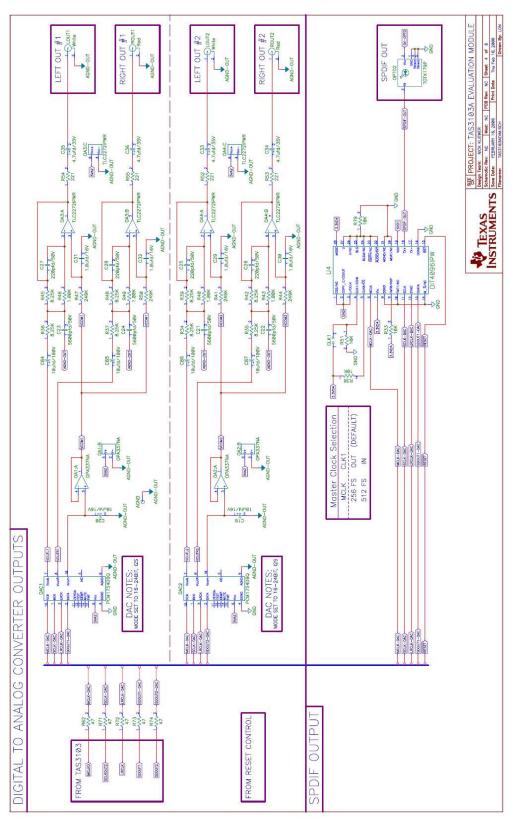

| TAS3103A EVM Schematic – Digital-to-Analog Converter Outputs | 25                                                                                                                                                                                                                                                                                                                                                                                                           |

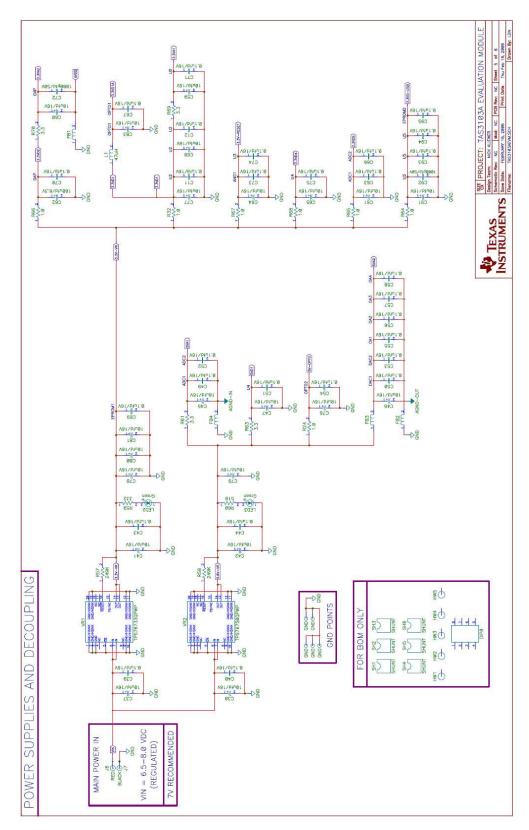

| TAS3103A EVM Schematic – Power Supplies and Decoupling       | 26                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                              | TAS3103A EVM Block Diagram<br>TAS3103A EVM Components<br>Default Configuration Data From EEPROM<br>Enable Analog Input Configuration<br>TAS3103A EVM Schematic – S/PDIF Input<br>TAS3103A EVM Schematic – Reset/I <sup>2</sup> C<br>TAS3103A EVM Schematic – TAS3103A, Digital I/O<br>TAS3103A EVM Schematic – Digital-to-Analog Converter Outputs<br>TAS3103A EVM Schematic – Power Supplies and Decoupling |

### List of Tables

| 3-1 | J2 and J5 Pin Descriptions    | 18 |

|-----|-------------------------------|----|

| 3-2 | Master Clock Rate             | 19 |

| 3-3 | Clock Control                 | 19 |

| 3-4 | Device Address                | 20 |

| 3-5 | I <sup>2</sup> C Master/Slave | 20 |

Preface SLEU087–February 2007

#### About This Manual

This manual describes the operation of the TAS3103AEVM evaluation module from Texas Instruments.

#### How to Use This Manual

This document contains the following chapters:

Chapter 1: Overview Chapter 2: Quick Setup Guide Chapter 3: System Interfaces

Chapter 4: Schematics

#### **Information About Cautions and Warnings**

This book may contain cautions and warnings.

#### CAUTION

This is an example of a caution statement.

A caution statement describes a situation that could potentially damage your software or equipment.

### WARNING

This is an example of a warning statement.

A warning statement describes a situation that could potentially cause harm to you.

The information in a caution or a warning is provided for your protection. Please read each caution and warning carefully.

#### **Related Documentation From Texas Instruments**

The following data manuals have detailed descriptions of the integrated circuits used in the design of the TAS3103AEVM.

| PART NUMBER | LITERATURE NUMBER |

|-------------|-------------------|

| TAS3103A    | <u>SLES166</u>    |

| PCM1802     | SLES023           |

| PCM1754     | SLES092           |

PurePath is a trademark of Texas Instruments.

#### **FCC Warning**

This equipment is intended for use in a laboratory test environment only. It generates, uses, and can radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to subpart J of part 15 of FCC rules, which are designed to provide reasonable protection against radio frequency interference. Operation of this equipment in other environments may cause interference with radio communications, in which case the user at his own expense will be required to take whatever measures may be required to correct this interference.

The TAS3103A is a 48-bit single-chip 3-channel digital audio playback processor with integrated audio processing for speaker equalization, dual-band dynamics processing (compressor/expander/limiter/noise gate), delay compensation, and spatial enhancement. These algorithms can be used to compensate for real-world limitations of speakers, amplifiers, and listening environments, resulting in a dramatic improvement of the reproduced audio quality. The TAS3103A EVM is an evaluation board for the TAS3103A digital audio processor.

The TAS3103A EVM permits evaluation and demonstration of the TAS3103A 3-channel 48-bit digital audio processor.

TAS3103A applications include digital televisions, home theater systems, mini-component audio systems, and professional audio.

A TI PurePath<sup>™</sup> digital amplifier EVM can be connected to the TAS3103A EVM digital output, enabling the TAS3103A to drive a loudspeaker. Examples of EVMs that can be connected include, but are not limited to, TAS5508-5142K7EVM, TAS5518-5152K8EVM, TAS5518-5182C8EVM, and TAS5086-5186V6EVM. This system is designed for home theater applications such as A/V receivers, DVD mini component systems, home theater in a box (HTIB), DVD receivers, or plasma display panels (PDP).

#### Topic

Page

| 1.1 | TAS3103A EVM Features | 8 |

|-----|-----------------------|---|

| 1.2 | PCB Configuration     | 9 |

7

#### 1.1 TAS3103A EVM Features

The TAS3103A EVM contains a TAS3103A processor, a signal input interface, an output signal interface, and a power supply.

The EVM accepts input signals in three formats:

- Two-channel optical S/PDIF format

- Four-channel RCA analog inputs into two PCM1802 ADCs, 102-dB DYR-A weighted

- Four digital serial inputs (eight channels) that support left-justified, right-justified, I<sup>2</sup>S, or DSP modes

The TAS3103A EMC provides outputs in three formats:

- Optical S/PDIF format

- Four-channel RCA analog outputs from two PCM1754 DACs, 106-dB DYR-A weighted

- Three digital serial outputs (six channels) that support left-justified, right-justified, I<sup>2</sup>S, or DSP modes

The internal signal processing program and parameters of the TAS3103A can be controlled by a computer parallel-port driven  $I^2C$  interface, a PC-USB to  $I^2C$  interface, or a command-and-control GUI.

Power requirements are 6.5 V to 8 V  $\pm$  5% dc. On-board regulators provide separate supplies for the digital and analog sections.

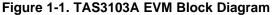

#### **1.2 PCB Configuration**

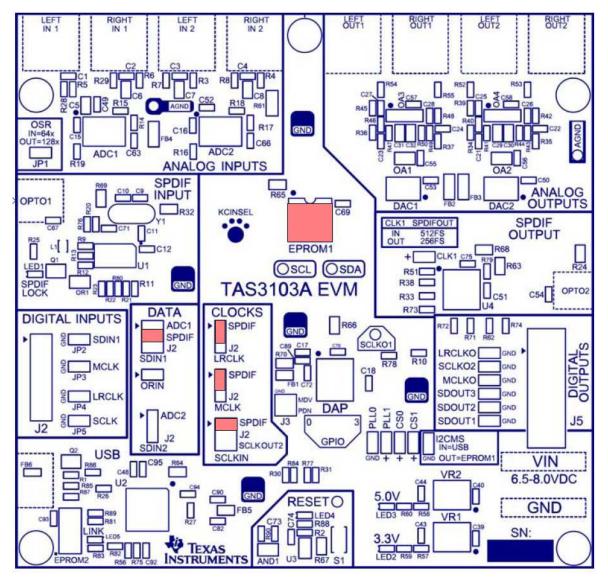

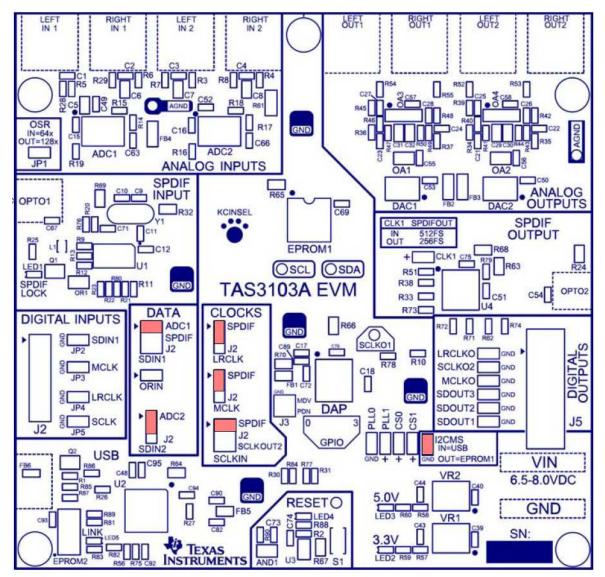

The following components are on the EVM board:

- The TAS3103A device is located at U1 (also labled DAP).

- The EEPROM adjacent to U1 is used for program and coefficient storage.

- LED2 and LED3 are green LEDs that indicate that the power supply voltage is within specification and that the device is out of RESET.

- Blue LED 1 indicates that the board is receiving a valid S/PDIF signal and the S/PDIF lock has been achieved by the AK4113.

- Switch SW1 is a momentary switch that can be used to apply reset to the TSA3103A.

- LED4 is an orange LED that indicates the TAS3103A is receiving an active-low reset.

The following input ports are available on the EVM:

• S/PDIF Input

TOSLINK input optical connector supporting sampling rates up to 96 kHz.

- Four analog line-in channels

Two TI Burr-Brown PCM1802 ADCs (24 bit, 96 kHz, stereo) provide the four channels. Each ADC is provided with separate left-channel and right-channel RCA input jacks.

- Digital input header (J2, which contains JP2, JP3, JP4, and JP5) Provides the means of inputting four serial data sources (SDIN1, SDIN2, SDIN3, SDIN4) and three clocks (MCLK, SCLK, and LRCLK). J2 is a 16-pin box header that is compatible with most of the PurePath digital amplifier boards.

- USB port for connection to the PC (J1) This TUSB3210 provides a translation between the PC-USB interface and the I<sup>2</sup>C interface of the TAS3103A.

- Coaxial jack power connector

The following output ports are available on the EVM:

• S/PDIF out

TOSLINK optical connector providing sample rates as high as 96 kHz. This outputs the TAS3103A SDOUT1 signal. This output is active at all times.

Four analog line-out channels

Two TI Burr-Brown PCM1754 DACs (24 bit, 96 kHz, stereo) provide the four channels. Each DAC output is available through separate left-channel and right-channel RCA jacks. These receive inputs from the TAS3103A SDOUT1 and SDOUT2. This output is active at all times.

- Digital output header (J5, which contains MCLKO, SCLO2, LRCLKO, SDOUT1, SDOUT2, SDOUT3) This header provides the output of three serial data sources (SDOUT1, SDOUT2, and SDOUT3) and three clocks (MCLK, SCLK, and LRCLK). J5 is a 16-pin box header that is compatible with most PurePath digital amplifier boards. This output is active at all times.

- GPIO header (on underside of board) Provides access to the four (4) GPIO ports provided by the TAS3103A. The output header is a 2×4-pin open header.

The board requires only one 7-V to 8-V  $\pm$  5% 650-mA power source. The power is supplied though coaxial connector. The center is positive voltage. From this input power source, the EVM provides power to I<sup>2</sup>C paddle board via the provided I<sup>2</sup>C cable. The paddle board is used as an interface between a PC parallel port and the I<sup>2</sup>C port on the EVM. The paddle board is provided with the EVM.

All clocks can be supplied by the board, or the user can choose to input clocks via the I<sup>2</sup>S input header.

Internally, all devices are configured to the I<sup>2</sup>S data format. When using the S/PDIF receiver or the ADCs to input data, the I<sup>2</sup>S output header outputs I<sup>2</sup>S formatted data.

When using the I<sup>2</sup>S input header to source data to the EVM and using either the S/PDIF transmitter or the DAC to output data, the data on the I<sup>2</sup>S output header is I<sup>2</sup>S formatted data. However, when using the I<sup>2</sup>S input header to source data to the EVM and the I<sup>2</sup>S output header to output the data, any of the data formats supported by the TAS3103A can be used.

To support the I<sup>2</sup>S input and output 24-bit format, set register F9 to 0x01 0x00 0x01 0x22.

Figure 1-2. TAS3103A EVM Components

The TAS3103A EVM has several configuration options that permit the user to configure the TAS3103A to meet a variety of system configuration requirements.

| Торіс |                                 | Page |

|-------|---------------------------------|------|

| 2.1   | Electrostatic Discharge Warning | 12   |

|       | Electrostatic Discharge Warning |      |

| 2.2   | Default EVM Configuration       | 12   |

| 2.3   | Load Configuration from EEPROM  | 14   |

| 2.4   | Analog Input Configuration      | 15   |

| 2.5   | Initializing the TAS3103A       | 16   |

| 1     |                                 |      |

#### 2.1 Electrostatic Discharge Warning

Many of the components on the TAS3103A EVM are susceptible to damage by electrostatic discharge (ESD). Customers are advised to observe proper ESD handling precautions when unpacking and handling the EVM, including the use of a grounded wrist strap at an approved ESD workstation.

#### CAUTION

Failure to observe ESD handling procedures may result in damage to EVM components.

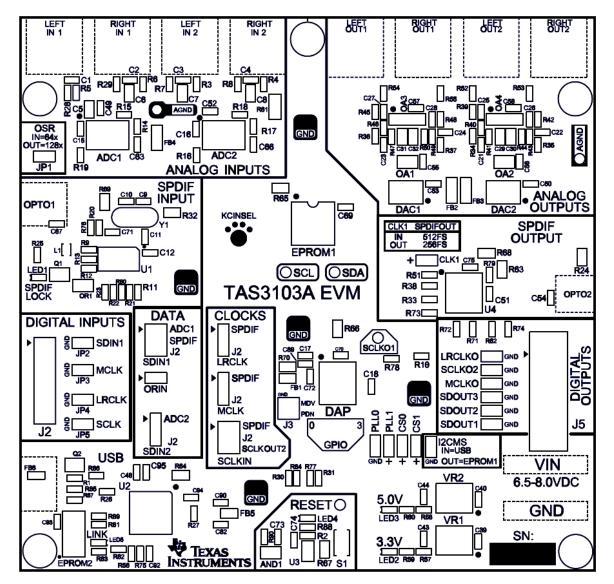

#### 2.2 Default EVM Configuration

As shipped, the TAS3103A EVM is configured as follows:

- I<sup>2</sup>C slave mode (does not obtain configuration from EEPROM)

- I<sup>2</sup>S clock slave mode

- MCLK, SCLK, and LRCLK provided by the S/PDIF receiver

- Input data is from S/PDIF receiver on SDIN1

- SPDIFOUT CLK is 256 Fs

- ADC oversampling rate is 128 Fs

- PLL clock is 11 × MCLK/2

- Device I<sup>2</sup>C address is 0x68

- ORIN is low

The TAS3103A analog, S/PDIF, and digital outputs are always enabled.

The default jumper settings are shown in Figure 2-1 (jumpers are shown in red).

Figure 2-1. Default Configuration

Load Configuration from EEPROM

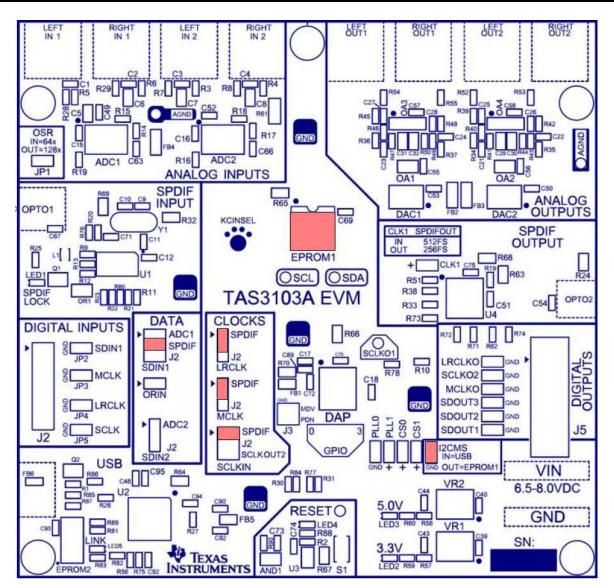

#### 2.3 Load Configuration from EEPROM

The TAS3103A EVM can be configured to boot up in I<sup>2</sup>C master mode and input the configuration settings from the EEPROM, using the configuration shown in Figure 2-2.

Figure 2-2. Load Configuration Data From EEPROM

#### 2.4 Analog Input Configuration

The TAS3103A EVM can be configured to use the analog inputs and a clock provided by the S/PDIF receiver, using the configuration shown in Figure 2-3.

Figure 2-3. Enable Analog Input Configuration

#### 2.5 Initializing the TAS3103A

Upon receiving a reset, the TAS3103A EVM starts operating in clock slave mode. The S/PDIF receiver, on the input board, is the MCLK clock master in this system.

To start up the TAS3103A EVM, use following procedure:

- 1. Insert the PurePath CD-ROM and, if it does not auto load, run the ReadMe file.

- a. Select Software in the menu on the left.

- b. Select the Digital Audio Processor Configuration Tool (DCT) 4.0 (USB).

- c. Follow the instructions to install the DCT.

- 2. Turn on all power supplies before connecting the USB interface.

- 3. Connect the USB interface and press the RESET button.

- 4. Ensure that blue LED on the EVM is on.

- 5. Start the DAS DCT software.

- 6. Load the TAS3103Example.dat file.

- 7. Ensure that the bottom status indication shows Ready. If not, recheck the power and USB connection.

- 8. Select Demo GUI or Debug GUI.

- 9. The EVM is ready to use.

**Note:** If using the TAS3103A EVM without using the DAS DCT software, the EVM can be set to stream audio from input to output by setting the serial interface format and volume.

To enable the TAS3103A to communicate to the S/PDIF receiver, S/PDIF transmitter, ADC, and DACs, the TAS3103A data interfaces must be set to 24-bit I<sup>2</sup>S mode. This is done for the clock slave mode by setting register F9 to 0x01 0x01 0x24 0x33.

After a reset, the default configuration of the TAS3103A sets volume 1, 2, and 3 to mute. The TAS3103A streams audio from SDIN1 to SDOUT1 when the volume at I<sup>2</sup>C addresses 0xF2 and 0xF3 are set to a desired gain value. A value of 1 is specified by 0x00 0x80 0x00 0x00.

Chapter 3 SLEU087–February 2007

# System Interfaces

This chapter describes the power supplies and system interfaces of the TAS3103A EVM board.

| Торіс      |                                                                     | Page |

|------------|---------------------------------------------------------------------|------|

| 3.1<br>3.2 | Digital Audio Interface: Input (J2), Output (J5)<br>Jumper Settings |      |

| J.Z        | Jumper Settings                                                     | 10   |

#### 3.1 Digital Audio Interface: Input (J2), Output (J5)

The digital audio interface contains digital audio signal data (I<sup>2</sup>S) and clocks. See the TAS3103A data manual (TI literature number <u>SLES166</u>) for signal timing and details not explained in this document.

| PIN |       | DECODIDITION                              |  |

|-----|-------|-------------------------------------------|--|

| NO. | NAME  | DESCRIPTION                               |  |

| 1   | GND   | Ground                                    |  |

| 2   | MCLK  | Master clock input                        |  |

| 3   | GND   | Ground                                    |  |

| 4   | SDIN1 | I <sup>2</sup> S data 1, channels 1 and 2 |  |

| 5   | SDIN2 | I <sup>2</sup> S data 2, channels 3 and 4 |  |

| 6   | SDIN3 | I <sup>2</sup> S data 3, channels 5 and 6 |  |

| 7   | SDIN4 | I <sup>2</sup> S data 4, channels 7 and 8 |  |

| 8   | -     | Reserved                                  |  |

| 9   | -     | Reserved                                  |  |

| 10  | GND   | Ground                                    |  |

| 11  | SCLK  | I <sup>2</sup> S bit clock                |  |

| 12  | GND   | Ground                                    |  |

| 13  | LRCLK | I <sup>2</sup> S left-right clock         |  |

| 14  | GND   | Ground                                    |  |

| 15  | _     | Reserved                                  |  |

| 16  | GND   | Ground                                    |  |

| Table 3-1 | . J2 and J5 | Pin | Descriptions |

|-----------|-------------|-----|--------------|

|-----------|-------------|-----|--------------|

#### 3.2 Jumper Settings

#### 3.2.1 Over Sample Rate (JP1)

When jumper JP1 is inserted, the ADC oversample rate is 64 Fs. When jumper JP1 is removed, the ADC oversample rate is 128 Fs.

#### 3.2.2 Clock Jumpers

The sources for MCLK, SCLK, and LRCLK to the TAS3103A are jumper selectable.

#### 3.2.2.1 MCLK

When MCLK pins 1-2 are connected, the MCLK source is the S/PDIF receiver.

When MCLK pins 2-3 are connected, the MCLK source is an external MCLK.

#### 3.2.2.2 SCLKIN

When SCLKIN pins 1-2 are connected, the SCLKIN source is the S/PDIF receiver.

When SCLKIN pins 3-4 are connected, the SCLKIN source is the external SCLK.

When SCLKIN pins 5-6 are connected, the SCLKIN source is SCLKOUT2 (for master clock mode).

#### 3.2.2.3 LRCLK

When LRCLK pins 1-2 are connected, the LRCLK source is the S/PDIF receiver. When LRCLK pins 3-4 are connected, the LRCLK source is an external LRCLK.

#### 3.2.3 Clk1 Jumper – Master Clock Selection

The master clock rate is selected by jumper CLK1 (see Table 3-2).

#### Table 3-2. Master Clock Rate

| MODE                                 | I2CMS |

|--------------------------------------|-------|

| Master clock rate = 256 Fs (default) | Out   |

| Master clock rate = 512 Fs           | In    |

#### 3.2.4 Data Jumpers

The sources for SDIN1, SDIN2, SDIN4, and ORIN to the TAS3103A are jumper selectable.

#### 3.2.4.1 SDIN1

When SDIN1 pins 1-2 are connected, the SDIN1 source is ADC1. When SDIN1 pins 3-4 are connected, the SDIN1 source is the S/PDIF receiver. When SDIN1 pins 5-6 are connected, the SDIN1 source is an external SDIN1.

#### 3.2.4.2 SDIN2

When SDIN2 pins 1-2 are connected, the SDIN1 source is ADC2.

When SDIN2 pins 3-4 are connected, the SDIN2 source is an external SDIN2.

#### 3.2.4.3 ORIN

When ORIN pins 1-2 are connected, the SDIN1 source is ADC2.

#### 3.2.5 Clock Control

The PLL divide ratios are set by PLL0 and PLL1 (see Table 3-3).

#### Table 3-3. Clock Control

| MODE               | PLL1 | PLL0 |

|--------------------|------|------|

| $11 \times MCLK$   | Out  | In   |

| $11 \times MCLK/2$ | Out  | Out  |

| 11 × MCLK/4        | In   | In   |

| MCLK               | In   | Out  |

#### 3.2.6 Device Address

The device address is set by CS0 and CS1 (see Table 3-4).

#### Table 3-4. Device Address

| MODE | CS1 | CS0 |

|------|-----|-----|

| 0x68 | Out | Out |

| 0x6A | Out | In  |

| 0x6C | In  | Out |

| 0x6E | In  | In  |

#### 3.2.7 I<sup>2</sup>C Master/Slave

The I<sup>2</sup>C mode is set by I2CMS (see Table 3-5).

#### Table 3-5. I<sup>2</sup>C Master/Slave

| MODE                      | I2CMS |  |

|---------------------------|-------|--|

| Master mode (EEPROM load) | Out   |  |

| Slave mode (slave load)   | In    |  |

Chapter 4 SLEU087–February 2007

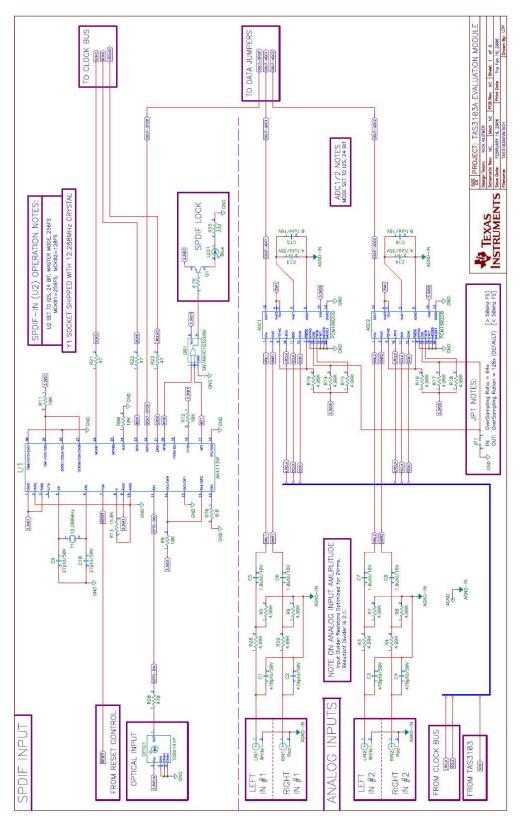

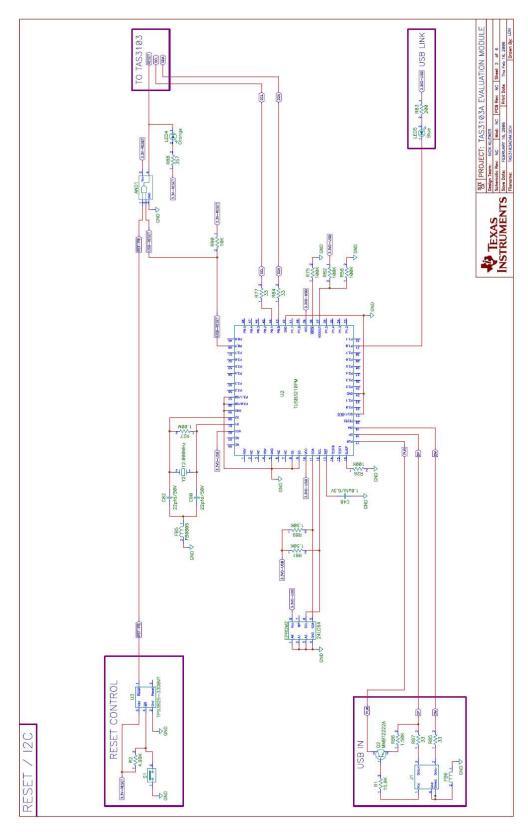

## **Schematics**

This chapter contains the TAS3103A EVM schematics.

Figure 4-1. TAS3103A EVM Schematic – S/PDIF Input

Figure 4-3. TAS3103A EVM Schematic – TAS3103A, Digital I/O

Figure 4-4. TAS3103A EVM Schematic – Digital-to-Analog Converter Outputs

#### **Schematic Disclaimer**

The preliminary schematic information and materials ("Materials") provided here are provided by Texas Instruments Incorporated ("TI") as a service to its customers and/or suppliers, and may be used for informational purposes only, and only subject to the following terms. By downloading or viewing these Materials, you are signifying your assent to these terms.

- These preliminary evaluation schematics are intended for use for PRELIMINARY ENGINEERING DEVELOPMENT AND EVALUATION PURPOSES ONLY and are not considered by Texas Instruments to be fit as a basis for establishing production products or systems. This information may be incomplete in several respects, including but not limited to information relating to required design, marketing, and/or manufacturing-related protective considerations and product safety measures typically found in the end-product incorporating the goods.

- 2. Accordingly, neither TI nor its suppliers warrant the accuracy or completeness of the information, text, graphics, links or other items contained within the Materials. TI may make changes to the Materials, or to the products described therein, at any time without notice. TI makes no commitment to update the Materials.

- 3. TI assumes no liability for applications assistance, customer product design, software performance, or services that may be described or referenced in the Materials. The user assumes all responsibility and liability for proper and safe design and handling of goods. Accordingly, the user indemnifies TI from all claims arising from its use of the Materials.

- 4. TI currently deals with various customers for products, and therefore our arrangement with the user will not be exclusive. TI makes no representations regarding the commercial availability of non-TI components that may be referenced in the Materials.

- 5. No license is granted under any patent right or other intellectual property right of TI covering or relating to any combination, machine, or process in which such TI products or services might be or are used. Except as expressly provided herein, TI and its suppliers do not grant any express or implied right to you under any patents, copyrights, trademarks, or trade secret information.

- 6. Performance tests and ratings, to the extent referenced in the Materials, are measured using specific computer systems and/or components and reflect the approximate performance of TI products as measured by those tests. Any difference in system hardware or software design or configuration may affect actual performance. Buyers should consult other sources of information to evaluate the performance of systems or components they are considering purchasing.

- 7. Resale of TI's products or services with statements different from or beyond the parameters stated by TI for that product or service in official TI data books or data sheets voids all express and any implied warranties for the associated TI product or service, and is an unfair and deceptive business practice, and TI is not responsible for any such use.

- 8. The Materials are copyrighted and any unauthorized use may violate copyright, trademark, and other laws. You may only download one copy for your internal use only, unless you are specifically licensed to do otherwise by TI in writing. This is a license, not a transfer of title, and is subject to the following restrictions: You may not: (a) modify the Materials (including any associated warranties, conditions, limitations or notices) or use them for any commercial purpose, or any public display, performance, sale or rental; (b) decompile, reverse engineer, or disassemble software Materials except and only to the extent permitted by applicable law; (c) remove any copyright or other proprietary notices from the Materials; (d) transfer the Materials to another person. You agree to prevent any unauthorized copying of the Materials. TI may terminate this license at any time if you are in breach of the terms of this Agreement. Upon termination, you will immediately destroy the Materials.

- 9. THE MATERIALS ARE PROVIDED "AS IS" WITHOUT ANY EXPRESS OR IMPLIED WARRANTY OF ANY KIND INCLUDING WARRANTIES OF MERCHANTABILITY, NONINFRINGEMENT OF INTELLECTUAL PROPERTY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT SHALL TI OR ITS SUPPLIERS BE LIABLE FOR ANY DAMAGES WHATSOEVER (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, LOSS OF INFORMATION) ARISING OUT OF THE USE OF OR INABILITY TO USE THE MATERIALS, EVEN IF TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products           |                        | Applications       |                           |

|--------------------|------------------------|--------------------|---------------------------|

| Amplifiers         | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters    | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface          | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic              | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt         | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers   | microcontroller.ti.com | Security           | www.ti.com/security       |

| Low Power Wireless | www.ti.com/lpw         | Telephony          | www.ti.com/telephony      |

|                    |                        | Video & Imaging    | www.ti.com/video          |

|                    |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2007, Texas Instruments Incorporated