# TLV9061DPWEVM User's Guide

This user's guide contains support documentation for the TLV9061DPW evaluation module (EVM). Included in this document is a description of how to set up and configure the EVM, printed circuit board (PCB) layout, schematic, and bill of materials (BOM) for the TLV9061DPWEVM.

#### Contents

| 1<br>2<br>3<br>4 | Introduction TLV9061DPWEVM Kit Contents. Circuit Configurations Schematic and PCB Layout | 2 2 3 |

|------------------|------------------------------------------------------------------------------------------|-------|

| 5<br>6           | Connections                                                                              |       |

|                  | List of Figures                                                                          | Ĭ     |

| 1                | TLV9061DPWEVM Schematic                                                                  | 3     |

| 2                | Silkscreen Schematic                                                                     | 3     |

| 3                | Difference Amplifier Schematic                                                           | 4     |

| 4                | Difference Amplifier Configured on TLV9061DPWEVM                                         | 4     |

| 5                | Non-inverting Amplifier Schematic                                                        |       |

| 6                | Non-inverting Amplifier Configured on TLV9061DPWEVM                                      | 5     |

| 7                | Inverting Amplifier Schematic                                                            | 6     |

| 8                | Inverting Amplifier Configured on TLV9061DPWEVM                                          | 6     |

| 9                | Top Layer PCB Layout                                                                     | 7     |

| 10               | Bottom Layer PCB Layout                                                                  | 7     |

|                  | List of Tables                                                                           |       |

| 1                | TLV9061DPWEVM Kit Contents                                                               | 2     |

| 2                | TLV9061DPWEVM BOM                                                                        | 8     |

Introduction www.ti.com

#### **Trademarks**

All trademarks are the property of their respective owners.

#### 1 Introduction

The TLV9061 is a high-performance, low cost, low power operational amplifier. For a full list of electrical characteristics of the TLV9061, please refer to the TLV9061 product data sheet (SBOS839). This EVM is developed to give users the ability to easily evaluate their design concepts using the TLV9061. The EVM can be configured into three circuit configurations: difference amplifier, non-inverting amplifier and inverting amplifier by populating different components on board.

# 2 TLV9061DPWEVM Kit Contents

Table 1 details the contents included in the TLV9061DPWEVM kit.

Table 1. TLV9061DPWEVM Kit Contents

| ITEM          | DESCRIPTION                                          | QUANTITY |

|---------------|------------------------------------------------------|----------|

| TLV9061DPWEVM | PCB                                                  | 1        |

| Header strip  | 100-mil (2.54-mm) spacing, 32 position, through hole | 2        |

# 3 Circuit Configurations

By populating different components on the PCB, the TLV9061DPWEVM can be configured into three different circuits:

- Difference amplifier

- · Non-inverting amplifier

- Inverting amplifier

# 4 Schematic and PCB Layout

This section provides the schematic and PCB layout of the TLV9061DPWEVM. Also included are the schematics for the three TLV9061DPWEVM circuit configuration options.

#### 4.1 Schematic

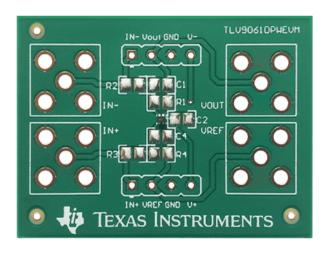

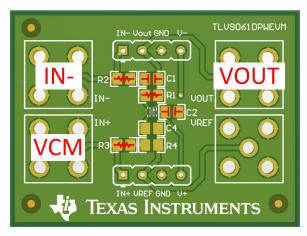

Figure 1 displays the circuit schematic of the TLV9061DPWEVM.

Figure 1. TLV9061DPWEVM Schematic

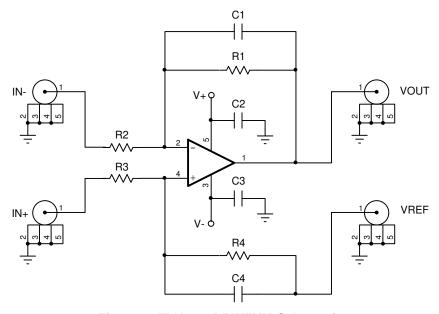

The schematic of the EVM is provided in silk screen located on the back of the PCB for easy reference. Figure 2 displays the schematic provided on the back of the PCB.

Figure 2. Silkscreen Schematic

# 4.2 Difference Amplifier

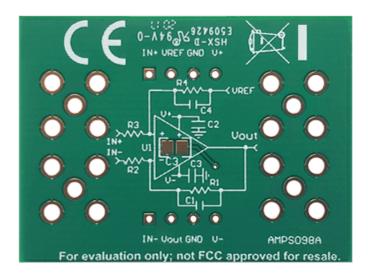

Figure 3 displays the schematic for the difference amplifier circuit configuration.

Figure 3. Difference Amplifier Schematic

Equation 1 displays the transfer function of the difference amplifier circuit configuration.

$$V_{\text{out}} = (\frac{R_4}{R_3 + R_4}) \times (1 + \frac{R_1}{R_2}) \times IN_+ + (\frac{R_3}{R_3 + R_4}) \times (1 + \frac{R_1}{R_2}) \times V_{\text{ref}} - \frac{R_1}{R_2} \times IN_-$$

(1)

If R1 = R4 and R2 = R3, Equation 1 can simplify to Equation 2.

$$V_{out} = \frac{R_1}{R_2} \times (IN_+ - IN_-) + V_{ref}$$

(2)

Capacitors C1 and C4 provide the option to filter the output of the amplifier. Equation 3 calculates the cutoff frequency,  $f_c$ , of the filter.

$$f_c = \frac{1}{2 \times \pi \times R_1 \times C_1} \tag{3}$$

#### Where

• R1 = R4, R2 = R3, and C1 = C4

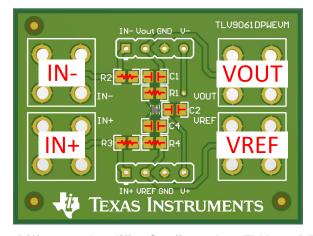

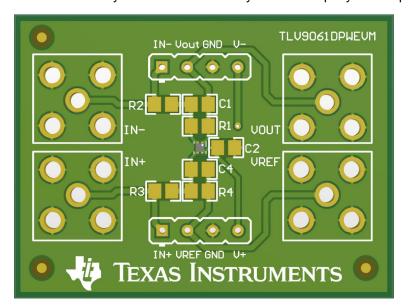

Figure 4 displays the TLV9061DPWEVM populated with the required components to be configured as a difference amplifier.

Figure 4. Difference Amplifier Configured on TLV9061DPWEVM

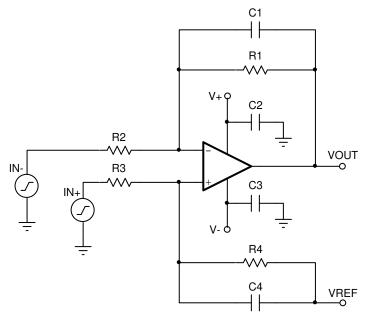

#### 4.3 Non-inverting Amplifier

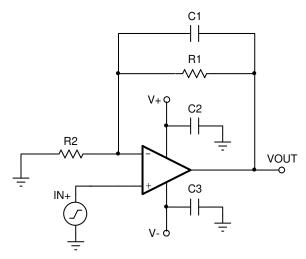

Figure 5 displays the schematic for the non-inverting amplifier circuit configuration. To configure the EVM in a non-inverting configuration short R3 using a  $0-\Omega$  resistor or solder bridge, leave R4 and C4 unpopulated, and ground the input connection IN–. The input signal is applied directly to the high impedance non-inverting input terminal using the IN+ connection on the EVM.

Figure 5. Non-inverting Amplifier Schematic

Equation 4 displays the DC transfer function of the non-inverting amplifier circuit configuration shown in Figure 5.

$$V_{out} = (1 + \frac{R_1}{R_2}) \times IN_+$$

(4)

Capacitor C1 provides the option to filter the output. The cutoff frequency,  $f_c$ , of the filter can be calculated using Equation 5.

$$f_{c} = \frac{1}{2 \times \pi \times R_{1} \times C_{1}} \tag{5}$$

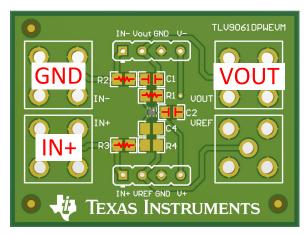

Figure 6 displays the TLV9061DPWEVM populated with the required components to be configured as a non-inverting amplifier.

Figure 6. Non-inverting Amplifier Configured on TLV9061DPWEVM

#### 4.4 Inverting Amplifier

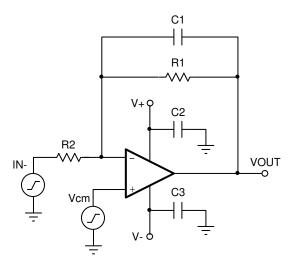

Figure 7 shows the schematic for the inverting amplifier circuit configuration. To configure the EVM in an inverting configuration short R3 using a  $0-\Omega$  resistor or solder bridge, leave R4 and C4 unpopulated, and apply the desired common mode voltage to the input connection, IN+. The input signal is applied using the input connection IN-.

Figure 7. Inverting Amplifier Schematic

Equation 6 displays the DC transfer function of the inverting amplifier circuit configuration.

$$V_{out} = -\frac{R_1}{R_2} \times IN_- + (1 + \frac{R_1}{R_2}) \times V_{cm}$$

(6)

Capacitor C1 provides the option to filter the output. The cutoff frequency,  $f_c$ , of the filter can be calculated using Equation 7.

$$f_{c} = \frac{1}{2 \times \pi \times R_{1} \times C_{1}} \tag{7}$$

Figure 8 shows the TLV9061DPWEVM populated with the required components to be configured as an inverting amplifier.

Figure 8. Inverting Amplifier Configured on TLV9061DPWEVM

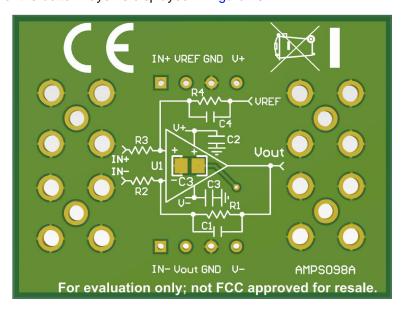

# 4.5 PCB Layout

The TLV9061DPWEVM is a two layer board. The PCB layout of the top layer is displayed in Figure 9.

Figure 9. Top Layer PCB Layout

The PCB layout of the bottom layer is displayed in Figure 10.

Figure 10. Bottom Layer PCB Layout

Connections www.ti.com

#### 5 Connections

This section provides a description for each connection available on the EVM.

#### 5.1 Power

The power supply connections for the TLV9061DPWEVM can only be applied using the header strips located at the top and bottom of the PCB. The positive power supply connection is labeled V+, the negative power supply connection is labeled V-, and the ground connection is labeled GND. For the minimum and maximum supply voltages of the TLV9061DPWEVM, please refer to the TLV9061 product data sheet (SBOS839).

# 5.2 Input Connections

Signals for the input can be applied to the TLV9061DPWEVM through the use of SMA connectors or the header pins. The input connections are labeled as IN+ and IN-.

#### 5.3 Output Connections

Output connections are provided through the use of SMA connectors or the header pin labeled as VOUT.

#### 5.4 Reference Voltage Connections

Signals or DC voltages for the reference voltage is applied to the TLV9061DPWEVM through the use of the SMA connector or header pin labeled VREF.

#### 6 Bill of Materials and References

# 6.1 Bill of Materials (BOM)

Table 2. TLV9061DPWEVM BOM

| DESIGNATOR    | QUANTITY | DESCRIPTION                    | PART NUMBER   |

|---------------|----------|--------------------------------|---------------|

| PCB           | 1        | Printed-Circuit-Board          | TLV9061DPWEVM |

| Header Strips | 2        | Header, 100 mil, 4x1, Gold, TH | TS-104-G-AA   |

# 6.2 References

- (1) DIYAMP-EVM: https://www.ti.com/tool/DIYAMP-EVM

- (2) DUAL-DIYAMP-EVM: https://www.ti.com/tool/DUAL-DIYAMP-EVM

- (3) TI Precision Labs Training: https://training.ti.com/ti-precision-labs-overview

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated