# UCD3138064 Programmer's Manual

SLUUAD8B - May 2014

### Table of Contents

| 1  | Intro  | oduction                                                                   | 6    |

|----|--------|----------------------------------------------------------------------------|------|

| 2  | Mer    | nory Map Changes for UCD3138064                                            | 6    |

|    | 2.1    | Overall memory map changes                                                 | 6    |

|    | 2.2    | Changes to ROM, RAM, and FLASH addresses                                   | 9    |

| 3  | Cha    | nges to ROM Boot Program                                                   |      |

| 4  | $I^2C$ | Interface to EEPROM                                                        | . 12 |

|    | 4.1    | I2C Initialization                                                         | . 12 |

|    | 4.2    | I2C speed setting                                                          | . 12 |

|    | 4.3    | Enabling the I2C EOM Interrupt                                             |      |

|    | 4.4    | Writing to the EEPROM with $\tilde{I}^2C$                                  | . 13 |

|    | 4.5    | Waiting Until the EEPROM is Ready for the Next Write with I <sup>2</sup> C | . 14 |

|    | 4.5.   |                                                                            | . 14 |

|    | 4.5.   |                                                                            | . 14 |

|    | 4.5.   |                                                                            |      |

|    | 4.6    | Reading From the EEPROM at a Specific Address with I2C (Random Read)       |      |

|    | 4.7    | I <sup>2</sup> C Current Address Read.                                     |      |

| 5  | SPI    | Interface to EEPROM                                                        |      |

|    | 5.1    | SPI Initialization                                                         | . 17 |

|    | 5.2    | SPI Key Registers and bitfields                                            | . 17 |

|    | 5.3    | Frames and Messages                                                        |      |

|    | 5.4    | SPI Programming Overview                                                   | . 18 |

|    | 5.5    | SPI Simple Example – Read EEPROM Status                                    | . 19 |

|    | 5.5.   | 1 SPI sequence start – write to SPITX0                                     | . 19 |

|    | 5.5.   | -                                                                          |      |

|    | 5.5.   | 3 SPI Read Status From SPIRX0                                              |      |

|    | 5.6    | SPI Read from Memory                                                       | . 19 |

|    | 5.6.   | 1 SPI Write Page to Memory                                                 | . 20 |

| 6  | Reg    | ister Changes for Program Flash Block 2                                    |      |

| 7  | Enh    | anced Peak Current Mode Blanking                                           | . 22 |

| 8  | Cha    | nges to HFO_LN_FILTER_EN bit                                               | . 24 |

| 9  | I2C    | Interface Reference                                                        | . 24 |

|    | 9.1    | I2C Control Register 1 (I2CCTRL1)                                          | . 24 |

|    | 9.2    | I2C Transmit Data Buffer (I2CTXBUF)                                        | . 25 |

|    | 9.3    | I2C Receive Data Register (I2CRXBUF)                                       |      |

|    | 9.4    | I2C Acknowledge Register (I2CACK)                                          |      |

|    | 9.5    | I2C Status Register (I2CST)                                                | . 26 |

|    | 9.6    | I2C Interrupt Mask Register (I2CINTM)                                      |      |

|    | 9.7    | I2C Control Register 2 (I2CCTRL2)                                          |      |

|    | 9.8    | I2C Hold Slave Address Register (I2CHSA)                                   |      |

|    | 9.9    | I2C Control Register 3 (I2CCTRL3)                                          | . 31 |

| 1( |        | Reference                                                                  | . 33 |

|    | 10.1   | SPI Control Register (SPICTRL)                                             |      |

|    | 10.2   | SPI Status Register (SPISTAT)                                              |      |

|    | 10.3   | SPI Pin Function Register (SPIFUNC)                                        |      |

|    | 10.4   | SPI Pin Direction Register (SPIDIR)                                        | . 34 |

| 10.5   | SPI Pin GP Out Register (SPIGPOUT)                      | 35 |

|--------|---------------------------------------------------------|----|

| 10.6   | SPI Pin GP In Register (SPIGPIN)                        | 35 |

| 10.7   | SPI TX Buffer Register (SPITX0)                         | 35 |

| 10.8   | SPI TX Buffer Register (SPITX1)                         | 36 |

| 10.9   | SPI Read Buffer Register (SPIRX0)                       | 36 |

| 10.10  | SPI Read Buffer Register (SPIRX1)                       | 36 |

| 10.11  | SPI Read Buffer Register (SPIRX2)                       | 36 |

| 11 IOM | IUX Reference                                           |    |

| 11.1   | I/O Mux Control Register (IOMUX)                        | 37 |

| 12 DEC | C-Address Manager Reference                             | 38 |

| 12.1   | Memory Fine Base Address High Register 0 (MFBAHR0)      | 38 |

| 12.2   | Memory Fine Base Address Low Register 0 (MFBALR0)       | 39 |

| 12.3   | Memory Fine Base Address High Register 1-3,17 (MFBAHRx) | 39 |

| 12.4   | Memory Fine Base Address Low Register 1-3,17(MFBALRx)   | 40 |

| 12.5   | Memory Fine Base Address High Register 4 (MFBAHR4)      | 41 |

| 12.6   | Memory Fine Base Address Low Register 4-16 (MFBALRx)    | 41 |

| 12.7   | Memory Fine Base Address High Register 5 (MFBAHR5)      |    |

| 12.8   | Memory Fine Base Address High Register 6 (MFBAHR6)      | 42 |

| 12.9   | Memory Fine Base Address High Register 7 (MFBAHR7)      |    |

| 12.10  | Memory Fine Base Address High Register 8 (MFBAHR8)      | 42 |

| 12.11  | Memory Fine Base Address High Register 9 (MFBAHR9)      | 43 |

| 12.12  | Memory Fine Base Address High Register 10 (MFBAHR10)    | 43 |

| 12.13  | Memory Fine Base Address High Register 11 (MFBAHR11)    | 43 |

| 12.14  | Memory Fine Base Address High Register 12 (MFBAHR12)    | 43 |

| 12.15  | Memory Fine Base Address High Register 13 (MFBAHR13)    | 44 |

| 12.16  | Memory Fine Base Address High Register 14 (MFBAHR14)    |    |

| 12.17  | Memory Fine Base Address High Register 15 (MFBAHR15)    | 44 |

| 12.18  | Memory Fine Base Address High Register 16 (MFBAHR16)    | 44 |

| 12.19  | Program Flash Control Register 1(PFLASHCTRL1)           | 44 |

| 12.20  | Data Flash Control Register (DFLASHCTRL)                |    |

| 12.21  | Flash Interlock Register (FLASHILOCK)                   | 45 |

| 12.22  | Program Flash #2 Control Register (PFLASHCTRL2)         | 46 |

| 13 DPV | VMCTRL2 Reference                                       | 46 |

| 13.1   | DPWM Control Register 2 (DPWMCTRL2)                     |    |

| 14 Con | verting UCD3138 programs to UCD3138064                  | 48 |

| 14.1   | Change linker addresses                                 | 48 |

| 14.2   | Change header files which define peripherals            | 48 |

| 14.3   | Changes to the Flash Control Registers                  | 49 |

| 14.4   | Set Blank_PCM_EN for Peak Current Mode                  | 49 |

| 14.5   | Update Parm Info/Parm Value Pointers                    | 49 |

| 14.5   |                                                         |    |

| 14.5   | .2 Changes in Parm Info/Parm Value File                 | 51 |

| 14.6   | Changes to load.asm                                     |    |

| 14.7   | Changes to system_defines.h                             | 53 |

| 14.8   | Changes to software interrupt addresses                 |    |

| 14.9   | Changes to Device ID                                    | 53 |

| 14 | 4.10   | Delete Write to HFO | _LN_FILTER | _EN | 3 |

|----|--------|---------------------|------------|-----|---|

| 15 | Refere | nces                |            |     | ł |

# Scope of this Document

The following topics are covered in the UCD3138064 Enhancements Programmer's Manual

- Memory Map Changes in UCD3138064 compared to UCD3138

- Added FLASH BLOCK

- Relocation of Fast Peripherals

- Relocation of ROM

- Added Interfaces for External EEPROM

- I2C Interface for External EEPROM

- SPI Interface for External EEPROM

- Other Changes in UCD3138064 compared to UCD3138

- Changes to IOMUX to support SPI and I2C pin multiplexing

- BLANK\_PCM\_ENABLE bit to optimize Peak Current Mode response time

- How to migrate firmware programs from UCD3138 to UCD3138064

Topics covered in the following UCD3138 programmer's manuals are also relevant to UCD3138064:

#### UCD3138 ARM and Digital System Programmer's Manual (Literature #: SLUU994)

- Boot ROM & Boot Flash

- BootROM Function

- o Memory Read/Write Functions

- Checksum Functions

- Flash Functions

- o Avoiding Program Flash Lock-Up

- ARM7 Architecture

- Modes of Operation

- Hardware/Software Interrupts

- o Instruction Set

- Dual State Inter-working (Thumb 16-bit Mode/ARM 32-bit Mode)

- Memory & System Module

- Address Decoder, DEC (Memory Mapping)

- Memory Controller (MMC)

- o Central Interrupt Module

- Register Map for all of the above peripherals in UCD3138

- UCD3138 Monitoring and Communications Programmer's Manual (Literature #: SLUU996)

- ADC12

- Control, Conversion, Sequencing & Averaging

- Digital Comparators

- Temperature Sensor

- PMBUS Addressing

- Dual Sample & Hold

- Miscellaneous Analog Controls (Current Sharing, Brown-Out, Clock-Gating)

- PMBUS Interface

- General Purpose Input Output (GPIO)

- Timer Modules

- PMBus

Register Map for all of the above peripherals in UCD3138

#### UCD3138 Digital Power Peripheral Programmer's Manual(Literature #: SLUU995)

- Digital Pulse Width Modulator (DPWM)

- Modes of Operation (Normal/Multi/Phase-shift/Resonant etc)

- Automatic Mode Switching

- DPWMC, Edge Generation & Intra-Mux

- Front End

- Analog Front End

- Error ADC or EADC

- Front End DAC

- Ramp Module

- Successive Approximation Register Module

- Filter

- Filter Math

- Loop Mux

- Analog Peak Current Mode

- Constant Current/Constant Power (CCCP)

- Automatic Cycle Adjustment

- Fault Mux

- Analog Comparators

- Digital Comparators

- Fault Pin functions

- DPWM Fault Action

- Ideal Diode Emulation (IDE), DCM Detection

- Oscillator Failure Detection

- Register Map for all of the above peripherals in UCD3138

# FUSION\_DIGITAL\_POWER\_DESIGNER GUI for Isolated Power Applications (Literature #: SLUA676)

For the most up to date product specifications please consult the UCD3138064 Device datasheet (Literature # SLUSB72) available at <u>http://www.ti.com/product/ucd3138064</u>.

# **1** Introduction

The UCD3138064 device is a 64kB program flash memory derivative of Texas Instruments' UCD3138 with additional options to interface with external memory. These are provided to support field updates of firmware and support larger size firmware programs. A summary of the key differences between UCD3138064 and UCD3138 is provided in Table 2-1 in UCD3138064 device datasheet (Literature #: SLUSB72).

This manual highlights the differences between the UCD3138 and the UCD3138064. It describes the newly added features in UCD3138064 and changes to the features in UCD3138. It also gives guidance on converting firmware programs from the UCD3138 to the UCD3138064. The UCD3138 Programmer's Manuals mentioned earlier should be used for information on all elements that are common to both devices.

The UCD3138064 adds:

- An additional completely independent 32 Kbyte FLASH memory block for a total of 64 Kbytes (vs. 32kbytes available in UCD3138)

- An I<sup>2</sup>C Master interface for interface to external EEPROM (unavailable in UCD3138)

- An SPI interface for external EEPROM (unavailable in UCD3138)

The two FLASH blocks are completely independent. It is possible to execute from one of the blocks while simultaneously writing to or erasing the other block. This permits live switching from one program version to another without interrupting power supply operation.

The Boot ROM program is changed slightly to support the new memory capabilities.

The additional memory and peripherals require a significant change in the memory map of the UCD3138064. This is mostly transparent to the programmer because almost all of the existing register names stay the same. New device files are supplied which change the addresses used by the development tools.

Three additional registers are added to the DEC-Address-Manager-area to support the new FLASH block.

Most of the I<sup>2</sup>C and SPI interface additions are in new sets of peripheral registers, but the pin multiplexing is in the IOMUX register in the Miscellaneous Analog Control peripheral. IOMUX is also changed to permit optimal multiplexing of the 48 pin version of UCD3138064.

The BLANK\_PCM\_EN bit is added to the DPWMCTRL2 registers. This enhances PCM (Peak Current Mode).

Finally, this manual describes how to take TI-provided UCD3138 reference code (eg. UCD3138 EVM firmware code) and convert it to apply to UCD3138064.

# 2 Memory Map Changes for UCD3138064

The addition of extra Program FLASH to the UCD3138064 requires that the other memories and many of the peripherals move to higher addresses.

### 2.1 Overall memory map changes

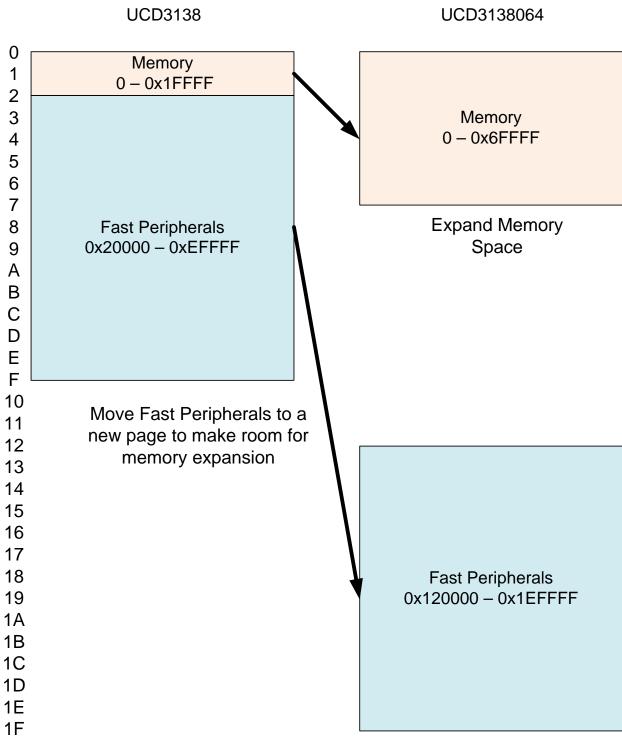

The figure below shows the memory map changes for the UCD3138064.

Overall Memory Map Changes (UCD3138 vs. UCD3138064)

The fast peripherals are moved up by 0x100000 bytes. This makes it very simple to calculate their new addresses. The slow peripherals, those mapped to 0xFFF7F600 and above, are not moved at all, so they are not shown on the figure. Fast peripherals use the same address decode scheme as memories. They have address mapping registers and run at the processor clock speed. Slow peripherals are on a

separate I/O bus with no address mapping registers. The I/O bus and the slow peripherals run at half the processor clock speed.

# 2.2 Changes to ROM, RAM, and FLASH addresses

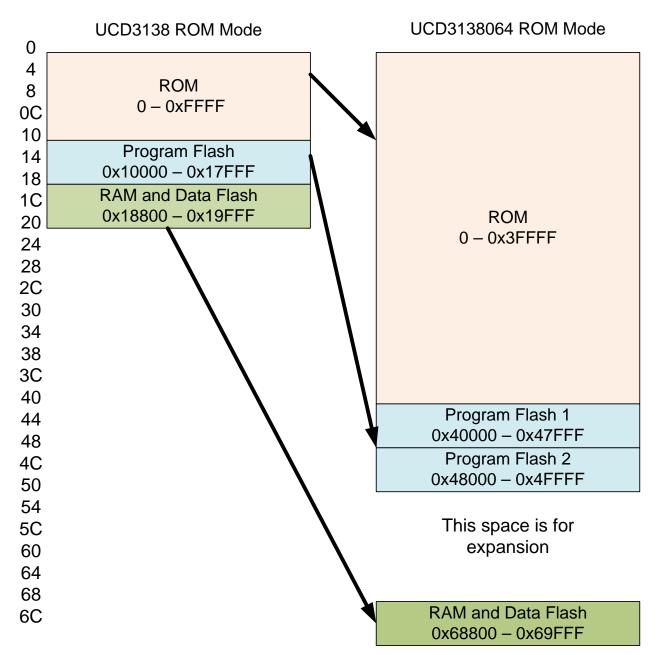

The UCD3138064 has different memory maps, depending on whether it is in ROM mode or in FLASH mode. In ROM mode, the ROM is located at location 0 so that it provides the reset and interrupt vector table. Here are the maps for UCD3138 and UCD3138064 in ROM mode.

Memory Map changes to ROM, RAM, and FLASH in ROM mode (UCD3138 vs. UCD3138064)

In the ARM core, the reset and interrupt vectors start at location 0 in memory. At power up reset, the ROM must be at location 0 to provide the vectors. In flash mode, the flash must be at location 0 to control the interrupt vectors. This is accomplished by changing the addresses of the ROM and FLASH. In ROM mode, the ROM must extend from location 0 to the location where it will be in FLASH mode. The ROM reset vectors make it jump to the locations it will execute from when the program FLASH is moved down to the zero location. This way, when flash mode is entered, the ROM simply remaps itself to the higher address. The program is already executing there. Then it remaps the flash to location 0 and jumps the vector at 0. The ROM on the UCD3138064 is 8K. That same 8K image is repeated throughout the entire memory space from 0 to 0x3FFFF in ROM mode.

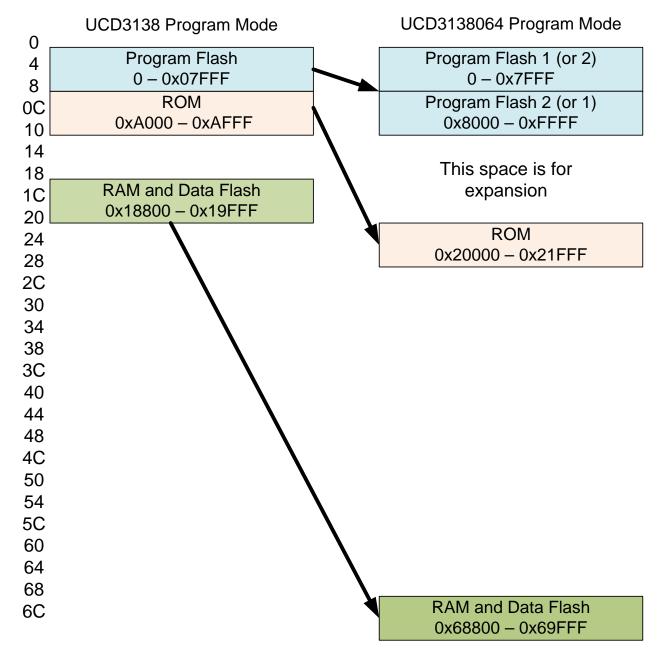

The figure below shows the changes for FLASH mode for the UCD3138064:

Memory Map changes to ROM, RAM, and FLASH in FLASH mode (UCD3138 vs. UCD3138064)

Note that the program FLASH blocks, 1 and 2, are interchangeable. Either one can be moved to location 0. This means that two independent programs with different interrupt vectors can be stored in chip at the same time. The programs themselves can switch control between the two programs, or it can be done through a reset using the ROM program. The entire 64K space can also be used to hold a single program. A 2K boot flash/62K program space configuration is also possible.

# 3 Changes to ROM Boot Program

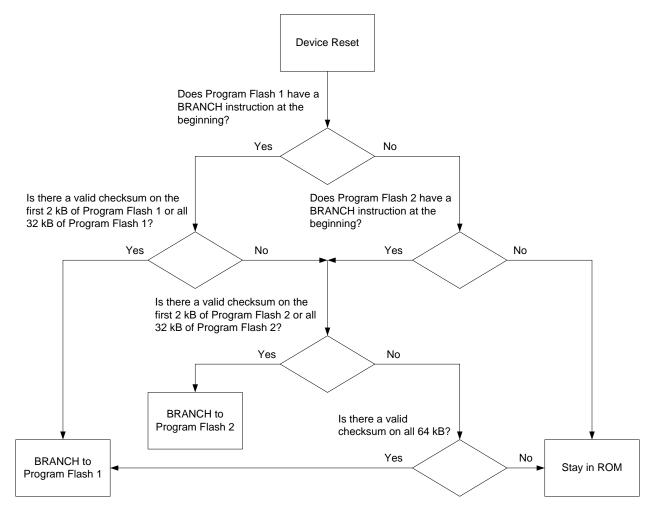

The ROM program changes how it handles program startup. Instead of 2 checksums on the UCD3138, there are now 4 locations for checksums on the UCD3138064, and one of those does double duty as a checksum for two different blocks. The checksums and their locations are:

0x7fc – Boot block for Block 1 0x7ffc – Overall checksum for Block 1 0x87fc – Boot block for Block 2 0xffc – Overall checksum for a 64K program combining Blocks 1 and 2 or for Block 2 alone

The locations above assume that Block1 is mapped to location 0, and Block 2 is mapped to 0x8000.

Here is a flowchart showing the order in which the ROM verifies the checksums:

The branch instruction check prevents the checksum program from looking at an empty block of memory.

When the flowchart says "Branch to Program Flash 1", this means that it puts Block 1 at location 0 and branches to location 0. For ""Branch to Program Flash 2", it puts Block 2 at 0 and branches there. The other block is always put at 0x8000.

The UCD3138 has a PMBus command code 0xF0 which causes the program to execute. On the UCD3138064, the same command causes Block 1 to be placed in control. A 0xF7 command has been added which puts Block 2 at location 0 and starts executing there.

In addition, the ROM has been expanded to 8K bytes.

# 4 I<sup>2</sup>C Interface to EEPROM

The  $I^2C$  interface is a modified PMBus interface. When it is used for  $I^2C$  mode, many of the bit fields are not used. For a complete list of the registers and bit fields, see 7,  $I^2C$  Interface Reference.

## 4.1 I2C Initialization

Very few of the I<sup>2</sup>C interface register values need to be changed from their default states. Here is the complete initialization required to write to an I<sup>2</sup>C EEPROM device.

Configure FAULT0 and FAULT 1 pins for I2C.

#### MiscAnalogRegs.IOMUX.bit.FAULT\_01\_MUX\_SEL = 2;

Fault 0 is used for I<sup>2</sup>C clock, and Fault 1 is used for <sup>I2</sup>C data

Enable master mode and  $I^2C$  mode.

#### I2CRegs.I2CCTRL3.bit.MASTER\_EN = 1; I2CRegs.I2CCTRL3.bit.I2C\_MODE\_EN = 1;

Since the I<sup>2</sup>C interface is derived from a PMBus interface, the Clock Low Timeout function should be disabled for full I<sup>2</sup>C emulation:

#### I2CRegs.I2CCTRL3.bit.CLK\_LO\_DIS = 1;

In practice, the Clock Low Timeout is very unlikely to occur with an EEPROM. It can be enabled safely to help detect firmware issues with the I<sup>2</sup>C interface.

### 4.2 I2C speed setting

The default speed for the I<sup>2</sup>C hardware is 100 KHz. Setting the FAST\_MODE\_PLUS bit will give approximately 1 MHz:

#### I2CRegs.I2CCTRL3.bit.FAST\_MODE\_PLUS = 1;

It is also possible to set the FAST\_MODE bit for 400 KHz.

# 4.3 Enabling the I2C EOM Interrupt

Some of the program logic will be simpler if the  $I^2C$  EOM interrupt is enabled in the  $I^2C$  peripheral. It is not necessary to enable it in the CIM (Central Interrupt Module). The firmware will just poll the interrupt request flag in the CIM to determine if the EOM bit is set. For details see Section 4.55 Waiting Until the EEPROM is Ready for the Next Write.

# 4.4 Writing to the EEPROM with $f^2C$

The I<sup>2</sup>C interface is very simple to use for writing to an external EEPROM. Many I<sup>2</sup>C EEPROMs require 2 bytes of address followed by 1 to 128 bytes of data.

The I<sup>2</sup>C write is started by a firmware write to the I2CRegs.I2CCTRL1 register.

This means 2 things:

- 1. The I2CRegs.I2CTXBUF register should be initialized first

- 2. Only one write should be performed to the I2CRegs.I2CCTRL1 register

To make a single write to the I2CRegs.I2CCTRL1 register convenient, create a variable with the same type:

#### union I2CCTRL1\_REG i2cctrl1;

Then the variable can be initialized easily with bitwise structure statements before being written once to the actual register.

The first step, which can be done at initialization, is to put the address into the variable:

#### i2cctrl1.bit.SLAVE\_ADDR = 0x50; //default address of eeprom

The byte count and read/write bit need to be configured as well:

# i2cctrl1.bit.BYTE\_COUNT = 130 ;//send address and 128 bytes i2cctrl1.bit.RW = 0; //write

Before writing to the control register, the transmit buffer must be written. It is a good idea to use a variable for the transmit buffer as well. It is not necessary for the first write, but subsequent writes in the same  $I^2C$  message are started by the write to the transmit buffer.

There are no bitfields in the transmit buffer, so it can be represented by a simple Uint32:

#### Uint32 i,txbuf;

It can be loaded with the data to write:

The page size for this EEPROM is 128 bytes, so only the most significant bit of the low address byte is used. This ensures that the address starts at the beginning of the page. The address

needs to go out high byte first, low byte second, so the low byte of the address is put into the second byte of txbuf. The high byte is put in the first byte of txbuf.

Then both registers can be written:

```

I2CRegs.I2CTXBUF.all = txbuf ;

I2CRegs.I2CCTRL1 = i2cctrl1; //start write

```

This will write the two bytes of the address and the first two bytes of data to the EEPROM.

Next, the firmware needs to wait for the write to complete. When the write is complete, the DATA\_REQUEST bit will be set. The firmware needs to wait until the bit is set:

```

while (I2CRegs.I2CST.bit.DATA_REQUEST == 0)

{

; //wait for data to go out

}

```

Note that the I2CST register is cleared on read.

Then the firmware can loop writing to I2CTXBUF and waiting for data request until all the data is sent. The I<sup>2</sup>C hardware will automatically issue an I<sup>2</sup>C stop sequence when the number of bytes in BYTE\_COUNT has been sent out. This will cause the EEPROM to start programming the page. Smaller numbers of bytes can be written out if desired, simply by changing the BYTE\_COUNT value.

# 4.5 Waiting Until the EEPROM is Ready for the Next Write with $l^2C$

It is possible to use a firmware delay function programmed for the maximum EEPROM write time. But many EEPROMs are self clocked, and will normally write more quickly than the specified maximum. These EEPROMs generally will NACK I<sup>2</sup>C messages until programming is complete. Here is the sequence used to support this feedback from the EEPROM.

### 4.5.1 Step 1 Detect end of final write to EEPROM

Instead of a DATA\_REQUEST, the final write command will return an EOM bit. So the firmware can first wait for the EOM bit to be set:

#### if (I2CRegs.I2CST.bit.EOM == 1) //when i2c is done

#### 4.5.2 Step 2. Try a simple read from EEPROM

Once the EOM is received, it is necessary poll the EEPROM to see when it is done. A one byte read is a legitimate command for many EEPROMs. It will just read the next location in the EEPROM, assuming the EEPROM is done writing. Since the slave address is already initialized, only 2 bitfields in I2CCTRL2 must be written to:

i2cctrl1.bit.RW = 1; //read i2cctrl1.bit.BYTE\_COUNT = 1; I2CRegs.I2CCTRL1 = i2cctrl1;

This will cause the I<sup>2</sup>C interface to send out one byte with the slave address, and receive one byte back from the EEPROM.

### 4.5.3 Step 3. Determine if message is ACKed or NACKed

This step is complicated by the fact that the NACK bit will be set before the EOM bit on messages which are NACKed. One method for dealing with this is to read the EOM interrupt bit from the Central Interrupt Module. The interrupt is enabled at the  $l^2C$ :

#### I2CRegs.I2CINTM.bit.EOM = 0; ,

but it is not enabled in the Central Interrupt Module. This way the EOM state can be polled without reading from the I2CST register. This makes the program logic simpler.

# if(CimRegs.INTREQ.bit.INTREQ\_DIGI\_COMP == 1) //if i2c eom interrupt is being requested

{

#### if(I2CRegs.I2CST.bit.NACK == 0) //if we were acked, it's done

The digital comparators share the interrupt bit with the I2C. If the digital comparator interrupt is also being used, this scheme will not work.

If the NACK bit is not set, then the write of the next page can begin. If it is set, then steps 2 and 3 must be repeated until the NACK bit is not set in the if-statement above.

# 4.6 Reading From the EEPROM at a Specific Address with I2C (Random Read)

The EEPROM random read sequence involves sending:

- 1. An  $I^2C$  start sequence

- 2. The EEPROM I<sup>2</sup>C address (1 byte) with the R/W bit set to zero. This signals a write.

- 3. 2 bytes of address within the EEPROM

- 4. An I<sup>2</sup>C repeated start sequence

- 5. The EEPROM I<sup>2</sup>C address (1 byte) with the R/W bit set to one. This signals a read

- 6. As many reads as are desired.

- 7. A NACK from the UCD3138064 followed by a stop sequence.

This sequence is the same as the extended command sequence in the PMBus, so the EXT\_CMD bit can be used.

The I2CTXBUF register is loaded with the address at which the read will start:

#### I2CRegs.I2CTXBUF.all = (((eeprom\_address & 0xff) << 8) + ((eeprom\_address & 0xff00) >> 8));

Then the control register is loaded using the RAM variable:

i2cctrl1.bit.EXT\_CMD = 1 ; //set it as extended command to get 2 bytes out i2cctrl1.bit.RW = 1; //read i2cctrl1.bit.CMD\_ENA = 1; //otherwise we'll just get a read. i2cctrl1.bit.BYTE\_COUNT = 16; I2CRegs.I2CCTRL1 = i2cctrl1; //need single write to ctrl1.

The EXT\_CMD and CMD\_ENA bits are only set for this function, so it is efficient to clear them in the i2cctrl1 variable as soon as possible. This example will read 16 bytes.

i2cctrl1.bit.EXT\_CMD = 0 ; //clear it for other uses. i2cctrl1.bit.CMD\_ENA = 0;

If the CMD\_ENA bit is not set, the I<sup>2</sup>C logic will ignore the contents of TXBUF and the EXT\_CMD bit and only send out a read address.

The code sequence above will handle steps 1 through 5 above, and will accept the first 4 bytes of data from the EEPROM.

The I<sup>2</sup>C peripheral will signal that the bytes are ready by setting the DATA\_READY flag in I2CST:

```

while(I2CRegs.I2CST.bit.DATA_READY == 0)

{

//wait for DATA_READY

}

eeprom_buffer[0] = I2CRegs.I2CRXBUF.all;

//this read starts an i2c read.

```

When the firmware reads from the RXBUF, the  $I^2C$  peripheral will start clocking in the next 4 bytes. After the desired number of bytes are read in, the  $I^2C$  peripheral will automatically send a NACK and a stop sequence to finish the transaction.

# 4.7 <sup>2</sup>C Current Address Read

Only one address is needed to read a long string of data from the EEPROM. Because of the size of BYTE\_COUNT, the I<sup>2</sup>C interface can only support reading 255 bytes per I<sup>2</sup>C message. With the current address read, additional blocks can be read easily and efficiently. A random read is used first to set the address. After this current address reads are executed until all the data is read.

To execute a current address read, do exactly the same thing as the random read above, but omit the sending of the address. Omit the loading of the TXBUF register and the setting of the CMD\_ENA and EXT\_CMD bits. This will cause the I<sup>2</sup>C interface to just issue the device address with a read state in the LSB. Then it will read data from the EEPROM just as the random read does.

```

i2cctrl1.bit.RW = 1; //read

i2cctrl1.bit.BYTE_COUNT = 16;

I2CRegs.I2CCTRL1 = i2cctrl1; //need single write to ctrl1.

```

# 5 SPI Interface to EEPROM

The SPI interface uses 4 wires to interface to the EEPROM. The peripheral logic and registers are completely different from  $I^2C$ , even though 2 of the pins (Fault 0 and Fault 1) are still the same. The pins are:

- TDI SPI\_MISO

- TDO- DPI\_MOSI

- FAULT1 SPI\_CLK

- FAULT0 SPI\_CS

Most of the control for SPI is in SPIRegs. Like I<sup>2</sup>C, the IOMUX must also be configured.

### 5.1 SPI Initialization

The initialization for SPI is very simple. Two IOMUX bitfields need to be configured to enable the 4 SPI pins:

MiscAnalogRegs.IOMUX.bit.FAULT\_01\_MUX\_SEL = 1; // SPI CS/CLK on pins Fault-0 / Fault-1

MiscAnalogRegs.IOMUX.bit.JTAG\_DATA\_MUX\_SEL = 4; // MOSI / MISO on pins TDO / TDI

Next the SPI interface needs to be enabled:

SPIRegs.SPICTRL.bit.SPIEN = 1; // enable SPI - only non-default statement needed.

This is all that is required for initialization.

# 5.2 SPI Key Registers and bitfields

There are a few key registers and bitfields for the SPI interface. They are:

- SPICTRL.bit.TXCNT sets number of bytes to transmit

- SPICTRL.bit.RXCNT sets number of bytes to receive

- SPICTRL.bit.FRLMLEN sets number of messages for which the hardware will automatically hold CS (Chip Select) low

- SPISTAT.bit.SPIF shows that the SPI operation is complete

- SPITX0 4 byte transmit buffer writing to this register starts the next SPI operation

- SPITX1 another 4 byte transmit buffer sent out after SPITX0

- SPIRX0-3 4 receive buffers of 4 bytes each

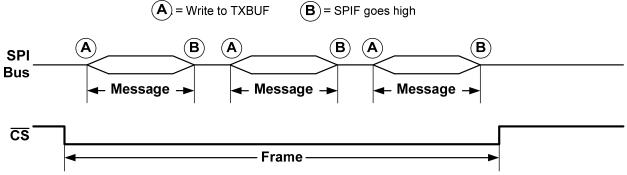

### 5.3 Frames and Messages

A single SPI transaction with an EEPROM can be much longer than will fit in the SPI buffers. Generally an SPI transaction is defined by the Chip Select pin going low at the beginning and high at the end. This is called a frame.

For the purposes of this document, a message is one emptying of the TXBUF and/or one loading of the RXBUF. Messages are always started by writing to one or more TX Buffer registers. Sometimes it may be necessary to change the values in TXCNT and RXCNT before writing to the TX Buffer. The SPI interface signals that the message is done by setting the SPIF bit.

A frame contains one or more messages. The first message in a frame needs to set up the FRMLEN bitfield. This field dictates how many messages there are in that frame. The SPI hardware will keep the CS (Chip Select) line active for all the messages in the frame. For some long frames, the CS pin must be controlled by firmware.

Here is an example of a frame with 3 messages:

There are several different length limitations on SPI messages on the UCD3138064.

- TX Buffer size 8 bytes

- TXCNT size 15 bytes

- RX Buffer size 16 bytes

- RXCNT size 31 bytes

So it is possible to transmit up to 15 bytes per message. This will require two writes to the TX Buffer Registers. Similarly, up to 31 bytes can be read at a time, with two reads from the RX Buffer Registers.

In a typical application, it is simpler to use the buffer sizes as the maximum message size. In this case, each message has up to 8 bytes of transmitted data and 16 bytes of received data.

If the message is small, the frame will have only one message. The maximum number of messages per frame is 31 messages. In practical applications, generally the maximum number of messages per frame is 16.

This means that the longest write frame is 8 bytes times 16, or 128 bytes. However some SPI EEPROMS have pages of 256 bytes or more. And the page write is started by the CS pin going inactive. In this case, instead of using the frame control of CS, it is simpler to just use direct firmware control of the pin.

### 5.4 SPI Programming Overview

Every SPI frame has very similar starting and ending C statements.

At the start of every frame, write to TXCNT, RXCNT, and FRMLEN (or activate CS pin)

Then write to the TX buffers with SPITX0 last to start the message.

The next step is to poll the SPIF. When it goes high, the message is done.

It is necessary to write a 1 to the SPIF to clear it.

When the message is done, read any data which needs to be read from the RX buffers. If more needs to be read or written in the frame, write any new values to TXCNT and RXCNT, and then write to at least SPITX0. Even if TXCNT is 0, a write to SPITX0 is what starts the next message.

This sequence continues until all of the messages have gone out and the frame is done. If FRMLEN is being used, then CS will automatically go inactive. If CS is being controlled directly by firmware, then it should be made inactive.

# 5.5 SPI Simple Example – Read EEPROM Status

Reading EEPROM status just requires sending 1 byte and receiving 1 byte – the status byte.

The first step is to write to TXCNT, RXCNT, and FRMLEN

```

SPIRegs.SPICTRL.bit.TXCNT = 1;

SPIRegs.SPICTRL.bit.RXCNT = 1;

SPIRegs.SPICTRL.bit.FRMLEN = 1;

```

#### 5.5.1 SPI sequence start – write to SPITX0

The sequence is always started by a write to SPITX0. For instance, in the status read, the read status command byte for the EEPROM is put into SPI\_TX0:

#### SPIRegs.SPITX0.all = SPI\_CMD\_READ\_STATUS\_REGISTER; //starts SPI engine

With the write to the SPITX0 register, the SPI\_CS line will go low, the SPI\_CLK will start, and the data will be transferred.

Just like I<sup>2</sup>C, the SPITX0 register should be written only once. If individual bytes must be assembled into the 4 bytes of the register, assemble them in a 4 byte variable in RAM and then write that variable into the register.

#### 5.5.2 SPIF tells when sequence is complete or when new data is needed

The SPIF needs to be cleared by writing a 1 to it, so that the next end of message can be detected. Here is the code:

```

while(SPIRegs.SPISTAT.bit.SPIF == 0)

{

//waiting for SPI to finish its message

}

SPIRegs.SPISTAT.bit.SPIF = 1; //1 to clear spif

```

#### 5.5.3 SPI Read Status From SPIRX0

The final step is to read from the SPIRX0 and get the status byte. It will appear in the least significant bit of SPIRX0. Normally the status byte is read to see if a write is complete – if the EEPROM is no longer busy.

### 5.6 SPI Read from Memory

Memory read on a typical SPI EEPROM is very flexible. The method described below reads 256 bytes with each frame.

TXCNT is loaded with a 5 because there are 3 bytes of meaningful data and 2 bytes of dummy data for a delay.

RXCNT is loaded with 16 to read 16 bytes each message.

FRMLEN is loaded with 16 to permit 16 messages.

Then the command and address bytes are combined in the RAM variable and written to the SPITX0 register to start the first command.

Once SPIF is set by the hardware and cleared by the firmware, the first 16 bytes are read from the SPIRXx registers. TXCNT should be written with a 0. Then something random can be written to the SPITX0 register to start the read, followed again by polling SPIF.

This same sequence is followed until 16 bytes have been read a total of 16 times. Then the SPI hardware will automatically make the CS pin inactive.

### 5.6.1 SPI Write Page to Memory

Using powers of 2 for TXCNT and FRMLEN, the SPI hardware does not support a full 256 byte write. So it is necessary to use the GPIO control of the CS pin.

The default value of SPIDIR.bit.SCS already supports an output, so it doesn't need to be written. But the pin function bit needs to be written:

SPIRegs.SPIFUNC.bit.SCS = 1; //take firmware control of chip select.

Next it is necessary to send out a 1 byte command and a 3 byte page address, so TXCNT gets 4 bytes:

SPIRegs.SPICTRL.bit.TXCNT = 4; SPIRegs.SPICTRL.bit.RXCNT = 0;

FRMLEN just needs to be short to avoid having CS active when the frame is done and CS control is returned to the SPI hardware.

```

SPIRegs.SPICTRL.bit.FRMLEN = 1;

```

Then the write data needs to be assembled in a variable before the write to SPITX0: temp = SPI\_CMD\_MAIN\_MEMORY\_PAGE\_PROGRAM\_THROUGH\_BUFFER + ((eeprom\_address & 0x3ff00)<< 1) + (eeprom\_address & 0xff);

#### SPIRegs.SPITX0.all = temp; //starts SPI engine

Then there is a wait for the SPI message to go out, which just polls and then clears SPIF:

# spi\_engine\_busy\_wait(); //wait for command and address to finish

Now WRSTART is set to a 1. WRSTART selects which SPITXx register starts the SPI message. When sending sequential data, using a write to SPITX1 is more convenient than a write to SPITX0:

#### SPIRegs.SPICTRL.bit.WRSTART = 1;

Now 8 bytes will go out with every message

#### SPIRegs.SPICTRL.bit.TXCNT = 8; // now send out 8 bytes

To send out 256 bytes, 32 messages are required:

```

for(i = 0;i < 32;i++)

{

SPIRegs.SPITX0.all = *source ++;

SPIRegs.SPITX1.all = *source ++; //write to start

spi_engine_busy_wait();

}</pre>

```

Source is a pointer to a 32 bit word.

Then it is necessary to return control of the CS to the SPI hardware:

```

SPIRegs.SPIFUNC.bit.SCS = 0;

//release firmware control of chip select.

```

It is also good to clear WRSTART for the normal short messages which only write to SPITX0:

#### SPIRegs.SPICTRL.bit.WRSTART = 0; //most commands use 0, set it back to that.

This must be followed by a delay to permit the EEPROM to write the page. The delay can be accomplished using the timer interrupt. If maximum speed is desired, the firmware can continuously read the status register and wait for the EEPROM to signal that it is not busy.

# 6 Register Changes for Program Flash Block 2

Three registers are added to the UCD3138064 to control the second block of program flash. They are:

- DecRegs.PFLASHCTRL2

- DecRegs. MFBAHR17

- DecRegs.MFBALR17

In addition, PFLASHCTRL, which controls block 1, has its name changed to PFLASHCTRL1.

The new registers work the same as the registers for block 1. PFLASHCTRL2 is used for page and mass erase, and for status monitoring of block 2. The MFB... registers are used to change the address mapping of Block 2. They can be used to map block 2 to the 0 location in memory so that a code image in block 2 can provide the interrupt vectors to the processor.

Please refer to UCD3138 ARM and Digital System programmer's manual (literature #: SLUU994) for more information on these types of registers.

There is still only one DecRegs.FLASHILOCK register, but a different value must be written to it to unlock program flash block 2. Data flash and block 1 still have the same number as before:

#### #define PROGRAM\_FLASH1\_INTERLOCK\_KEY 0x42DC157E

#### #define PROGRAM\_FLASH2\_INTERLOCK\_KEY 0x6C97D0C5

#### #define DATA\_FLASH\_INTERLOCK\_KEY 0x42DC157E

See the Dec – Address Manager Reference section of this document for information on the detailed memory and bit maps for these registers.

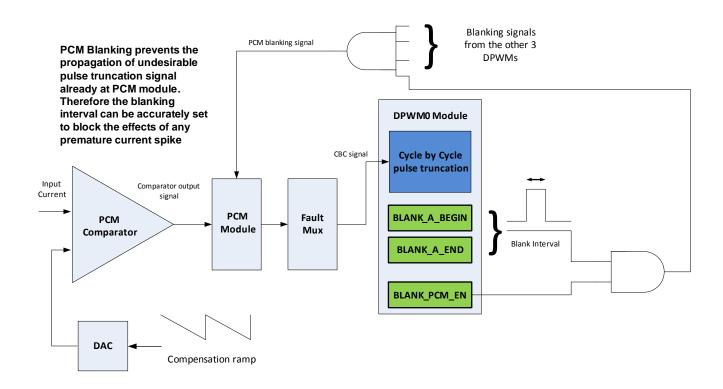

# 7 Enhanced Peak Current Mode Blanking

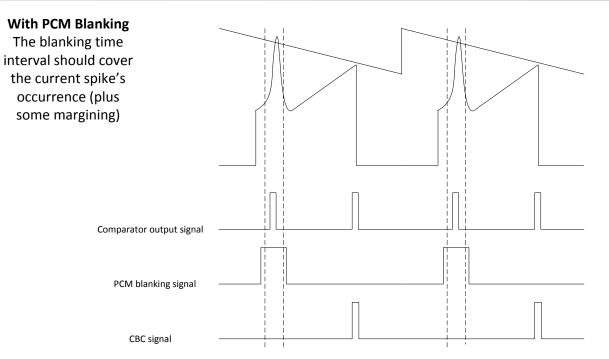

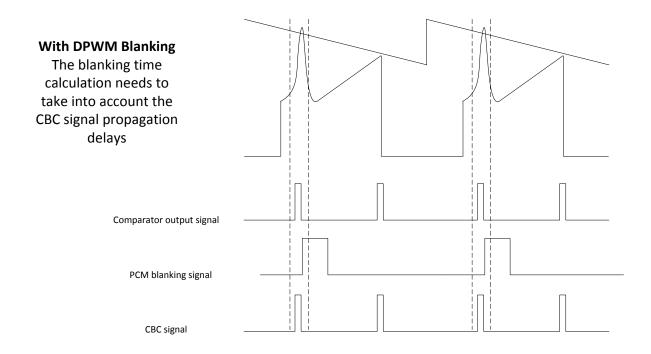

The BLANK\_PCM\_EN bit in DPWMCTRL2 provides improved blanking of noise spikes in the Peak Current Mode comparator signal path. PCM blanking provides an earlier blanking than the blanking using the Blank A and Blank B enable bits on DPWM modules when used for PCM. It also makes it possible to use blanking signals from multiple DPWMs for all DPWMs.

When Blank A enable bit in a DPWM module is used, the blanking signal from the DPWM is 'and'ed with the CBC signal in the DPWM logic. This means that the CBC signal must first propagate though the PCM module and then through the Fault Mux before it arrives at the DPWM for blanking. It also means that the only blanking signals are available are Blank A and Blank B from that DPWM. With PSFB (Phase Shifted Full Bridge), only Blank A is available, because Blank B is being used to generate a waveform.

With the BLANK\_PCM\_EN bit set, the blanking signal is sent to the PCM module, so it can be 'and'ed much sooner in the signal path. The latency from input to DPWM shut off is not changed, but the signal blanking interval is much closer to the actual interval from the blanking registers. This makes the blanking calculation easier. In addition, all the blanking signals are combined in the PCM module, so up to 8 blanking intervals can be applied to the CBC signal to all the DPWMs.

Here is the block diagram:

Here is the relative timing with and without BLANK\_PCM\_EN:

# 8 Changes to HFO\_LN\_FILTER\_EN bit

On the UCD3138, it is recommended to clear the HFO\_LN\_FILTER\_EN bit in the CLKTRIM register. On the UCD3138064, the HFO\_LN\_FILTER\_EN register is controlled by the test program, it has become a trim bit. This way TI can control the bit setting at test time for optimal results. It is recommended that writes to HFO\_LN\_FILTER\_EN be removed when moving programs from UCD3138 to UCD3138064.

# 9 I2C Interface Reference

This section describes the new registers added for the I2C interface

# 9.1 I2C Control Register 1 (I2CCTRL1)

Address FFF7E400

| Bit Number | 20       | 19      | 18      | 17      |

|------------|----------|---------|---------|---------|

| Bit Name   | PRC_CALL | GRP_CMD | PEC_ENA | EXT_CMD |

| Access     | R/W      | R/W     | R/W     | R/W     |

| Default    | 0        | 0       | 0       | 0       |

| Bit Number | 16      | 15:8       | 7:1        | 0   |

|------------|---------|------------|------------|-----|

| Bit Name   | CMD_ENA | BYTE_COUNT | SLAVE_ADDR | RW  |

| Access     | R/W     | R/W        | R/W        | R/W |

| Default    | 0       | 0000_0000  | 000_0000   | 0   |

#### Bit 20: PRC\_CALL – Master Process Call Message Enable

0 = Default state for all messages besides Process Call message (Default)

- 1 = Enables transmission of Process Call message

- Bit 19: GRP\_CMD Master Group Command Message Enable

- 0 = Default state for all messages besides Group Command message (Default)

- 1 = Enables transmission of Group Command message

- Bit 18: PEC\_ENA Master PEC Processing Enable

- 0 = Disables PEC processing (Default)

- 1 = Enables PEC byte transmission/reception

- Bit 17: EXT\_CMD Master Extended Command Code Enable

- 0 = Use 1 byte for Command Code (Default)

- 1 = Use 2 bytes for Command Code

- Bit 16: CMD\_ENA Master Command Code Enable

- 0 = Disables use of command code on Master initiated messages (Default)

- 1 = Enables use of command code on Master initiated messages

**Bits 15-8: BYTE\_COUNT** – Indicates number of data bytes transmitted in current message. Byte count does not include any device addresses, command words or block lengths in block messages. In block messages, the PMBus Interface automatically inserts the block length into the message based on the byte count setting. The firmware only needs to load the address, command words and data to be transmitted. PMBus Interface supports byte writes up to 255 bytes.

**Bits 7-1: SLAVE\_ADDR** – Specifies the address of the slave to which the current message is directed towards.

Bit 0: RW – Indicates if current Master initiated message is read operation or write operation.

- 0 = Message is a write transaction (data from Master to Slave) (Default)

- 1 = Message is a read transaction (data from Slave to Master)

# 9.2 I2C Transmit Data Buffer (I2CTXBUF)

#### Address FFF7E404

| Bit Number | 31:24     | 23:16     | 15:8      | 7:0       |

|------------|-----------|-----------|-----------|-----------|

| Bit Name   | BYTE3     | BYTE2     | BYTE1     | BYTE0     |

| Access     | R/W       | R/W       | R/W       | R/W       |

| Default    | 0000_0000 | 0000_0000 | 0000_0000 | 0000_0000 |

**Bits 31-24: BYTE3** – Last data byte transmitted from Transmit Data Buffer **Bits 23-16: BYTE2** – Third data byte transmitted from Transmit Data Buffer **Bits 15-8: BYTE1** – Second data byte transmitted from Transmit Data Buffer **Bits 7-0: BYTE0** – First data byte transmitted from Transmit Data Buffer

# 9.3 I2C Receive Data Register (I2CRXBUF)

#### Address FFF7E408

| Bit Number | 31:24 | 23:16 | 15:8  | 7:0   |

|------------|-------|-------|-------|-------|

| Bit Name   | BYTE3 | BYTE2 | BYTE1 | BYTE0 |

| Access     | R     | R     | R     | R     |

| Default    | -     | -     | -     | -     |

**Bits 31-24: BYTE3** – Last data byte received in Receive Data Buffer **Bits 23-16: BYTE2** – Third data byte received in Receive Data Buffer **Bits 15-8: BYTE1** – Second data byte received in Receive Data Buffer **Bits 7-0: BYTE0** – First data byte received in Receive Data Buffer

# 9.4 I2C Acknowledge Register (I2CACK)

#### Address FFF7E40C

| Bit Number | 0   |

|------------|-----|

| Bit Name   | ACK |

| Access     | R/W |

| Default    | 0   |

Bit 0: ACK – Allows firmware to acknowledge or not acknowledge received data 0 = NACK received data (Default)

1 = Acknowledge received data, bit clears upon issue of ACK on PMBus

# 9.5 I2C Status Register (I2CST)

| Address FFF7E410 |         |         |             |           |  |  |  |

|------------------|---------|---------|-------------|-----------|--|--|--|

| Bit Number       | 21      | 20      | 19          | 18        |  |  |  |

| Bit Name         | SCL_RAW | SDA_RAW | CONTROL_RAW | ALERT_RAW |  |  |  |

| Access           | R       | R       | R           | R         |  |  |  |

| Default          | -       | -       | -           | -         |  |  |  |

| Bit Number | 17           | 16         | 15     |

|------------|--------------|------------|--------|

| Bit Name   | CONTROL_EDGE | ALERT_EDGE | MASTER |

| Access     | R            | R          | R      |

| Default    | -            | -          | -      |

| Bit Number | 14       | 13       | 12        | 11        | 10               |

|------------|----------|----------|-----------|-----------|------------------|

| Bit Name   | LOST_ARB | BUS_FREE | UNIT_BUSY | RPT_START | SLAVE_ADDR_READY |

| Access     | R        | R        | R         | R         | R                |

| Default    | -        | -        | -         | -         | -                |

| Bit Number | 9                 | 8               | 7         | 6    |

|------------|-------------------|-----------------|-----------|------|

| Bit Name   | CLK_HIGH_DETECTED | CLK_LOW_TIMEOUT | PEC_VALID | NACK |

| Access     | R                 | R               | R         | R    |

| Default    | -                 | -               | -         | -    |

| Bit Number | 5   | 4            | 3          | 2:0           |

|------------|-----|--------------|------------|---------------|

| Bit Name   | EOM | DATA_REQUEST | DATA_READY | RD_BYTE_COUNT |

| Access     | R   | R            | R          | R             |

| Default    | -   | -            | -          | -             |

Bit 21: SCL\_RAW – PMBus Clock Pin Real Time Status

- 0 = PMBus clock pin observed at logic level low

- 1 = PMBus clock pin observed at logic level high

- Bit 20: SDA\_RAW PMBus Data Pin Real Time Status

- 0 = PMBus data pin observed at logic level low

- 1 = PMBus data pin observed at logic level high

Bit 19: CONTROL\_RAW - Control Pin Real Time Status

- 0 = Control pin observed at logic level low

- 1 = Control pin observed at logic level high

Bit 18: ALERT\_RAW – Alert Pin Real Time Status 0 = Alert pin observed at logic level low

1 = Alert pin observed at logic level high

Bit 17: CONTROL\_EDGE – Control Edge Detection Status

- 0 = Control pin has not transitioned

- 1 = Control pin has been asserted by another device on PMBus

Bit 16: ALERT\_EDGE – Alert Edge Detection Status

- 0 = Alert pin has not transitioned

- 1 = Alert pin has been asserted by another device on PMBus

- Bit 15: MASTER Master Indicator

- 0 = PMBus Interface in Slave Mode or Idle Mode

- 1 = PMBus Interface in Master Mode

- Bit 14: LOST\_ARB Lost Arbitration Flag

- 0 = Master has attained control of PMBus

- 1 = Master has lost arbitration and control of PMBus

- Bit 13: BUS\_FREE PMBus Free Indicator

- 0 = PMBus processing current message

- 1 = PMBus available for new message

- Bit 12: UNIT\_BUSY PMBus Busy Indicator

- 0 = PMBus Interface is idle, ready to transmit/receive message

- 1 = PMBus Interface is busy, processing current message

- Bit 11: RPT\_START Repeated Start Flag

- 0 = No Repeated Start received by interface

- 1 = Repeated Start condition received by interface

- Bit 10: SLAVE\_ADDR\_READY Slave Address Ready

- 0 = Indicates no slave address is available for reading

- 1 = Slave address ready to be read from Receive Data Register (Bits 6:0)

- Bit 9: CLK\_HIGH\_DETECTED Clock High Detection Status

- 0 = No Clock High condition detected

- 1 = Clock High exceeded 50us during message

- Bit 8: CLK\_LOW\_TIMEOUT Clock Low Timeout Status

- 0 = No clock low timeout detected

- 1 = Clock low timeout detected, clock held low for greater than 35ms

- Bit 7: PEC\_VALID PEC Valid Indicator

- 0 = Received PEC not valid (if EOM is asserted)

- 1 = Received PEC is valid

- Bit 6: NACK Not Acknowledge Flag Status

- 0 = Data transmitted has been accepted by receiver

- 1 = Receiver has not accepted transmitted data

- Bit 5: EOM End of Message Indicator

- 0 = Message still in progress or PMBus in idle state.

- 1 = End of current message detected

- Bit 4: DATA\_REQUEST Data Request Flag

- 0 = No data needed by PMBus Interface

- 1 = PMBus Interface request additional data. PMBus clock stretching enabled to stall bus

- until firmware provides transmit data.

- Bit 3: DATA\_READY Data Ready Flag

- 0 = No data available for reading by processor

1 = PMBus Interface read buffer full, firmware required to read data prior to further bus activity. PMBus clock stretching enabled to stall bus until data is read by firmware.

- Bits 2-0: RD\_BYTE\_COUNT Number of Data Bytes available in Receive Data Register

- 0 = No received data

- 1 = 1 byte received. Data located in Receive Data Register, Bits 7-0

- 2 = 2 bytes received. Data located in Receive Data Register, Bits 15-0

- 3 = 3 bytes received. Data located in Receive Data Register, Bits 23-0

- 4 = 4 bytes received. Data located in Receive Data Register, Bits 31-0

### 9.6 I2C Interrupt Mask Register (I2CINTM)

#### Address FFF7E414

| Bit Number | 9 8             |          | 7       | 6     |

|------------|-----------------|----------|---------|-------|

| Bit Name   | CLK_HIGH_DETECT | LOST_ARB | CONTROL | ALERT |

| Access     | R/W             | R/W      | R/W     | R/W   |

| Default    | 1               | 1        | 1       | 1     |

| Bit Number | 5   | 4                | 3            |

|------------|-----|------------------|--------------|

| Bit Name   | EOM | SLAVE_ADDR_READY | DATA_REQUEST |

| Access  | R/W | R/W | R/W |  |

|---------|-----|-----|-----|--|

| Default | 1   | 1   | 1   |  |

| Bit Number | 2          | 1               | 0        |  |

|------------|------------|-----------------|----------|--|

| Bit Name   | DATA_READY | BUS_LOW_TIMEOUT | BUS_FREE |  |

| Access     | R/W        | R/W             | R/W      |  |

| Default    | 1          | 1               | 1        |  |

**Bit 9: CLK\_HIGH\_DETECT** – Clock High Detection Interrupt Mask

- 0 = Generates interrupt if clock high exceeds 50us during message

- 1 = Disables interrupt generation for Clock High detection (Default)

- Bit 8: LOST\_ARB Lost Arbitration Interrupt Mask

- 0 = Generates interrupt upon assertion of Lost Arbitration flag

- 1 = Disables interrupt generation upon assertion of Lost Arbitration flag (Default)

- Bit 7: CONTROL Control Detection Interrupt Mask

- 0 = Generates interrupt upon assertion of Control flag

- 1 = Disables interrupt generation upon assertion of Control flag (Default)

- Bit 6: ALERT Alert Detection Interrupt Mask

- 0 = Generates interrupt upon assertion of Alert flag

- 1 = Disables interrupt generation upon assertion of Alert flag (Default)

- Bit 5: EOM End of Message Interrupt Mask

- 0 = Generates interrupt upon assertion of End of Message flag

- 1 = Disables interrupt generation upon assertion of End of Message flag (Default)

- Bit 4: SLAVE\_ADDR\_READY Slave Address Ready Interrupt Mask

- 0 = Generates interrupt upon assertion of Slave Address Ready flag

- 1 = Disables interrupt generation upon assertion of Slave Address Ready flag (Default)

- Bit 3: DATA\_REQUEST Data Request Interrupt Mask

- 0 = Generates interrupt upon assertion of Data Request flag

- 1 = Disables interrupt generation upon assertion of Data Request flag (Default)

- Bit 2: DATA\_READY Data Ready Interrupt Mask

- 0 = Generates interrupt upon assertion of Data Ready flag

- 1 = Disables interrupt generation upon assertion of Data Ready flag (Default)

- Bit 1: BUS\_LOW\_TIMEOUT Clock Low Timeout Interrupt Mask

- 0 = Generates interrupt upon assertion of Clock Low Timeout flag

- 1 = Disables interrupt generation upon assertion of Clock Low Timeout flag (Default)

- Bit 0: BUS\_FREE Bus Free Interrupt Mask

- 0 = Generates interrupt upon assertion of Bus Free flag

- 1 = Disables interrupt generation upon assertion of Bus Free flag (Default)

# 9.7 I2C Control Register 2 (I2CCTRL2)

#### Address FFF7E418

| Bit Number | 22:21           | 20      | 19     | 18:16    |

|------------|-----------------|---------|--------|----------|

| Bit Name   | RX_BYTE_ACK_CNT | MAN_CMD | TX_PEC | TX_COUNT |

| Access     | Access R/W      |         | R/W    | R/W      |

| Default    | 11              | 0       | 0      | 000      |

| Bit Number | 15      | 14:8       | 7             | 6:0        |

|------------|---------|------------|---------------|------------|

| Bit Name   | PEC_ENA | SLAVE_MASK | MAN_SLAVE_ACK | SLAVE_ADDR |

| Access     | R/W     | R/W        | R/W           | R/W        |

| Default    | 0       | 111_1111   | 0             | 111_1100   |

**Bit 22-21: RX\_BYTE\_ACK\_CNT** – Configures number of data bytes to automatically acknowledge when receiving data in slave mode.

00 = 1 byte received by slave. Firmware is required to manually acknowledge every received byte.

01 = 2 bytes received by slave. Hardware automatically acknowledges the first received byte. Firmware is required to manually acknowledge after the second received byte.

10 = 3 bytes received by slave. Hardware automatically acknowledges the first 2 received bytes. Firmware is required to manually acknowledge after the third received byte.

11 = 4 bytes received by slave. Hardware automatically acknowledges the first 3 received bytes. Firmware is required to manually acknowledge after the third received byte.

11 = 4 bytes received by slave. Hardware automatically acknowledges the first 3 received bytes. Firmware is required to manually acknowledge after the fourth received byte (Default)

#### Bit 20: MAN\_CMD – Manual Command Acknowledgement Mode

0 = Slave automatically acknowledges received command code (Default)

1 = Data Request flag generated after receipt of command code, firmware required to issue ACK to continue message

**Bit 19: TX\_PEC** – Asserted when the slave needs to send a PEC byte at end of message. PMBus Interface will transmit the calculated PEC byte after transmitting the number of data bytes indicated by TX Byte Cnt(Bits 19:17).

0 = No PEC byte transmitted (Default)

1 = PEC byte transmitted at end of current message

Bit 18-16: TX\_COUNT- Number of valid bytes in Transmit Data Register

0 = No bytes valid (Default)

1 = One byte valid, Byte #0 (Bits 7:0 of Receive Data Register)

2 = Two bytes valid, Bytes #0 and #1 (Bits 15:0 of Receive Data Register)

3 = Three bytes valid, Bytes #0-2 (Bits 23:0 of Receive Data Register)

4 = Four bytes valid, Bytes #0-3 (Bits 31:0 of Receive Data Register)

Bit 15: PEC\_ENA – PEC Processing Enable

0 = PEC processing disabled (Default)

1 = PEC processing enabled

**Bit 14-8: SLAVE\_MASK** – Used in address detection, the slave mask enables acknowledgement of multiple device addresses by the slave. Writing a '0' to a bit within the slave mask enables the corresponding bit in the slave address to be either '1' or '0' and still allow for a match. Writing a '0' to all bits in the mask enables the PMBus Interface to acknowledge any device address. Upon power-up, the slave mask defaults to 7Fh, indicating the slave will only acknowledge the address programmed into the Slave Address (Bits 6-0).

Bit 7: MAN\_SLAVE\_ACK- Manual Slave Address Acknowledgement Mode

0 = Slave automatically acknowledges device address specified in SLAVE\_ADDR, Bits 6-0 (Default)

1 = Enables the Manual Slave Address Acknowledgement Mode. Firmware is required to read received address and acknowledge on every message

**Bits 6-0: SLAVE\_ADDR** – Configures the current device address of the slave. Used in automatic slave address acknowledge mode (default mode). The PMBus Interface will compare the received device address with the value stored in the Slave Address bits and the mask configured in the Slave Mask bits. If matching, the slave will acknowledge the device address.

### 9.8 I2C Hold Slave Address Register (I2CHSA)

Address FFF7E41C

| Bit Number | 7:1        | 0        |  |

|------------|------------|----------|--|

| Bit Name   | SLAVE_ADDR | SLAVE_RW |  |

| Access     | R          | R        |  |

| Default    | -          | -        |  |

Bits 7-1: SLAVE\_ADDR – Stored device address acknowledged by the slave Bit 0: SLAVE\_RW – Stored R/W bit from address acknowledged by the slave

0 = Write Access

1 = Read Access

# 9.9 I2C Control Register 3 (I2CCTRL3)

|              | 5               |     | •        |      |      |          |            |      |           |       |          |

|--------------|-----------------|-----|----------|------|------|----------|------------|------|-----------|-------|----------|

| Address FFF7 | 7E420           |     |          |      |      |          |            |      |           |       |          |

| Bit Number   |                 |     |          |      |      |          |            |      |           |       | 23       |

| Bit Name     |                 |     |          |      |      |          |            |      |           | I2C_  | _MODE_EN |

| Access       |                 |     |          |      |      |          |            |      |           |       | R/W      |

| Default      |                 |     |          |      |      |          |            |      |           |       | 0        |

|              |                 |     |          |      |      |          |            |      |           |       |          |

| Bit Number   | 22              |     | 21       |      | 2    | 0        | 1          | 9    |           |       | 18       |

| Bit Name     | MASTER_EN       | SL  | AVE_EN   | CLł  | <_L  | .O_DIS   | IBIAS_     | _B_E | IN        | IBI   | AS_A_EN  |

| Access       | R/W             |     | R/W      |      | R/   | W        | R/         | W    |           |       | R/W      |

| Default      | 0               |     | 1        |      | (    | C        | (          | )    |           |       | 0        |

|              |                 |     |          |      |      |          |            |      |           |       |          |

| Bit Number   | 17              |     | 16       |      | 1    | 5        | 1          | 4    |           |       | 13       |

| Bit Name     | SCL_DIR         | SC  | L_VALUE  | SC   | :L_I | MODE     | SDA        | _DIF | र         | SD    | A_VALUE  |

| Access       | R/W             |     | R/W      |      | R/   | /W       | R/W        |      |           | R/W   |          |

| Default      | 0               |     | 0        |      | (    | 0        | 0          |      |           | 0     |          |

|              |                 |     |          |      |      |          |            |      |           |       |          |

| Bit Number   | 12              |     | 11       |      |      | 10       |            |      | 9         |       | 9        |

| Bit Name     | SDA_MODE        |     | CNTL_I   | DIR  |      | CNTL     | CNTL_VALUE |      | CNTL_MODE |       | MODE     |

| Access       | R/W             |     | R/W      | 1    |      | R/W      |            |      | R/W       |       | /W       |

| Default      | 0               |     | 0        |      | 0    |          |            | 0    |           |       |          |

|              |                 |     |          |      |      |          |            |      |           |       |          |

| Bit Number   | 8               |     | 7        |      |      | 6        |            |      |           | 5     |          |

| Bit Name     | ALERT_DIR       |     | ALERT_VA | ALUE |      | ALERT_   | MODE       |      | CNT       | L_INT | _EDGE    |

| Access       | R/W             |     | R/W      |      |      | R/V      | V          | R/W  |           | V     |          |

| Default      | 0               |     | 0        |      |      | 0        |            |      |           | 0     |          |

|              |                 |     |          |      |      |          |            |      |           |       |          |

| Bit Number   | 4               |     | 3        |      |      | 2        |            |      | 1         |       | 0        |

| Bit Name     | FAST_MODE_P     | LUS | FAST_MC  | DDE  | Βl   | JS_LO_IN | T_EDGE     | A    | LERT_     | EN    | RESET    |

| Access       | R/W             |     | R/W      |      |      | R/W      |            |      | R/W       |       | R/W      |

| Default      | 0               |     | 0        |      |      | 0        |            |      | 0         |       | 0        |

| Bit 23       | : I2C_MODE_EN - |     |          |      |      |          |            |      |           |       |          |

- 0 = Enables PMBus interface capability (Default)

- 1 = Enables I2C interface capability

- Bit 22: MASTER EN PMBus Master Enable

- 0 = Disables PMBus Master capability (Default)

- 1 = Enables PMBus Master capability

- Bit 21: SLAVE EN PMBus Slave Enable

- 0 = Disables PMBus Slave capability

- 1 = Enables PMBus Slave capability (Default)

- Bit 20: CLK\_LO\_DIS Clock Low Timeout Disable

- 0 = Clock Low Timeout Enabled (Default)

- 1 = Clock Low Timeout Disabled

- Bit 19: IBIAS B EN PMBus Current Source B Control

- 0 = Disables Current Source for PMBUS address detection thru ADC (Default)

- 1 = Enables Current Source for PMBUS address detection thru ADC

Bit 16: SCL\_VALUE – Configures output value of PMBus clock pin in GPIO Mode 0 = PMBus clock pin driven low in GPIO Mode (Default) 1 = PMBus clock pin driven high in GPIO Mode Bit 15: SCL\_MODE – Configures mode of PMBus Clock pin 0 = PMBus clock pin configured in functional mode (Default) 1 = PMBus clock pin configured as GPIO Bit 14: SDA DIR – Configures direction of PMBus data pin in GPIO mode 0 = PMBus data pin configured as output (Default) 1 = PMBus data pin configured as input Bit 13: SDA\_VALUE – Configures output value of PMBus data pin in GPIO Mode 0 = PMBus data pin driven low in GPIO Mode (Default) 1 = PMBus data pin driven high in GPIO Mode Bit 12: SDA\_MODE - Configures mode of PMBus Data pin 0 = PMBus data pin configured in functional mode (Default) 1 = PMBus data pin configured as GPIO Bit 11: CNTL\_DIR - Configures direction of Control pin in GPIO mode 0 = Control pin configured as output (Default) 1 = Control pin configured as input Bit 10: CNTL\_VALUE - Configures output value of Control pin in GPIO Mode 0 = Control pin driven low in GPIO Mode (Default) 1 = Control pin driven high in GPIO Mode Bit 9: CNTL\_MODE – Configures mode of Control pin 0 = Control pin configured in functional mode (Default) 1 = Control pin configured as GPIO

0 = Disables Current Source for PMBUS address detection thru ADC (Default)

1 = Enables Current Source for PMBUS address detection thru ADC

Bit 17: SCL DIR – Configures direction of PMBus clock pin in GPIO mode

0 = PMBus clock pin configured as output (Default)

Bit 18: IBIAS A EN – PMBus Current Source A Control

1 = PMBus clock pin configured as input

- Bit 8: ALERT\_DIR Configures direction of Alert pin in GPIO mode

- 0 = Control pin configured as output (Default)

- 1 = Control pin configured as input

- Bit 7: ALERT\_VALUE Configures output value of Alert pin in GPIO Mode

- 0 = Alert pin driven low in GPIO Mode (Default)

- 1 = Alert pin driven high in GPIO Mode

- Bit 6: ALERT\_MODE Configures mode of Alert pin

- 0 = Alert pin configured in functional mode (Default)

- 1 = Aler3 pin configured as GPIO

- Bit 5: CNTL\_INT\_EDGE Control Interrupt Edge Select

- 0 = Interrupt generated on falling edge of Control (Default)

- 1 = Interrupt generated on rising edge of Control

- Bit 4: FAST\_MODE\_PLUS Fast Mode Plus Enable

- 0 = Standard 100 KHz mode enabled (Default)

- 1 = Fast Mode Plus enabled (1MHz operation on PMBus)

- Bit 3: FAST\_MODE Fast Mode Enable

- 0 = Standard 100 KHz mode enabled (Default)

- 1 = Fast Mode enabled (400KHz operation on PMBus)

- Bit 2: BUS\_LO\_INT\_EDGE Clock Low Timeout Interrupt Edge Select

- 0 = Interrupt generated on rising edge of clock low timeout (Default)

- 1 = Interrupt generated on falling edge of clock low timeout

- Bit 1: ALERT\_EN Slave Alert Enable

- 0 = PMBus Alert is not driven by slave, pulled up high on PMBus (Default)

- 1 = PMBus Alert driven low by slave

Bit 0: RESET – PMBus Interface Synchronous Reset

- 0 = No reset of internal state machines (Default)

- 1 = Control state machines are reset to initial states

# **10 SPI Reference**

# 10.1 SPI Control Register (SPICTRL)

Address FFF7E800

| Bit Number |  |  | 23:21   |

|------------|--|--|---------|

| Bit Name   |  |  | CLKRATE |

| Access     |  |  | R/W     |

| Default    |  |  | 000     |

| Bit Number | 20:16  | 15:11 | 10:7  | 6       | 5       |

|------------|--------|-------|-------|---------|---------|

| Bit Name   | FRMLEN | RXCNT | TXCNT | WRSTORE | WRSTART |

| Access     | R/W    | R/W   | R/W   | R/W     | R/W     |

| Default    | 00000  | 00000 | 0000  | 0       | 0       |

| Bit Number | 4   | 3   | 2       | 1     | 0     |

|------------|-----|-----|---------|-------|-------|

| Bit Name   | POL | PHA | INTEN   | MODE  | SPIEN |

| Access     | R/W | R/W | R/W R/W |       | R/W   |

| Default    | 0   | 0   | 0       | 0 0 0 |       |

Bit 23:21: CLKRATE - Master clock rate relative to ICLK

- 0 = SCK is ICLK/2 (Default)

- 1 = SCK is ICLK/4 (Default)

- 2 = SCK is ICLK/8 (Default)

- 3 = SCK is ICLK/16 (Default)

Bit 20:16: FRMLEN – Sets the number of messages (TXCNT + RXCNT) to hold CS low.

Bit 15:11: RXCNT – Sets the number bytes to receive after TXCNT bytes have been transmitted

Bit 10:7: TXCNT – Sets the bytes to transmit from the SPITX registers

Bit 6: WRSTORE – Places or discards data received during TXCNT

- 0 = Data received during TXCNT discarded (Default)

- 1 = Data received during TXCNT placed in RXBUF

- Bit 5: WRSTART- Sets which WRREG initiates transfer

- 0 = Write to SPITX-0 starts message transfer (Default)

- 1 = Write to SPITX-1 starts message transfer

- Bit 4: POL The polarity bit, together with the phase bit, determines the transfer-mode.

- Bit 3: PHA The phase bit, together with the polarity bit, determines the transfer-mode.

- Bit 2: INTEN Enable interrupt generation to the CPU

- 0 = Disabled (Default)

- 1 = Enabled

- Bit 1: MODE Configures SPI mode

- 0 = Master Mode (Default)

- 1 = Slave mode

- Bit 0: SPIEN Enable for SPI Module

- 0 = Disabled (Default)

- 1 = Enabled

# 10.2 SPI Status Register (SPISTAT)

#### Address FFF7E804

| Bit Number | 7:3    | 2     | 1    | 0    |

|------------|--------|-------|------|------|

| Bit Name   | FRMCNT | WRCOL | BUSY | SPIF |

| Access     | R      | R     | R    | R    |

| jDefault   | 0      | 0     | 0    | 0    |

**Bit 12:4: FRMCNT** – Indicates the number of messages remaining in the FRMLEN before SCS will go inactive.

Bit 2: WCOL - SPI interface is busy - only accurate in very simple cases

Bit 1: BUSY – SPI interface is busy – only accurate in very simple cases

Bit 0: SPIF - SPI Flag, set when current message is complete. Write a 1 to this bit to clear it.

## 10.3 SPI Pin Function Register (SPIFUNC)

#### Address FFF7E808

| Bit Number | 3    | 2    | 1   | 0   |

|------------|------|------|-----|-----|

| Bit Name   | MISO | MOSI | SCS | SCK |

| Access     | R/W  | R/W  | R/W | R/W |

| Default    | 0    | 0    | 0   | 0   |

Bit 3: MISO – Selects SPI or GPIO function for SPI-MISO pin

- 0 = SPI function (Default)

- 1 = GPIO function

- Bit 2: MOSI Selects SPI or GPIO function for SPI-MOSI pin

- 0 = SPI function (Default)

- 1 = GPIO function

- Bit 1: SCS Selects SPI or GPIO function for SPI-CS pin

- 0 = SPI function (Default)

- 1 = GPIO function

- Bit 0: SCK Selects SPI or GPIO function for SPI-CK pin

- 0 = SPI function (Default)

- 1 = GPIO function

### 10.4 SPI Pin Direction Register (SPIDIR)

#### Address FFF7E80C

| Bit Number | 3    | 2    | 1   | 0   |

|------------|------|------|-----|-----|

| Bit Name   | MISO | MOSI | SCS | SCK |

| Access     | R/W  | R/W  | R/W | R/W |

| Default    | 0    | 0    | 0   | 0   |

Bit 3: MISO – Selects direction for SPI-MISO pin in GPIO mode

Bit 2: MOSI - Selects direction for SPI-MOSI pin in GPIO mode

0 = Output (Default)

1 = Input

- Bit 1: SCS Selects direction for SPI-CS pin in GPIO mode

- 0 = Output (Default)

- 1 = Input

- Bit 0: SCK Selects direction for SPI-CS pin in GPIO mode

- 0 = Output (Default)

- 1 = Input

### 10.5 SPI Pin GP Out Register (SPIGPOUT)

#### Address FFF7E810

| Bit Number | 3    | 2    | 1   | 0   |

|------------|------|------|-----|-----|

| Bit Name   | MISO | MOSI | SCS | SCK |

| Access     | R/W  | R/W  | R/W | R/W |

| Default    | 0    | 0    | 0   | 0   |

Bit 3: MISO - Selects value for SPI-MISO pin in GPIO output mode

- 0 = Pin driven low (Default)

- 1 = Pin driven high

- Bit 2: MOSI Selects value for SPI-MOSI pin in GPIO output mode

- 0 = Pin driven low (Default)

- 1 = Pin driven high

- Bit 1: SCS Selects value for SPI-CS pin in GPIO output mode

- 0 = Pin driven low (Default)

- 1 = Pin driven high

- Bit 0: SCK Selects value for SPI-CS pin in GPIO output mode

- 0 = Pin driven low (Default)

- 1 = Pin driven high

# 10.6 SPI Pin GP In Register (SPIGPIN)

#### Address FFF7E814

| Bit Number | 3    | 2    | 1   | 0   |

|------------|------|------|-----|-----|

| Bit Name   | MISO | MOSI | SCS | SCK |

| Access     | R    | R    | R   | R   |

| Default    | 0    | 0    | 0   | 0   |

Bit 3: MISO – Selects value for SPI-MISO pin in GPIO output mode

- 1 = Pin driven high

- Bit 2: MOSI Selects value for SPI-MOSI pin in GPIO output mode

- 0 = Pin driven low (Default)

- 1 = Pin driven high

- Bit 1: SCS Selects value for SPI-CS pin in GPIO output mode

- 0 = Pin driven low (Default)

- 1 = Pin driven high

- Bit 0: SCK Selects value for SPI-CS pin in GPIO output mode

- 0 = Pin driven low (Default)

- 1 = Pin driven high

### 10.7 SPI TX Buffer Register (SPITX0)

#### Address FFF7E818

|  | Bit Number | 31:0 |

|--|------------|------|

|--|------------|------|

<sup>0 =</sup> Pin driven low (Default)

| Bit Name | DATA |

|----------|------|

| Access   | R/W  |

| Default  | 0    |

Bits 31:0: Data to be transmitted by SPI interface

# 10.8 SPI TX Buffer Register (SPITX1)

| Address FFF7E8 | 1C |

|----------------|----|

|----------------|----|

| Bit Number | 31:0 |

|------------|------|

| Bit Name   | DATA |

| Access     | R/W  |

| Default    | 0    |

Bits 31:0: Data to be transmitted by SPI interface

# 10.9 SPI Read Buffer Register (SPIRX0)

| Address FFF7E820 |      |  |

|------------------|------|--|

| Bit Number       | 31:0 |  |

| Bit Name         | DATA |  |

| Access           | R    |  |

| Default          | 0    |  |

|                  |      |  |

Bits 31:0: Data received by SPI interface

# 10.10SPI Read Buffer Register (SPIRX1)

| Address FFF7E824 |      |  |

|------------------|------|--|

| Bit Number       | 31:0 |  |

| Bit Name         | DATA |  |

| Access           | R    |  |

| Default          | 0    |  |

Bits 31:0: Data received by SPI interface

# 10.11 SPI Read Buffer Register (SPIRX2)

| Address FFF7E828 |      |  |

|------------------|------|--|

| Bit Number       | 31:0 |  |

| Bit Name         | DATA |  |

| Access           | R    |  |

| Default          | 0    |  |

Bits 31:0: Data received by SPI interface

# **11 IOMUX Reference**

The IOMUX register in the Misc Analog Control peripheral is one of the very few registers to be changed between the UCD3138 and UCD3138064.

The FAULT\_01\_MUX\_SEL bitfield is added to permit the use of Fault 0 and Fault 1 as SPI or I2C pins.

The JTAG\_DATA\_MUX\_SEL field is enhanced to permit the use of TDO and TDI pins for SPI.

## 11.11/O Mux Control Register (IOMUX)

Address FFF7F030

| Bit Number |  | 12:11             |

|------------|--|-------------------|

| Bit Name   |  | FAULT_01 _MUX_SEL |

| Access     |  | R/W               |

| Default    |  | 00                |

| Bit Number | 10:9             | 8:7              | 6:4               |

|------------|------------------|------------------|-------------------|

| Bit Name   | EXT_TRIG_MUX_SEL | JTAG_CLK_MUX_SEL | JTAG_DATA_MUX_SEL |

| Access     | R/W              | R/W              | R/W               |

| Default    | 00               | 10               | 000               |

| Bit Number | 3:2          | 1            | 0             |

|------------|--------------|--------------|---------------|

| Bit Name   | SYNC_MUX_SEL | UART_MUX_SEL | PMBUS_MUX_SEL |

| Access     | R/W          | R/W          | R/W           |

| Default    | 00           | 0            | 0             |

Bits 12-11: FAULT\_01\_MUX\_SEL - Fault 0 and 1 Pin Mux Select

| I/O Pin | 0       | 1       | 2        | 3 |

|---------|---------|---------|----------|---|

| FAULT-0 | FAULT-0 | SPI-CS  | I2C-DATA |   |

| FAULT-1 | FAULT-1 | SPI-CLK | I2C-CLK  |   |

#### Bits 10-9: EXT\_TRIG\_MUX\_SEL - EXT\_TRIG Pin Mux Select

| I/O Pin  | 0        | 1    | 2    | 3     |

|----------|----------|------|------|-------|

| EXT_TRIG | EXT_TRIG | TCAP | SYNC | PWM-0 |

#### Bits 8-7: JTAG\_CLK\_MUX\_SEL – TCK Pin Mux Select

| I/O Pin | 0   | 1    | 2    | 3     |

|---------|-----|------|------|-------|

| ТСК     | ТСК | TCAP | SYNC | PWM-0 |

#### Bits 6-4: JTAG\_DATA\_MUX\_SEL - TDO/TDI Pin Mux Select

| I/O Pin | 0   | 1        | 2       | 3       | 4        |

|---------|-----|----------|---------|---------|----------|

| TDO     | TDO | SCI_TX-0 | ALERT   | FAULT-0 | SPI-MOSI |

| TDI     | TDI | SCI_RX-0 | CONTROL | FAULT-1 | SPI-MISO |

#### Bits 3-2: SYNC\_MUX\_SEL - SYNC Pin Mux Select :w

| I/O Pin | 0    | 1    | 2        | 3     |

|---------|------|------|----------|-------|

| SYNC    | SYNC | TCAP | EXT_TRIG | PWM-0 |

#### Bit 1: UART\_MUX\_SEL - SCL/SDA Pins Mux Select

| I/O Pin  | 0        | 1       |

|----------|----------|---------|

| SCI_TX-1 | SCI_TX-1 | ALERT   |

| SCI_RX-1 | SCI_RX-1 | CONTROL |

#### Bit 0: PMBUS\_MUX\_SEL - SCL/SDA Pins Mux Select

|--|

| SCL | SCL | SCI_TX-0 |

|-----|-----|----------|

| SDA | SDA | SCI_RX-0 |

# **12 DEC-Address Manager Reference**

The DEC generates the memory selects and SAR peripheral select signals by decoding the address and control signals from the ARM processor. In addition, the DEC provides the control signals for the Program and Data Flash.

The assigned memory selects for Cyclone are as follows: