### **TPS60100, TPS60110 DC/DC Converter Evaluation Module**

# User's Guide

June 1999

**Mixed-Signal Products**

**SLVU016**

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

### Contents

| 1 | TPS6 | 0100 and TPS60110 EVM | 1-1 |

|---|------|-----------------------|-----|

|   | 1.1  | Introduction          | 1-2 |

|   | 1.2  | Schematic of the EVM  | 1-3 |

|   | 1.3  | Layout of the EVM     | 1-4 |

|   | 1.4  | Setup of the EVM      | 1-5 |

## Figures

| 1–1 | Schematic of the Evaluation Module (EVM) | 1-3 |

|-----|------------------------------------------|-----|

| 1–2 | Placement of the Components              | 1-4 |

| 1–3 | Top Layer of the EVM                     | 1-5 |

### **Tables**

| 1–1 | Components on the EVM                    | 1-3 |

|-----|------------------------------------------|-----|

| 1–2 | Selected Modes by Connecting the Jumpers | 1-4 |

### **Chapter 1**

### **TPS60100 and TPS60110 EVM**

The evaluation modules (EVM) for the new Texas Instruments (TI<sup>™</sup>) charge pump devices TPS60100 and TPS60110 help designers to evaluate the devices. The TPS60100 and TPS60110 charge pumps (also called switched capacitor DC/DC converters) are regulated voltage doublers.

With these EVMs it is possible to evaluate all different modes of the devices as well as their performance. Using jumpers to adjust the logic pin voltage levels, the devices can be set into the different modes. You only need a voltage source to test the operation of the devices.

The layout of charge pumps is critical, similar to the layout of inductive DC/DC converters. Therefore this given layout is a good tool to reduce evaluation-time for the designer.

#### Topic

1.1

Introduction

1–2

1.2

Schematic of the EVM

1–3

1.3

Layout of the EVM

1–4

1.4

Setup of the EVM

1–5

Page

### 1.1 Introduction

The Texas Instruments TPS60100 and TPS60110 charge pumps are regulated voltage doublers. The TPS60100 has an output voltage of 3.3 V from an input signal between 1.8 V and 3.6 V. The TPS60110 has an output voltage of 5 V from an input voltage between 2.7 V and 5.4 V. Both devices consist of two single-ended charge pumps that can operate either in phase (for minimum external components) or in anti-phase (for minimum output noise). For a description of the different operation modes and a functional description, please refer to the datasheets [literature number SLVS213A (TPS60100) and SLVS215 (TPS60110)].

The minimum number of external parts is three for the single-ended mode (both charge pumps operate in phase) or four in push-pull mode (the two charge pumps operate with 180° phase shift). The EVM is built up with six external parts for optimized performance.

The best performance of the charge pumps can be seen with ceramic capacitors. Actually this would be the most expensive solution because of the higher capacitive parts at the input and output. Therefore, on the TPS60100 or TPS60110 EVMs tantalum capacitors are used for the higher capacitive parts. To reduce the spikes during turnover from the transfer phase (charging of the output capacitor) of one charge pump to that of the other one, a ceramic capacitor is used in parallel with the tantalum ones at the input and output. Tantalum capacitors are not able to filter these spikes because their equivalent series resistance (ESR) is too high to act as fast as a ceramic one.

The flying capacitors have to be ceramic because they must be charged and discharged very fast and so their ESR has to be low. This criterion can only be reached with ceramic capacitors.

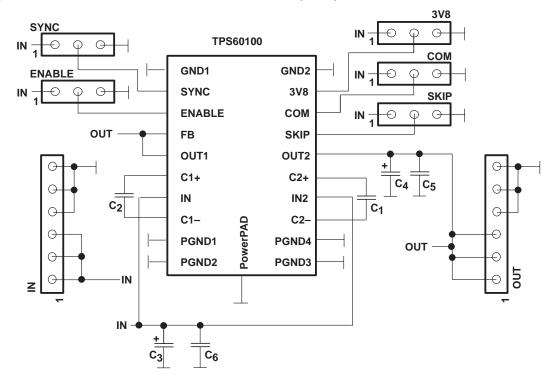

### 1.2 Schematic of the EVM

The schematics of the two EVMs for TPS60100 and TPS60110 are the same. The differences between the boards are the IC itself, the values for the external components (see Table 1–1), and the use of the connector 3V8. The connector 3V8 can be used on the EVM for TPS60100 to adjust the output voltage to 3.8 V. This mode is not implemented on the TPS60110. As long as you do not want to synchronize the TPS60110, connect this pin with a jumper to GND. When the TPS60100 or the TPS60110 is synchronized, the second pin of the connector 3V8 is used to apply the external clock signal.

Figure 1–1. Schematic of the Evaluation Module (EVM)

| COMPONENT                       | TPS60100     | TPS60110     | DESCRIPTION                                 |

|---------------------------------|--------------|--------------|---------------------------------------------|

| C <sub>1</sub> , C <sub>2</sub> | 2.2 μF, 16 V | 2.2 μF, 16 V | Ceramic flying capacitors                   |

| C <sub>3</sub>                  | 10 μF, 16 V  | 15 μF, 16 V  | Tantalum input capacitor                    |

| C <sub>4</sub>                  | 22 μF, 20 V  | 33 μF,16 V   | Tantalum output capacitor                   |

| C <sub>5</sub> , C <sub>6</sub> | 1 μF, 16 V   | 1 μF, 16 V   | Ceramic help capacitors at input and output |

Capacitors  $C_5$  and  $C_6$  are the two ceramic capacitors for reducing the spikes. If spikes are not critical in your application, it is possible to remove these two capacitors.

For the input and output of the voltage, there are two six-pin connectors on the board. Each has the first three pins for the supply (IN or OUT) and the last three pins for the ground (GND) signal.

The five three-pin connectors can be used to connect the five logic pins of the device. These pins are used to adjust the modes of the devices

(see Table 1–2). Each connector has the supply (In) signal at the first pin, the logic input at the second pin, and the ground (GND) signal at the third pin. So it is possible to use jumpers to connect the pin either to input (supply voltage) or to ground. It is also possible to connect any other signal by using an external signal source and connecting it to the second pin. These five pins are logic level CMOS inputs; for the specification of the levels, refer to the datasheets. The value of the signal connected to the logic pins can be higher than the supply voltage, but do not exceed the maximum ratings (see datasheets).

Leaving the second pin of these five three-pin connectors open is not allowed; either connect it via a jumper to the first or third pin, or use an appropriate external signal source with the appropriate signal level.

Table 1–2. Selected Modes by Connecting the Jumpers

| Name | Connected to GND (Pin 3)                                  | Connected to In (Pin 1)                                                                           |

|------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 3V8  | 3.3 V at the output<br>(TPS60110: internal clock is used) | 3.8 V at the output<br>(TPS60110: Do not connect to IN)                                           |

| Com  | Push-pull mode                                            | Single-ended mode                                                                                 |

| EN   | Device is disabled                                        | Device is enabled                                                                                 |

| Skip | Fixed-frequency mode                                      | Pulse-skip mode                                                                                   |

| Sync | Device is internally synchronized                         | Device is externally synchronized, connect the external clock to the second pin of connector 3V8. |

### 1.3 Layout of the EVM

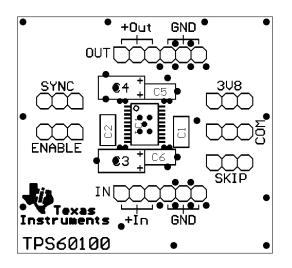

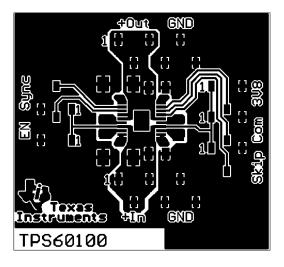

Figure 1–2 and Figure 1–3 show the placement of the components and the layout of the EVM. Components are placed only on the top layer of the board. The signal on the bottom is the ground signal (GND). For good performance, the entire bottom layer is one GND plane, only interrupted by some vias.

Figure 1–2. Placement of the Components

Figure 1–3. Top Layer of the EVM

Table 1–1 contains the values and description of all 6 capacitors that are placed on the EVM.

The space needed for the IC and the capacitors on the EVM is around  $15 \text{ mm} \times 16 \text{ mm} = 240 \text{ mm}^2$ . The capacitors are not optimized for space. They are optimized for performance. It is possible to use smaller capacitors to optimize the layout for minimum board space. On the EVM, it is also possible to solder some other capacitors because the pads are bigger than needed for the given capacitors.

#### 1.4 Setup of the EVM

For proper operation of the EVM, follow these few steps:

- 1) Check if all five logic signals are properly connected, either jumper or external source.

- 2) Connect a load to the output (between GND and Out). TPS60100: 16.5  $\Omega$  to  $\infty\Omega$  or 0 mA to 200 mA TPS60110: 16.7  $\Omega$  to  $\infty\Omega$  or 0 mA to 300 mA

- Connect a signal source (or a battery pack) with the appropriate voltage between the input (In) and ground, GND.

TPS60100: 1.8 V to 3.6 V

TPS60110: 2.7 V to 5.4 V