## **TPS65987DDH and TPS65988DH Host Interface Technical Reference Manual**

# **Technical Reference Manual**

Literature Number: SLVUBH2B July 2018–Revised September 2018

## **Contents**

| 1 | Intro | duction                                              | 10 |

|---|-------|------------------------------------------------------|----|

|   | 1.1   | Introduction                                         | 10 |

|   |       | 1.1.1 Purpose and Scope                              | 10 |

|   |       | 1.1.2 Related Documents                              | 10 |

|   | 1.2   | PD Controller Host Interface Description             | 11 |

|   |       | 1.2.1 Overview                                       |    |

|   |       | 1.2.2 Dual Port Addressing                           |    |

|   | 1.3   | Unique Address Interface                             |    |

|   |       | 1.3.1 Unique Address Interface Protocol              |    |

|   |       | 1.3.2 Unique Address Interface Registers             |    |

| 2 | PD C  | ontroller Policy Modes                               |    |

| - | 2.1   | Overview                                             |    |

|   | 2.2   | Source Policy Modes                                  |    |

|   | 2.3   | Sink Policy                                          |    |

|   | 2.3   | Alternate Modes and Alternate Mode Policy            |    |

| 2 |       | · · · · · · · · · · · · · · · · · · ·                |    |

| 3 | -     | Je Address Interface Register Detailed Descriptions  |    |

|   | 3.1   | 0x14 - 0x19 IntEventX, IntMaskX, IntClearX Registers |    |

|   | 3.2   | 0x1A Status Register                                 |    |

|   | 3.3   | 0x21 Discovered SVIDs Register                       |    |

|   | 3.4   | 0x26 Power Path Status Register                      |    |

|   | 3.5   | 0x27 Global System Configuration                     |    |

|   | 3.6   | 0x28 Port Configuration                              |    |

|   | 3.7   | 0x29 Port Control                                    |    |

|   | 3.8   | 0x2D Boot Flags Register                             |    |

|   | 3.9   | 0x30 RX Source Capabilities Register                 |    |

|   | 3.10  | 0x31 RX Sink Capabilities Register                   |    |

|   | 3.11  | 0x32 TX Source Capabilities Register                 |    |

|   | 3.12  | 0x33 TX Sink Capabilities Register                   |    |

|   | 3.13  | 0x34 Active Contract PDO                             |    |

|   | 3.14  | 0x35 Active Contract RDO                             | 45 |

|   | 3.15  | 0x36 Sink Request RDO                                | 46 |

|   | 3.16  | 0x37 Auto Negotiate Sink                             | 47 |

|   | 3.17  | 0x38 Alternate Mode Entry Sequence                   | 49 |

|   | 3.18  | 0x3F Power Status                                    | 50 |

|   | 3.19  | 0x40 PD Status                                       | 51 |

|   | 3.20  | 0x41 PD3.0 Status                                    | 53 |

|   | 3.21  | 0x42 PD3.0 Configuration Register                    | 54 |

|   | 3.22  | 0x43 Delay Configuration Register                    | 55 |

|   | 3.23  | 0x47 TX Identity                                     | 56 |

|   | 3.24  | 0x48 RX Identity SOP                                 | 57 |

|   | 3.25  | 0x49 RX Identity SOP'                                | 58 |

|   | 3.26  | 0x4A User VID Configuration                          | 59 |

|   | 3.27  | 0x4B MIPI VID Configuration                          |    |

|   | 3.28  | 0x4E RX Attention                                    |    |

|   | 3.29  | 0x4F RX VDM                                          |    |

|   |       |                                                      |    |

| www. | ti.com |                                                                 |     |

|------|--------|-----------------------------------------------------------------|-----|

|      | 3.30   | 0x50 Data Control                                               | 66  |

|      | 3.31   | 0x51 DP SID Configuration                                       | 67  |

|      | 3.32   | 0x52 Intel VID Configuration                                    | 69  |

|      | 3.33   | 0x57 User VID Status                                            | 70  |

|      | 3.34   | 0x58 DP SID Status                                              | 71  |

|      | 3.35   | 0x59 Intel VID Status                                           | 72  |

|      | 3.36   | 0x5C GPIO Configuration                                         | 73  |

|      |        | 3.36.1 GPIO Multiplexor                                         | 75  |

|      |        | 3.36.2 GPIO Events                                              | 75  |

|      | 3.37   | 0x5D Retimer Debug Mode                                         | 82  |

|      | 3.38   | 0x5F Data Status                                                | 83  |

|      | 3.39   | 0x60 RX User VID Attention VDM                                  | 86  |

|      | 3.40   | 0x61 RX User VID Other VDM                                      | 87  |

|      | 3.41   | 0x62 Binary Data Indices                                        | 88  |

|      | 3.42   | 0x63 MIPI VID Status                                            | 89  |

|      | 3.43   | 0x64 I2C Master Config                                          | 90  |

|      | 3.44   | 0x69 TypeC State Register                                       |     |

|      | 3.45   | 0x6B HW Control                                                 |     |

|      | 3.46   | 0x6C App Configuration                                          |     |

|      | 3.47   | 0x70 Sleep Configuration Register                               |     |

|      | 3.48   | 0x71 Received Manufacturer Info Data Block SOP (MIDB)           |     |

|      | 3.49   | 0x72 GPIO Status Register                                       |     |

|      | 3.50   | 0x73 Transmit Manufacturer Info Data Block SOP (MIDB)           |     |

|      | 3.51   | 0x74 Received Alert Data Object (ADO)                           |     |

|      | 3.52   | 0x75 Transmit Alert Data Object (ADO)                           |     |

|      | 3.53   | 0x76 Received Source Capabilities Extended Data Block (SCEDB) 1 |     |

|      | 3.54   | 0x77 Transmit Source Capabilities Extended Data Block (SCEDB)   |     |

|      | 3.55   | 0x78 Received Status Data Block (SDB) 1                         |     |

|      | 3.56   | 0x79 Transmit Status Data Block (SDB)                           |     |

|      | 3.57   | 0x7A Received Battery Status Data Objects (BSDO) 1              |     |

|      | 3.58   | 0x7B Transmit Battery Status Data Objects (BSDO) 1              |     |

|      | 3.59   | 0x7C Received Battery Capability Data Block (BCDB) 1            |     |

|      | 3.60   | 0x7D Transmit Battery Capability Data Block (BCDB) 1            |     |

|      | 3.61   | 0x7E Received Manufacturer Info Data Block SOP' (MIDB) 1        |     |

|      | 3.62   | 0x7F Transmit Manufacturer Info Data Block SOP' (MIDB) 1        |     |

| 4    | One-l  | PD Controller Command and Task Detailed Descriptions 1          |     |

| -    | 4.1    | -                                                               | 111 |

|      | 4.2    |                                                                 | 111 |

|      | 4.3    |                                                                 | 111 |

|      | 4.4    |                                                                 | 12  |

|      | 4.4    |                                                                 | 112 |

|      |        |                                                                 | 113 |

|      | 4.5    |                                                                 | 114 |

|      | 4.0    |                                                                 | 114 |

|      | 4.6    |                                                                 | 115 |

|      | 4.0    | •                                                               | 115 |

|      |        |                                                                 | 116 |

|      | 4.7    |                                                                 | 117 |

|      | 7.7    | •                                                               | 117 |

|      |        | ·                                                               | 118 |

|      |        |                                                                 | 119 |

|      |        | 4.7.3 SWUF – FD DR_Swap to UFP                                  |     |

|      |        | 4.7.4 SWOF – PD DR_Swap to OFF                                  |     |

|      |        |                                                                 | ~ 1 |

## TEXAS INSTRUMENTS

| i.com |

|-------|

|       |

|                  | 4.7.6 'GSkC' – PD Get Sink Capabilities          | 100 |

|------------------|--------------------------------------------------|-----|

|                  |                                                  |     |

|                  |                                                  |     |

|                  | 4.7.8 'SSrC' – PD Send Source Capabilities       |     |

|                  | 4.7.9 'HRST' – PD issue Hard Reset               |     |

|                  | 4.7.10 'CRST' – PD issue Cable Reset             |     |

|                  | 4.7.11 'VDMs' – PD send VDM                      |     |

| 4.8              | Alternate Mode Tasks                             |     |

|                  | 4.8.1 'AMEn' – PD send Enter Mode                |     |

|                  | 4.8.2 'AMEx' – PD send Exit Mode                 |     |

|                  | 4.8.3 'AMDs' – PD Start Alternate Mode Discovery | 131 |

| 4.9              | 'GCdm' – Get Custom Discovered Modes             | 132 |

| 4.10             | Power Switch Tasks                               | 133 |

|                  | 4.10.1 'SRDY' – System ready to sink power       | 133 |

|                  | 4.10.2 'SRYR' – SRDY reset                       | 134 |

| 4.11             | Patch Bundle Update Tasks                        | 135 |

|                  | 4.11.1 'PTCs' – Start Patch Download Sequence    | 135 |

|                  | 4.11.2 'PTCd' – Patch Download                   |     |

|                  | 4.11.3 'PTCc' – Patch Download Complete          |     |

|                  | 4.11.4 'PTCq' – Patch Query                      |     |

|                  | 4.11.5 'PTCr' – Patch Reset                      |     |

|                  | 4.11.6 'FLrr' – Flash Load Read Regions          |     |

|                  | 4.11.7 'FLer' – Flash Erase Region Pointer       |     |

|                  | 4.11.8 'FLrd' – Flash Memory Read                |     |

|                  | 4.11.9 'FLad' – Flash Memory Write Start Address |     |

|                  | 4.11.10 'FLwd' – Flash Memory Write              |     |

|                  | -                                                |     |

|                  |                                                  |     |

| 4.40             | 4.11.12 'FLvy' – Flash Memory Verify             |     |

| 4.12             |                                                  |     |

|                  | 4.12.1 'GPoe' – GPIO Output Enable               |     |

|                  | 4.12.2 'GPie' – GPIO Input Enable                |     |

|                  | 4.12.3 'GPsh' – GPIO Set Output High             |     |

|                  | 4.12.4 'GPsl' – GPIO Set Output Low              |     |

| 4.13             | Miscellaneous Commands                           |     |

|                  | 4.13.1 'ANeg' – Auto Negotiate Sink Update       |     |

|                  | 4.13.2 'DBfg – Clear Dead Battery Flag           |     |

| 4.14             | PD3.0 Specific 4CC Commands                      |     |

|                  | 4.14.1 GSCX – PD Get_Source_Cap_Extended         | 153 |

|                  | 4.14.2 GSSt – PD Get_Status                      | 154 |

|                  | 4.14.3 GBaS – PD Get_Battery_Status              | 155 |

|                  | 4.14.4 GBaC – PD Get_Battery_Cap                 | 156 |

|                  | 4.14.5 GMfI – PD Get_Manufacturer_Info           | 157 |

|                  | 4.14.6 MBWr – Message Buffer Write               | 158 |

|                  | 4.14.7 MBRd – Message Buffer Read                | 159 |

|                  | 4.14.8 SRrq– Security Request                    | 160 |

|                  | 4.14.9 SRrs– Security Response                   | 161 |

|                  | 4.14.10 ALRT – Send Alert Message                | 162 |

| 4.15             | UCSI 4CC Commands                                | 163 |

| <del>т</del> .т5 | 4.15.1 'UCSI' - UCSI Commands                    |     |

|                  |                                                  | 103 |

## List of Figures

| 1-1. | I2C Read/Write Protocol Key                | 11 |

|------|--------------------------------------------|----|

| 1-2. | I2C Unique Address write register protocol | 12 |

| 1-3. | I2C Unique Address read register protocol  | 12 |

## List of Tables

| 1-1.  | Unique Address Interface Registers                                        | 12 |

|-------|---------------------------------------------------------------------------|----|

| 1-2.  | Unique Address Interface Commands                                         | 16 |

| 3-1.  | 0x14 - 0x19 IntEventX, IntMaskX, IntClearX Registers                      | 20 |

| 3-2.  | 0x14 - 0x19 IntEventX, IntMaskX, IntClearX Register Bit Field Definitions | 20 |

| 3-3.  | 0x1A Status Register                                                      | 23 |

| 3-4.  | 0x1A Status Register Bit Field Definitions                                | 23 |

| 3-5.  | 0x21 Discovered SVIDs Register                                            | 25 |

| 3-6.  | 0x21 Discovered SVIDs Register Bit Field Definitions                      | 25 |

| 3-7.  | 0x26 Power Path Status Register                                           | 26 |

| 3-8.  | 0x26 Power Path Status Register Bit Field Definitions                     | 26 |

| 3-9.  | 0x27 Global System Configuration Register                                 | 28 |

| 3-10. | 0x27 Global System Configuration Register Bit Field Definitions           | 28 |

| 3-11. | 0x28 Port Configuration Register                                          |    |

| 3-12. | 0x28 Port Configuration Register Bit Field Definitions                    |    |

| 3-13. | 0x29 Port Control Register                                                |    |

| 3-14. | 0x29 Port Control Register Bit Field Definitions                          | 35 |

| 3-15. | 0x2D Boot Flags Register                                                  |    |

| 3-16. | 0x2D Boot Flags Register Bit Field Definitions                            |    |

| 3-17. | 0x30 RX Source Capabilities Register                                      |    |

| 3-18. | 0x30 RX Source Capabilities Register Bit Field Definitions                |    |

| 3-19. | 0x31 RX Sink Capabilities Register                                        |    |

| 3-20. | 0x31 RX Sink Capabilities Register Bit Field Definitions                  |    |

| 3-21. | 0x32 TX Source Capabilities Register                                      |    |

| 3-22. | 0x32 TX Source Capabilities Register Bit Field Definitions                |    |

| 3-23. | 0x33 TX Sink Capabilities Register                                        |    |

| 3-24. | 0x33 TX Sink Capabilities Register Bit Field Definitions                  |    |

| 3-25. | 0x34 Active Contract PDO Register                                         |    |

| 3-26. | 0x34 Active Contract PDO Register Bit Field Definitions                   |    |

| 3-27. | 0x35 Active Contract RDO Register                                         |    |

| 3-28. | 0x35 Active Contract RDO Register Bit Field Definitions                   |    |

| 3-29. | 0x36 Sink Request RDO Register                                            |    |

| 3-30. | 0x36 Sink Request RDO Register Bit Field Definitions                      |    |

| 3-31. | 0x37 Auto Negotiate Sink Register                                         | 47 |

| 3-32. |                                                                           | 47 |

| 3-33. | 0x38 Alternate Mode Entry Sequence Register                               |    |

| 3-34. | 0x38 Alternate Mode Entry Sequence Register Bit Field Definitions         |    |

| 3-35. | 0x3F Power Status Register                                                | 50 |

| 3-36. | 0x3F Power Status Register Bit Field Definitions                          | 50 |

| 3-37. | 0x40 PD Status Register                                                   | 51 |

| 3-38. | 0x40 PD Status Register Bit Field Definitions                             |    |

| 3-39. | 0x41 PD3.0 Status Register                                                |    |

| 3-40. | 0x41 PD3.0 Status Register Bit Field Definitions                          | 53 |

|       |                                                                           |    |

| 3-41. | 0x42 PD3.0 Configuration Register                                     | 54 |

|-------|-----------------------------------------------------------------------|----|

| 3-42. | 0x42 PD3.0 Configuration Register Bit Field Definitions               |    |

| 3-43. | 0x43 Delay Configuration Register                                     |    |

| 3-44. | 0x43 Delay Configuration Register Bit Field Definitions               |    |

| 3-45. | 0x47 TX Identity Register                                             |    |

| 3-46. | 0x47 TX Identity Register Bit Field Definitions                       |    |

| 3-47. | 0x48 RX Identity SOP Register                                         |    |

| 3-48. | 0x48 RX Identity SOP Register Bit Field Definitions                   |    |

| 3-49. | 0x49 RX Identity SOP' Register                                        |    |

| 3-50. | 0x49 RX Identity SOP' Register Bit Field Definitions                  |    |

| 3-51. | 0x4A User VID Configuration Register                                  |    |

| 3-52. | 0x4A User VID Configuration Register Bit Field Definitions            |    |

| 3-53. | 0x4B MIPI VID Configuration Register                                  |    |

| 3-54. | 0x4B – MIPI VID Configuration Register Bit Field Definitions          |    |

| 3-55. | 0x4E RX Attention Register                                            |    |

| 3-56. | 0x4E RX Attention Register Bit Field Definitions                      |    |

| 3-57. | 0x4F RX VDM Register                                                  |    |

| 3-58. | 0x4F RX VDM Register Bit Field Definitions                            |    |

| 3-59. | 0x50 Data Control Register                                            |    |

| 3-60. | 0x50 Data Control Register Bit Field Definitions                      |    |

| 3-61. | 0x51 DP SID Configuration Register                                    |    |

| 3-62. | 0x51 DP SID Configuration Register Bit Field Definitions              |    |

| 3-63. | 0x52 Intel VID Configuration Register                                 |    |

| 3-64. | 0x52 Intel VID Configuration Register Bit Field Definitions           |    |

| 3-65. | 0x57 User VID Status Register                                         |    |

| 3-66. | 0x57 User VID Status Register Bit Field Definitions                   |    |

| 3-67. | 0x58 DP SID Status Register                                           |    |

| 3-68. | 0x58 DP SID Status Register Bit Field Definitions                     |    |

| 3-69. | 0x59 Intel VID Status Register                                        |    |

| 3-70. | 0x59 Intel VID Status Register Bit Field Definitions                  |    |

| 3-71. | 0x5C GPIO Configuration Register                                      |    |

| 3-72. | 0x5C GPIO Configuration Register Bit Field Definitions                |    |

| 3-73. | GPIO Secondary Functions                                              | 75 |

| 3-74. | GPIO Events                                                           |    |

| 3-75. | 0x5D Retimer Debug Mode Register                                      | 82 |

| 3-76. | 0x5D Retimer Debug Mode Register Bit Field Definitions                | 82 |

| 3-77. | 0x5F Data Status Register                                             | 83 |

| 3-78. | 0x5F Data Status Register Bit Field Definitions                       |    |

| 3-79. | 0x5F Data Status (Equivalent DP Specification Pin Assignment Mapping) | 84 |

| 3-80. | 0x60 RX User VID Attention VDM Register                               | 86 |

| 3-81. | 0x60 RX User VID Attention VDM Register Bit Field Definitions         | 86 |

| 3-82. | 0x61 RX User VID Other VDM Register                                   | 87 |

| 3-83. | 0x61 RX User VID Other VDM Register Bit Field Definitions             | 87 |

| 3-84. | 0x62 Binary Data Indices Register                                     | 88 |

| 3-85. | 0x62 Binary Data Indices Register Bit Field Definitions               | 88 |

| 3-86. | 0x63 MIPI VID Status Register                                         | 89 |

| 3-87. | 0x63 MIPI VID Status Register Bit Field Definitions                   | 89 |

| 3-88. | 0x64 I2C Master Configuration Register                                | 90 |

| 3-89. | 0x64 I2C Master Configuration Register Bit Field Definitions          | 90 |

| www.ti.com |                                                                            |     |  |

|------------|----------------------------------------------------------------------------|-----|--|

| 3-9        | 0. 0x69 TypeC State Register                                               | 91  |  |

| 3-9        | 1. 0x69 TypeC State Register Bit Field Definitions                         | 91  |  |

| 3-9        | 2. 0x6B HW Control Register                                                | 93  |  |

| 3-9        | 3. 0x6B HW Control Register Bit Field Definitions                          | 93  |  |

| 3-9        | 4. 0x6C App Configuration Register                                         | 94  |  |

| 3-9        | 5. 0x6C App Configuration Register Bit Field Definitions                   | 94  |  |

| 3-9        | 6. 0x70 Sleep Configuration Register                                       | 95  |  |

| 3-9        | 7. 0x70 Sleep Configuration Register Bit Field Definitions                 | 95  |  |

| 3-9        | 8. 0x71 Received Manufacturer Info Data Block SOP (MIDB) Register          | 96  |  |

| 3-9        | 9. 0x71 Received Manufacturer Info Data Block SOP (MIDB)                   | 96  |  |

| 3-1        | 00. 0x72 GPIO Status Register                                              | 96  |  |

| 3-1        | 01. 0x72 GPIO Status Register Bit Field Definitions                        | 96  |  |

| 3-1        | 02. 0x73 Transmit Manufacturer Info Data Block SOP (MIDB) Register         | 98  |  |

|            | 03. 0x73 Transmit Manufacturer Info Data Block SOP (MIDB)                  |     |  |

| 3-1        | 04. 0x74 Received Alert Data Object (ADO) Register                         | 99  |  |

|            | 05. 0x74 Received Alert Data Object (ADO)                                  |     |  |

| 3-1        | 06. 0x75 Transmit Alert Data Object (ADO) Register                         | 100 |  |

| 3-1        | 07. 0x75 Transmit Alert Data Object (ADO)                                  | 100 |  |

|            | 08. 0x76 Received Source Capabilities Extended Data Block (SCEDB) Register |     |  |

|            | 09. 0x76 Received Source Capabilities Extended Data Block (SCEDB)          |     |  |

|            | 10. 0x77 Transmit Source Capabilities Extended Data Block (SCEDB) Register |     |  |

|            | 11. 0x77 Transmit Source Capabilities Extended Data Block (SCEDB)          |     |  |

|            | 12. 0x78 Received Status Data Block (SDB) Register                         |     |  |

|            | 13. 0x78 Received Status Data Block (SDB)                                  |     |  |

|            | 14. 0x79 Transmit Status Data Block (SDB) Register                         |     |  |

|            | 15. 0x79 Transmit Source Data Block (SDB)                                  |     |  |

|            | 16. 0x7A Received Battery Status Data Objects (BSDO) Register              |     |  |

|            | 17. 0x7A Received Battery Status Data Objects (BSDO)                       |     |  |

|            | 18. 0x7B Transmit Battery Status Data Objects (BSDO) Register              |     |  |

|            | 19. 0x7B Transmit Battery Status Data Objects (BSDO)                       |     |  |

|            | 20. 0x7C Received Battery Capability Data Block (BCDB) Register            |     |  |

|            | 21. 0x7C Received Battery Capability Data Block (BCDB)                     |     |  |

|            | 22. 0x7D Transmit Battery Capability Data Block (BCDB) Register            |     |  |

|            | 23. 0x7D Transmit Battery Capability Data Block (BCDB)                     |     |  |

|            | 25. 0x7E Received Manufacturer Info Data Block SOP' (MIDB) Register        |     |  |

|            | 26. 0x7F Transmit Manufacturer Info Data Block SOP (MIDB) Register         |     |  |

|            | 27. 0x7F Transmit Manufacturer Info Data Block (MIDB)                      |     |  |

| 4-1        |                                                                            |     |  |

| 4-2        | ·                                                                          |     |  |

| 4-3        |                                                                            |     |  |

| 4-4        | · · · · · · · · · · · · · · · · · · ·                                      |     |  |

| 4-5        |                                                                            |     |  |

| 4-6        |                                                                            |     |  |

| 4-7        |                                                                            |     |  |

| 4-8        | · · · · · · · · · · · · · · · · · · ·                                      |     |  |

| 4-9        | •                                                                          |     |  |

| 4-1        |                                                                            |     |  |

| 4-1        |                                                                            |     |  |

|            |                                                                            |     |  |

| www.ti.com |

|------------|

|------------|

| 4-12. | GSkC' – PD Get Sink Capabilities           | 122 |

|-------|--------------------------------------------|-----|

| 4-13. | 'GSrC' – PD Get Source Capabilities        |     |

| 4-14. | 'SSrC' – PD Send Source Capabilities       |     |

| 4-15. | 'HRST' – PD issue Hard Reset               |     |

| 4-16. | 'CRST' – PD issue Cable Reset              | 126 |

| 4-17. | 'VDMs' – PD send VDM                       |     |

| 4-18. | 'AMEn' – PD send Enter Mode                |     |

| 4-19. | 'AMEx' – PD send Exit Mode                 |     |

| 4-20. | 'AMDs' – PD Start Alternate Mode Discovery |     |

| 4-21. | 'GCdm' – Get Custom Discovered Modes       |     |

| 4-22. | 'SRDY' – System ready to sink power        |     |

| 4-23. | 'SRYR' – SRDY reset                        |     |

| 4-24. | 'PTCs' – Start Patch Load Sequence         |     |

| 4-25. | 'PTCd' – Patch Download                    |     |

| 4-26. | 'PTCc' – Patch Data Transfer Complete      |     |

| 4-27. | 'PTCq' – Patch Query                       |     |

| 4-28. | 'PTCr' – Patch Reset                       |     |

| 4-29. | 'FLrr' – Set Flash Read Region             |     |

| 4-30. | 'FLer' –Flash Erase Region Pointer         |     |

| 4-31. | 'FLrd' – Flash Memory Read                 |     |

| 4-32. | 'FLad' – Flash Memory Write Start Address  |     |

| 4-33. | 'FLwd' – Flash Memory Write                |     |

| 4-34. | 'FLem' – Flash Memory Erase                |     |

| 4-35. | 'FLvy' – Flash Memory Verify               |     |

| 4-36. | 'GPoe' – GPIO Output Enable                |     |

| 4-37. | 'GPie' – GPIO Input Enable                 |     |

| 4-38. | GPsh' – GPIO Set Output High               |     |

| 4-39. | GPsl' – GPIO Set Output Low                |     |

| 4-40. | 'ANeg' – Auto Negotiate Sink Update        |     |

| 4-41. | 'DBfg' – Clear Dead Battery Flag           |     |

| 4-42. | GSCX – PD Get Source Capabilities Extended |     |

| 4-43. | GSSt – PD Get Status                       |     |

| 4-44. | GBaS – PD Get Battery Status               | 155 |

| 4-45. | GBaC – PD Get Battery Capabilities         | 156 |

| 4-46. | GMfI – PD Get Manufacturer Info            |     |

| 4-47. | MBWr – Message Buffer Write                |     |

| 4-48. | MBRd – Message Buffer Read                 | 159 |

| 4-49. | SRrq – Security Request                    | 160 |

| 4-50. | SRrs - Security Response                   | 161 |

| 4-51. | ALRT – Send Alert Message                  | 162 |

| 4-52. | UCSI - PPM_RESET                           | 163 |

| 4-53. | UCSI - CONNECTOR_RESET                     | 163 |

| 4-54. | UCSI - GET_CAPABILITY                      | 165 |

| 4-55. | UCSI - GET_CONNECTOR_CAPABILITY            |     |

| 4-56. | UCSI - SET_UOR.                            | 168 |

| 4-57. | UCSI - SET_PDR                             | 169 |

| 4-58. | UCSI - GET_CONNECTOR_STATUS                |     |

| 4-59. | UCSI - GET_ALTERNATE_MODES                 |     |

| 4-60. | UCSI - GET_CAM_SUPPORTED                   |     |

|       | _                                          |     |

| 4-61. | UCSI - GET_PDOS         | 174 |

|-------|-------------------------|-----|

| 4-62. | UCSI - GET_ERROR_STATUS | 175 |

## Introduction

### 1.1 Introduction

#### 1.1.1 Purpose and Scope

This document describes the Host Interface for the TPS65987D and TPS65988 Type-C Port Switch / Power Delivery (PD) Controller devices.

#### 1.1.2 Related Documents

- Universal Serial Bus Specification, Revision 2.0, April 27, 2000 plus ECN and Errata. http://www.usb.org/developers/docs/usb20\_docs/

- Battery Charging Specification, Revision 1.2, December 7, 2010 plus Errata.

- Universal Serial Bus 3.1 Specification, Revision 1.0, July 26, 2013 and ECNs approved through August 11, 2014. www.usb.org/developers/docs

- USB Power Delivery Specification Revision 3.0, Version 1.0a www.usb.org/developers/docs

- USB Type-C Cable and Connector Specification Revision 1.2, March 25, 2016. www.usb.org/developers/docs

- VESA DisplayPort (DP) Standard, Version 1.3, September 17, 2014.

- Proposed DisplayPort Alt Mode on USB Type-C Standard, Version 1, Draft 5, September 6, 2014.

### **1.2 PD Controller Host Interface Description**

#### 1.2.1 Overview

The PD Controller provides a slave I2C port to interface to a host. The Host Interface provides general status information about the PD Controller, ability to control the PD Controller, status of USB Type-C Port and communications to/from a connected device and/or cable via USB PD messages.

The PD Controller supports a single I2C address for each USB-C port. A single port device will have a total of one unique I2C address, and a dual port device will have a total of two unique I2C addresses. This unique address for each USB-C port, defined as the Unique I2C address, is used for direct interaction with a specific USB-C port within the PD controller. All Host Interface communication that uses the Unique I2C address is referred to as Unique Address Interface.

The PD Controller supports a register-based Unique Address Interface. Section 1.3.1 lists the Unique Address Interface registers and Table 1-1 provides detailed Unique Address Interface register descriptions.

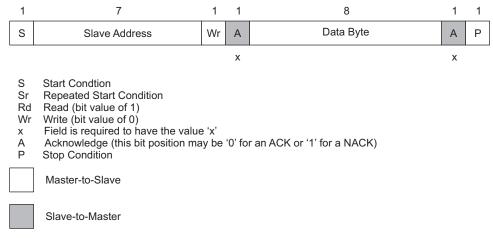

The key to the protocol diagrams is in the SMBus Specification, version 2.0 and is repeated here in part in Figure 1-1.

Figure 1-1. I2C Read/Write Protocol Key

### 1.2.2 Dual Port Addressing

The dual port PD Controller supports two identical ports in a single device. The Host, when present in the system, requires a method to address each port, Port 1 or Port 2, independently over each I2C interface.

For I2C1, Port1 and Port2 addresses are determined by the voltage sensed at the ADCIN2 terminal. The voltage at ADCIN2 is generated by a resistor divider from LDO\_3V3 to ground. By changing the divider ratio, four pairs of slave addresses are possible. Each pair of slave addresses corresponds to Port 1 and Port 2 slave addresses. By default, I2C2 Port1 and Port2 addresses are unique but fixed. Refer to the TPS65988 Datasheet for further details. If TBTControllerType is set to 11b in the 0x27 Global System Configuration Register, then I2C2 Port1 and Port2 addresses are set to the same values as the I2C1 Port1 and Port2 addresses.

### **1.3 Unique Address Interface**

#### 1.3.1 Unique Address Interface Protocol

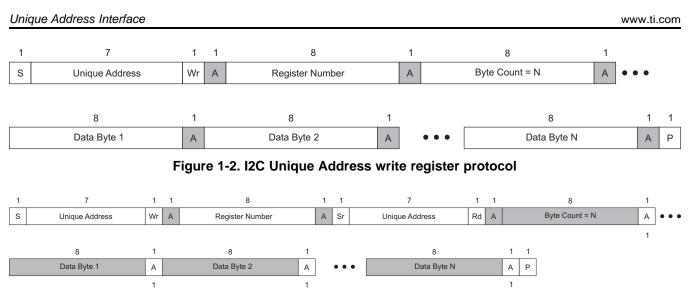

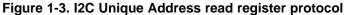

The Unique Address Interface allows for complex interactions between an I2C master and each PD Controller. The I2C Slave unique address is used to receive or respond to Host Interface protocol commands. Figure 1-2 and Figure 1-3 show the write and read protocols, respectively.

### 1.3.2 Unique Address Interface Registers

The PD Controller supports Unique Address Interface registers (Unique Address Registers) provided in Table 1-1. Unless otherwise indicated, registers are little endian (least significant byte in Data Byte 1). Registers that use four character codes (4CC) are defined where the first character corresponds to the ASCII value of Data Byte 1, the second character corresponds to the ASCII value of Data Byte 1, the second character corresponds to the ASCII value of Data Byte 2, and so forth. Any 4CC codes that are less than 4 characters pad the tail with spaces (0x20). For a dual port PD controller, each port has its own independent set of Unique Address Registers, unless a Unique Address Register specifies that it is a register shared across both ports of the device.

| Register<br>Number <sup>(1)</sup> | Register<br>Name        | Read/Write | # Data<br>Bytes | Description                                                                                                                                                                                                                                                                                           |  |

|-----------------------------------|-------------------------|------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x00                              | VID <sup>(2)</sup>      | RO         | 4               | 4 Intel-assigned Thunderbolt <sup>™</sup> Vendor ID, with the most significant 8<br>bits of the field padded with 0's. OTP boot loader will use TI's<br>Vendor ID; application firmware may change to another vendor's<br>VID.                                                                        |  |

| 0x01                              | DID <sup>(2)</sup>      | RO         | 4               | 4 Vendor-specific Device ID. Boot loader will use Device ID specific<br>to part (expected to be different per TI part number). Application<br>firmware may change to a value specified by vendor.                                                                                                     |  |

| 0x02                              | ProtoVer <sup>(2)</sup> | RO         | 4               | Thunderbolt <sup>™</sup> Protocol Version. Required to return 1 per current specification.                                                                                                                                                                                                            |  |

| 0x03                              | Mode <sup>(2)</sup>     | RO         | 4CC             | Indicates the operational state of the port.<br>'APP ' = The PD Controller is fully functioning in the application<br>firmware.<br>'BOOT' = Device booting in dead battery.<br>'PTCH' = Device in patch mode.<br>Any other value indicates the PD Controller is functioning in a<br>limited capacity. |  |

| 0x04                              | Type <sup>(2)</sup>     | RO         | 4CC             | 4CC PD Controller default response is 'I2C ' (note space as 4th character).                                                                                                                                                                                                                           |  |

| 0x05                              | UID <sup>(2)</sup>      | RO         | 16              | 16 128-bit unique ID (unique for each PD Controller Port)                                                                                                                                                                                                                                             |  |

| 0x06                              | Customer<br>Use         | RO         | 8               | These 8 bytes are allocated for customer use as needed.<br>Initialized by Application Customization.                                                                                                                                                                                                  |  |

| 0x07                              | Reserved                | RO         | 0               | This register is not to be allocated and shall return a length of 0.                                                                                                                                                                                                                                  |  |

(1) Registers marked (Lock) may be write-protected unless the LOCK command is used to successfully unlock registers.

<sup>(2)</sup> On devices containing two ports, these registers are shared between the ports.

| Register<br>Number <sup>(1)</sup> | Register<br>Name                                                | Read/Write | # Data<br>Bytes | Description                                                                                                                                                                                                                                                                                                                                             |  |

|-----------------------------------|-----------------------------------------------------------------|------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x08                              | Cmd1                                                            | RW         | 4CC             | Command register used for the primary command interface.<br>Cleared to 0x0000_0000 by the PD Controller during initialization<br>and after successful processing of every command. If an<br>unrecognized command is written to this register, it is replaced by a<br>4CC value of "!CMD".                                                               |  |

| 0x09                              | Data1                                                           | RW         | 64              | Data register used for the primary command interface.                                                                                                                                                                                                                                                                                                   |  |

| 0x0A-0x0E                         | Reserved                                                        | RO         | 0               | These registers are not allocated and return a length of 0.                                                                                                                                                                                                                                                                                             |  |

| 0x0F                              | Version <sup>(2)</sup>                                          | RO         | 4               | Binary Coded Decimal version number, bootloader/application code version.Represented as VVVV.MM.RR with leading 0's removed.e.g. 65794d (decimal) -> 0x00010102 -> 0001.01.02 -> 1.1.2 (version). The version information is returned in little Endian format i.e. byte 1 = RR, byte 2 = MM, etc.                                                       |  |

| 0x10                              | Cmd2                                                            | RW         | 4CC             | Command register used for the secondary command interface.<br>Shall be cleared to 0x00000000 by PD Controller during<br>initialization and after successful processing of every command. If<br>an unrecognized command is written to this register it shall be<br>replaced by a 4CC value of "!CMD".                                                    |  |

| 0x11                              | Data2                                                           | RW         | 64              | Data register used for the secondary command interface.                                                                                                                                                                                                                                                                                                 |  |

| 0x12-0x13                         | Reserved                                                        | RO         | 0               | These registers are not allocated and return a length of 0.                                                                                                                                                                                                                                                                                             |  |

| 0x14                              | IntEvent1                                                       | RO         | 11              | Interrupt event bit field for I2C_IRQ1 (output is low if any bit in this register is set). See Table 3-1.                                                                                                                                                                                                                                               |  |

| 0x15                              | IntEvent2                                                       | RO         | 11              | Interrupt event bit field for I2C_IRQ2 (output is low if any bit in this register is set). See Table 3-1.                                                                                                                                                                                                                                               |  |

| 0x16                              | IntMask1                                                        | RW         | 11              | Interrupt mask bit field corresponding to IntEvent1. A bit in<br>IntEvent1 cannot be set if it is cleared in this register. See Table 3-<br>1.                                                                                                                                                                                                          |  |

| 0x17                              | IntMask2                                                        | RW         | 11              | Interrupt mask bit field corresponding to IntEvent2. A bit in<br>IntEvent2 cannot be set if it is cleared in this register. See Table 3-<br>1.                                                                                                                                                                                                          |  |

| 0x18                              | IntClear1                                                       | RW         | 11              | Interrupt clear bit field for IntEvent1. Bits set in this register are cleared from IntEvent1. See Table 3-1.                                                                                                                                                                                                                                           |  |

| 0x19                              | IntClear2                                                       | RW         | 11              | Interrupt clear bit field for IntEvent2. Bits set in this register are cleared from IntEvent2. See Table 3-1.                                                                                                                                                                                                                                           |  |

| 0x1A                              | Status                                                          | RO         | 8               | Status bit field for non-interrupt events. See Table 3-3.                                                                                                                                                                                                                                                                                               |  |

| 0x1B-0x1F                         | Reserved                                                        | RO         | 0               | These registers are not allocated and return a length of 0.                                                                                                                                                                                                                                                                                             |  |

| 0x20                              | System<br>Power State <sup>(3)</sup>                            | RW         | 1               | System Power State<br>0x00 = S0, 0x03 = S3, 0x04 = S4, 0x05 = S5                                                                                                                                                                                                                                                                                        |  |

| 0x21                              | Discovered<br>SVIDs                                             | RO         | 49              | SVID information returned from Discover SVIDs messages                                                                                                                                                                                                                                                                                                  |  |

| 0x22-0x25                         | Reserved                                                        | RO         | 0               | These registers are not allocated and return a length of 0.                                                                                                                                                                                                                                                                                             |  |

| 0x26                              | Power Path<br>Status <sup>(3)</sup>                             | RO         | 8               | Power Path Status. See Table 3-7.                                                                                                                                                                                                                                                                                                                       |  |

| 0x27                              | Global<br>System<br>Configuration <sup>(</sup><br><sub>3)</sub> | RW         | 14              | Configuration bits that define hardware that is common to all ports<br>and in most cases will not change in normal operation or will not<br>require immediate action if changed. Any modifications to this<br>register will cause a port disconnect and reconnect with the new<br>settings. See Table 3-9.<br>Initialized by Application Customization. |  |

| 0x28                              | Port<br>Configuration                                           | RW         | 8               | Configuration bits that define hardware that is specific to a the respective port and in most cases will not change in normal operation or will not require immediate action if changed. Any modifications to this register will cause a port disconnect and reconnect with the new settings. See Table 3-11. Initialized by Application Customization. |  |

$^{\scriptscriptstyle (3)}$   $\,$  On devices containing two ports, these registers are shared between the ports.

| Register<br>Number <sup>(1)</sup> | Register<br>Name                    | Read/Write | # Data<br>Bytes | Description                                                                                                                                                                                                                                                                                                                                                                         |  |

|-----------------------------------|-------------------------------------|------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x29                              | Port Control                        | RW         | 4               | Configuration bits affecting system policy. These bits may change<br>during normal operation and are used for controlling the respective<br>port. The PD Controller will not take immediate action upon writing.<br>Changes made to this register will take effect the next time the<br>appropriate policy is invoked. See Table 3-14.<br>Initialized by Application Customization. |  |

| 0x2A                              | Reserved                            | RO         | 0               | These registers are not allocated and return a length of 0.                                                                                                                                                                                                                                                                                                                         |  |

| 0x2B                              | Reserved                            | RO         | 0               | These registers are not allocated and return a length of 0.                                                                                                                                                                                                                                                                                                                         |  |

| 0x2C                              | Reserved                            | RO         | 0               | These registers are not allocated and return a length of 0.                                                                                                                                                                                                                                                                                                                         |  |

| 0x2D                              | Boot Flags <sup>(3)</sup>           | RO         | 12              | Provides details on PD Controller boot flags and silicon revision.<br>See Table 3-15.                                                                                                                                                                                                                                                                                               |  |

| 0x2E                              | Build<br>Identifier <sup>(3)</sup>  | RO         | 49              | ASCII string returns uniquely identifying custom build<br>information.40 Hex Characters representing the build + 1<br>underscore character + MMDDYYYY (build date) + null terminator<br>(0).Returns 0 length on released firmware.                                                                                                                                                  |  |

| 0x2F                              | Device Info <sup>(3)</sup>          | RO         | 47              | ASCII string with hardware and firmware version information of the PD Controller.                                                                                                                                                                                                                                                                                                   |  |

| 0x30                              | RX Source<br>Capabilities           | RO         | 29              | Stores latest Source Capabilities message received over BMC.<br>See Table 3-17.                                                                                                                                                                                                                                                                                                     |  |

| 0x31                              | RX Sink<br>Capabilities             | RO         | 29              | Stores latest Sink Capabilities message received over BMC. See Table 3-19.                                                                                                                                                                                                                                                                                                          |  |

| 0x32                              | TX Source<br>Capabilities           | RW         | 64              | Stores PDOs and settings for outgoing Source Capabilities<br>messages to send over BMC See Table 3-21 .<br>Initialized by Application Customization.                                                                                                                                                                                                                                |  |

| 0x33                              | TX Sink<br>Capabilities             | RW         | 57              | Stores PDOs for outgoing Sink Capabilities messages to send over<br>BMC. See Table 3-23.<br>Initialized by Application Customization.                                                                                                                                                                                                                                               |  |

| 0x34                              | Active<br>Contract PDO              | RO         | 6               | Stores PDOs data for the current contract. See Table 3-25.                                                                                                                                                                                                                                                                                                                          |  |

| 0x35                              | Active<br>Contract RDO              | RO         | 4               | Stores the RDO of the current contract, or all zeroes if no contract. See Table 3-27.                                                                                                                                                                                                                                                                                               |  |

| 0x36                              | Sink Request<br>RDO                 | RO         | 4               | Most recent RDO sent by Sink, regardless of current PD Controller<br>power role. May not be the current contract if an Accept has not yet<br>been sent or if a Reject/Wait has been sent instead. Once it<br>becomes active, it will be copied into register 0x35. See Table 3-29.                                                                                                  |  |

| 0x37                              | Auto<br>Negotiate<br>Sink           | RW         | 20              | Defines the voltage range between which the system can function properly, allowing the PD Controller to negotiate its own contracts. Initialized by Application Customization. See Table 3-31.                                                                                                                                                                                      |  |

| 0x38                              | Alternate<br>Mode Entry<br>Sequence | RW         | 16              | Allows for selection of up to four alternate modes along with their sequence for auto entry attempt. A single mode will be entered automatically if valid. See Table 3-33. Initialized by Application Customization.                                                                                                                                                                |  |

| 0x39-0x3E                         | Reserved                            | RO         | 0               | These registers are not allocated and return a length of 0.                                                                                                                                                                                                                                                                                                                         |  |

| 0x3F                              | Power Status                        | RO         | 2               | Status bit field for data consumed by the System Power Policy Manager. See Table 3-35.                                                                                                                                                                                                                                                                                              |  |

| 0x40                              | PD Status                           | RO         | 4               | Status bit field for PD messages and state machine. See Table 3-<br>37.                                                                                                                                                                                                                                                                                                             |  |

| 0x41                              | PD3.0 Status                        | RO         | 4               | Satus bit field for PD3.0 messages and state machine. See Table 3-39.                                                                                                                                                                                                                                                                                                               |  |

| 0x42                              | PD3.0<br>Configuration              | RW         | 4               | PD3.0 configuration settings. See Table 3-41.                                                                                                                                                                                                                                                                                                                                       |  |

| 0x43                              | Delay<br>Configuration              | RW         | 9               | Delay configuration settings. See Section 3.22.                                                                                                                                                                                                                                                                                                                                     |  |

| 0x44-0x46                         | Reserved                            | RO         | 0               | These registers are not allocated and return a length of 0.                                                                                                                                                                                                                                                                                                                         |  |

| Table 1-1. Unique | Address Interfac | e Registers | (continued) |

|-------------------|------------------|-------------|-------------|

|-------------------|------------------|-------------|-------------|

| Register<br>Number <sup>(1)</sup> | Register<br>Name                   | Read/Write | # Data<br>Bytes | Description                                                                                                                                                                                                          |  |

|-----------------------------------|------------------------------------|------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x47                              | TX Identity                        | RW         | 49              | Data to send over BMC as a response to Discover Identity. See Table 3-45.<br>Initialized by Application Customization.                                                                                               |  |

| 0x48                              | RX Identity<br>SOP                 | RO         | 28              | Latest Discover Identity response received over BMC from standard SOP. See Table 3-47.                                                                                                                               |  |

| 0x49                              | RX Identity<br>SOP'                | RO         | 28              | Latest Discover Identity response received over BMC from standard SOP'. See Table 3-49.                                                                                                                              |  |

| 0x4A                              | User VID<br>Configuration          | RW         | 64              | User VID Configuration. See Table 3-51.<br>Initialized by Application Customization.                                                                                                                                 |  |

| 0x4B-0x4D                         | Reserved                           | RO         | 0               | These registers are not allocated and return a length of 0.                                                                                                                                                          |  |

| 0x4E                              | RX Attention                       | RO         | 29              | Latest Structured VDM Attention Initiator message received over<br>BMC. NOTE: Only Structured VDM "Attention" messages get<br>stored in this buffer. See register 0x4F for all other inbound<br>VDMs:See Table 3-55. |  |

| 0x4F                              | RX VDM                             | RO         | 29              | Latest VDM message received over BMC except for Structured VDM Attention Initiator messages and SOP*_Debug messages). See Table 3-57.                                                                                |  |

| 0x50                              | Data Control                       | RW         | 6               | Data provided by the Thunderbolt Controller. See .                                                                                                                                                                   |  |

| 0x51                              | DP SID<br>Configuration            | RW         | 6               | DisplayPort Alternate Mode configuration. See Table 3-61.<br>Initialized by Application Customization.                                                                                                               |  |

| 0x52                              | Intel VID<br>Configuration         | RW         | 7               | Intel VID Thunderbolt Alternate Mode Configuration. See Table 3-<br>63.<br>Initialized by Application Customization.                                                                                                 |  |

| 0x53                              | Reserved                           | RO         | 0               | Reserved.                                                                                                                                                                                                            |  |

| 0x54                              | Reserved                           | RO         | 0               | Reserved.                                                                                                                                                                                                            |  |

| 0x55                              | Reserved                           | RO         | 0               | Reserved.                                                                                                                                                                                                            |  |

| 0x56                              | Reserved                           | RO         | 0               | Reserved.                                                                                                                                                                                                            |  |

| 0x57                              | User VID<br>Status                 | RO         | 2               | User VID Status. See Table 3-65.                                                                                                                                                                                     |  |

| 0x58                              | DP SID<br>Status                   | RO         | 37              | DisplayPort Alternate Mode Status. See Table 3-67.                                                                                                                                                                   |  |

| 0x59                              | Intel VID<br>Status                | RO         | 9               | Intel VID Thunderbolt Alternate Mode Status. See Table 3-69.                                                                                                                                                         |  |

| 0x5A                              | Reserved                           | RO         | 0               | Reserved.                                                                                                                                                                                                            |  |

| 0x5B                              | Reserved                           | RO         | 0               | Reserved.                                                                                                                                                                                                            |  |

| 0x5C                              | GPIO<br>Configuration <sup>(</sup> | RO         | 64              | Application-specific GPIO Configurations. See Table 3-71.                                                                                                                                                            |  |

| 0x5D                              | Retimer<br>Debug Mode              | RW         | 4               | Holds data read from Retimer's Debug Mode Register                                                                                                                                                                   |  |

| 0x5E                              | Reserved                           | RO         | 0               | Reserved.                                                                                                                                                                                                            |  |

| 0x5F                              | Data Status                        | RO         | 5               | Status bit field of data consumed by the System Data Policy Manager. See Table 3-77.                                                                                                                                 |  |

| 0x60                              | RX User VID<br>Attention<br>VDM    | RO         | 29              | Latest Structured VDM Attention Initiator message received for User VID. See Table 3-80.                                                                                                                             |  |

| 0x61                              | RX User VID<br>Other VDM           | RO         | 29              | Latest Unstructured VDM or a non-Attention Structured VDM received for User VID. See Table 3-82.                                                                                                                     |  |

| 0x62                              | Binary Indices                     | RW         | 12              | See .                                                                                                                                                                                                                |  |

| 0x63                              | MIPI VID<br>Status                 | RO         | 0               | See Section 3.42                                                                                                                                                                                                     |  |

<sup>(4)</sup> These registers are used by the TPS6598x Application Customizer Tool to properly configure the device. Modifying these registers directly is not supported by TI.

| Register<br>Number <sup>(1)</sup> Register<br>Name         Read/Write         # Data<br>Bytes         Description |                               |    |    | Description                                                                 |  |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------|----|----|-----------------------------------------------------------------------------|--|

| 0x64                                                                                                              | I2C Master<br>Config          | RW | 16 | See Section 3.43                                                            |  |

| 0x66-0x68                                                                                                         | Reserved                      | RO | 0  | These registers are not allocated and return a length of 0.                 |  |

| 0x69                                                                                                              | CCn Pin<br>States             | RO | 4  | Contains current status of both CCn pins. See Table 3-90.                   |  |

| 0x6A                                                                                                              | Reserved                      | RO | 0  | This register is not allocated and returns a length of 0.                   |  |

| 0x6B                                                                                                              | HW Control                    | RW | 9  | Used to control various hardware peripherals on the device. See Table 3-92. |  |

| 0x6C                                                                                                              | App Config <sup>(4)</sup>     | RO | 60 | Application-specific Configurations. See .                                  |  |

| 0x6D - 0x6F                                                                                                       | Reserved                      | RO | 0  | These registers are not allocated and return a length of 0.                 |  |

| 0x70                                                                                                              | Sleep<br>Configuration        | RW | 1  | Sleep Configurations. Initialized by application firmware. See Table 3-96.  |  |

| 0x71                                                                                                              | RX MIDB<br>SOP                | RO | 26 | Received Manufacturer Info Data Block SOP (MIDB). See Section 3.48.         |  |

| 0x72                                                                                                              | GPIO<br>Status <sup>(5)</sup> | RO | 8  | Captures status and settings of all GPIO pins. See Table 3-100.             |  |

| 0x73                                                                                                              | TX MIDB<br>SOP                | RW | 26 | Transmit Manufacturer Info Data Block SOP (MIDB). See Section 3.50.         |  |

| 0x74                                                                                                              | RX ADO                        | RO | 4  | Received Alert Message. See Section 3.51.                                   |  |

| 0x75                                                                                                              | TX ADO                        | RW | 4  | Transmit Alert Message. See Section 3.52.                                   |  |

| 0x76                                                                                                              | RX SCEDB                      | RO | 24 | Received Source Capabilities Extended Data Block (SCEDB). See Table 3-108.  |  |

| 0x77                                                                                                              | TX SCEDB                      | RW | 24 | Transmit Source Capabilities Extended Data Block (SCEDB). See Table 3-110.  |  |

| 0x78                                                                                                              | RX SDB                        | RO | 7  | Received Status Data Block (SDB), See Table 3-112.                          |  |

| 0x79                                                                                                              | TX SDB                        | RW | 7  | Transmit Status Data Block (SDB), See Table 3-114.                          |  |

| 0x7A                                                                                                              | RX BSDO                       | RO | 32 | Received Battery Status Data Objects (BSDO). See Table 3-116.               |  |

| 0x7B                                                                                                              | TX BSDO                       | RW | 32 | Transmit Battery Status Data Objects (BSDO). See Section 3.58.              |  |

| 0x7C                                                                                                              | RX BCDB                       | RO | 9  | Received Battery Capability Data Block (BCDB). See Table 3-120.             |  |

| 0x7D                                                                                                              | TX BCDB                       | RW | 63 | Transmit Battery Capability Data Block (BCDB). See Section 3.60.            |  |