# User Guide for Powering Jacinto<sup>™</sup> 7 J7200 DRA821 with Single TPS6594-Q1 PMIC, PDN-2A

#### **ABSTRACT**

This User's Guide can be used as a guide for integrating the TPS65941515-Q1 power management integrated circuit (PMIC) into a system powering the Automotive Jacinto™ 7 DRA821 processor.

#### **Table of Contents**

| 1 Introduction                                          |    |

|---------------------------------------------------------|----|

| 2 Device Versions                                       | 2  |

| 3 Processor Connections                                 | 3  |

| 3.1 Power Mapping                                       | 3  |

| 3.2 Control Mapping                                     | 6  |

| 4 Supporting Functional Safety Systems                  | 9  |

| 4.1 Achieving ASIL-B System Requirements                | 10 |

| 4.2 Achieving up to ASIL-D System Requirements          | 10 |

| 5 Static NVM Settings                                   | 11 |

| 5.1 Application-Based Configuration Settings            | 12 |

| 5.2 Device Identification Settings                      |    |

| 5.3 BUCK Settings                                       |    |

| 5.4 LDO Settings                                        | 15 |

| 5.5 VCCA Settings                                       |    |

| 5.6 GPIO Settings                                       |    |

| 5.7 Finite State Machine (FSM) Settings                 | 18 |

| 5.8 Interrupt Settings                                  |    |

| 5.9 POWERGOOD Settings                                  | 21 |

| 5.10 Miscellaneous Settings                             | 22 |

| 5.11 Interface Settings                                 | 23 |

| 5.12 Watchdog Settings                                  | 23 |

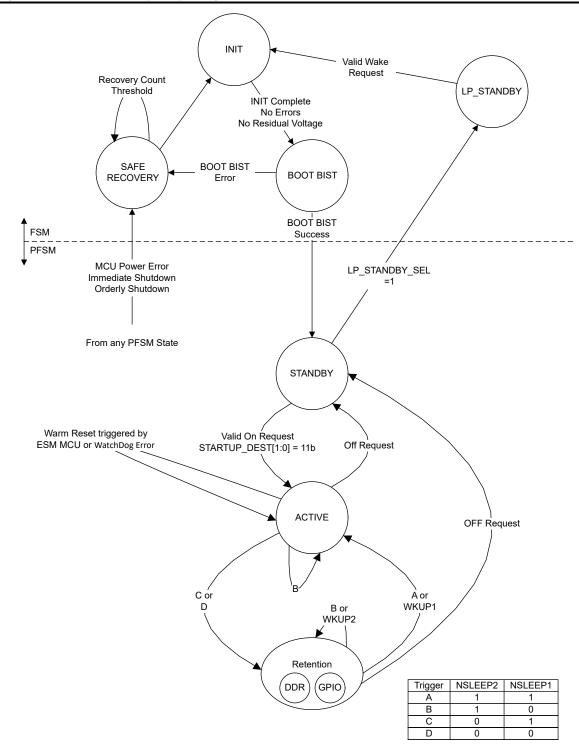

| 6 Pre-Configurable Finite State Machine (PFSM) Settings | 24 |

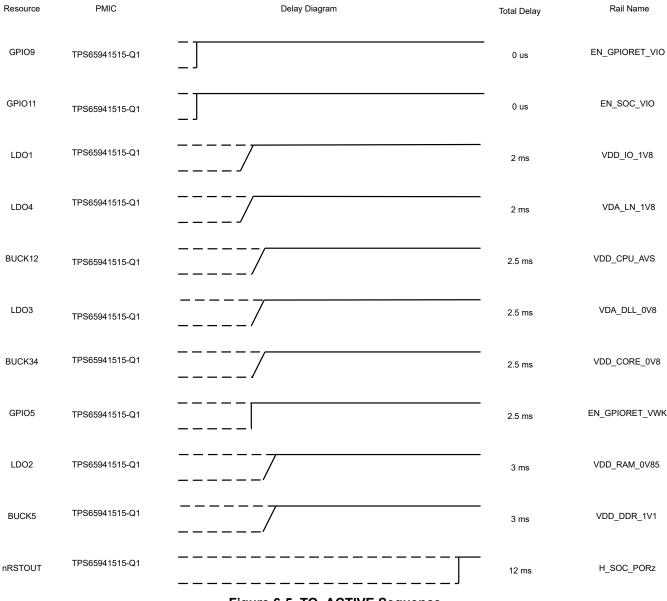

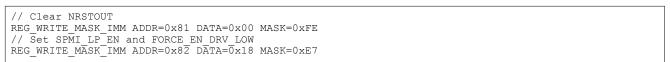

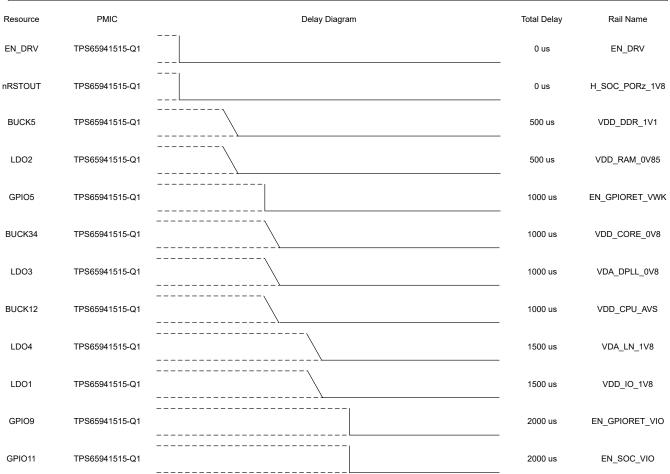

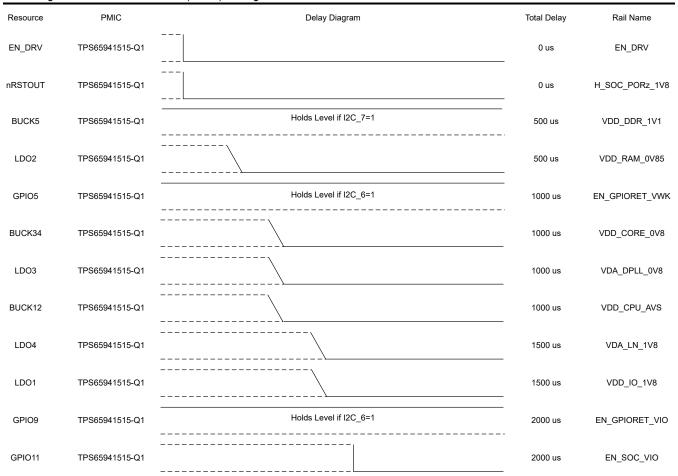

| 6.1 Configured States                                   | 25 |

| 6.2 PFSM Triggers                                       | 27 |

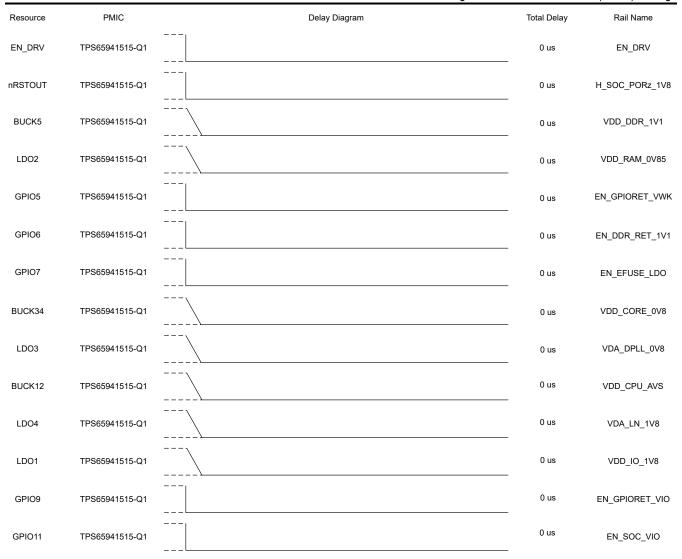

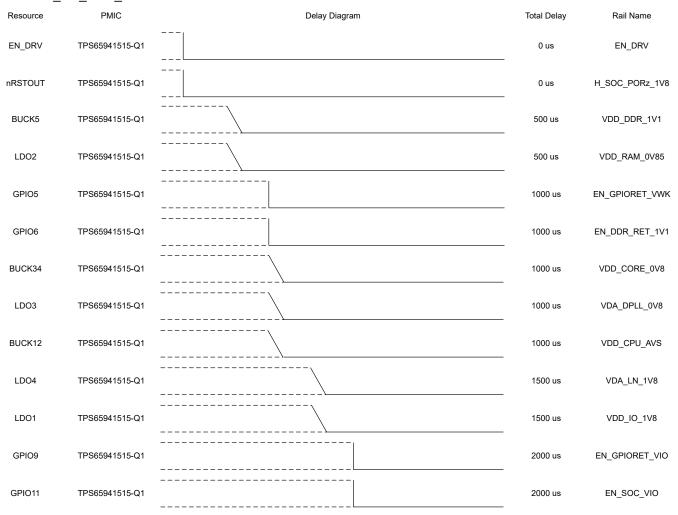

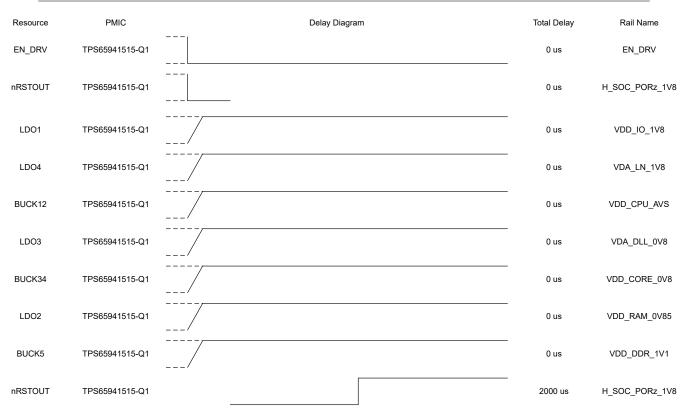

| 6.3 Power Sequences                                     | 28 |

| 7 Application Examples                                  |    |

| 7.1 Moving Between States: ACTIVE and RETENTION         |    |

| 7.2 Entering and Exiting Standby                        | 36 |

| 7.3 Entering and Existing LP_STANDBY                    |    |

| 7.4 GPIO8 and Watchdog                                  |    |

| 8 References                                            | 37 |

# **Trademarks**

Jacinto™ is a trademark of Texas Instruments.

All trademarks are the property of their respective owners.

Introduction Www.ti.com

#### 1 Introduction

This user's guide describes a power distribution network (PDN), PDN-2A, using a single TPS6594-Q1 PMIC and a few discrete components to power the DRA821 processor and peripherals.

#### Note

PDN-2A for DRA821 is recommended for solutions not requiring board level isolation of the MCU power for an additional lower power mode.

The following topics are described to clarify platform system operation:

- 1. PDN power resource connections

- 2. PDN digital control connections

- 3. Primary and secondary PMIC static NVM contents

- 4. PMIC sequencing settings to support different PDN power state transitions for an advanced processor system

PMIC and processor datasheets provide recommended operating conditions, electrical characteristics, recommended external components, package details, register maps, and overall component functionality. In the event of any inconsistency between any user's guide, application report, or other referenced material, the data sheet specification is the definitive source.

#### 2 Device Versions

There are different versions of the TPS6594-Q1 device available with unique NVM settings to support different processor solutions. The unique NVM settings for each PMIC device are optimized per PDN design to support different processors, processing loads, SDRAM types, system functional safety levels, and end product features (such as low power modes, processor voltages, and memory subsystems). The NVM settings can be identified by both the TI\_NVM\_ID and NVM\_REV registers.

Table 2-1. TPS6594-Q1 NVM Settings and Orderable Part Number

| PDN USE CASE                                              | Orderable Part Number | TI_NVM_ID | TI_NVM_REV |

|-----------------------------------------------------------|-----------------------|-----------|------------|

| Up to 5.95 A <sup>(1)</sup> on the CORE rail              | TPS65941515           | 0x15      | 0x03       |

| Up to 5.95 A <sup>(1)</sup> on the CPU rails              |                       |           |            |

| Up to 1.7 A <sup>(1)</sup> on the SDRAM, with support for |                       |           |            |

| LPDDR4                                                    |                       |           |            |

| Supports Functional Safety up to ASIL-D level             |                       |           |            |

| Supports low power modes including GPIO                   |                       |           |            |

| Retention, and DDR Retention states                       |                       |           |            |

| Supports I/O level of 3.3 V or 1.8 V                      |                       |           |            |

| Supports use of SD card                                   |                       |           |            |

|                                                           |                       |           |            |

<sup>(1)</sup> TI recommends having 15% margin between the maximum expected load current and the maximum current allowed per each PMIC output rail.

www.ti.com Processor Connections

#### **3 Processor Connections**

This section details how the TPS65941515-Q1 power resources and GPIO signals are connected to the processor and other peripheral components.

#### 3.1 Power Mapping

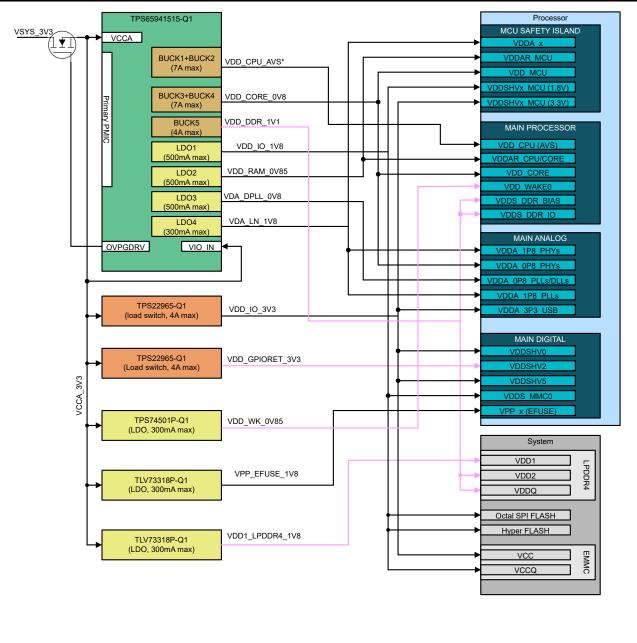

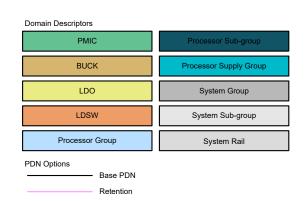

Figure 3-1 shows the power mapping between the TPS65941515-Q1 PMIC and peripheral regulators to power the processor and associated accessories. In this configuration, the PMIC and additional resources use a 3.3 V input voltage. For Functional Safety applications, there is a protection FET before VCCA that connects to the OVPGDRV pin of the PMIC, allowing voltage monitoring of the input supply to the system.

This PDN uses five discrete power components with four being required and one is optional depending upon end product features. The two TPS22965-Q1 Load Switches connect VCCA\_3V3 power rail to supply 3.3 V to processor I/O domains. The third discrete device is a TPS274501-Q1 LDO is used to supply power in low-power retention mode. The fourth discrete device is a TLV73318-Q1 LDO which supplies the LPDDR4 SDRAM component with required 1.8V supply. The last discrete power component is an optional TLV73318-Q1 LDO that can be used if an end product uses a high security processor type and desires the capability to program EFUSE values on-board. If this feature is not desired, then this LDO can be omitted and processor pins terminated per data manual recommendations.

Processor Connections

INSTRUMENTS

www.ti.com

Figure 3-1. Power Connections

- \* VDD\_CPU\_AVS, boot voltage of 0.8 V then software sets device specific AVS

- \*\* VPP\_EFUSE\_1V8, is optional

ww.ti.com Processor Connections

Table 3-1 identifies which power resources are required to support different system features. In the Active SoC column, there is an additional option for including or excluding the VPP\_x(EFUSE) rail.

**Table 3-1. PDN Power Mapping and System Features**

|                    |                   | Power Map           | pping                                    | System Features <sup>(1)</sup> |                   |                  |         |                  |

|--------------------|-------------------|---------------------|------------------------------------------|--------------------------------|-------------------|------------------|---------|------------------|

| Device             | Power<br>Resource | Power<br>Rails      | Processor and Memory<br>Domains          | Active<br>SoC                  | GPIO<br>Retention | DDR<br>Retention | SD Card | USB<br>Interface |

|                    | BUCK12            | VDD_CPU<br>_AVS     | VDD_CPU                                  | R                              |                   |                  |         |                  |

|                    | BUCK34            | VDD_COR<br>E_0V8    | VDD_MCU,<br>VDDA_SERDES                  | R                              |                   |                  |         |                  |

|                    | BUCK5             | VDD_DDR             | VDDS_DDR                                 | R                              |                   | R                |         |                  |

|                    |                   | _1V1                | Mem: LPDDR4_VDD2 and VDDQ                |                                |                   |                  |         |                  |

| TPS659415<br>15-Q1 | LDO1              | VDD_IO_1<br>V8      | VDDS_MMC0,<br>VDDSHVx_MCU(1.8V)          | R                              |                   |                  |         |                  |

|                    |                   |                     | Mem: VCC                                 |                                |                   |                  |         |                  |

|                    | LDO2              | VDD_RAM<br>_0V85    | VDDAR_MCU, VDDAR_CPU/<br>CORE            | R                              |                   |                  |         |                  |

|                    | LDO3              | VDA_DPLL<br>_0V8    | VDDA_0P8_PLLs/DLLs                       | R                              |                   |                  |         |                  |

|                    | LDO4              | VDA_LN_1<br>V8      | VDDA_x(1.8V)                             | R                              |                   |                  |         |                  |

| TPS22965-<br>Q1    | Load<br>Switch-A  | VDD_IO_3<br>V3      | VDDSHVx_MCU (3.3 V),<br>VDDSHV0, VDDSHV5 | R                              |                   |                  | R       | R                |

|                    |                   |                     | Mem: EMMC VCC                            |                                |                   |                  |         |                  |

| TPS22965-<br>Q1    | Load<br>Switch-B  | VDD_GPIO<br>RET_3V3 | VDDSHV0-4,VDDSHV6 (3.3 V)                | R                              | R                 |                  |         |                  |

| TPS74501<br>P-Q1   | LDO-A             | VDD_WK_<br>0V8      | VDDSHV2                                  | R                              | R                 |                  |         |                  |

| TLV73318P<br>-Q1   | LDO-B             | VDD1_LPD<br>DR4_1V8 | Mem: LPDDR4_VDD1                         | R                              |                   |                  |         |                  |

| TLV73318P<br>-Q1   | LDO-C             | VPP_EFUS<br>E_1V8   | VPP_x(EFUSE)                             | 0                              |                   |                  |         |                  |

<sup>(1) &#</sup>x27;R' is required and 'O' is optional.

**Processor Connections** www.ti.com

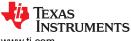

#### 3.2 Control Mapping

Figure 3-2 shows the digital control signal mapping between processor, PMIC, and discrete power devices. Connections from the TPS65941515 PMIC to the processor provide error monitoring, processor reset, processor wake up, and system low-power modes. Specific GPIO pins have been assigned to key signals in order to ensure proper operation during low power modes when only a few GPIO pins remain operational.

The digital connections shown in Figure 3-2 allow system features including GPIO and DDR Retention modes, functional safety up to ASIL-D, and compliant dual voltage SD card operation.

ww.ti.com Processor Connections

Figure 3-2. TPS65941515-Q1 Digital Connections

1. PMIC IO can have distinct power domains for input and output functionality. The SDA function for I2C1 and I2C2 use the VINT voltage domain as an input and the VIO voltage domain as an output. Please refer to the

Processor Connections

device data sheet for a complete description. The PMIC voltage domains indicated are for the TPS65941515

2. PMIC Wake1 is typically a CAN PHY INH output.

NVM configuration.

3. The EFUSE LDO is an optional feature and must be enabled by another signal in the system

#### Note

In addition to the I<sup>2</sup>C signals, three additional signals are open-drain outputs and require a pullup to a specific power rail. Please refer to Table 3-2 for a list of the signals and the specific power rail.

Table 3-2. Open-drain signals and Power Rail

| •                  | <u> </u>          |

|--------------------|-------------------|

| PDN Signal         | Pullup Power Rail |

| H_MCU_INTn_3V3     | VDD_IO_3V3        |

| H_SOC_PORz_1V8     | VDA_LN_1V8        |

| EN_DDR_RET_1V1     | VDD_DDR_1V1_REG   |

| H_WKUP_I2C0        | VDD_IO_3V3        |

| H_MCU_I2C0_SCL/SDA | VDD_IO_3V3        |

Please use Table 3-3 as a guide to understand GPIO assignments required for each PDN system feature. If the feature listed is not required, the digital connection can be removed; however, the GPIO pin is still configured per NVM defined default function shown. After the processor has booted up, the processor can reconfigure unused GPIOs to support new functions. Reconfiguring unused GPIOs is possible as long as that function is only needed after boot and default function does not cause any conflicts with normal operations (for example, two outputs driving same net). For details on how functional safety related connections help achieve functional safety system-level goals, see Section 4.

**Table 3-3. Digital Connections by System Feature**

|                    |                   |                  | Mapping           |            |                      | eatures <sup>(1)</sup> |                   |

|--------------------|-------------------|------------------|-------------------|------------|----------------------|------------------------|-------------------|

| Device             | PMIC Pin          | NVM<br>Function  | PDN Signals       | Active SoC | Functional<br>Safety | DDR<br>Retention       | GPIO<br>Retention |

|                    | nPWRON/<br>ENABLE | Enable           | SOC_PWR_ON        | R          |                      |                        |                   |

|                    | INT               | INT              | H_MCU_INTn        |            | R                    |                        |                   |

|                    | nRSTOUT           | nRSTOUT          | H_SOC_PORz_1V8    | R          |                      |                        |                   |

|                    | SCL_I2C1          | SCL_I2C1         | H_WKUP_I2C0       | R          |                      |                        |                   |

|                    | SDA_I2C1          | SDA_I2C1         | H_WKUP_I2C0       | R          |                      |                        |                   |

|                    | GPIO_1            | SCL_I2C2         | H_MCU_I2C0_SCL    |            | R                    |                        |                   |

|                    | GPIO_2            | SDA_I2C2         | H_MCU_I2C0_SDA    |            | R                    |                        |                   |

|                    | GPIO_3            | nERR_SoC         | H_SOC_SAFETY_ERRn |            | 0                    |                        |                   |

| TPS6594151<br>5-Q1 | GPIO_4            | LP_WKUP1         | PMIC_WAKE1        |            |                      | R                      | R                 |

|                    | GPIO_5            | GPO              | EN_GPIORET_VWK    | R          |                      |                        | R                 |

|                    | GPIO_6            | GPO              | EN_DDR_RET_1V1    |            |                      | R                      |                   |

|                    | GPIO_7            | nERR_MCU         | H_MCU_SAFETY_ERRn |            | R                    |                        |                   |

|                    | GPIO_8            | DISABLE_W<br>DOG | PMICA_GPIO8       | (3)        | (3)                  |                        |                   |

|                    | GPIO_9            | GPO              | EN_GPIORET_VIO    | R          |                      |                        | R                 |

|                    | GPIO_10           | CLK32OUT         | H_WKUP_LFOSCO_XI  | 0          |                      |                        |                   |

|                    | GPIO_11           | GPO              | EN_SOC_VIO        | R          |                      |                        | R                 |

<sup>(1)</sup> R is Required.

<sup>(2)</sup> LP\_WKUP1 function is masked in the static settings. Instructions for unmasking the function are provided in RETENTION, Entering and Exiting Standby and Entering and Existing LP STANDBY.

(3) If it is desired to disable the watchdog through hardware, GPIO\_8 is required and must be set high by the time nRSTOUT goes high. After nRSTOUT is high, the watchdog state is latched and the pin can be configured for other functions through software. If GPIO\_8 is not set high, then the processor must service the watch dog before the long window expires.

#### 4 Supporting Functional Safety Systems

By using the TPS65941515-Q1 solution to power the DRA821 processor, the system can leverage the following PMIC functional safety features:

- Input Supply Monitoring

- · Output Voltage and Current Monitoring

- · Question and Answer Watchdog

- Fault Reporting Interrupts

- · Enable Drive Pin that provides an independent path to disable system actuators

- Error Pin Monitoring

- · Internal Diagnostics including voltage monitoring, temperature monitoring, and Built-In Self-Test

Refer to the Safety Manual of the TPS6594-Q1 device for full descriptions and analysis of the PMIC functional safety features. These functional safety features can assist in achieving up to ASIL-D rating for a system. Additionally, these features help in achieving the functional safety assumptions utilized by the processor to achieve up to ASIL-D rating. See the DRA821 Safety Manual for Jacinto™ 7 Processors for a complete list of functional safety system assumptions.

#### 4.1 Achieving ASIL-B System Requirements

To achieve a system functional safety level of ASIL-B, the following PDN features are available:

- PMIC over voltage and under voltage monitoring on the power resource voltage outputs

- PMIC over-voltage monitoring and protection on the input to the PMIC (VCCA)

- · Watchdog monitoring of safety processor

- · MCU error monitoring

- MCU reset

- I<sup>2</sup>C communication

- · Error indicator for driving external circuitry (optional)

The PDN has an in-line, external power FET, as shown in Figure 3-1, between the input supply and PMICs. The voltage before and after the FET is monitored by the PMIC, and the PMIC controls the FET through the OVPGDRV pin. The FET can quickly isolate the PMIC when an over-voltage event greater than 6 V is detected on the input supply to protect the system from being damaged. Any power connected upstream from the FET is not protected from over voltage events. In Figure 3-1 the load switches that supply power to the MCU and Main I/O domains, the discrete buck supplying the DDR, and the discrete LDO supplying EFUSE are all connected after the FET to extend the over voltage protection to these processor domains and discrete power resources.

The PMIC internal over voltage and under voltage monitoring and their respective monitoring threshold levels are enabled by default and can be updated through I<sup>2</sup>C after startup. PMIC power rails connected directly to the processor are monitored by default.

The steps for configuring and starting the watchdog can be found in the TPS6594-Q1 data sheet. Setting the DISABLE\_WDOG signal high on GPIO\_8 disables the watchdog timer if this feature needs to be suspended during initial development or is not required in the system. An example of re-purposing GPIO\_8 is provided in Section 7.4.

GPIO\_7 is configured as the MCU error signal monitor, but must be enabled though the ESM\_MCU\_EN register bit. MCU reset is supported through the connection between the primary PMIC nRSTOUT pin and the MCU\_PORz of the processor. Lastly, there are two I<sup>2</sup>C ports between the TPS6594-Q1 and the processor. The first is used for all non-watchdog communication, such as voltage level control, and the second allows the watchdog monitoring to be on an independent communication channel.

There is an option to use the EN\_DRV pin to indicate an error has been detected and the system is entering SAFE state. This signal can be utilized if the system has external circuitry that needs to be driven by an error event. In this PDN, the EN\_DRV is not utilized, but available if needed.

#### 4.2 Achieving up to ASIL-D System Requirements

For ASIL-C or ASIL-D systems, the following features in addition to the ones described in Section 4.1 can be used:

- · PMIC current monitoring on all output power rails

- SoC error monitoring

- · Residual Voltage Monitoring

- · Read-back of Logic Output Pins

- nINT

- nRSTOUT

- EN\_DRV (when used)

The current monitoring is enabled by default for all BUCKs and LDOs for the PMIC. Additionally, Figure 3-1 shows that the MCU domain of the processor is powered by different power resources of the PMICs than the main power domain of the processor.

GPIO\_3 is configured as the SoC error signal monitor. Similar to the MCU error signal monitor, this feature is enabled through I<sup>2</sup>C using the ESM\_SOC\_EN register bit. For the TPS65941515, an SoC reset is not supported but an interrupt fires and the nINT pin driven low.

www.ti.com Static NVM Settings

Table 4-1. System Level Safety Features

| ASIL-B                   | ASIL-B   |                                                                              |                         |                                                                     |                                                         | ASIL-D                             |  |

|--------------------------|----------|------------------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------|---------------------------------------------------------|------------------------------------|--|

| External SW<br>Wdog      | INTn     | Safety MCU<br>Processing ESM<br>Safety MCU Reset                             | Safety Status<br>Signal | System Input<br>Voltage Monitoring                                  | SoC Main<br>Processing ESM                              | IO Read-Back<br>Feature            |  |

| Q&A Watchdog<br>and I2C2 | nINT Pin | nERR_MCU connected to SOC:MCU_SAFE TY_ERRz nRSTOUT connected to MCU_PORz_1V8 | ENDRV                   | VSYS_SENSE<br>-OV with Safety<br>FET OVPGDRV<br>VCCA OV & UV<br>and | nERR_SoC<br>connected to<br>SOC:<br>SOC_SAFETY_E<br>RRz | PMICA: nINT,<br>nRSTOUT,<br>EN_DRV |  |

**Table 4-2. Power Monitoring Safety Features**

|                | Tuble 4-2.1 Ower morntoring durity reactives |                     |                            |                              |                              |                                |  |

|----------------|----------------------------------------------|---------------------|----------------------------|------------------------------|------------------------------|--------------------------------|--|

|                |                                              |                     |                            | ASIL-B                       | ASIL-D Adds                  |                                |  |

| Device         | Power Resource                               | PDN Power Rail      | Safe State Power<br>Group1 | Supply Voltage<br>Monitoring | Supply Current<br>Monitoring | Residual Voltage<br>Monitoring |  |

| TPS65941515-Q1 | BUCK1-2                                      | VDD_CPU_AVS         | мси                        | OV & UV                      | YES                          | YES                            |  |

|                | BUCK3-4                                      | VDD_CORE_0V8        | MCU                        | OV & UV                      | YES                          | YES                            |  |

|                | BUCK5                                        | VDD_DDR_1V1         | мси                        | OV & UV                      | YES2                         | YES                            |  |

|                | LDO1                                         | VDD_IO_1V8          | мси                        | OV & UV                      | YES                          | YES                            |  |

|                | LDO2                                         | VDD_RAM_0V85        | MCU                        | OV & UV                      | YES                          | YES                            |  |

|                | LDO3                                         | VDA_DPLL_0v8        | мси                        | OV & UV                      | YES                          | YES                            |  |

|                | LDO4                                         | VDA_LN_1V8          | MCU                        | OV & UV                      | YES                          | YES                            |  |

| TPS22965W-Q1   | Ld Sw A                                      | VDD_IO_3V3          | None                       | NO                           | NO3                          |                                |  |

| TPS22965W-Q1   | Ld Sw B                                      | VDD_GPIORET_3<br>V3 | None                       | NO                           | NO4                          |                                |  |

| TLV73318P-Q1   | LDO-A                                        | VDD1_LPDDR4_1<br>V8 | None                       | NO<br>2                      | NO2                          |                                |  |

| TPS74501P-Q1   | LDO-B                                        | VDD_WK_0V8          | None                       | NO                           | NO                           |                                |  |

| TLV73318P-Q1   | LDO-C                                        | VPP_EFUSE_1V8       | None                       | NO5                          | NO5                          |                                |  |

- 1. Rail Group settings for the TPS65941515-Q1 are found in Table 5-7.

- Power rails VDD\_DDR\_1V1 and VDD1\_LPDDR4\_1V8 are safety critical but do not required direct voltage

or current monitoring since other means are available (for example, SoC internal timeout gaskets and ECC

checkers) provide diagnostic coverage to detect faults in the DDR voltage.

- Power rails VDD\_IO\_1V8/3V3 is typically not safety critical since other means are available (for example, black-channel checkers) to provide diagnostic coverage to detect faults in SoC signaling interfaces (for example, CAN, UART, and SPI).

- 4. If an SoC GPIO control signal is used in a *safety critical* interface, then adding voltage and current monitoring to specific VIO power rail may be needed per customer's end product design.

- 5. Power rail VPP\_EFUSE\_1V8 is *not safety critical* since Efuse programming does not occur during safety critical processing.

#### 5 Static NVM Settings

The TPS6594-Q1 devices consist of user register space and an NVM. The settings in NVM, which are loaded into the user registers during the transition from INIT to BOOT BIST, are provided in this section. Note: The user registers can be changed during state transitions, such as moving from STANDBY to ACTIVE mode. The user register map is described in the TPS6594-Q1 data sheet.

Static NVM Settings www.ti.com

#### 5.1 Application-Based Configuration Settings

In the TPS6594-Q1 data sheet, there are seven application-based configurations for each BUCK to operate within. The following list includes the different configurations available:

- 2.2 MHz Single Phase for DDR Termination

- 4.4 MHz VOUT Less than 1.9 V, Multiphase or High COUT Single Phase

- 4.4 MHz VOUT Less than 1.9 V, Low COUT, Single Phase Only

- 4.4 MHz VOUT Greater than 1.7 V, Single Phase Only

- 2.2 MHz VOUT Less than 1.9 V Multiphase or Single Phase

- 2.2 MHz Full VOUT Range and VIN Greater than 4.5 V, Single Phase Only

- · 2.2 MHz Full VOUT and Full VIN Range, Single Phase Only

The seven configurations also have optimal output inductance values that optimize the performance of each buck under these various conditions. Table 5-1 shows the default configurations for the BUCKs. These settings cannot be changed after device startup.

**Table 5-1. Application Use Case Settings**

| Device         | BUCK Rail | Default Application Use Case              | Recommended Inductor Value |

|----------------|-----------|-------------------------------------------|----------------------------|

|                | BUCK1     | 4.4 MHz VOUT Less than 1.9 V Single Phase | 220 nH                     |

|                | BUCK2     | 4.4 MHz VOUT Less than 1.9 V Single Phase | 220 nH                     |

| TPS65941515-Q1 | BUCK3     | 4.4 MHz VOUT Less than 1.9 V Single Phase | 220 nH                     |

|                | BUCK4     | 4.4 MHz VOUT Less than 1.9 V Single Phase | 220 nH                     |

|                | BUCK5     | 4.4 MHz VOUT Less than 1.9 V Single Phase | 220 nH                     |

www.ti.com Static NVM Settings

#### 5.2 Device Identification Settings

These settings are used to distinguish which device is detected in a system. These settings cannot be changed after device startup.

**Table 5-2. Device Identification NVM Settings**

| Register Name | Field Name | TPS65941515-Q1 |             |  |

|---------------|------------|----------------|-------------|--|

| Register Name | Field Name | Value          | Description |  |

| DEV_REV       | DEVICE_ID  | 0x82           |             |  |

| NVM_CODE_1    | TI_NVM_ID  | 0x15           |             |  |

| NVM_CODE_2    | TI_NVM_REV | 0x03           |             |  |

| PHASE_CONFIG  | MP_CONFIG  | 0x4            | 2+2+1       |  |

#### **5.3 BUCK Settings**

These settings describe the voltages, configurations, and monitoring of the BUCK rails stored in the NVM. All these settings can be changed though  $I^2C$  after startup. Some settings, typically the enable bits, are also changed by the PFSM, as described in Section 6.3.

After the Section 6.3.4 sequence has completed, the BUCKx\_EN and BUCKx\_VMON\_EN bits are set for BUCK1, BUCK3, and BUCK5. The BUCKx\_RV\_SEL bit is cleared for all BUCKs. The other bits remain unchanged, but are still accessible via I<sup>2</sup>C.

Table 5-3. BUCK NVM Settings

| Register Name | Field Name      | TPS659415 | TPS65941515-Q1                             |  |  |  |

|---------------|-----------------|-----------|--------------------------------------------|--|--|--|

|               | rieid Name      | Value     | Description                                |  |  |  |

| BUCK1_CTRL    | BUCK1_EN        | 0x0       | Disabled; BUCK1 regulator                  |  |  |  |

|               | BUCK1_FPWM      | 0x0       | PFM and PWM operation (AUTO mode).         |  |  |  |

|               | BUCK1_FPWM_MP   | 0x0       | Automatic phase adding and shedding.       |  |  |  |

|               | BUCK1_VMON_EN   | 0x0       | Disabled; OV, UV, SC and ILIM comparators. |  |  |  |

|               | BUCK1_VSEL      | 0x0       | BUCK1_VOUT_1                               |  |  |  |

|               | BUCK1_PLDN      | 0x1       | Enabled; Pull-down resistor                |  |  |  |

|               | BUCK1_RV_SEL    | 0x1       | Enabled                                    |  |  |  |

| BUCK1_CONF    | BUCK1_SLEW_RATE | 0x3       | 5.0 mV/µs                                  |  |  |  |

|               | BUCK1_ILIM      | 0x5       | 5.5 A                                      |  |  |  |

| BUCK2_CTRL    | BUCK2_EN        | 0x0       | Disabled; BUCK2 regulator                  |  |  |  |

|               | BUCK2_FPWM      | 0x0       | PFM and PWM operation (AUTO mode).         |  |  |  |

|               | BUCK2_VMON_EN   | 0x0       | Disabled; OV, UV, SC and ILIM comparators. |  |  |  |

|               | BUCK2_VSEL      | 0x0       | BUCK2_VOUT_1                               |  |  |  |

|               | BUCK2_PLDN      | 0x1       | Enabled; Pull-down resistor                |  |  |  |

|               | BUCK2_RV_SEL    | 0x1       | Enabled                                    |  |  |  |

| BUCK2_CONF    | BUCK2_SLEW_RATE | 0x3       | 5.0 mV/µs                                  |  |  |  |

|               | BUCK2_ILIM      | 0x5       | 5.5 A                                      |  |  |  |

| BUCK3_CTRL    | BUCK3_EN        | 0x0       | Disabled; BUCK3 regulator                  |  |  |  |

|               | BUCK3_FPWM      | 0x0       | PFM and PWM operation (AUTO mode).         |  |  |  |

|               | BUCK3_FPWM_MP   | 0x0       | Automatic phase adding and shedding.       |  |  |  |

|               | BUCK3_VMON_EN   | 0x0       | Disabled; OV, UV, SC and ILIM comparators. |  |  |  |

|               | BUCK3_VSEL      | 0x0       | BUCK3_VOUT_1                               |  |  |  |

|               | BUCK3_PLDN      | 0x1       | Enabled; Pull-down resistor                |  |  |  |

|               | BUCK3_RV_SEL    | 0x1       | Enabled                                    |  |  |  |

| BUCK3_CONF    | BUCK3_SLEW_RATE | 0x3       | 5.0 mV/µs                                  |  |  |  |

|               | BUCK3_ILIM      | 0x5       | 5.5 A                                      |  |  |  |

Static NVM Settings www.ti.com

#### **Table 5-3. BUCK NVM Settings (continued)**

|                 | Table 5-3. BUCK NV |       | TPS65941515-Q1                             |  |  |  |

|-----------------|--------------------|-------|--------------------------------------------|--|--|--|

| Register Name   | Field Name         | Value | Description                                |  |  |  |

| BUCK4_CTRL      | BUCK4_EN           | 0x0   | Disabled; BUCK4 regulator                  |  |  |  |

|                 | BUCK4_FPWM         | 0x0   | PFM and PWM operation (AUTO mode).         |  |  |  |

|                 | BUCK4_VMON_EN      | 0x0   | Disabled; OV, UV, SC and ILIM comparators. |  |  |  |

|                 | BUCK4_VSEL         | 0x0   | BUCK4_VOUT_1                               |  |  |  |

|                 | BUCK4_PLDN         | 0x1   | Enabled; Pull-down resistor                |  |  |  |

|                 | BUCK4_RV_SEL       | 0x1   | Enabled                                    |  |  |  |

| BUCK4_CONF      | BUCK4_SLEW_RATE    | 0x3   | 5.0 mV/µs                                  |  |  |  |

|                 | BUCK4_ILIM         | 0x5   | 5.5 A                                      |  |  |  |

| BUCK5_CTRL      | BUCK5_EN           | 0x0   | Disabled; BUCK5 regulator                  |  |  |  |

|                 | BUCK5_FPWM         | 0x0   | PFM and PWM operation (AUTO mode).         |  |  |  |

|                 | BUCK5_VMON_EN      | 0x0   | Disabled; OV, UV, SC and ILIM comparators. |  |  |  |

|                 | BUCK5_VSEL         | 0x0   | BUCK5_VOUT_1                               |  |  |  |

|                 | BUCK5_PLDN         | 0x1   | Enable Pull-down resistor                  |  |  |  |

|                 | BUCK5_RV_SEL       | 0x1   | Enabled                                    |  |  |  |

| BUCK5_CONF      | BUCK5_SLEW_RATE    | 0x3   | 5.0 mV/µs                                  |  |  |  |

|                 | BUCK5_ILIM         | 0x3   | 3.5 A                                      |  |  |  |

| BUCK1_VOUT_1    | BUCK1_VSET1        | 0x37  | 0.800 V                                    |  |  |  |

| BUCK1_VOUT_2    | BUCK1_VSET2        | 0x37  | 0.800 V                                    |  |  |  |

| BUCK2_VOUT_1    | BUCK2_VSET1        | 0x37  | 0.800 V                                    |  |  |  |

| BUCK2_VOUT_2    | BUCK2_VSET2        | 0x37  | 0.800 V                                    |  |  |  |

| BUCK3_VOUT_1    | BUCK3_VSET1        | 0x37  | 0.800 V                                    |  |  |  |

| BUCK3_VOUT_2    | BUCK3_VSET2        | 0x37  | 0.800 V                                    |  |  |  |

| BUCK4_VOUT_1    | BUCK4_VSET1        | 0x37  | 0.800 V                                    |  |  |  |

| BUCK4_VOUT_2    | BUCK4_VSET2        | 0x37  | 0.800 V                                    |  |  |  |

| BUCK5_VOUT_1    | BUCK5_VSET1        | 0x73  | 1.10 V                                     |  |  |  |

| BUCK5_VOUT_2    | BUCK5_VSET2        | 0x73  | 1.10 V                                     |  |  |  |

| BUCK1_PG_WINDOW | BUCK1_OV_THR       | 0x3   | +5% / +50 mV                               |  |  |  |

|                 | BUCK1_UV_THR       | 0x3   | -5% / -50 mV                               |  |  |  |

| BUCK2_PG_WINDOW | BUCK2_OV_THR       | 0x3   | +5% / +50 mV                               |  |  |  |

|                 | BUCK2_UV_THR       | 0x3   | -5% / -50 mV                               |  |  |  |

| BUCK3_PG_WINDOW | BUCK3_OV_THR       | 0x3   | +5% / +50 mV                               |  |  |  |

|                 | BUCK3_UV_THR       | 0x3   | -5% / -50 mV                               |  |  |  |

| BUCK4_PG_WINDOW | BUCK4_OV_THR       | 0x3   | +5% / +50 mV                               |  |  |  |

|                 | BUCK4_UV_THR       | 0x3   | -5% / -50 mV                               |  |  |  |

| BUCK5_PG_WINDOW | BUCK5_OV_THR       | 0x3   | +5% / +50 mV                               |  |  |  |

|                 | BUCK5_UV_THR       | 0x3   | -5% / -50 mV                               |  |  |  |

www.ti.com Static NVM Settings

# 5.4 LDO Settings

These settings detail the voltages, configurations, and monitoring of the LDO rails stored in the NVM. All these settings can be changed though  $I^2C$  after startup. Some settings, typically the enable bits, are also changed by the PFSM, as described in Section 6.3.

After the Section 6.3.4 sequence has completed, the LDOx\_EN and LDOx\_VMON\_EN bits are set and the LDOx\_RV\_SEL bit is cleared for all LDOs. The other bits remain unchanged, but are still accessible via I<sup>2</sup>C.

Table 5-4. LDO NVM Settings

| Table 5-4. LDO NVM Settings |                |          |                                                                            |  |  |

|-----------------------------|----------------|----------|----------------------------------------------------------------------------|--|--|

| Register Name               | Field Name     | TPS65941 | 515-Q1                                                                     |  |  |

| register Hame               | I loid Haille  | Value    | Description                                                                |  |  |

| LDO1_CTRL                   | LDO1_EN        | 0x0      | Disabled; LDO1 regulator.                                                  |  |  |

|                             | LDO1_SLOW_RAMP | 0x0      | 25mV/us max ramp up slew rate for LDO output from 0.3V to 90% of LDO1_VSET |  |  |

|                             | LDO1_PLDN      | 0x1      | 125 Ohm                                                                    |  |  |

|                             | LDO1_VMON_EN   | 0x0      | Disable OV and UV comparators.                                             |  |  |

|                             | LDO1_RV_SEL    | 0x1      | Enabled                                                                    |  |  |

| LDO2_CTRL                   | LDO2_EN        | 0x0      | Disabled; LDO2 regulator.                                                  |  |  |

|                             | LDO2_SLOW_RAMP | 0x0      | 25mV/us max ramp up slew rate for LDO output from 0.3V to 90% of LDO2_VSET |  |  |

|                             | LDO2_PLDN      | 0x1      | 125 Ohm                                                                    |  |  |

|                             | LDO2_VMON_EN   | 0x0      | Disabled; OV and UV comparators.                                           |  |  |

|                             | LDO2_RV_SEL    | 0x1      | Enabled                                                                    |  |  |

| LDO3_CTRL                   | LDO3_EN        | 0x0      | Disabled; LDO3 regulator.                                                  |  |  |

| _                           | LDO3_SLOW_RAMP | 0x0      | 25mV/us max ramp up slew rate for LDO output from 0.3V to 90% of LDO3_VSET |  |  |

|                             | LDO3_PLDN      | 0x1      | 125 Ohm                                                                    |  |  |

|                             | LDO3_VMON_EN   | 0x0      | Disabled; OV and UV comparators.                                           |  |  |

|                             | LDO3_RV_SEL    | 0x1      | Enabled                                                                    |  |  |

| LDO4_CTRL                   | LDO4_EN        | 0x0      | Disabled; LDO4 regulator.                                                  |  |  |

|                             | LDO4_SLOW_RAMP | 0x0      | 25mV/us max ramp up slew rate for LDO output from 0.3V to 90% of LDO4_VSET |  |  |

|                             | LDO4_PLDN      | 0x1      | 125 Ohm                                                                    |  |  |

|                             | LDO4_VMON_EN   | 0x0      | Disabled; OV and UV comparators.                                           |  |  |

|                             | LDO4_RV_SEL    | 0x1      | Enabled                                                                    |  |  |

| LDO1_VOUT                   | LDO1_VSET      | 0x1c     | 1.80 V                                                                     |  |  |

|                             | LDO1_BYPASS    | 0x0      | Linear regulator mode.                                                     |  |  |

| LDO2_VOUT                   | LDO2_VSET      | 0x9      | 0.85 V                                                                     |  |  |

|                             | LDO2_BYPASS    | 0x0      | Linear regulator mode.                                                     |  |  |

| LDO3_VOUT                   | LDO3_VSET      | 0x8      | 0.80 V                                                                     |  |  |

|                             | LDO3_BYPASS    | 0x0      | Linear regulator mode.                                                     |  |  |

| LDO4_VOUT                   | LDO4_VSET      | 0x38     | 1.800 V                                                                    |  |  |

| LDO1_PG_WINDOW              | LDO1_OV_THR    | 0x3      | +5% / +50 mV                                                               |  |  |

|                             | LDO1_UV_THR    | 0x3      | -5% / -50 mV                                                               |  |  |

| LDO2_PG_WINDOW              | LDO2_OV_THR    | 0x3      | +5% / +50 mV                                                               |  |  |

|                             | LDO2_UV_THR    | 0x3      | -5% / -50 mV                                                               |  |  |

| LDO3_PG_WINDOW              | LD03_OV_THR    | 0x3      | +5% / +50 mV                                                               |  |  |

|                             | LDO3_UV_THR    | 0x3      | -5% / -50 mV                                                               |  |  |

| LDO4_PG_WINDOW              | LDO4_OV_THR    | 0x3      | +5% / +50 mV                                                               |  |  |

|                             | LDO4_UV_THR    | 0x3      | -5% / -50 mV                                                               |  |  |

|                             |                |          |                                                                            |  |  |

Static NVM Settings www.ti.com

# 5.5 VCCA Settings

These settings detail the default monitoring enabled on VCCA. All these settings can be changed though I<sup>2</sup>C after startup.

**Table 5-5. VCCA NVM Settings**

| Donistay Name  | Field Name        | TPS659415 | TPS65941515-Q1                  |  |

|----------------|-------------------|-----------|---------------------------------|--|

| Register Name  | Field Name        | Value     | Description                     |  |

| VCCA_VMON_CTRL | VMON_DEGLITCH_SEL | 0x1       | 20 us                           |  |

|                | VCCA_VMON_EN      | 0x1       | Enabled; OV and UV comparators. |  |

| VCCA_PG_WINDOW | VCCA_OV_THR       | 0x7       | +10%                            |  |

|                | VCCA_UV_THR       | 0x7       | -10%                            |  |

|                | VCCA_PG_SET       | 0x0       | 3.3 V                           |  |

#### 5.6 GPIO Settings

These settings detail the default configurations of the GPIO rails. All these settings can be changed though I<sup>2</sup>C after startup. Note that the contents of the GPIOx SEL field determine which other fields in the GPIOx CONF and GPIO OUT x registers are applicable. To understand which NVM fields apply to each GPIOx SEL option, see the Digital Signal Descriptions section in TPS6594-Q1 data sheet.

Table 5-6. GPIO NVM Settings

| D. of the Name | Field News        | TPS65941515-Q1 |                                       |  |

|----------------|-------------------|----------------|---------------------------------------|--|

| Register Name  | Field Name        | Value          | Description                           |  |

| GPIO1_CONF     | GPIO1_OD          | 0x0            | Push-pull output                      |  |

|                | GPIO1_DIR         | 0x0            | Input                                 |  |

|                | GPIO1_SEL         | 0x1            | SCL_I2C2/CS_SPI                       |  |

|                | GPIO1_PU_SEL      | 0x0            | Pull-down resistor selected           |  |

|                | GPIO1_PU_PD_EN    | 0x0            | Disabled; Pull-up/pull-down resistor. |  |

|                | GPIO1_DEGLITCH_EN | 0x0            | No deglitch, only synchronization.    |  |

| GPIO2_CONF     | GPIO2_OD          | 0x0            | Push-pull output                      |  |

|                | GPIO2_DIR         | 0x0            | Input                                 |  |

|                | GPIO2_SEL         | 0x2            | SDA_I2C2/SDO_SPI                      |  |

|                | GPIO2_PU_SEL      | 0x0            | Pull-down resistor selected           |  |

|                | GPIO2_PU_PD_EN    | 0x0            | Disabled; Pull-up/pull-down resistor. |  |

|                | GPIO2_DEGLITCH_EN | 0x0            | No deglitch, only synchronization.    |  |

| GPIO3_CONF     | GPIO3_OD          | 0x0            | Push-pull output                      |  |

|                | GPIO3_DIR         | 0x0            | Input                                 |  |

|                | GPIO3_SEL         | 0x2            | NERR_SOC                              |  |

|                | GPIO3_PU_SEL      | 0x0            | Pull-down resistor selected           |  |

|                | GPIO3_PU_PD_EN    | 0x1            | Enabled; Pull-up/pull-down resistor.  |  |

|                | GPIO3_DEGLITCH_EN | 0x1            | 8 us deglitch time.                   |  |

| GPIO4_CONF     | GPIO4_OD          | 0x0            | Push-pull output                      |  |

|                | GPIO4_DIR         | 0x0            | Input                                 |  |

|                | GPIO4_SEL         | 0x6            | LP_WKUP1                              |  |

|                | GPIO4_PU_SEL      | 0x0            | Pull-down resistor selected           |  |

|                | GPIO4_PU_PD_EN    | 0x1            | Enabled; Pull-up/pull-down resistor.  |  |

|                | GPIO4_DEGLITCH_EN | 0x1            | 8 us deglitch time.                   |  |

www.ti.com Static NVM Settings

Table 5-6. GPIO NVM Settings (continued)

|               | Table 5-6. GPIO NVN |       | TPS65941515-Q1                        |  |  |

|---------------|---------------------|-------|---------------------------------------|--|--|

| Register Name | Field Name          | Value | Description                           |  |  |

| GPIO5 CONF    | GPIO5_OD            | 0x0   | Push-pull output                      |  |  |

|               | GPIO5_DIR           | 0x1   | Output                                |  |  |

|               | GPIO5_SEL           | 0x0   | GPIO5                                 |  |  |

|               | GPIO5_PU_SEL        | 0x0   | Pull-down resistor selected           |  |  |

|               | GPIO5_PU_PD_EN      | 0x0   | Disabled; Pull-up/pull-down resistor. |  |  |

|               | GPIO5_DEGLITCH_EN   | 0x0   | No deglitch, only synchronization.    |  |  |

| GPIO6_CONF    | GPIO6_OD            | 0x1   | Open-drain output                     |  |  |

|               | GPIO6_DIR           | 0x1   | Output                                |  |  |

|               | GPIO6_SEL           | 0x0   | GPIO6                                 |  |  |

|               | GPIO6_PU_SEL        | 0x0   | Pull-down resistor selected           |  |  |

|               | GPIO6_PU_PD_EN      | 0x0   | Disabled; Pull-up/pull-down resistor. |  |  |

|               | GPIO6_DEGLITCH_EN   | 0x0   | No deglitch, only synchronization.    |  |  |

| GPIO7_CONF    | GPIO7_OD            | 0x0   | Push-pull output                      |  |  |

|               | GPIO7_DIR           | 0x0   | Input                                 |  |  |

|               | GPIO7_SEL           | 0x1   | NERR_MCU                              |  |  |

|               | GPIO7_PU_SEL        | 0x0   | Pull-down resistor selected           |  |  |

|               | GPIO7_PU_PD_EN      | 0x1   | Enabled; Pull-up/pull-down resistor.  |  |  |

|               | GPIO7_DEGLITCH_EN   | 0x1   | 8 us deglitch time.                   |  |  |

| GPIO8_CONF    | GPIO8_OD            | 0x0   | Push-pull output                      |  |  |

|               | GPIO8_DIR           | 0x0   | Input                                 |  |  |

|               | GPIO8_SEL           | 0x3   | DISABLE_WDOG                          |  |  |

|               | GPIO8_PU_SEL        | 0x0   | Pull-down resistor selected           |  |  |

|               | GPIO8_PU_PD_EN      | 0x1   | Enabled; Pull-up/pull-down resistor.  |  |  |

|               | GPIO8_DEGLITCH_EN   | 0x1   | 8 us deglitch time.                   |  |  |

| GPIO9_CONF    | GPIO9_OD            | 0x0   | Push-pull output                      |  |  |

|               | GPIO9_DIR           | 0x1   | Output                                |  |  |

|               | GPIO9_SEL           | 0x0   | GPIO9                                 |  |  |

|               | GPIO9_PU_SEL        | 0x0   | Pull-down resistor selected           |  |  |

|               | GPIO9_PU_PD_EN      | 0x0   | Disabled; Pull-up/pull-down resistor. |  |  |

|               | GPIO9_DEGLITCH_EN   | 0x0   | No deglitch, only synchronization.    |  |  |

| GPIO10_CONF   | GPIO10_OD           | 0x0   | Push-pull output                      |  |  |

|               | GPIO10_DIR          | 0x0   | Input                                 |  |  |

|               | GPIO10_SEL          | 0x0   | GPIO10                                |  |  |

|               | GPIO10_PU_SEL       | 0x0   | Pull-down resistor selected           |  |  |

|               | GPIO10_PU_PD_EN     | 0x1   | Enabled; Pull-up/pull-down resistor.  |  |  |

|               | GPIO10_DEGLITCH_EN  | 0x0   | No deglitch, only synchronization.    |  |  |

| GPIO11_CONF   | GPIO11_OD           | 0x0   | Push-pull output                      |  |  |

|               | GPIO11_DIR          | 0x1   | Output                                |  |  |

|               | GPIO11_SEL          | 0x0   | GPIO11                                |  |  |

|               | GPIO11_PU_SEL       | 0x0   | Pull-down resistor selected           |  |  |

|               | GPIO11_PU_PD_EN     | 0x0   | Disabled; Pull-up/pull-down resistor. |  |  |

|               | GPIO11_DEGLITCH_EN  | 0x0   | No deglitch, only synchronization.    |  |  |

Static NVM Settings Www.ti.com

Table 5-6. GPIO NVM Settings (continued)

| Deviator Name | Field Name         | TPS659415 | TPS65941515-Q1                                                   |  |  |

|---------------|--------------------|-----------|------------------------------------------------------------------|--|--|

| Register Name | Field Name         | Value     | Description                                                      |  |  |

| NPWRON_CONF   | NPWRON_SEL         | 0x0       | ENABLE                                                           |  |  |

|               | ENABLE_PU_SEL      | 0x0       | Pull-down resistor selected                                      |  |  |

|               | ENABLE_PU_PD_EN    | 0x1       | Enabled; Pull-up/pull-down resistor.                             |  |  |

|               | ENABLE_DEGLITCH_EN | 0x1       | 8 us deglitch time when ENABLE, 50 ms deglitch time when NPWRON. |  |  |

|               | ENABLE_POL         | 0x0       | Active high                                                      |  |  |

|               | NRSTOUT_OD         | 0x0       | Push-pull output                                                 |  |  |

| GPIO_OUT_1    | GPIO1_OUT          | 0x0       | Low                                                              |  |  |

|               | GPIO2_OUT          | 0x0       | Low                                                              |  |  |

|               | GPIO3_OUT          | 0x0       | Low                                                              |  |  |

|               | GPIO4_OUT          | 0x0       | Low                                                              |  |  |

|               | GPIO5_OUT          | 0x0       | Low                                                              |  |  |

|               | GPIO6_OUT          | 0x0       | Low                                                              |  |  |

|               | GPIO7_OUT          | 0x0       | Low                                                              |  |  |

|               | GPIO8_OUT          | 0x0       | Low                                                              |  |  |

| GPIO_OUT_2    | GPIO9_OUT          | 0x0       | Low                                                              |  |  |

|               | GPIO10_OUT         | 0x0       | Low                                                              |  |  |

|               | GPIO11_OUT         | 0x0       | Low                                                              |  |  |

# 5.7 Finite State Machine (FSM) Settings

These settings describe how the PMIC output rails are assigned to various system-level states. Also, the default trigger for each system-level state is described. All these settings can be changed though I<sup>2</sup>C after startup.

**Table 5-7. FSM NVM Settings**

| Register Name  | Field Name        | TPS659415 | TPS65941515-Q1                                      |  |

|----------------|-------------------|-----------|-----------------------------------------------------|--|

| Register Name  | rieia Name        | Value     | Description                                         |  |

| RAIL_SEL_1     | BUCK1_GRP_SEL     | 0x1       | MCU rail group                                      |  |

|                | BUCK2_GRP_SEL     | 0x1       | MCU rail group                                      |  |

|                | BUCK3_GRP_SEL     | 0x1       | MCU rail group                                      |  |

|                | BUCK4_GRP_SEL     | 0x1       | MCU rail group                                      |  |

| RAIL_SEL_2     | BUCK5_GRP_SEL     | 0x1       | MCU rail group                                      |  |

|                | LDO1_GRP_SEL      | 0x1       | MCU rail group                                      |  |

|                | LDO2_GRP_SEL      | 0x1       | MCU rail group                                      |  |

|                | LDO3_GRP_SEL      | 0x1       | MCU rail group                                      |  |

| RAIL_SEL_3     | LDO4_GRP_SEL      | 0x1       | MCU rail group                                      |  |

|                | VCCA_GRP_SEL      | 0x1       | MCU rail group                                      |  |

| FSM_TRIG_SEL_1 | MCU_RAIL_TRIG     | 0x2       | MCU power error                                     |  |

|                | SOC_RAIL_TRIG     | 0x3       | SOC power error Not used in this NVM configuration. |  |

|                | OTHER_RAIL_TRIG   | 0x3       | SOC power error Not used in this NVM configuration. |  |

|                | SEVERE_ERR_TRIG   | 0x0       | Immediate shutdown                                  |  |

| FSM_TRIG_SEL_2 | MODERATE_ERR_TRIG | 0x1       | Orderly shutdown                                    |  |

www.ti.com Static NVM Settings

# 5.8 Interrupt Settings

These settings detail the default configurations for what is monitored by nINT pin. All these settings can be changed though  $I^2C$  after startup.

**Table 5-8. Interrupt NVM Settings**

| Davietes News   | Field Name          | TPS659415 | TPS65941515-Q1                        |  |  |

|-----------------|---------------------|-----------|---------------------------------------|--|--|

| Register Name   | Field Name          | Value     | Description                           |  |  |

| FSM_TRIG_MASK_1 | GPIO1_FSM_MASK      | 0x1       | Masked                                |  |  |

|                 | GPIO1_FSM_MASK_POL  | 0x0       | Low; Masking sets signal value to '0' |  |  |

|                 | GPIO2_FSM_MASK      | 0x1       | Masked                                |  |  |

|                 | GPIO2_FSM_MASK_POL  | 0x0       | Low; Masking sets signal value to '0' |  |  |

|                 | GPIO3_FSM_MASK      | 0x1       | Masked                                |  |  |

|                 | GPIO3_FSM_MASK_POL  | 0x0       | Low; Masking sets signal value to '0' |  |  |

|                 | GPIO4_FSM_MASK      | 0x1       | Masked                                |  |  |

|                 | GPIO4_FSM_MASK_POL  | 0x0       | Low; Masking sets signal value to '0' |  |  |

| FSM_TRIG_MASK_2 | GPIO5_FSM_MASK      | 0x1       | Masked                                |  |  |

|                 | GPIO5_FSM_MASK_POL  | 0x0       | Low; Masking sets signal value to '0' |  |  |

|                 | GPIO6_FSM_MASK      | 0x1       | Masked                                |  |  |

|                 | GPIO6_FSM_MASK_POL  | 0x0       | Low; Masking sets signal value to '0' |  |  |

|                 | GPIO7_FSM_MASK      | 0x1       | Masked                                |  |  |

|                 | GPIO7_FSM_MASK_POL  | 0x0       | Low; Masking sets signal value to '0' |  |  |

|                 | GPIO8_FSM_MASK      | 0x1       | Masked                                |  |  |

|                 | GPIO8_FSM_MASK_POL  | 0x0       | Low; Masking sets signal value to '0' |  |  |

| FSM_TRIG_MASK_3 | GPIO9_FSM_MASK      | 0x1       | Masked                                |  |  |

|                 | GPIO9_FSM_MASK_POL  | 0x0       | Low; Masking sets signal value to '0' |  |  |

|                 | GPIO10_FSM_MASK     | 0x1       | Masked                                |  |  |

|                 | GPIO10_FSM_MASK_POL | 0x0       | Low; Masking sets signal value to '0' |  |  |

|                 | GPIO11_FSM_MASK     | 0x1       | Masked                                |  |  |

|                 | GPIO11_FSM_MASK_POL | 0x0       | Low; Masking sets signal value to '0' |  |  |

| MASK_BUCK1_2    | BUCK1_ILIM_MASK     | 0x0       | Interrupt generated                   |  |  |

|                 | BUCK1_OV_MASK       | 0x0       | Interrupt generated                   |  |  |

|                 | BUCK1_UV_MASK       | 0x0       | Interrupt generated                   |  |  |

|                 | BUCK2_ILIM_MASK     | 0x0       | Interrupt generated                   |  |  |

|                 | BUCK2_OV_MASK       | 0x0       | Interrupt generated                   |  |  |

|                 | BUCK2_UV_MASK       | 0x0       | Interrupt generated                   |  |  |

| MASK_BUCK3_4    | BUCK3_ILIM_MASK     | 0x0       | Interrupt generated                   |  |  |

|                 | BUCK3_OV_MASK       | 0x0       | Interrupt generated                   |  |  |

|                 | BUCK3_UV_MASK       | 0x0       | Interrupt generated                   |  |  |

|                 | BUCK4_OV_MASK       | 0x0       | Interrupt generated                   |  |  |

|                 | BUCK4_UV_MASK       | 0x0       | Interrupt generated                   |  |  |

|                 | BUCK4_ILIM_MASK     | 0x0       | Interrupt generated                   |  |  |

| MASK_BUCK5      | BUCK5_ILIM_MASK     | 0x0       | Interrupt generated                   |  |  |

|                 | BUCK5_OV_MASK       | 0x0       | Interrupt generated                   |  |  |

|                 | BUCK5_UV_MASK       | 0x0       | Interrupt generated                   |  |  |

Static NVM Settings INSTRUMENTS

www.ti.com

|                   |                                  | M Settings (continued) TPS65941515-Q1 |                                                    |  |

|-------------------|----------------------------------|---------------------------------------|----------------------------------------------------|--|

| Register Name     | Field Name                       | Value                                 | Description                                        |  |

| MASK_LDO1_2       | LDO1_OV_MASK                     | 0x0                                   | Interrupt generated                                |  |

|                   | LDO1_UV_MASK                     | 0x0                                   | Interrupt generated                                |  |

|                   | LDO2_OV_MASK                     | 0x0                                   | Interrupt generated                                |  |

|                   | LDO2_UV_MASK                     | 0x0                                   | Interrupt generated                                |  |

|                   | LDO1_ILIM_MASK                   | 0x0                                   | Interrupt generated                                |  |

|                   | LDO2_ILIM_MASK                   | 0x0                                   | Interrupt generated                                |  |

| MASK_LDO3_4       | LDO3_OV_MASK                     | 0x0                                   | Interrupt generated                                |  |

|                   | LDO3_UV_MASK                     | 0x0                                   | Interrupt generated                                |  |

|                   | LDO4_OV_MASK                     | 0x0                                   | Interrupt generated                                |  |

|                   | LDO4_UV_MASK                     | 0x0                                   | Interrupt generated                                |  |

|                   | LDO3_ILIM_MASK                   | 0x0                                   | Interrupt generated                                |  |

|                   | LDO4_ILIM_MASK                   | 0x0                                   | Interrupt generated                                |  |

| MASK_VMON         | VCCA_OV_MASK                     | 0x1                                   | Interrupt not generated.                           |  |

|                   |                                  |                                       | Set to 0x0 after entering ACTIVE state.            |  |

|                   | VCCA UV MASK                     | 0x1                                   | Interrupt not generated.                           |  |

|                   |                                  | OXT                                   | Set to 0x0 after entering ACTIVE state.            |  |

| MASK CDIO1 8 EALI | CDIO1 FALL MASK                  | 0x1                                   |                                                    |  |

| ASK_GPIO1_8_FALL  | GPIO1_FALL_MASK                  | 0x1                                   | Interrupt not generated.                           |  |

|                   | GPIO2_FALL_MASK GPIO3_FALL_MASK  | 0x1                                   | Interrupt not generated.  Interrupt not generated. |  |

|                   |                                  |                                       |                                                    |  |

|                   | GPIO4_FALL_MASK GPIO5_FALL_MASK  | 0x1<br>0x1                            | Interrupt not generated.                           |  |

|                   |                                  |                                       | Interrupt not generated.                           |  |

|                   | GPIO6_FALL_MASK                  | 0x1                                   | Interrupt not generated.                           |  |

|                   | GPIO7_FALL_MASK                  | 0x1<br>0x1                            | Interrupt not generated.                           |  |

| MACK CDIO1 9 DICE | GPIO8_FALL_MASK                  |                                       | Interrupt not generated.                           |  |

| MASK_GPIO1_8_RISE | GPIO1_RISE_MASK                  | 0x1                                   | Interrupt not generated.                           |  |

|                   | GPIO2_RISE_MASK  GPIO3 RISE MASK | 0x1<br>0x1                            | Interrupt not generated.                           |  |

|                   |                                  |                                       | Interrupt not generated.                           |  |

|                   | GPIO4_RISE_MASK GPIO5_RISE_MASK  | 0x1<br>0x1                            | Interrupt not generated.  Interrupt not generated. |  |

|                   |                                  | 0x1                                   | Interrupt not generated.                           |  |

|                   | GPIO6_RISE_MASK                  | 0x1                                   | · · ·                                              |  |

|                   | GPIO7_RISE_MASK GPIO8_RISE_MASK  | 0x1                                   | Interrupt not generated.  Interrupt not generated. |  |

| MASK_GPIO9_11 /   | GPIO9 FALL MASK                  | 0x1                                   | Interrupt not generated.                           |  |

| MASK_GPIO9_10     | GPIO9_RISE_MASK                  | 0x1                                   | Interrupt not generated.                           |  |

|                   | GPIO10 FALL MASK                 | 0x1                                   | Interrupt not generated.                           |  |

|                   | GPIO11_FALL_MASK                 | 0x1                                   | Interrupt not generated.                           |  |

|                   | GPIO10_RISE_MASK                 | 0x1                                   | Interrupt not generated.                           |  |

|                   | GPIO11 RISE MASK                 | 0x1                                   | Interrupt not generated.                           |  |

| MASK_STARTUP      | NPWRON_START_MASK                | 0x1                                   | Interrupt not generated.                           |  |

|                   | ENABLE_MASK                      | 0x0                                   | Interrupt generated                                |  |

|                   | FSD MASK                         | 0x0<br>0x1                            | Interrupt not generated.                           |  |

|                   | SOFT_REBOOT_MASK                 | 0x1                                   | Interrupt not generated                            |  |

| MASK_MISC         | TWARN_MASK                       | 0x0                                   | Interrupt generated                                |  |

| W. COT WILDO      | BIST_PASS_MASK                   | 0x0<br>0x0                            | Interrupt generated                                |  |

|                   |                                  |                                       |                                                    |  |

|                   | EXT_CLK_MASK                     | 0x1                                   | Interrupt not generated.                           |  |

www.ti.com Static NVM Settings

Table 5-8. Interrupt NVM Settings (continued)

| Pagister Nama     | Field Name                    | TPS6594151 | TPS65941515-Q1           |  |  |

|-------------------|-------------------------------|------------|--------------------------|--|--|

| Register Name     | Field Name                    | Value      | Description              |  |  |

| MASK_MODERATE_ERR | BIST_FAIL_MASK                | 0x0        | Interrupt generated      |  |  |

|                   | REG_CRC_ERR_MASK              | 0x0        | Interrupt generated      |  |  |

|                   | SPMI_ERR_MASK                 | 0x1        | Interrupt not generated. |  |  |

|                   | NINT_READBACK_MASK            | 0x0        | Interrupt generated      |  |  |

|                   | NRSTOUT_READBACK_MASK         | 0x0        | Interrupt generated      |  |  |

|                   | NPWRON_LONG_MASK              | 0x1        | Interrupt not generated. |  |  |

| MASK_FSM_ERR      | IMM_SHUTDOWN_MASK             | 0x0        | Interrupt generated      |  |  |

|                   | MCU_PWR_ERR_MASK              | 0x0        | Interrupt generated      |  |  |

|                   | SOC_PWR_ERR_MASK              | 0x0        | Interrupt generated      |  |  |

|                   | ORD_SHUTDOWN_MASK             | 0x0        | Interrupt generated      |  |  |

| MASK_COMM_ERR     | COMM_FRM_ERR_MASK             | 0x0        | Interrupt generated      |  |  |

|                   | COMM_CRC_ERR_MASK             | 0x0        | Interrupt generated      |  |  |

|                   | COMM_ADR_ERR_MASK             | 0x0        | Interrupt generated      |  |  |

|                   | I2C2_CRC_ERR_MASK             | 0x0        | Interrupt generated      |  |  |

|                   | I2C2_ADR_ERR_MASK             | 0x0        | Interrupt generated      |  |  |

| MASK_READBACK_ERR | EN_DRV_READBACK_ MASK         | 0x0        | Interrupt generated      |  |  |

|                   | NRSTOUT_SOC_<br>READBACK_MASK | 0x0        | Interrupt generated      |  |  |

| MASK_ESM          | ESM_SOC_PIN_MASK              | 0x1        | Interrupt not generated. |  |  |

|                   | ESM_SOC_RST_MASK              | 0x1        | Interrupt not generated. |  |  |

|                   | ESM_SOC_FAIL_MASK             | 0x1        | Interrupt not generated. |  |  |

|                   | ESM_MCU_PIN_MASK              | 0x1        | Interrupt not generated. |  |  |

|                   | ESM_MCU_RST_MASK              | 0x1        | Interrupt not generated. |  |  |

|                   | ESM_MCU_FAIL_MASK             | 0x1        | Interrupt not generated. |  |  |

| GENERAL_REG_1     | PFSM_ERR_MASK                 | 0x0        | Interrupt generated      |  |  |

# **5.9 POWERGOOD Settings**

These settings detail the default configurations for what is monitored by PGOOD pin. All these settings can be changed though  $I^2C$  after startup.

**Table 5-9. POWERGOOD NVM Settings**

| Register Name | Field Name      | TPS659415 | TPS65941515-Q1 |  |

|---------------|-----------------|-----------|----------------|--|

| Register Name | rieiu Name      | Value     | Description    |  |

| PGOOD_SEL_1   | PGOOD_SEL_BUCK1 | 0x0       | Masked         |  |

|               | PGOOD_SEL_BUCK2 | 0x0       | Masked         |  |

|               | PGOOD_SEL_BUCK3 | 0x0       | Masked         |  |

|               | PGOOD_SEL_BUCK4 | 0x0       | Masked         |  |

| PGOOD_SEL_2   | PGOOD_SEL_BUCK5 | 0x0       | Masked         |  |

| PGOOD_SEL_3   | PGOOD_SEL_LDO1  | 0x0       | Masked         |  |

|               | PGOOD_SEL_LDO2  | 0x0       | Masked         |  |

|               | PGOOD_SEL_LDO3  | 0x0       | Masked         |  |

|               | PGOOD_SEL_LDO4  | 0x0       | Masked         |  |

Static NVM Settings www.ti.com

**Table 5-9. POWERGOOD NVM Settings (continued)**

| Desister Name | Field Name            | TPS65941515-Q1 |                                                      |  |

|---------------|-----------------------|----------------|------------------------------------------------------|--|

| Register Name |                       | Value          | Description                                          |  |

| PGOOD_SEL_4   | PGOOD_SEL_VCCA        | 0x0            | Masked                                               |  |

|               | PGOOD_SEL_TDIE_WARN   | 0x0            | Masked                                               |  |

|               | PGOOD_SEL_NRSTOUT     | 0x0            | Masked                                               |  |

|               | PGOOD_SEL_NRSTOUT_SOC | 0x0            | Masked                                               |  |

|               | PGOOD_POL             | 0x0            | PGOOD signal is high when monitored inputs are valid |  |

|               | PGOOD_WINDOW          | 0x1            | Both undervoltage and overvoltage are monitored      |  |

# 5.10 Miscellaneous Settings

These settings detail the default configurations of additional settings, such as spread spectrum, PFSM delays, and LDO timeout. All these settings can be changed though  $I^2C$  after startup.

Table 5-10. Miscellaneous NVM Settings

| De minten Nome        | Elald Name       | TPS659415 | TPS65941515-Q1                                                                        |  |  |

|-----------------------|------------------|-----------|---------------------------------------------------------------------------------------|--|--|

| Register Name         | Field Name       | Value     | Description                                                                           |  |  |

| PLL_CTRL              | EXT_CLK_FREQ     | 0x0       | 1.1 MHz                                                                               |  |  |

| CONFIG_1              | TWARN_LEVEL      | 0x0       | 130C                                                                                  |  |  |

|                       | I2C1_HS          | 0x0       | Standard, fast or fast+ by default, can be set to Hs-mode by Hs-mode controller code. |  |  |

|                       | 12C2_HS          | 0x0       | Standard, fast or fast+ by default, can be set to Hs-mode by Hs-mode controller code. |  |  |

|                       | EN_ILIM_FSM_CTRL | 0x0       | Buck/LDO regulator ILIM interrupts do not affect FSM triggers.                        |  |  |

|                       | NSLEEP1_MASK     | 0x0       | NSLEEP1(B) affects FSM state transitions.                                             |  |  |