# GC5316 Daughtercard GC Studio Reference User Guide

User's Guide

The GC5316 is a high density digital upconverter and downconverter. It is optimized for UMTS, TD-SCDMA and CDMA2000-1X standards. It provides 12 UMTS upconversion and 12 UMTS downconversion channels. Alternately, the chip can handle 24 CDMA upconversion and downconversion channels. The GC5316 daughtercard for the GC101 Motherboard provides a means for testing and evaluating this part, using the GC Studio program for device control.

# 1 GC5316 Daughtercard and GC101 EVM Setup

To operate the system, simply plug the GC5316 daughtercard into the DIMM socket on the GC101 motherboard, connect the parallel port interface cable to the GC101 and Host Computer (PC), and connect the power supply to the GC101.

Figure 1. GC101 EVM and GC5316 Daughtercard

#### 2 GC Studio and the GC5316/GC101 Evaluation Hardware

GC Studio includes a software "plug-in" to control the GC101 motherboard, GC5316 daughtercard and the GC5316 device. Input data from a text file on the host computer (PC) is loaded into the GC101 input memory and used to stimulate the GC5316 input ports. Output data from the GC5316 is captured in the GC101 capture memory and transferred to the host computer. GC Studio configures the GC5316 internal registers using the interactive GUI.

Several GC Studio projects for the GC5316 are included in the installation. These projects can be used as the starting point for creating new experiments as desired.

#### 2.1 GC Studio Installation

## 2.1.1 Required Elements

- GC101 evaluation motherboard, the external 5V power supply for the GC101 and a ECP parallel port enhanced speed cable.

- · GC Studio software, downloaded or provided on a CD

- GC5316 Rev A daughtercard

- Host Computer (PC) with BIOS supporting ECP mode for LPT1, running Win98 Rel 2, WinME, Win2000 SP1, WinXP Home or WinXP Professional.

- Administrator Group Privileges

#### 2.1.2 GC Studio Installation Instructions

Locate the "GC Studio\_Setup.exe" file on the CD or in the downloaded location on the host computer and double click on it to install.

# 2.2 GC Studio Projects

Several projects (sometimes referred to as experiments) are provided for the GC5316 in the GC Studio release. Users can execute these existing projects and create and save new projects using the GC Studio GUI interface.

## 2.2.1 Creating a New GC Studio Project for a CDMA Configuration

This project demonstrates the ability of the GC5316 to downconvert channels from a real, parallel input stream. The input spectrum shows the input image (which is a real signal, which explains the negative image in the spectrum).

The resampler is turned on, which downshifts the data by  $F_s/4$  (122.88/4 = 30.72). Therefore, Channel 0 A&B, which have their NCO's tuned to  $\pm$ .625 are filtering and isolating the signals centered at 30.72  $\pm$ .625MHz.

- A real CDMA carrier is applied to the GC5316 rxin\_a inputs with a simulated sample rate of 61.44 Msps and an IF frequency of 30.72MHz.

- Simulated rxclk to the gc5316 is 122.88MHz

- Receive FIFOs are enabled

- Receive Channel 0 is configured to process the signal

- The resampler is turned on, which downshifts the data by  $F_s/4$  (122.88/4 = 30.72).

- Channel 0 A&B, which have their NCO's tuned to  $\pm .625$  are filtering and isolating the signals centered at  $30.72 \pm .625 MHz$

- The CIC filter is programmed to decimate by 25 using a m=2 comb section configuration. The output sample rate at the CIC output is 4.9152 MSPS

- The CFIR filter compensates for the droop in the CIC filter, and provides some low pass filtering. It is configured as a 48 tap filter.

- The 64 tap PFIR provides final symbol shaping and filtering.

- · Channel AGC is configured as fixed unity gain

- Baseband data is transmitted and captured using the serial interface at the half rxclk rate.

- 1. Start GC Studio

- 2. Click on File > New Project to bring up the following window.

- 3. Choose a name for this new project, and click create.

- 4. Select GC5316 for the Plugin and click OK.

- 5. Using the wizard style interface, setup the GC101 evaluation board, then click next.

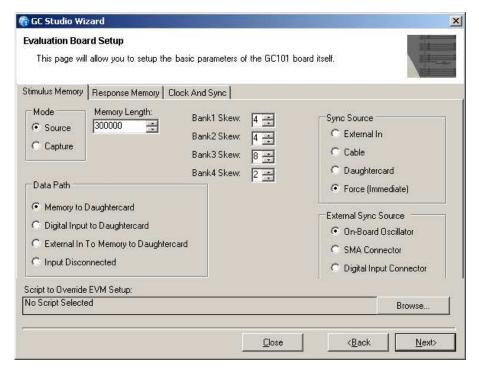

"Evaluation Board Setup" Menu allows the user to set up the data source (input and output), pattern length, capture length, and clock rates and sources. At this point, click the "NEXT" tab to proceed to the next screen:

Figure 2. CDMA - Evaluation Board Setup

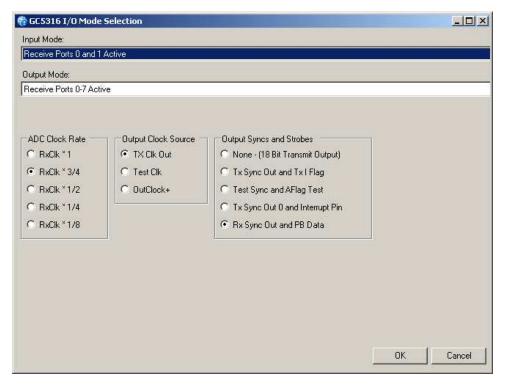

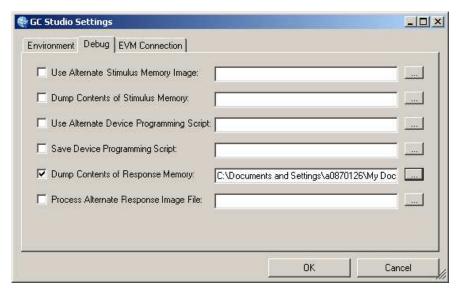

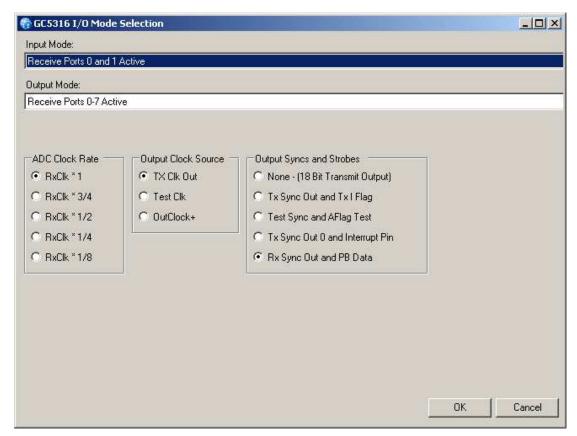

6. Setup the GC5316 I/O mode selection as shown and click next. In this example, be sure the ADC clock rate is set to 3/4. Because we are using a receive channel for this experiment, set the Input Mode and Output Mode boxes to Receive Ports as shown below. We will ignore the Output Clock Source and leave it also set to TX Clk Out. Ensure that the Output Syncs and Strobes are set to "Rx Sync Out and PB Data". Otherwise, the frame strobe for the receive output serial stream will not be output, and GC Studio will be incapable of deciphering the serial output data from the chip. Click "Next" to see the Simulated Clock Rates screen.

Figure 3. CDMA - I/O Mode Selection

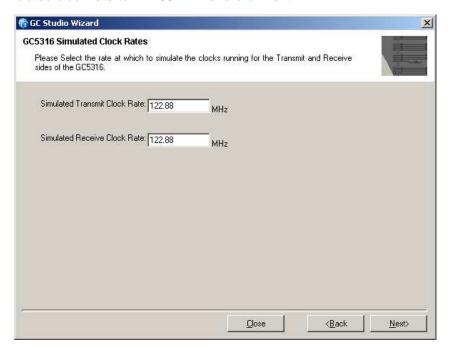

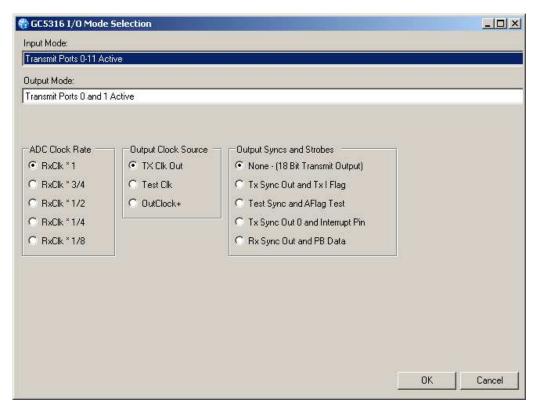

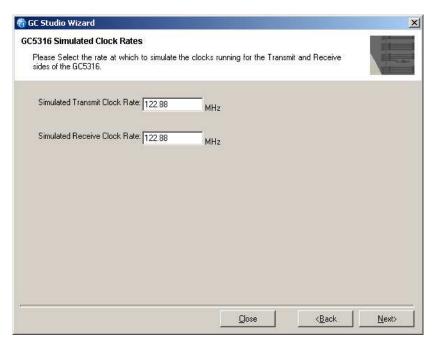

7. Set the simulated clock rate to 122.88 MHz and click next.

Figure 4. CDMA - Simulated Clock Rates

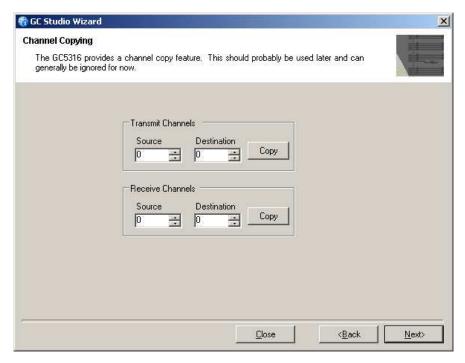

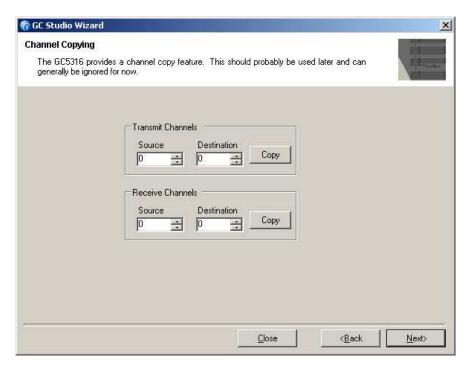

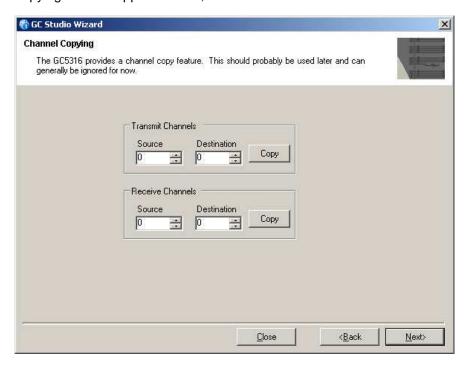

Figure 5. CDMA – Channel Copying

- 8. Channel Copying will be skipped for now, click Next.

- 9. Project description can be added to explain the details. Finish the set-up Wizard by clicking the "Finish" tab on the next screen.

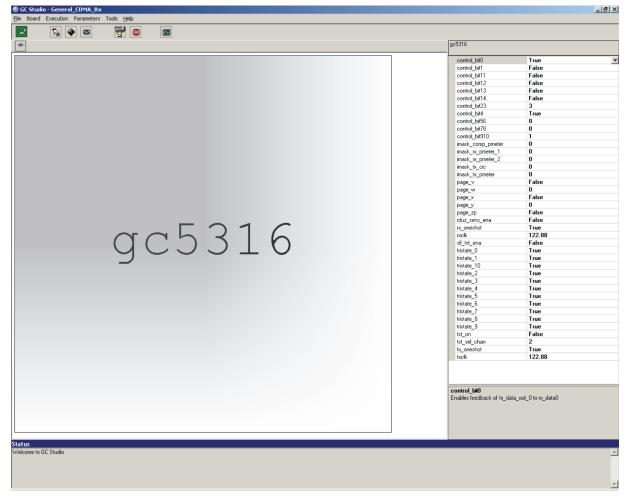

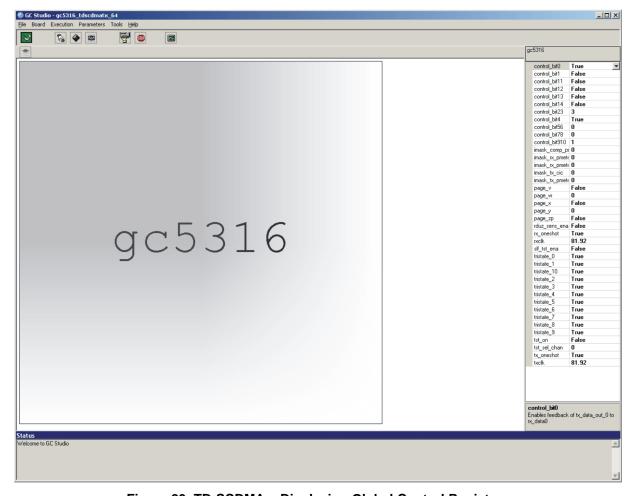

- 10. Click on the large gc5316 box to display the global control registers.

Figure 6. CDMA - Displaying Global Control Registers

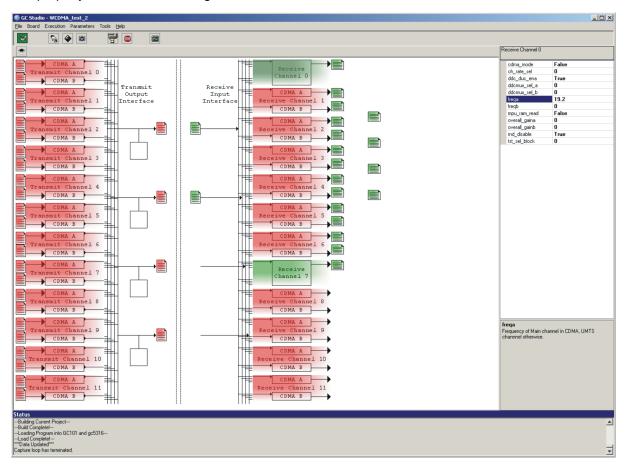

- 11. Next, double click on the gc5316 block to "push down" one level into the gc5316.

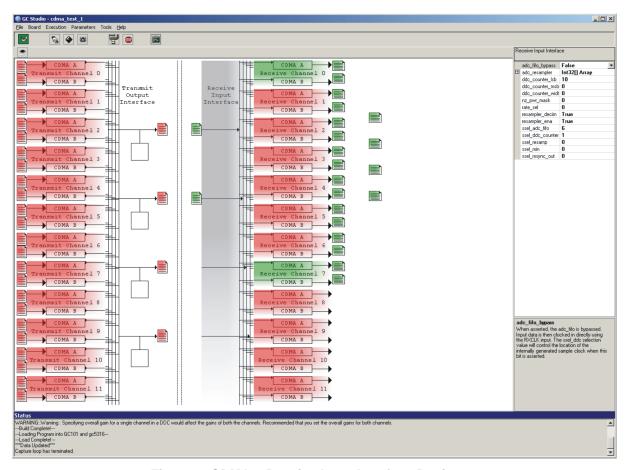

- 12. Click on the Receive Input Interface block to display and edit the receive input interface registers.

- 13. Make sure that the "adc\_fifo\_bypass" is set to FALSE to enable the rxin\_a/b/c/d input FIFO circuits.

Figure 7. CDMA – Receive Input Interface Registers

14. Next, since the ADC runs at 3/4 the GC5316 clock rate (92.16 MSPS), the resampler needs to be enabled and coefficients loaded. Enable the resampler and set its parameters by following the picture below:

Figure 8. CDMA - Receive Input Interface, adc-resampler

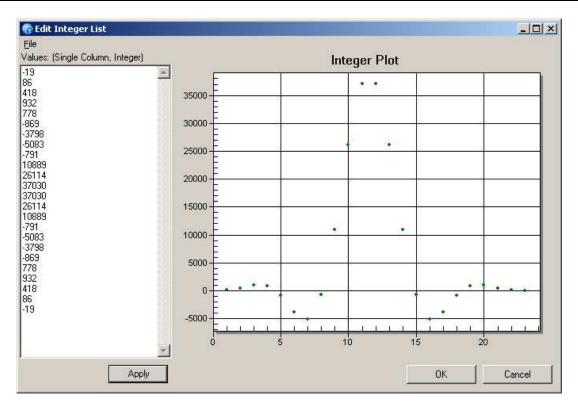

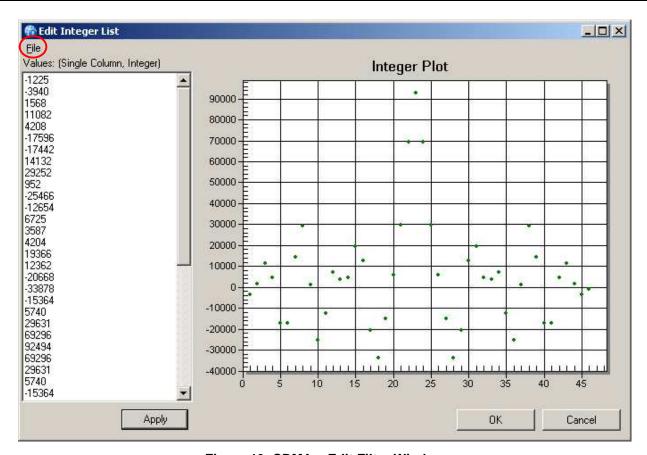

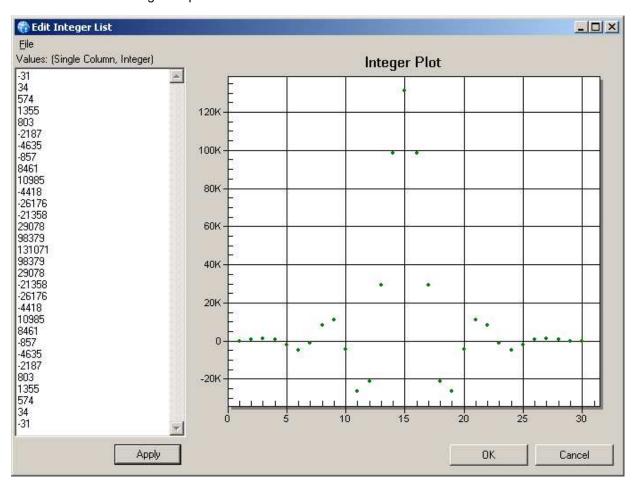

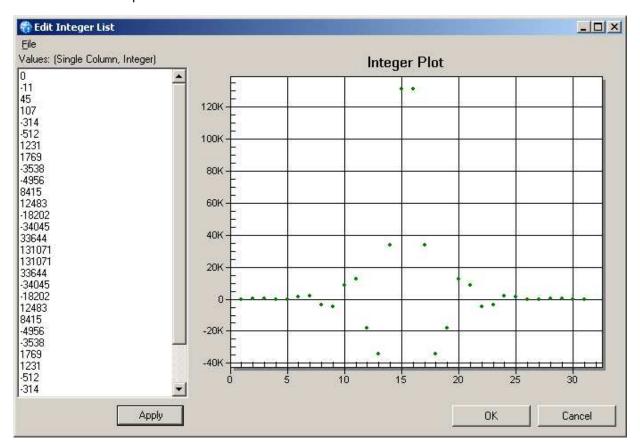

15. Click on the "adc\_resampler" Array (circled above) and load the following coefficients:

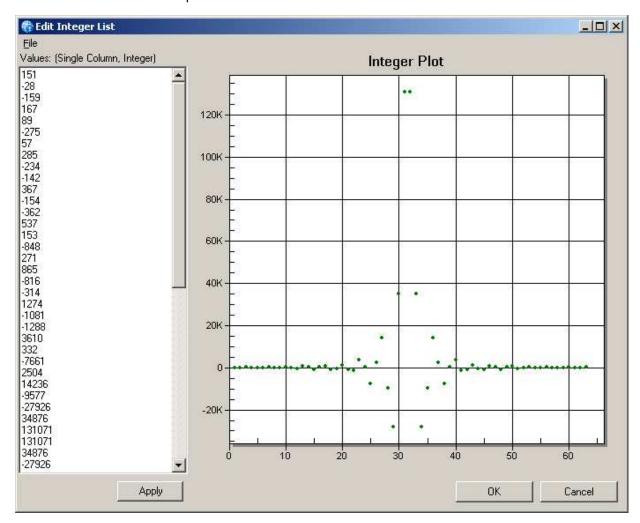

Figure 9. CDMA - Integer Plot

- 16. Click on "File", then "Load", then navigate on the provided CD for the Filter file named "cdma\_RS\_92p16to122p88.taps". This file contains the coefficients to be used by the resampler. Select this file. After the file is loaded, the Integer plot should look as shown above. Click on "OK".

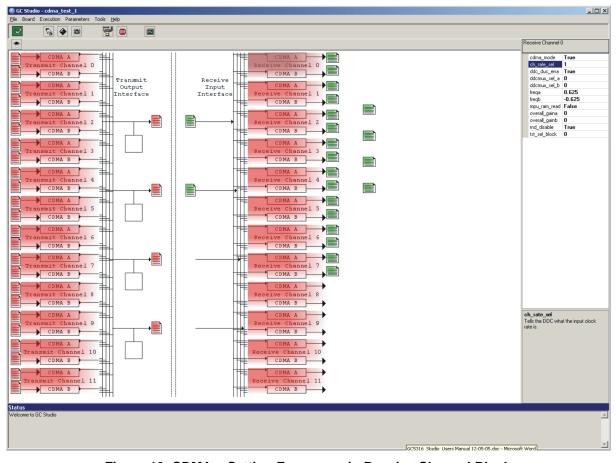

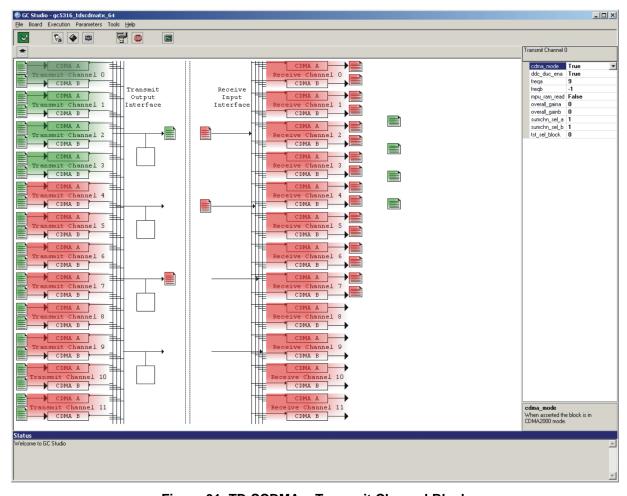

- 17. Click on the upper Receive Channel 1 0 block. Set ddc\_duc\_ena to True. Make sure that the cdma\_mode is set to True. The "ch\_rate\_sel" bit needs to be set to 1 to match the ADC rate.

- 18. Set the freqa to 0.625 (MHz) and freqb to -0.625 in order to tune to the positive and negative side of the real signal.

Figure 10. CDMA - Setting Frequency in Receive Channel Block

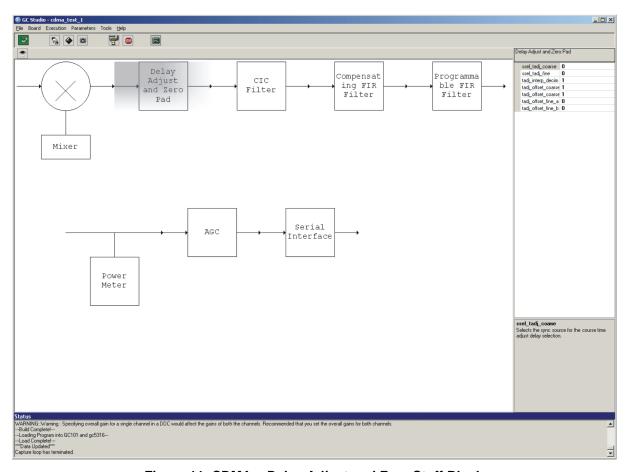

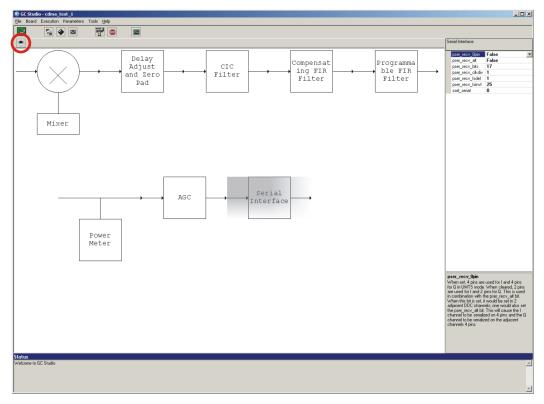

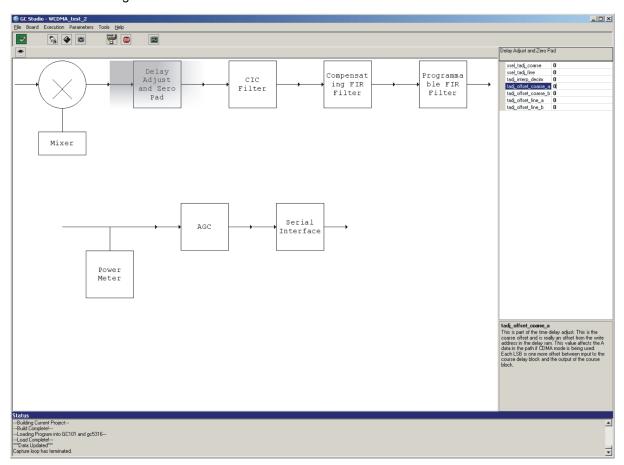

19. Double-click on the Receive Channel 0. Select the Delay Adjust and Zero Stuff block. Because the input sample rate is set to the rxclk rate, set the interpolation rate to 1. The tadj\_offset\_coarse and tadj\_offset\_fine settings allow the user to adjust the delay between various receive channels if desired. Set both tadj\_offset\_coarse\_a and tadj\_offset\_coarse\_b to 1.

Figure 11. CDMA - Delay Adjust and Zero Stuff Block

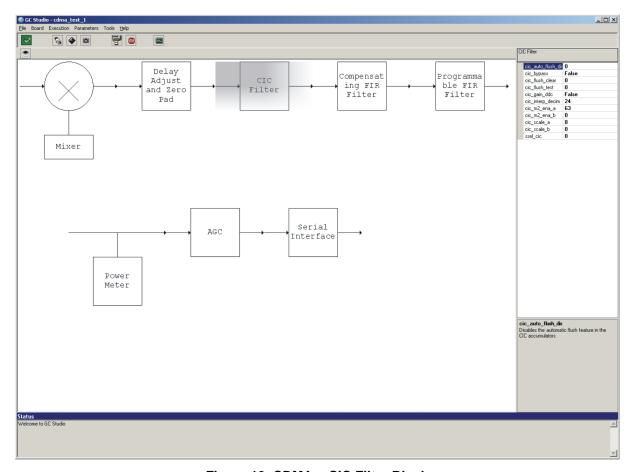

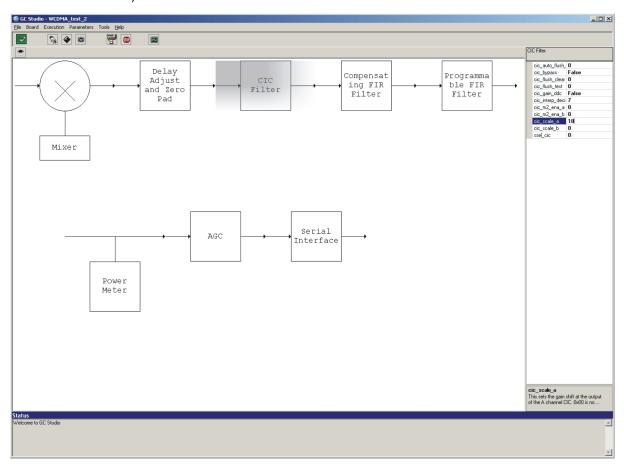

20. Click on the CIC filter block and set the registers as shown in the following panel. The decimation in the CIC is set to 25x, resulting in a 4.9152Msps CIC output rate (4x chip rate). For this example, all 6 CIC comb stages are set to m=2 (63 decimal = 111111 in binary).

Figure 12. CDMA - CIC Filter Block

- 21. Select the CFIR block and set the cfir\_gain to 0 (2.00E-18).

- 22. Next, select the cfir\_coeff register setting by clicking on it, and then click on the browse button, to open the Edit Filter window and fill in the CFIR filter tap weights.

Figure 13. CDMA - Edit Filter Window

- 23. To load the provided Filter coefficient file, click on the File tab (circled above) then click "Load", then navigate on the provided CD for the Filter file named "CDMA\_CFIR\_4x2x.taps". This file contains the coefficients to be used by the CIC filter. Select this file. After the file is loaded, the Integer plot should look as shown above. Click on "OK".

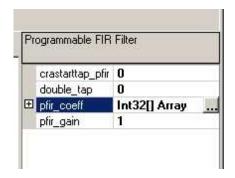

- 24. Select the PFIR block, set the pfir gain to 1 (2.00E-18).

- 25. Load the Filter coefficient file by clocking on the File tab (circled above) and by selecting the "CDMA\_PFIR\_2x2x.taps" file that can be found on the provided CD.

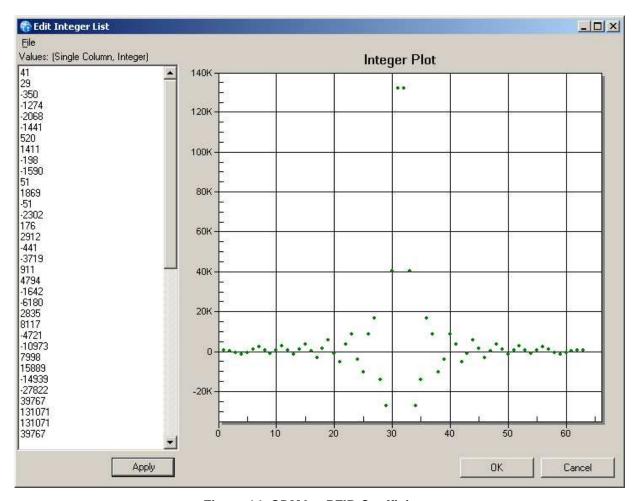

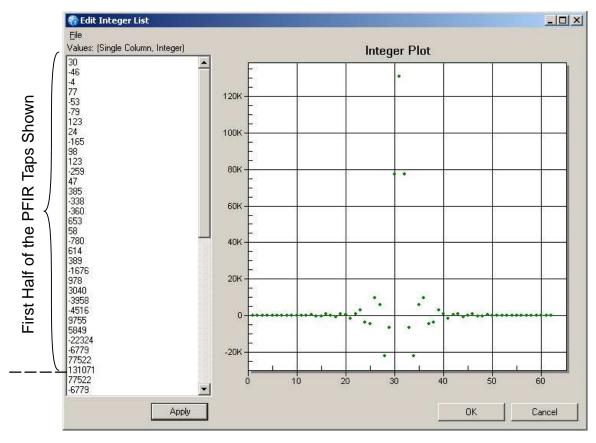

The following 64 taps are used for the PFIR coefficients (only half are shown in Figure 14).

Figure 14. CDMA - PFIR Coefficients

**Note:** Note that these coefficients are only for learning and test purposes and would not necessarily meet CDMA Receive Specifications.

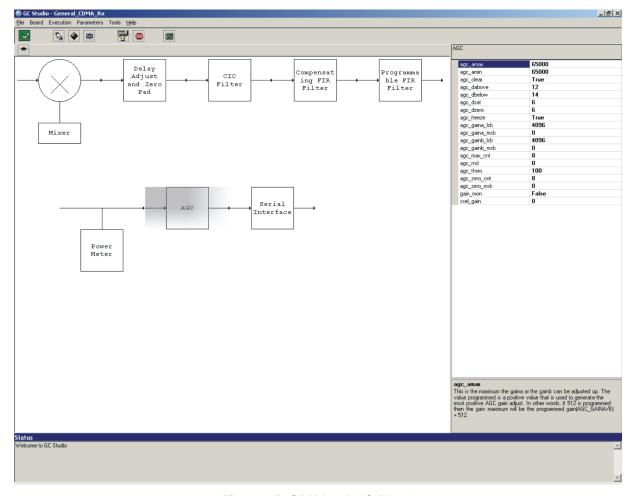

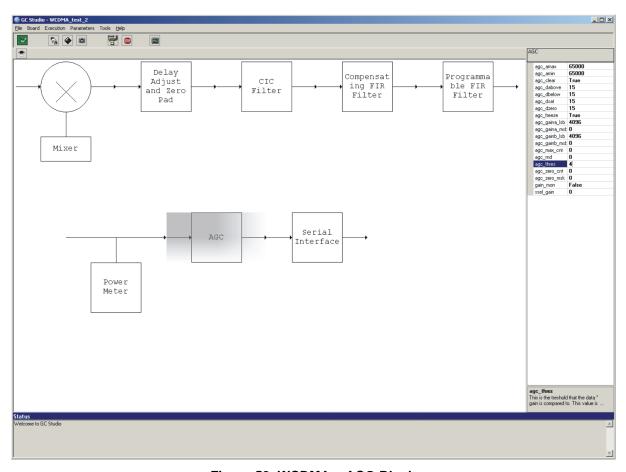

26. Click on "OK". Select the AGC block and set the registers as shown in Figure 15.

Figure 15. CDMA - AGC Block

The maximum and minimum gains are set to the same value, the agc\_freeze and agc\_clear are both set to True for this example. This puts the AGC in unity fixed gain mode. GC Studio will calculate the required values for the agc\_gaina\_msb and the agc\_gaina\_lsb registers after the experiment is executed.

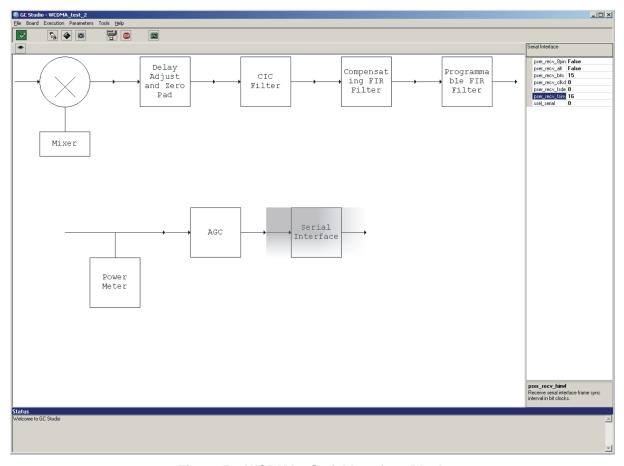

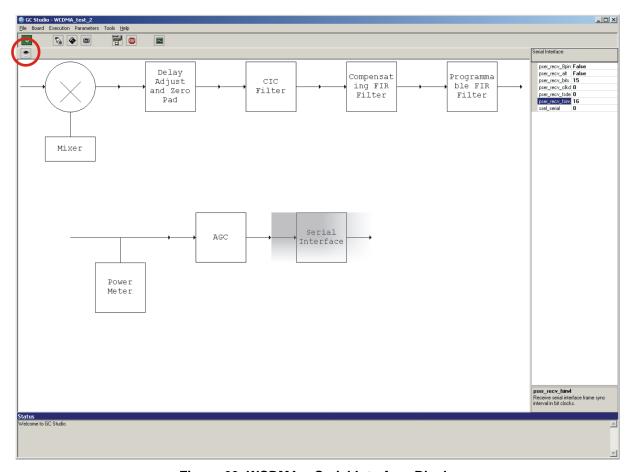

27. Select the Serial Interface block and set the parameters as indicated. Since the overall decimation is 50, and the maximum number of bits on the serial output is 18 (set value to 17), the output clock rate is set to the input clock divided by 2 (program a value of 1 in the register).

Figure 16. CDMA - Serial Interface Block

- 28. After verifying the values for the serial interface, click the arrow circled shown above to pop up one level in the GC5316 hierarchy.

- 29. Receive Channel 0 has now been configured to process:

- a CDMA signal at 122.88Msps with a 30.72MHz IF mixer/nco block shifts the signal to DC

- CIC block decimates by 25x to 4.9152Msps

- 48 tap CFIR compensates for the CIC droop, filters and decimates the signal to 2.4576 MSPS

- 64 tap PFIR filters the signal

- Channel AGC is set to a fixed gain of unit

- Serial interface is used to output the baseband signal at serial output clock of 61.44 MHz

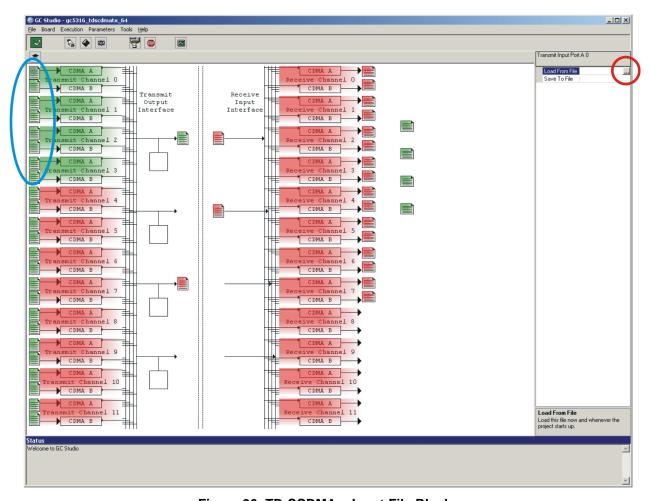

30. Input data presented to the GC5316 device comes from text format data files. Two input file icons can be seen in the block diagram to the left of the Input Interface block. Click on the top icon, shown in Figure 17.

Figure 17. CDMA - Input Interface Block

31. The upper file icon is connected to the rxin\_a input port, and the lower is connected to the rxin\_b input port. For this demonstration, load the file pattern from file "parallel\_in.gcin", located on the provided CD. Click "OK".

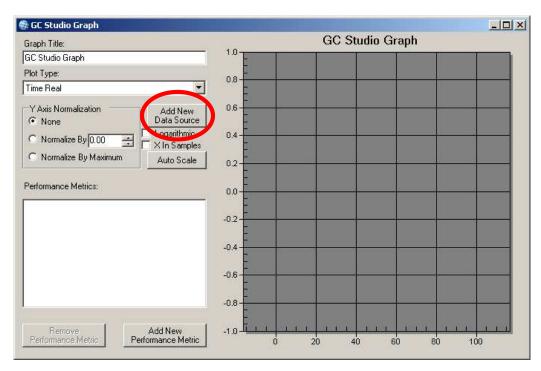

32. Next, click on the icon circled in Figure 18 for the graphical display settings.

Figure 18. Graphical Display Settings

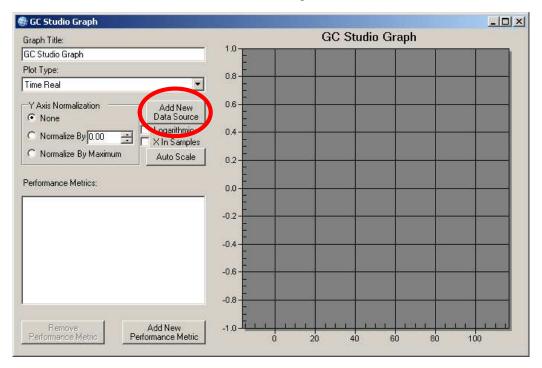

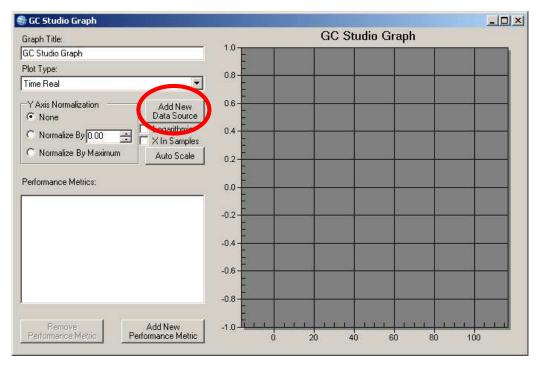

33. Click the Add New Data Source button circled in Figure 19.

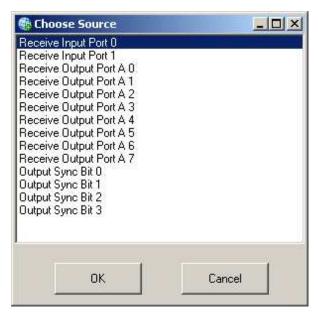

Figure 19. CDMA – Add New Data Source

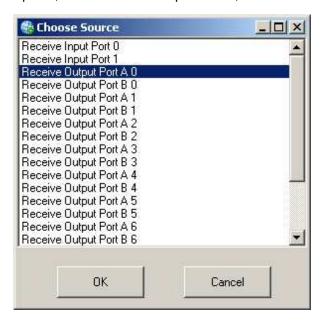

34. In the Choose Source panel, select Receive Output Port A, and click "OK".

Figure 20. CDMA - Choose Source Panel

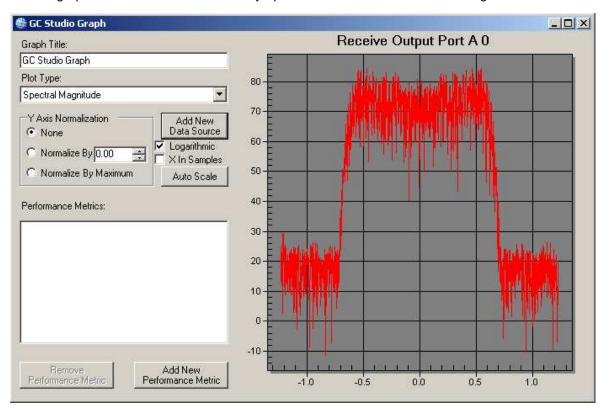

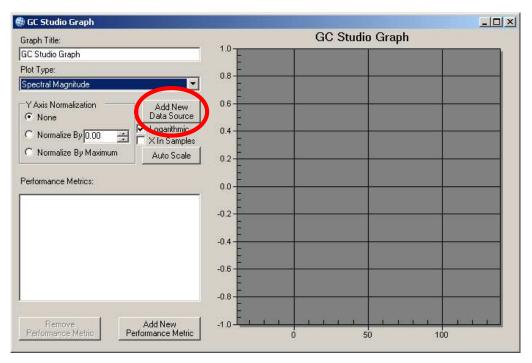

- 35. In the graph panel, set the Plot Type to Spectral Magnitude, and check Logarithmic.

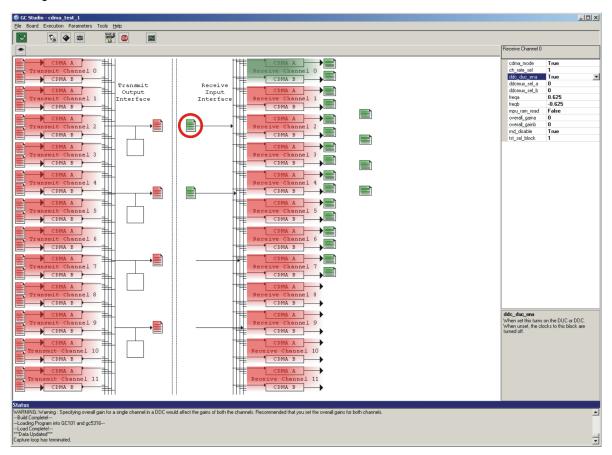

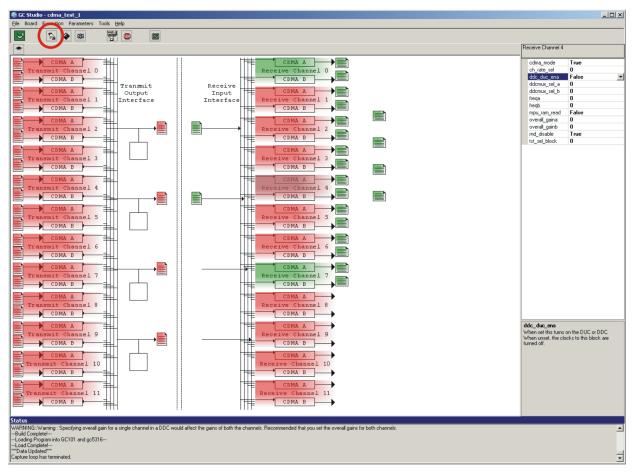

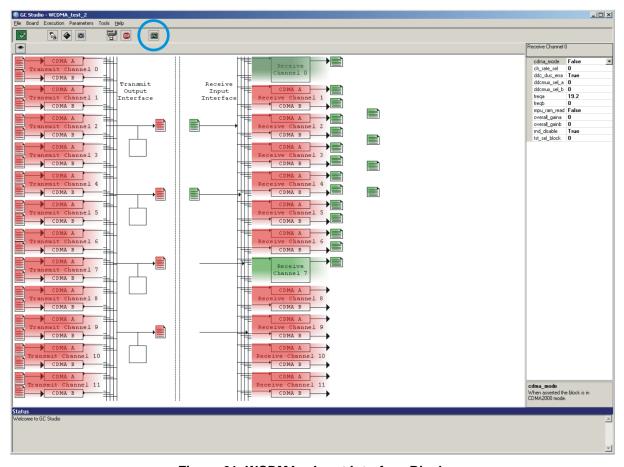

- 36. Next, copy the settings from Receive Channel 0 to Receive Channel 7, to match the delays for the capture, by going to Parameters, and selecting the channel copying option. Channel 7 should turn green as shown in Figure 21.

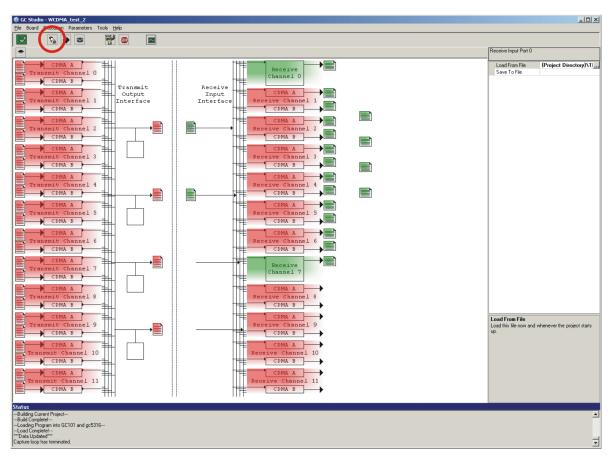

- 37. On the GC Studio panel, click the Build and Load buttons shown in Figure 21. This will execute the experiment.

Figure 21. CDMA - Build and Load Buttons

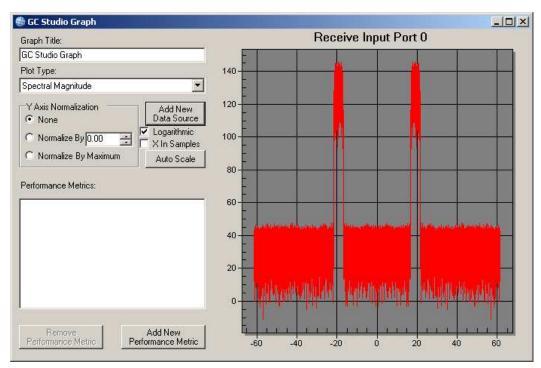

38. The graph window will be automatically updated with the results shown in Figure 22.

Figure 22. CDMA - Graph Window

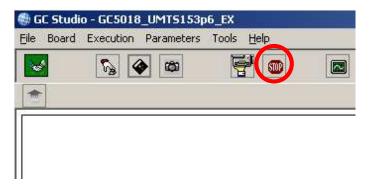

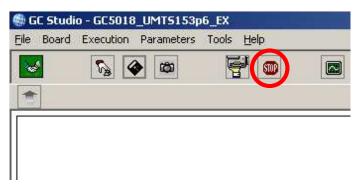

39. On the GC Studio panel, click on the stop button, shown circled in Figure 23, to stop the experiment, then select File -> Save Project to save this project.

Figure 23. CDMA - Stop Experiment and Save Project

- 40. Close the GC Studio Graph Window.

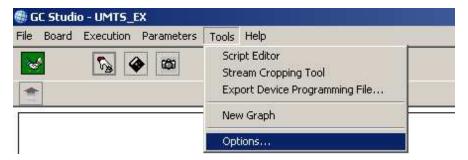

- 41. The raw response memory can be captured in a text format by selecting "Options..." in the Tools > window. Select the Debug tab, then select the "Dump Contents of Response Memory" option. Enter a file name for the data to be written to.

Figure 24. CDMA – Tools -> Options Window

Figure 25. CDMA – Capturing Raw Response Memory in Text Format

For this file to be generated, you must run the experiment after making this change.

The format of the file is hexadecimal, with the 32 bit response memory as the first 8 characters, a space, and then a single character for the other 4 special bits {sp7, sp6, sp5, syncout+} as shown below.

#### 2.2.2 Creating a New GC Studio Project for a TD-SCDMA Transmit Configuration

- Eight Real baseband TD-SCDMA signals are applied to the GC5316 inputs with an input rate of 1x (1.28 MSPS)

- Simulated txclk to the GC5316 is 81.92MHz (64x)

- The PFIR interpolates by two, and is configured for 63 taps

- The CFIR interpolates by two, and is configured for 31 taps

- The CIC filter is programmed to interpolate by 16, and uses 6. The output sample rate at the CIC output is 81.92 MSPS.

- The NCOs and Mixers are set to eight different IFs

- Eight outputs from four channels are MUXed on the output bus

- 1. Start GC Studio

- 2. Click on File > New Project to bring up the following window.

- 3. Choose a name for this new project, and click create.

- 4. Select GC5316 for the Plugin and click OK.

- 5. Using the wizard style interface, setup the GC101 evaluation board, then click next.

- 6. Setup the GC5316 I/O mode selection as shown and click next.

In this example, be sure the ADC clock rate is set to 1. Because we are using the transmit channels for this experiment, set the Input Mode and Output Mode boxes to Receive Ports as shown below. We will ignore the Output Clock Source and leave it also set to TX Clk Out. Click "Next" to see the Simulated Clock Rates screen.

Figure 26. TD-SCDMA - I/O Mode Selection

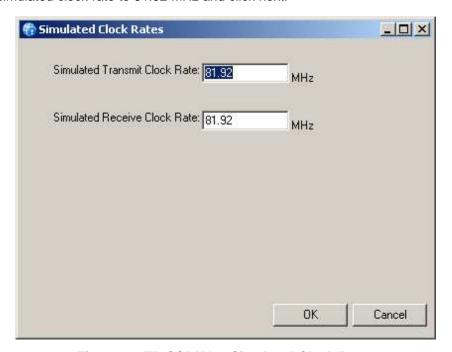

7. Set the simulated clock rate to 81.92 MHz and click next.

Figure 27. TD-SCDMA - Simulated Clock Rates

8. Channel Copying will be skipped for now, click Next.

Figure 28. TD-SCDMA - Channel Copying

- 9. Finish the set-up Wizard as explained in the previous example.

- 10. Click on the large gc5316 box to display the global control registers.

Figure 29. TD-SCDMA – Displaying Global Control Registers

- 11. Next, double click on the gc5316 block to "push down" one level into the gc5316.

- 12. Click on the Input File block (in blue), then load the file parameters by clicking to the field on the right (in red). Load the input files at zero IF.

Figure 30. TD-SCDMA – Input File Block

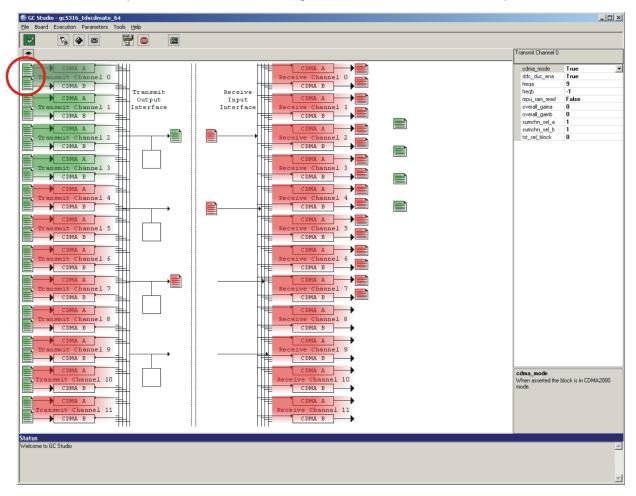

- 13. Click on the upper Transmit Channel 0 block. Set ddc\_duc\_ena to True. Make sure that the cdma\_mode is set to True.

- 14. Set the freqa to 9 (MHz) and freqb to -1. Since this example explains 8-channel output, NCO frequencies need to be set in channels 0-3. Also, since all eight channels will be summed on the same output, make sure that "sumchn\_sel\_a" and "sumchn\_sel\_b" of all four channels (0-3) is set to same output port, in this case to 1.

Figure 31. TD-SCDMA – Transmit Channel Block

15. Double-click on the Transmit Channel 0. The serial interface number of input bits should be set to 16 ("serp\_tran\_bits" = 15).

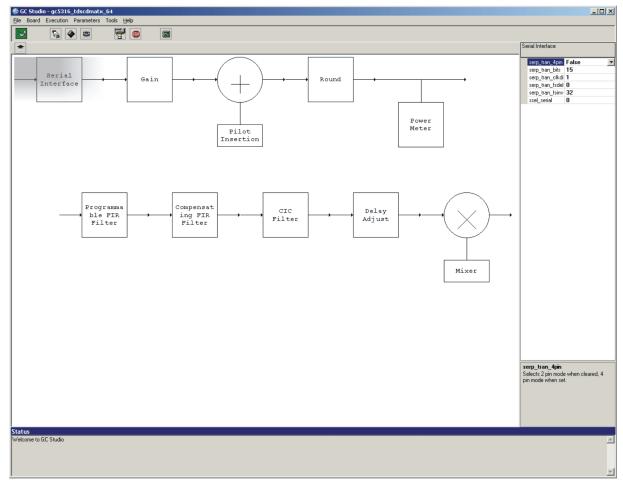

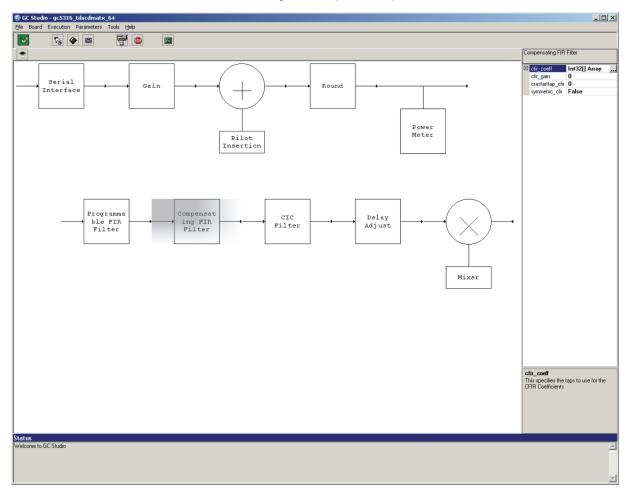

Figure 32. TD-SCDMA - Transmit Channel 0

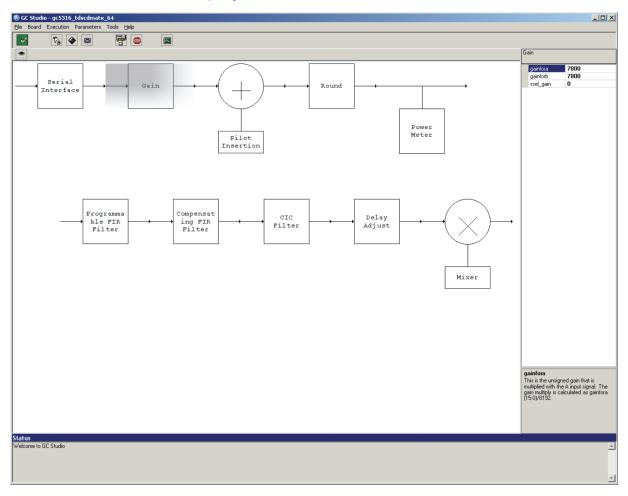

16. Next, set the value for the input gain.

Figure 33. TD-SCDMA - Input Gain Setting

Notice the Pilot insertion is available for CDMA application. The Power Meter is provided but will not be used in this example.

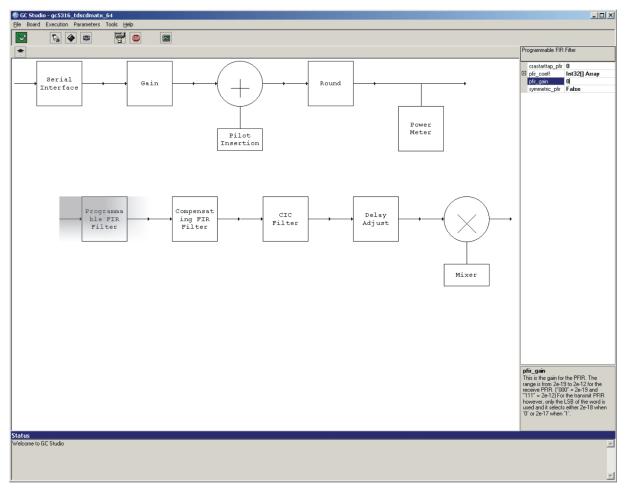

17. Select the PFIR block and set the cfir\_gain to 0 (2.00E-19).

Figure 34. TD-SCDMA – PFIR Block

18. Next, select the pfir\_coeff register setting by clicking on it, and then click on the browse button, to open the Edit Filter window and fill in the PFIR filter tap weights.

Figure 35. TD-SCDMA - pfir\_coeff Register Setting

19. Select the CFIR block next, set the cfir\_gain to 0 (2.00E-18).

Figure 36. TD-SCDMA – CFIR Block Setting

20. Select the pfir\_coeff register, and again select the browse button.

21. Enter the following 31 taps for the CFIR coefficients.

Figure 37. TD-SCDMA - CFIR Coefficients

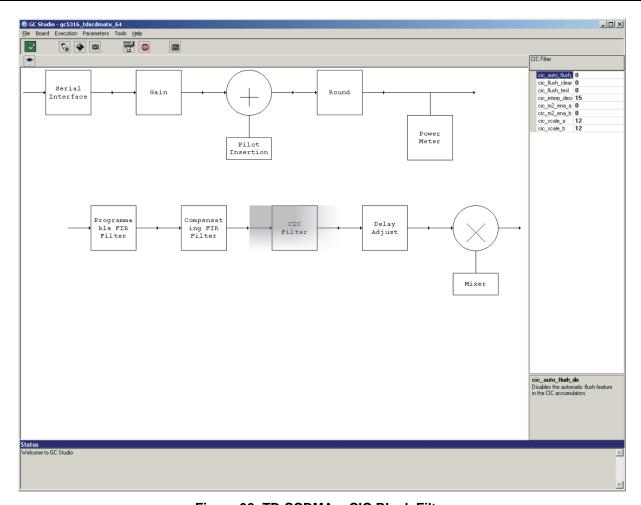

22. Next, select the CIC Filter block. Set the interpolation to 16 ("cic\_interp\_decim" = 15), and the CIC scale factor to (pre-calculated) value of 12. Please see the datasheet about the formulas to calculate the CIC Filter scale values ("cic\_scale\_x").

Figure 38. TD-SCDMA – CIC Block Filter

The other parameters can be set as default when GC Studio opened.

- 23. Transmit Channel 0 has now been configured to process:

- A TD-SCDMA signal from the input rate of 1.28Msps with a 0 MHz IF

- The PFIR shapes the signal, and interpolates by two; the output of the PFIR is at 2.56 MSPS

- The CFIR further filters the unwanted interpolation images and filters images outside the band of interest. The CFIR interpolates by 2; the output of the CFIR is at 5.12 MSPS

- The six-stage CIC filter interpolates by 16, to the final output rate of 81.92 MSPS.

- The NCO is set for the mixing frequency in mixer.

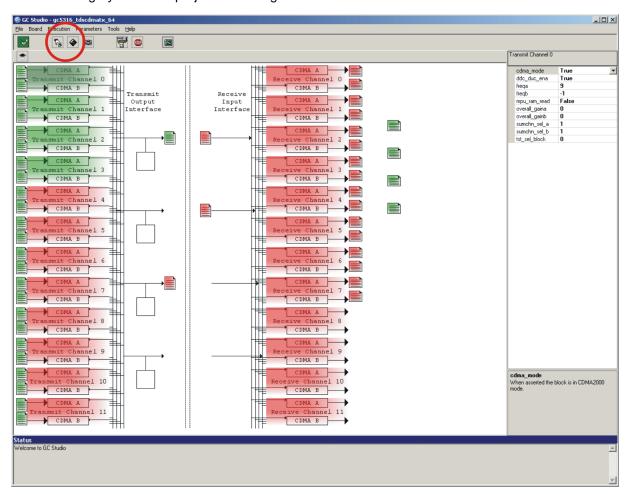

After all four channels are appropriately set, the block diagram should show first four channels as active (green).

Input data presented to the gc5316 pins comes from text format data files. Two input file icons can be seen in the block diagram to the far left since the mode is set to CDMA

24. Click on the top icon, circled as shown in Figure 39, and make sure that the input files are selected.

Figure 39. TD-SCDMA - Input Files

25. Now, select the data to be shown on the output.

26. Click the Add New Data Source button circled as shown in Figure 40.

Figure 40. TD-SCDMA - Add New Data Source

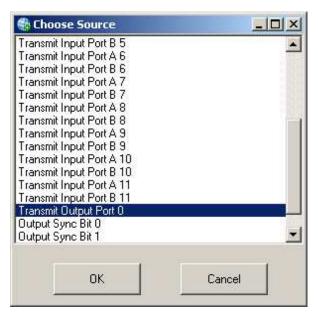

27. In the Choose Source panel, select both Transmit Output Port 0, and click OK. Since all eight outputs are muxed on a single transmit port, this will allow us to see them all displayed.

Figure 41. TD-SCDMA - Choose Source

28. In the graph panel, set the Plot Type to Spectral Magnitude, and check Logarithmic.

29. On the GC Studio panel, click the Build and Load buttons, circled as shown in Figure 42. The buttons will turn grey while the project is running.

Figure 42. TD-SCDMA – Build and Load Buttons

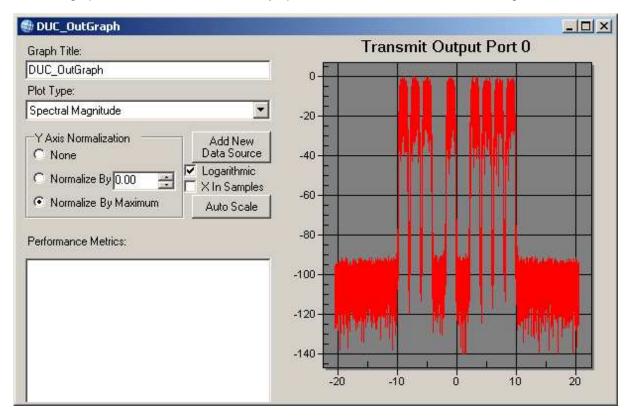

30. The graph window will be automatically updated with the results as shown in Figure 43.

Figure 43. TD-SCDMA - Graph Window Results

31. On the GC Studio panel, click on the stop button, shown circled below, to stop the experiment, then select File > Save Project to save this project.

Figure 44. TD-SCDMA - Stop and Saving Project

32. Close the GC Studio Graph Window.

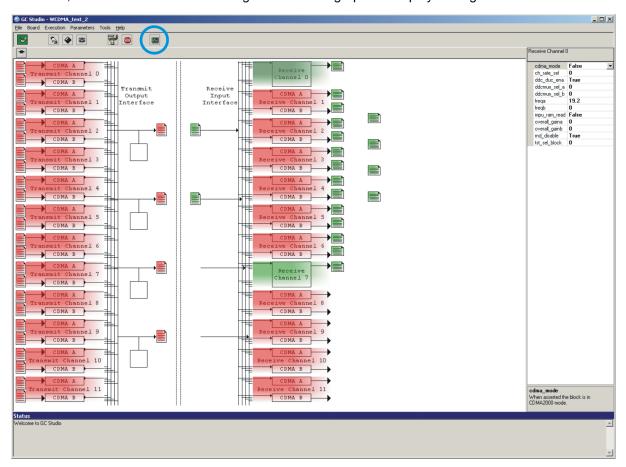

### 2.2.3 Creating a New GC Studio Project for a WCDMA Receive Configuration

This project demonstrates the ability of the GC5316 to downconvert channels from a real, parallel input stream. The input spectrum shows the input image (which is a real signal, which explains the negative image in the spectrum).

- One real WCDMA carriers is applied to the GC5316 rxin\_a

- Simulated rxclk to the GC5316 is 122.88MHz

- Receive FIFOs are enabled

- Receive Channel 0 is configured to process the signal

- Channel NCOs tune to an IF of 19.2 MHz

- The CIC filter is programmed to decimate by 8. The output sample rate at the CIC output is 15.36Msps

- The CFIR filter compensates for the droop in the CIC filter, and provides some low pass filtering. It is configured as a 32-tap filter. It decimates by 2.

- The 64 tap PFIR provides final symbol shaping and filtering.

- Channel AGC is configured as fixed unity gain

- Baseband data is transmitted and captured using the serial interface at the full rxclk rate.

- 1. Start GC Studio

- 2. Click on File > New Project to bring up the following window.

- 3. Choose a name for this new project, and click create.

- 4. Select GC5316 for the Plugin and click OK.

- 5. Using the wizard style interface, setup the GC101 evaluation board, then click next.

- 6. Setup the GC5316 I/O mode selection as shown and click next. In this example, be sure the ADC clock rate is set to 1. Because we are using a Receive channel for this experiment, set the Input Mode and Output Mode boxes to Transmit Ports as shown below. We will set the Output Clock Source to TX Clk Out. Ensure that the Output Syncs and Strobes are set to "Rx Sync Out and PB Data". Click "Next" to see the Simulated Clock Rates screen.

Figure 45. WCDMA - I/O Mode Selection

7. Set the simulated clock rate to 122.88 MHz and click next.

Figure 46. WCDMA - Simulated Clock Rates

8. Channel Copying will be skipped for now, click Next

Figure 47. WCDMA - Channel Copying

- 9. Finish the set-up Wizard as explained in the previous example.

- 10. Click on the large gc5316 box to display the global control registers.

Figure 48. WCDMA - Global Control Registers

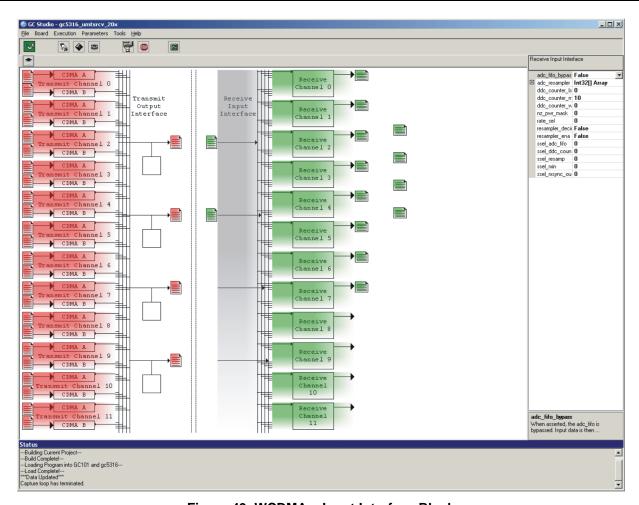

- 11. Next, double click on the gc5316 block to "push down" one level into the gc5316.

- 12. Click on the Input Interface block to display and edit the receive input interface registers. Set adc\_fifo\_bypass to FALSE to enable the rxin\_a/b/c/d input FIFO circuits.

Figure 49. WCDMA - Input Interface Block

13. Click on the upper Receive Channel 0 block. Set ddc\_duc\_ena to True. Make sure that the cdma\_mode is set to False, since this example is processing the WCDMA signal.

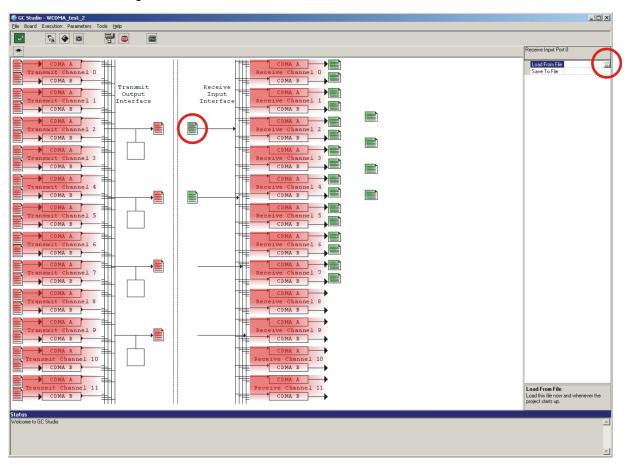

14. Click on the area circled by "Load From File", as shown in Figure 50. Load the stimulus file "TM1\_300k\_IF19.2\_Fup122.88\_1000.GCIN" found on the provided CD. This file will simulate a real TM1 WCDMA signal at an IF of 19.2 MHz.

Figure 50. WCDMA - Loading the Stimulus File

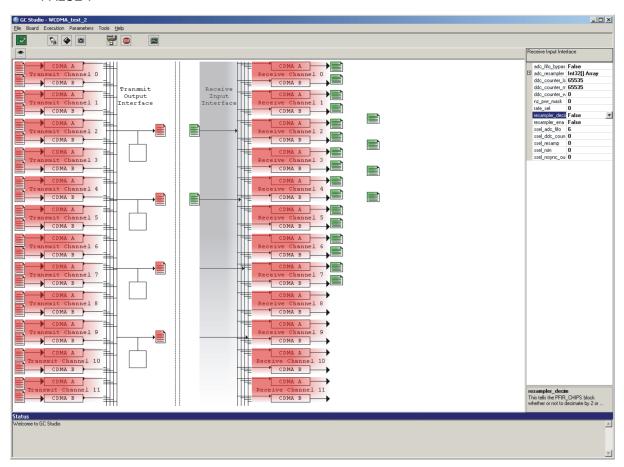

15. Click on the Receive Input Interface section, then make sure that the "resampler\_decimate" is set to "FALSE".

Figure 51. WCDMA - Receive Channel Block

16. Next, click on Receive Channel 0, and make sure cdma\_mode is set to "False". Set the NCO Frequency (freqa) to 19.2 (MHz). Re-set the "ch\_rate\_sel" to 0 to guarantee this register gets set properly. This is shown in Figure 52.

Figure 52. WCDMA - Enable Channel 0

17. Double-click on Receive Channel 0 to define the parameters inside the channel. Click on the "Delay Adjust and Zero Pad" box.

Since the ADC will run at the DDC rate, "tadj\_interp\_dec" bit needs to be set to 0, to interpolate by 1 as shown in Figure 53.

Figure 53. WCDMA - Delay Adjust and Zero Stuff Block

18. The CIC filter decimates by 8, and the CIC shifter gain needs to be scaled as shown (see the formula in the datasheet):

Figure 54. WCDMA – CIC Filter Block

19. The CFIR is 32 taps long with the coefficients loaded from the file"UMTS\_CFIR\_32.taps", which is located on the provided CD.

Figure 55. WCDMA - CFIR Block

20. The PFIR is 64 taps long, decimating by 1. Load coefficients from the file "UMTS\_PFIR\_64.taps", which is located on the provided CD.

Figure 56. WCDMA - PFIR Block

21. Set the gain of PFIR to "1".

Figure 57. WCDMA - Setting PFIR Gain

22. Click on the "AGC" block and set the registers as shown in Figure 58.

Figure 58. WCDMA - ACG Block

23. Select the Serial Interface block and set the parameters as indicated. Set the number of output bits to 16 ("pser\_recv\_bits" = 15) as shown in Figure 59. No clock division will be used. After verifying the values of the serial interface, click the arrow as shown in Figure 60 to pop up one level in the GC5316 hierarchy.

Figure 59. WCDMA - Serial Interface Block

Figure 60. WCDMA - Serial Interface Block

- 24. Receive Channel 0 has now been configured to process:

- Four WCDMA signals at 122.88 MSPS

- Mixer/nco block shifts the signal to DC

- The CIC block decimates by 8x to 15.36 MSPS

- 32-tap CFIR compensates for the CIC droop, filters and decimates the signal to 7.68 MSPS

- 64-tap PFIR filters the signal

- Channel AGC is set

- Serial interface is used to output the baseband signal at serial output clock of 122.88 MHz

- 25. Copy the Receive Channel 0 settings to Receive Channel 7 by going to Parameter  $\rightarrow$  GC5316 Channel Copy.

- 26. Next, click on the icon circled as shown in Figure 61 for the graphical display settings:

Figure 61. WCDMA - Input Interface Block

27. Click the Add New Data Source button circled shown in Figure 62.

Figure 62. WCDMA - Add New Data Source (1)

28. In the Choose Source panel, select Receive Output Port A 0, and click OK.

Figure 63. WCDMA - Choose Source (1)

- 29. In the graph panel, set the Plot Type to Spectral Magnitude, and check Logarithmic.

- 30. Again, click on the plot button to open another plot to view the input data.

- 31. Click the Add New Data Source button circled as shown in Figure 64.

Figure 64. WCDMA - Add New Source Data (2)

32. In the Choose Source panel, select Receive Input Port 0, and click OK.

Figure 65. WCDMA - Choose Source (2)

33. On the GC Studio panel, click the Build and Load buttons, circled in Figure 66. This will execute the experiment.

Figure 66. WCDMA - Build and Load Buttons

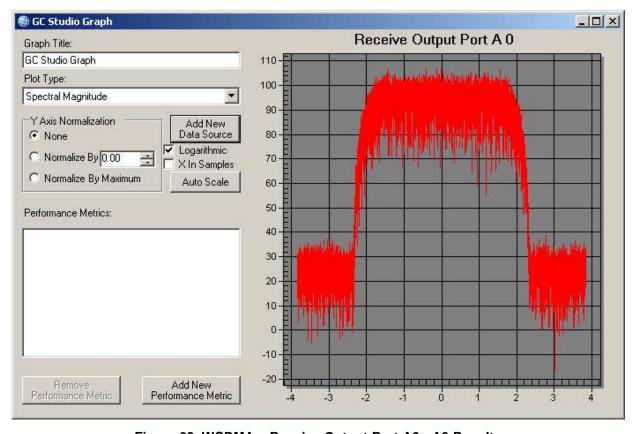

34. The graph window will be automatically updated with the results as shown in Figures 67 and 68.

Figure 67. WCDMA - Receive Input Port 0 Results

Figure 68. WCDMA – Receive Output Port A0 - A3 Results

35. On the GC Studio panel, click on the stop button, shown circled below, to stop the experiment, then select File → Save Project to save this project.

Figure 69. WCDMA - Stop and File -> Save

36. Close the GC Studio Graph Window.

# 2.2.4 GC5316 Projects included in the GC Studio Release

The following example projects are included in the GC Studio Release

### CDMA2000 Rx

- A real CDMA carrier is applied to the GC5316 rxin\_a inputs with a simulated sample rate of 61.44 Msps and an IF frequency of 30.72MHz.

- Simulated rxclk to the GC5316 is 122.88MHz

- Receive FIFOs are enabled

- Receive AGC is set to a constant gain

- Receive Channel 0 is configured to process the signal

- The resampler is turned on, which downshifts the data by  $F_8/4$  (122.88/4 = 30.72).

- Channel 0 A&B, which have their NCO's tuned to ± .625 are filtering and isolating the signals centered at 30.72 ±.625MHz.

- The CIC filter is programmed to decimate by 25 using a m=2 comb section configuration. The output sample rate at the CIC output is 4.9152Msps

- The CFIR filter compensates for the droop in the CIC filter, and provides some low pass filtering. It is configured as a 48 tap filter.

- The 64 tap PFIR provides final symbol shaping and filtering.

- Channel AGC is configured as fixed unity gain

- Baseband data is transmitted and captured using the serial interface at the half rxclk rate

#### CDMA2000 Tx

- Each of the transmit channels is fed a typical CDMA baseband signal at approximately 1.2288 MHz bandwidth.

- Simulated rxclk to the GC5316 is 122.88MHz

- This project shows a general CDMA transmit case, using 50x total interpolation.

- Front Gain is set to 78 dB

- First 8 Channels are configured to process 8 CDMA signals

- The output of this experiment shows the channels stacked against each other. The frequency spacing

in the stack is 1.25MHz.

- The channel that would be just to the left of 0MHz has been turned off in order to show the noise rejection between two channels of the chip.

#### TD-SCDMA

- A 3 carrier TD-SCDMA signal is applied to the GC5316 inputs with a simulated sample rate of 76.8Msps and an IF frequency of 9.6MHz.

- Simulated rxclk to the gc5316 is 76.8MHz

- Receive FIFOs are enabled

- Receive AGC is bypassed

- Receive Channel 0 is configured in CDMA mode and therefore processes two TD-SCDMA channels, referred to as A and B.

- A channel mixer/nco shifts the 11.2MHz carrier to DC, the B channel shifts the 8MHz carrier to DC.

- The CIC filter is programmed to decimate by 15 using a m=2 comb section configuration. The output sample rate at the CIC output is 5.12Msps

- The CFIR filter compensates for the droop in the CIC filter, and provides some low pass filtering. It is configured as a 28 tap filter, which is the maximum length that can be computed with rxclk at 76.8MHz and the CFIR output rate of 5.12Msps.

- The 60 tap PFIR provides final symbol shaping and filtering. 60 taps is the maximum length that can be computed with a 76.8MHz rxclk and 5.12Msps output rate

- Channel AGC is configured as fixed unity gain

- Baseband data is decimated by 2 in the output interface, and then transmitted and captured using the serial interface at the full rxclk rate.

## GSM

- A 24-carrier GSM signal is applied to the GC5316 inputs with a simulated sample rate of 34.6665Msps.

- Simulated rxclk to the GC5316 is 69.333MHz

- · Receive FIFOs are enabled

- Receive AGC is bypassed

- The DDC channel has a 64-tap PFIR at 4x, 48-tap CFIR at 8x, 32 Decimation ratio for CIC filter. (The DUC would be similar and would have 63-tap PFIR at 4x, and a 47-tap CFIR at 8x. The CIC ratio is 32, the CFIR ratio is 2, and the PFIR ratio is 1).

- Baseband data is transmitted and captured using the serial interface at the full rxclk rate.

#### **WCDMA**

- Four real WCDMA carriers is applied to the GC5316 rxin\_a

- Simulated rxclk to the GC5316 is 122.88MHz

- Receive FIFOs are enabled

- Receive Channels 0-3 are configured to process the signal

- Channel NCOs tune to four different IF frequencies

- The CIC filter is programmed to decimate by 5. The output sample rate at the CIC output is 15.36Msps

- The CFIR filter compensates for the droop in the CIC filter, and provides some low pass filtering. It is configured as a 20 tap filter.

- The 40 tap PFIR provides final symbol shaping and filtering

- Channel AGC is configured as fixed unity gain

- Baseband data is transmitted and captured using the serial interface at the full rxclk rate.

#### 2.2.5 GC Studio References

For more information on GC Studio, see the GC Studio User's Manual included with the software distribution. GC Studio also contains a powerful scripting language for expert users, see the SCR GC101 Language Reference also included in the software distribution. Selecting Help > User's Manuals in the GC Studio menu to these documents.

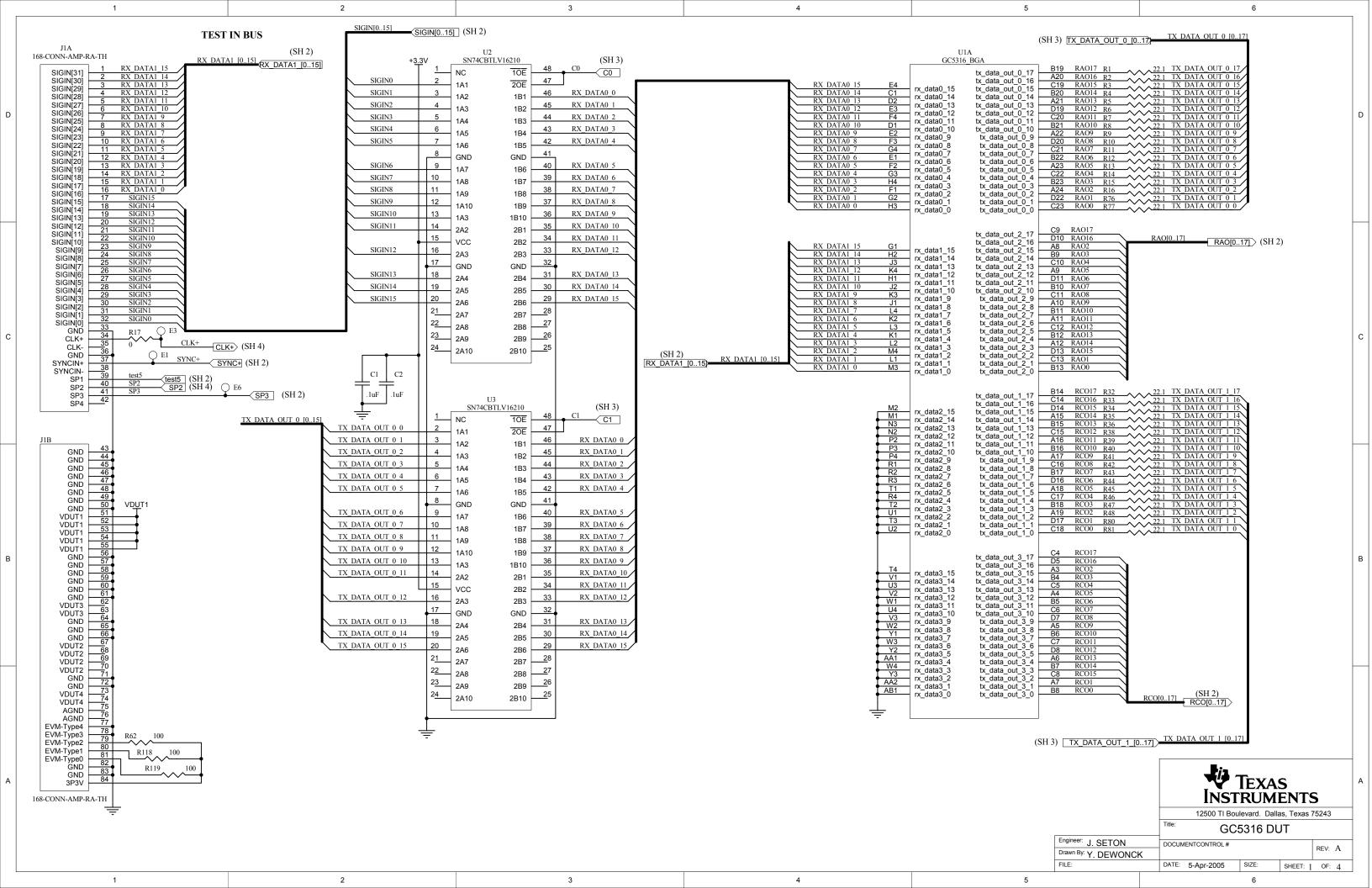

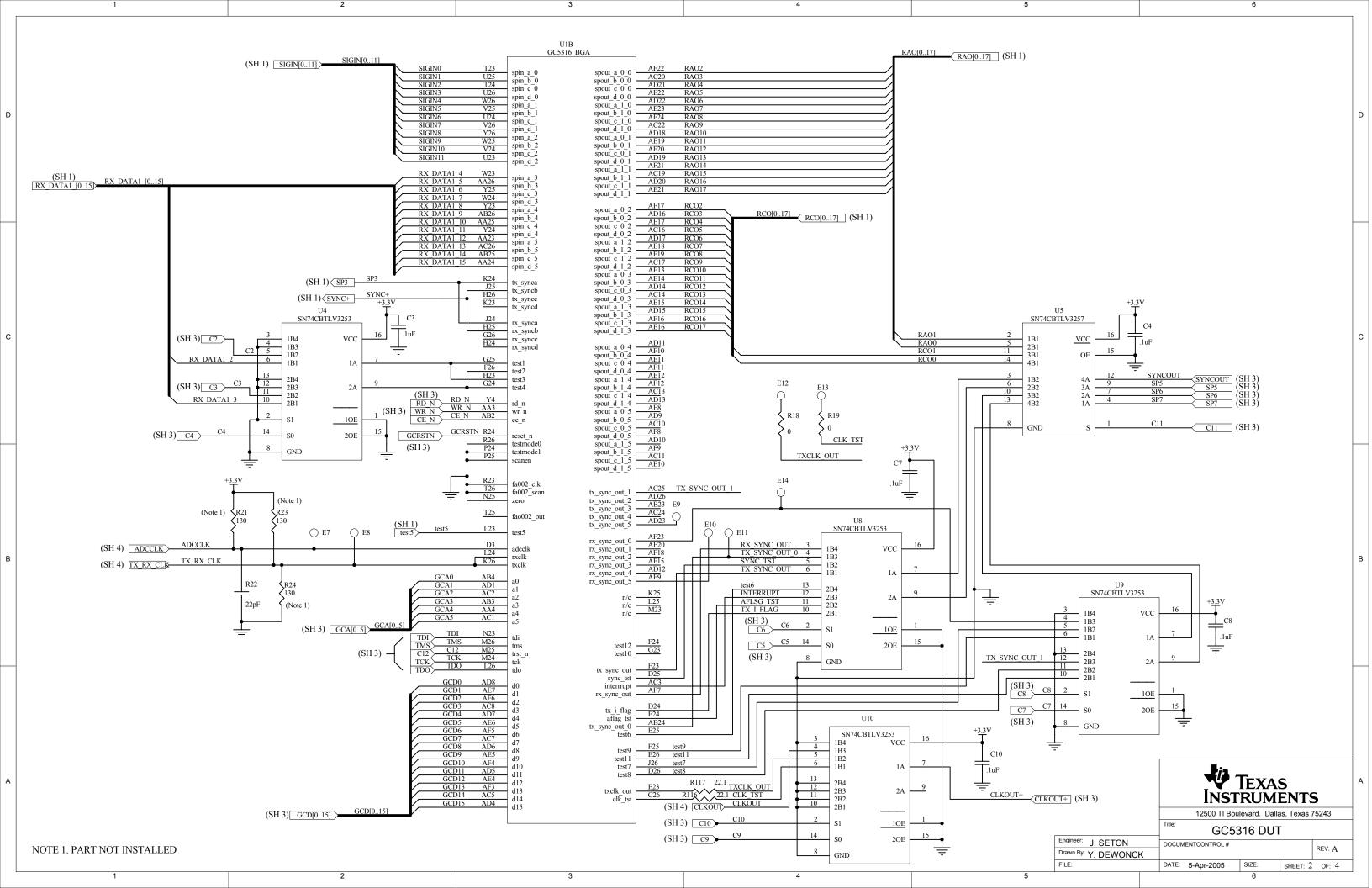

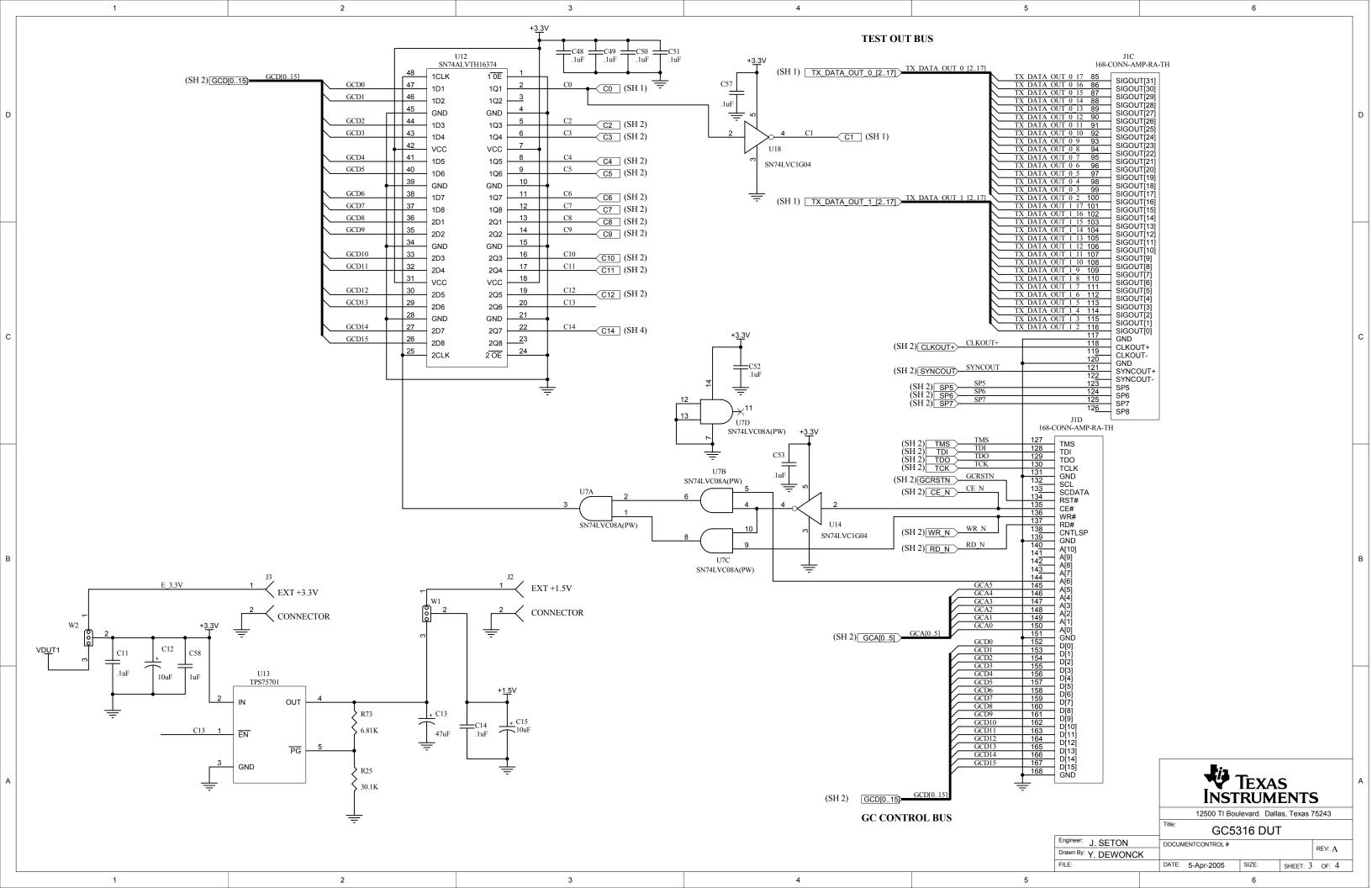

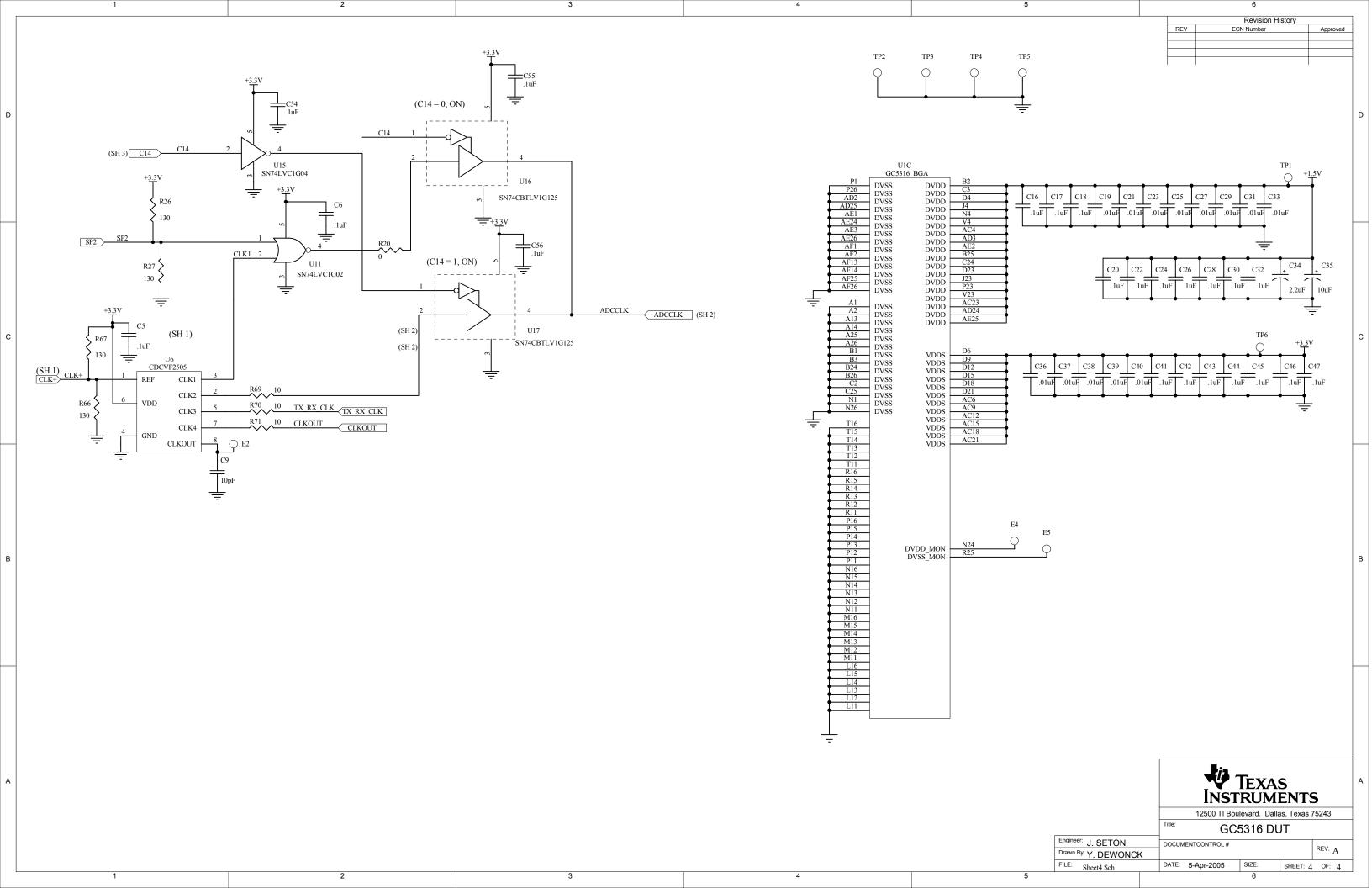

# 3 GC5316 Daughtercard Description

## 3.1 GC5316 Power and Ground Signal Description

- VDUT1 3.3V power from GC101 EVM to the daughtercard

- GND

See the GC101 EVM Manual for the 168 pin connector table. Detailed schematics for the GC5316 daughtercard can be found in Section 3.

## 3.2 GC5316 Daughtercard Jumpers

3.3V power for the GC5316 daughtercard can be supplied by the GC101 motherboard or an external power supply. A regulator on the daughtercard can be used to generate the 1.5V core supply voltage or an external supply can be used.

Jumper W1 - Selects source for GC5316 core 1.5V power

position 1:2 selects an external supply connected to J2 for the 1.5V core supply

position 2:3 selects the regulator on the daughtercard as the 1.5V core supply

Jumper W2 Selects source for GC5316 I/O 3.3V power

position 1:2 selects an external supply connected to J3 for the 3.3V I/O supply

position 2:3 selects the GC101 motherboard as the source for the 3.3V I/O supply

# 3.3 GC5316 Daughtercard Power Supplies

The GC5316 core power supply is 1.5V. The daughtercard includes a regulator that can be used to supply this 1.5V to the GC5316 or an external power supply can be connected at J2.

The GC5316 I/O power supply is 3.3V, and can be supplied by the GC101 motherboard or an external power supply connected to J3.

# 4 Physical Description

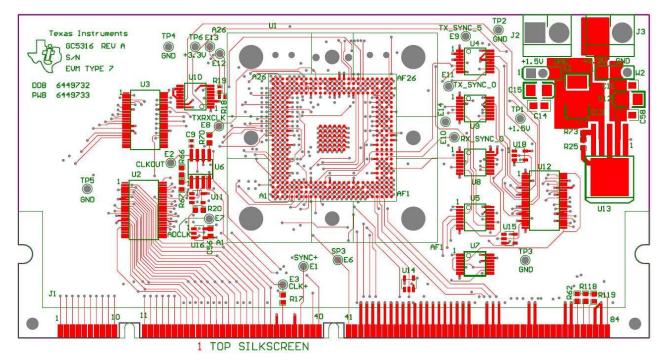

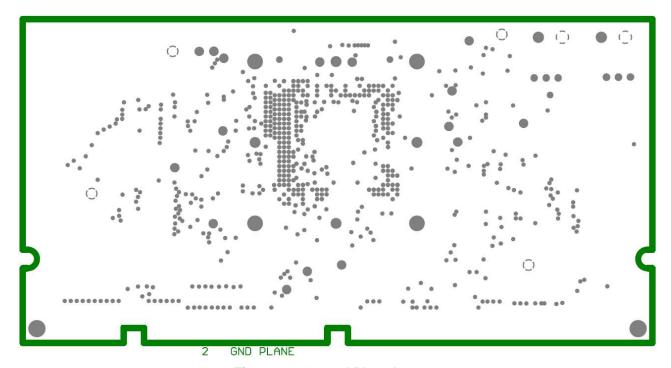

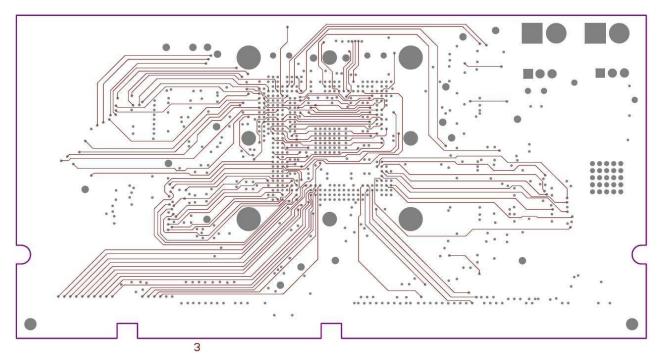

This chapter describes the physical characteristics and PCB layout of the GC5316 Daughtercard and lists the components used on the module.

# 4.1 PCB Layout

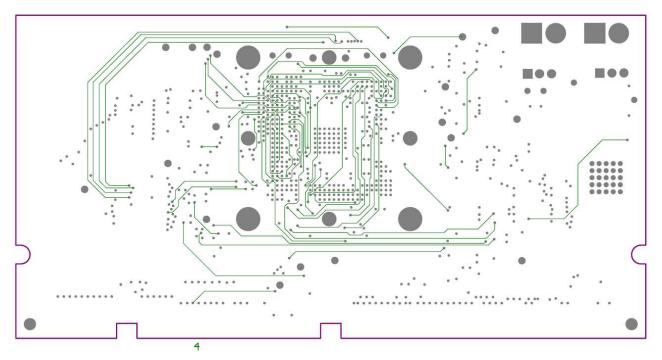

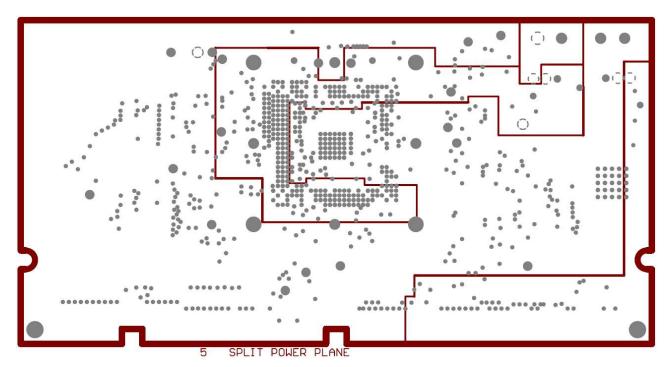

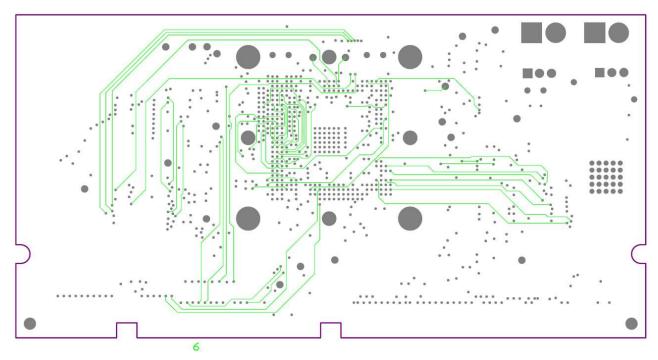

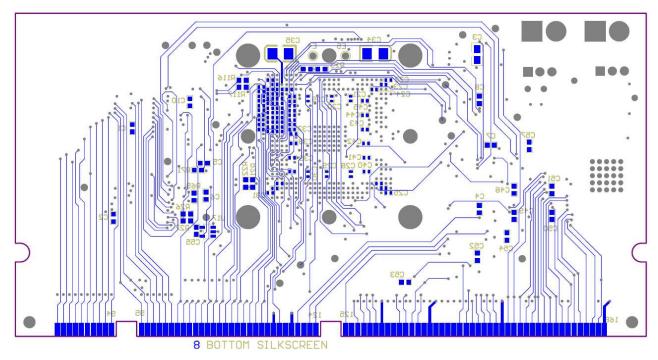

The board is constructed on a 8-layer, 5.25-inch x 2.7-inch, 0.056-inch thick PCB using FR-4 material. Figures 70 through 77 show the PCB layout for the daughtercard

Figure 70. Top Layer 1

Figure 71. Ground Plane Layer 2

Figure 72. Signal Layer 3

Figure 73. Signal Layer 4

Figure 74. Power Plan Layer 5

Figure 75. Signal Layer 6

Figure 76. Ground Plane Layer 7

Figure 77. Bottom Layer 8

# 4.2 Parts List

Table 5-1 lists the parts used in constructing the GC5316 Daughtercard.

**Table 1. Bill of Materials**

| Table 1. Dill of Materials     |        |                      |                      |                                                              |               |  |  |

|--------------------------------|--------|----------------------|----------------------|--------------------------------------------------------------|---------------|--|--|

| VALUE                          | QTY    | PART NUMBER          | VENDOR               | REF DES                                                      | NOT INSTALLED |  |  |

|                                |        | CAPA                 | CITORS               |                                                              |               |  |  |

| 47uF, 10V, 10%, Capacitor      | 1      | ECS-T1AD476R         | PANASONIC            | C13                                                          |               |  |  |

| 2.2uF, 20V, 10%, Capacitor     | 1      | ECS-T1DX225R         | PANASONIC            | C34                                                          |               |  |  |

| 10uF, 20V, 10%, Capacitor      | 3      | ECS-T1DX106R         | PANASONIC            | C12 C15 C35                                                  |               |  |  |

| 1uF, 10V, 10%, Capacitor       | 1      | ECJ-2YB1A105K        | PANASONIC            | C58                                                          |               |  |  |

| 0.1uF, 16V, 10%, Capacitor     | 3      | ECJ-2VB1C104K        | PANASONIC            | C3 C11 C14                                                   |               |  |  |

| 0.1uF, 16V, 10%, Capacitor     | 18     | ECJ-1VB1C104K        | PANASONIC            | C1 C2 C4-C8 C10<br>C48-C57                                   |               |  |  |

| 0.01uF,16V, 10%, Capacitor     | 13     | ECJ-0EF1C103Z        | PANASONIC            | C19 C21 C23 C25<br>C27 C29 C31 C33<br>C36 C37 C38 C39<br>C40 |               |  |  |

| 0.1uF,16V, 10%, Capacitor      | 17     | ECJ-0EF1C104Z        | PANASONIC            | C16 C17 C18 C20<br>C22 C24 C26 C28<br>C30 C32 C41-C47        |               |  |  |

| 22pF,50V, 5%, Capacitor        | 1      | ECJ-1VC1H220J        | PANASONIC            | C22                                                          |               |  |  |

| 10pF,50V, 5%, Capacitor        | 1      | ECJ-0EC1H100D        | PANASONIC            | C9                                                           |               |  |  |

|                                |        | RESIS                | STORS                |                                                              |               |  |  |

| 100 ohm resistor, 1/16 W, 1%   | 3      | ERJ-3EKF1000V        | PANASONIC            | R62 R118 R119                                                |               |  |  |

| 130 ohm resistor, 1/16 W, 1%   | 4      | ERJ-3EKF1300V        | PANASONIC            | R26 R27 R66 R67                                              | R21 R23 R24   |  |  |

| 10 Ohm Resistor, 1/16 W, 1%    | 2      | ERJ-3EKF100V         | PANASONIC            | R69 R70 R71                                                  |               |  |  |

| 0 Ohm Resistor, 1/16 W, 1%     | 2      | ERJ-3GEY0R00V        | PANASONIC            | R17 R20                                                      |               |  |  |

| 6.81K Ohm Resistor, 1/16 W, 1% | 1      | ERJ-3EKF6811V        | PANASONIC            | R73                                                          |               |  |  |

| 30.1K Ohm Resistor, 1/16 W, 1% | 1      | ERJ-3EKF3011V        | PANASONIC            | R25                                                          |               |  |  |

| 22.1ohm resistor, 1/16 W, 1%   | 2      | ERJ-3EKF22R1V        | PANASONIC            | R116 R117                                                    |               |  |  |

| 0 Ohm Resistor, 1/16 W, 5%     | 2      | 9C040210R00JLHF<br>3 | YAGEO                | R18 R19                                                      |               |  |  |

| 22.1ohm resistor, 1/16 W, 1%   | 36     | ERJ-2RKF22R1V        | PANASONIC            | R1-R16 R32-R36<br>R38-R48 R76 R77<br>R80 R81                 |               |  |  |

|                                | CONNEC | TORS, HEADERS, SW    | ITCHES, LED'S & TE   | ST POINTS                                                    |               |  |  |

| Red test point                 | 2      | 5000k                | KEYSTONE             | TP1 TP6                                                      |               |  |  |

| Black test point               | 4      | 5001k                | KEYSTONE             | TP2 TP3 TP4 TP5                                              |               |  |  |

| CON_2TERM_SCREW                | 2      | KRMZ3                | LUMBERG              | J2 J3                                                        |               |  |  |

| 3POS-HEADER                    | 2      | TWS-150-07-L-S       | SAMTEC               | W1 W2                                                        |               |  |  |

| ICs                            |        |                      |                      |                                                              |               |  |  |

| GC5316IZED                     | 1      | GC5316IZED           | TEXAS<br>INSTRUMENTS | U1                                                           |               |  |  |

| CDCVF2505D                     | 1      | CDCVF2505D           | TEXAS<br>INSTRUMENTS | U6                                                           |               |  |  |

| SN74CBTLV16210GR               | 2      | SN74CBTLV16210<br>GR | TEXAS<br>INSTRUMENTS | U2 U3                                                        |               |  |  |

| SN74CBTLV3253PWR               | 4      | SN74CBTLV3253P<br>WR | TEXAS<br>INSTRUMENTS | U4 U8 U9 U10                                                 |               |  |  |

| SN74CBTLV3257PWR               | 1      | SN74CBTLV3257P<br>WR | TEXAS<br>INSTRUMENTS | U5                                                           |               |  |  |

Table 1. Bill of Materials (continued)

| VALUE               | QTY | PART NUMBER             | VENDOR               | REF DES     | NOT INSTALLED |

|---------------------|-----|-------------------------|----------------------|-------------|---------------|

| SN74LVC08APWR       | 1   | SN74LVC08APWR           | TEXAS<br>INSTRUMENTS | U7          |               |

| SN74ALVTH16374(DGG) | 1   | SN74ALVTH16374(<br>DGG) | TEXAS<br>INSTRUMENTS | U12         |               |

| SN74CBTLV1G125DBVR  | 2   | SN74CBTLV1G125<br>DBVR  | TEXAS<br>INSTRUMENTS | U16 U17     |               |

| SN74LVC1G02DBVR     | 1   | SN74LVC1G02DBV<br>R     | TEXAS<br>INSTRUMENTS | U11         |               |

| SN74LVC1G04DBVR     | 3   | SN74LVC1G04DBV<br>R     | TEXAS<br>INSTRUMENTS | U14 U15 U18 |               |

| TPS75701KTTT        | 1   | TPS75701KTTT            | TEXAS<br>INSTRUMENTS | U13         |               |

# 4.3 Schematics

#### **EVALUATION BOARD/KIT IMPORTANT NOTICE**

Texas Instruments (TI) provides the enclosed product(s) under the following conditions:

This evaluation board/kit is intended for use for **ENGINEERING DEVELOPMENT**, **DEMONSTRATION**, **OR EVALUATION PURPOSES ONLY** and is not considered by TI to be a finished end-product fit for general consumer use. Persons handling the product(s) must have electronics training and observe good engineering practice standards. As such, the goods being provided are not intended to be complete in terms of required design-, marketing-, and/or manufacturing-related protective considerations, including product safety and environmental measures typically found in end products that incorporate such semiconductor components or circuit boards. This evaluation board/kit does not fall within the scope of the European Union directives regarding electromagnetic compatibility, restricted substances (RoHS), recycling (WEEE), FCC, CE or UL, and therefore may not meet the technical requirements of these directives or other related directives.

Should this evaluation board/kit not meet the specifications indicated in the User's Guide, the board/kit may be returned within 30 days from the date of delivery for a full refund. THE FOREGOING WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY SELLER TO BUYER AND IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED, IMPLIED, OR STATUTORY, INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE.

The user assumes all responsibility and liability for proper and safe handling of the goods. Further, the user indemnifies TI from all claims arising from the handling or use of the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge.

EXCEPT TO THE EXTENT OF THE INDEMNITY SET FORTH ABOVE, NEITHER PARTY SHALL BE LIABLE TO THE OTHER FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES.

TI currently deals with a variety of customers for products, and therefore our arrangement with the user is not exclusive.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein.

Please read the User's Guide and, specifically, the Warnings and Restrictions notice in the User's Guide prior to handling the product. This notice contains important safety information about temperatures and voltages. For additional information on TI's environmental and/or safety programs, please contact the TI application engineer or visit www.ti.com/esh.

No license is granted under any patent right or other intellectual property right of TI covering or relating to any machine, process, or combination in which such TI products or services might be or are used.

## **FCC Warning**

This evaluation board/kit is intended for use for **ENGINEERING DEVELOPMENT**, **DEMONSTRATION**, **OR EVALUATION PURPOSES ONLY** and is not considered by TI to be a finished end-product fit for general consumer use. It generates, uses, and can radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to part 15 of FCC rules, which are designed to provide reasonable protection against radio frequency interference. Operation of this equipment in other environments may cause interference with radio communications, in which case the user at his own expense will be required to take whatever measures may be required to correct this interference.

#### **EVM WARNINGS AND RESTRICTIONS**

It is important to operate this EVM within the input voltage range of 4.75 V to 5.25 V and the output voltage range of 4.75 V to 5.25 V.

Exceeding the specified input range may cause unexpected operation and/or irreversible damage to the EVM. If there are questions concerning the input range, please contact a TI field representative prior to connecting the input power.

Applying loads outside of the specified output range may result in unintended operation and/or possible permanent damage to the EVM. Please consult the EVM User's Guide prior to connecting any load to the EVM output. If there is uncertainty as to the load specification, please contact a TI field representative.

During normal operation, some circuit components may have case temperatures greater than 701½ C. The EVM is designed to operate properly with certain components above 701½ C as long as the input and output ranges are maintained. These components include but are not limited to linear regulators, switching transistors, pass transistors, and current sense resistors. These types of devices can be identified using the EVM schematic located in the EVM User's Guide. When placing measurement probes near these devices during operation, please be aware that these devices may be very warm to the touch.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2006, Texas Instruments Incorporated

### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products              |                        | Applications       |                           |

|-----------------------|------------------------|--------------------|---------------------------|

| Amplifiers            | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters       | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                   | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface             | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic                 | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt            | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers      | microcontroller.ti.com | Security           | www.ti.com/security       |

| RFID                  | www.ti-rfid.com        | Telephony          | www.ti.com/telephony      |

| Low Power<br>Wireless | www.ti.com/lpw         | Video & Imaging    | www.ti.com/video          |

|                       |                        | Wireless           | www.ti.com/wireless       |

|                       |                        |                    |                           |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2007, Texas Instruments Incorporated