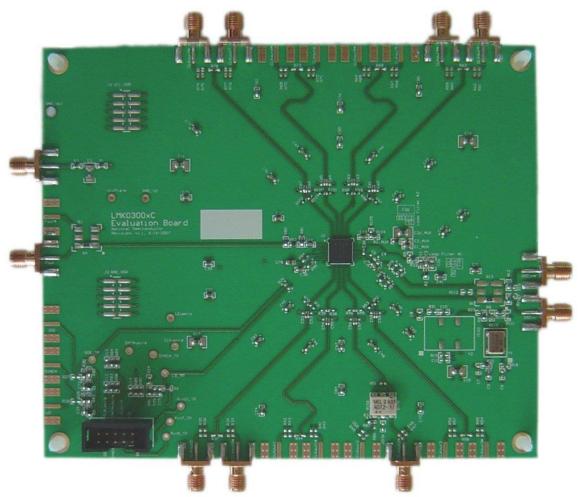

# LMK030xxC Evaluation Board

# **User's Guide**

November 2013 SNAU040A

## LMK03000C/01C/02C/33C

Precision Clock Conditioner with Integrated VCO Evaluation Board Operating Instructions

April 2009

## TABLE OF CONTENTS

| EQUIPMENT                                                                 | 5  |

|---------------------------------------------------------------------------|----|

| BASIC OPERATION                                                           |    |

| LMK03000C BOARD INFORMATION                                               |    |

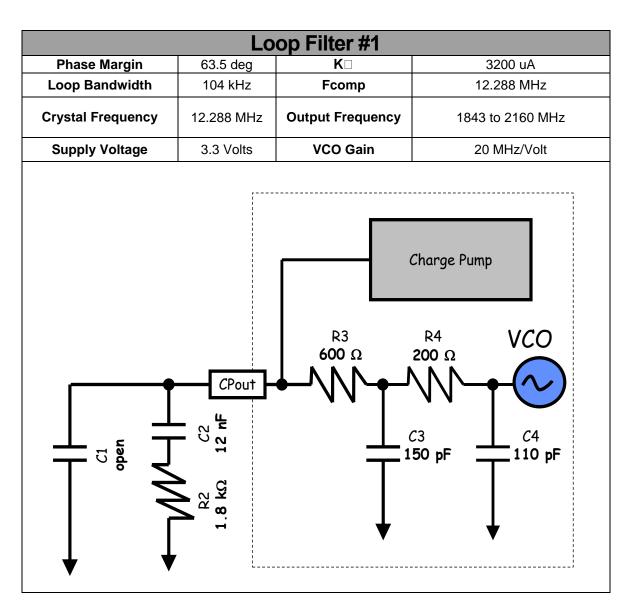

| LOOP FILTER #1                                                            | 9  |

| OSCin                                                                     | 10 |

| Fout                                                                      | 10 |

| Loop Filter                                                               |    |

| Features of the board                                                     |    |

| Other Important Notes                                                     |    |

| 1                                                                         |    |

| Evaluation Board Revision v1.0 Errata                                     |    |

| Results                                                                   |    |

| PHASE NOISE                                                               |    |

| DELAYS                                                                    |    |

| VCO PERFORMANCE.                                                          |    |

| IMPACT OF REFERENCE ON PHASE NOISE                                        |    |

| LMK03001C BOARD INFORMATION<br>LOOP FILTER #1                             |    |

|                                                                           |    |

| OSCin                                                                     |    |

| Fout                                                                      |    |

| Loop Filter                                                               | 18 |

| Features of the board                                                     | 19 |

| Other Important Notes                                                     | 19 |

| Evaluation Board Revision v1.0 Errata                                     |    |

| Results                                                                   |    |

| PHASE NOISE                                                               |    |

| DELAYS                                                                    |    |

| VCO PERFORMANCE                                                           |    |

| IMPACT OF REFERENCE ON PHASE NOISE                                        |    |

| LMK03002C BOARD INFORMATION                                               |    |

| LOOP FILTER #1                                                            | 25 |

| OSCin                                                                     | 26 |

| Fout                                                                      |    |

| Loop Filter                                                               |    |

| Features of the board                                                     |    |

|                                                                           |    |

| Other Important Notes                                                     |    |

| Results                                                                   |    |

| PHASE NOISE                                                               |    |

| DELAYS                                                                    |    |

| VCO PERFORMANCE                                                           |    |

| Loop Filter #2                                                            |    |

| IMPACT OF REFERENCE ON PHASE NOISE                                        |    |

| LMK03033C BOARD INFORMATION                                               |    |

| LOOP FILTER #1                                                            |    |

| OSCin                                                                     |    |

| Fout                                                                      |    |

| Loop Filter                                                               | 34 |

| Features of the board                                                     | 35 |

| Nevember 2012 IMK020vvC Evaluation Reard Llear's Quide SNAL1040A <b>2</b> |    |

| Other Important Notes                        | 35 |

|----------------------------------------------|----|

| Evaluation Board Revision v1.0 Errata        |    |

| Results                                      |    |

| PHASE NOISE                                  |    |

| DELAYS                                       |    |

| VCO PERFORMANCE                              |    |

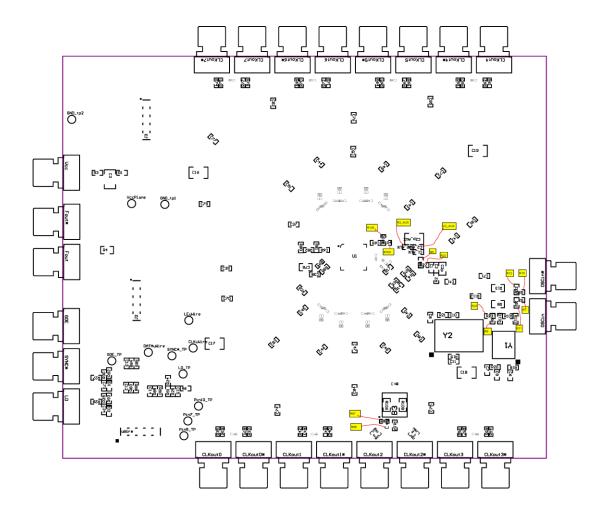

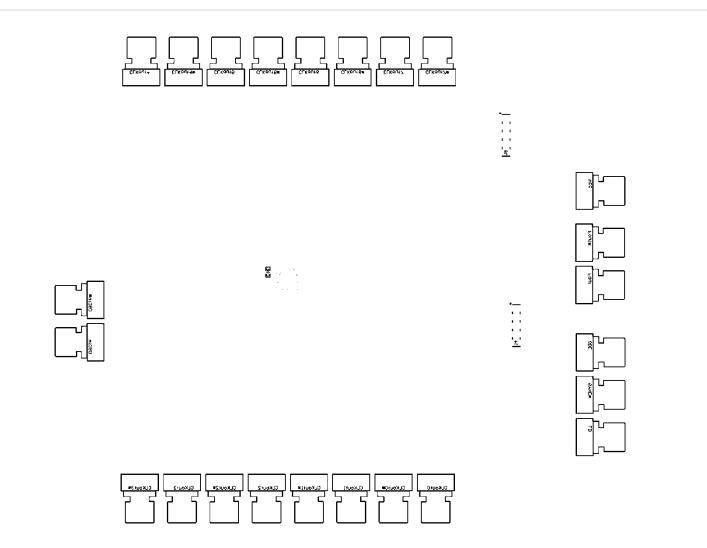

| APPENDIX A: SCHEMATICS                       | 40 |

| APPENDIX B: BILL OF MATERIALS                | 43 |

| APPENDIX C: BUILD DIAGRAM                    | 45 |

| APPENDIX D: QUICK START ON EVM COMMUNICATION | 47 |

|                                              |    |

## Equipment

#### Power Supply

The Power Supply should be a low noise power supply. An Agilent 6623A Triple power supply with LC filters on the output to reduce noise was used in creating these evaluation board instructions.

#### Phase Noise / Spectrum Analyzer

For measuring phase noise an Agilent E5052A is recommended. An Agilent E4445A PSA Spectrum Analyzer with the Phase Noise option is also usable although the architecture of the E5052A is superior for phase noise measurements. At frequencies less than 100 MHz the local oscillator noise of the PSA is too high and measurements will be of the local oscillator, not the device under test.

#### <u>Oscilloscope</u>

The oscilloscope and probes should be capable of measuring the output frequencies of interest when evaluating this board. The Agilent Infiniium DSO81204A was used in creating these evaluation board instructions.

#### Reference Oscillator

The on board crystal oscillator will provide a low noise reference signal to the device at offsets greater than 1 kHz.

Note: The default loop filter has a loop bandwidth of ~60 kHz. Inside the loop bandwidth of a PLL the noise is greatly affected by any noise on the reference oscillator (OSCin). Therefore any noise on the oscillator less than 60 kHz will be passed through and seen on the outputs. For this reason the main output of a Signal Generator is not recommended for driving OSCin in this setup.

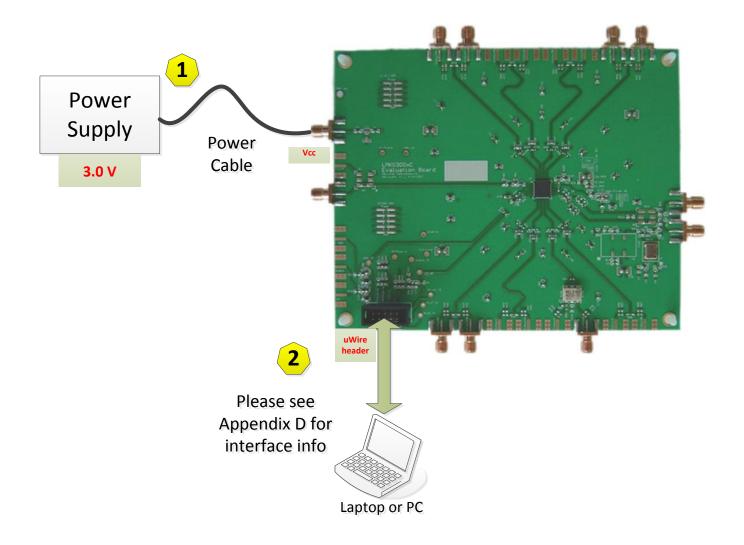

## **Basic Operation**

- 1. Connect a low noise **3.3 V** power supply to the **Vcc** connector located at the top left of the board.

- 2. Please see Appendix D for quick start on interfacing the board. Connect PC to the uWire header.

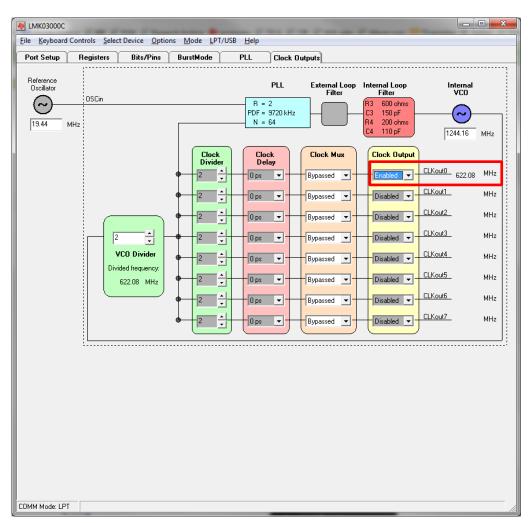

- 3. Start CodeLoader4.exe.

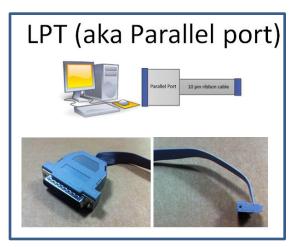

- 4. Select the USB or LPT Communication Mode on the Port Setup tab as appropriate.

- 5. Enable output to be measured, any of CLKout(0-7) or EN\_Fout from either Clock Outputs or Bits/Pins tab. In example below, CLKout0 is enabled.

|                                 | ls <u>S</u> elect Device <u>O</u> pt<br>gisters Bits/Pins | BurstMode | PLL | Clock Outputs |

|---------------------------------|-----------------------------------------------------------|-----------|-----|---------------|

|                                 | JISCEIS BICS/PINS                                         | Duistmode | FLL |               |

|                                 |                                                           |           |     |               |

| Power<br>POWERDOWN              | Program Pins                                              |           |     |               |

| EN_Fout                         | SYNC*                                                     |           |     |               |

| Bias<br>Vboost                  |                                                           |           |     |               |

| VD0030                          |                                                           |           |     |               |

| Miscellaneous                   |                                                           |           |     |               |

| DSCin_FREQ                      | 19 -                                                      |           |     |               |

| PLL_MUX                         | -                                                         |           |     |               |

| ΗZ                              | •                                                         |           |     |               |

| DIV4<br>RESET                   |                                                           |           |     |               |

| PLL_LF                          |                                                           |           |     |               |

| /CO_R3_LF                       |                                                           |           |     |               |

| 500 ohms<br>/CO_R4_LF           | •                                                         |           |     |               |

| 200 ohms                        | -                                                         |           |     |               |

| /CO_C3_C4_LF                    |                                                           |           |     |               |

| C3 = 150 pF, C4 = 110           | p 💌                                                       |           |     |               |

| Channel Outputs<br>▼ EN_CLKout0 |                                                           |           |     |               |

| EN_CENOUR                       |                                                           |           |     |               |

| EN_CLKout2<br>EN_CLKout3        |                                                           |           |     |               |

| EN_CLKout4<br>EN_CLKout5        |                                                           |           |     |               |

| EN_CLKout6                      |                                                           |           |     |               |

| EN_CLKout7<br>EN_CLKout_Global  |                                                           |           |     |               |

|                                 |                                                           |           |     |               |

|                                 |                                                           |           |     |               |

|                                 |                                                           |           |     |               |

| MM Mode: LPT                    |                                                           |           |     |               |

| Program Bits                                                                                                               |                                                                                                       |  |  |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|

| POWERDOWN                                                                                                                  | Powers the part down.                                                                                 |  |  |

| EN_Fout                                                                                                                    | Turns on the Fout pin for measuring the internal VCO.                                                 |  |  |

| OSCin_FREQ                                                                                                                 | Must be set to the OSCin frequency in MHz.                                                            |  |  |

| PLL_MUX                                                                                                                    | Programmable to many different values to support Lock Detect or aid troubleshooting.                  |  |  |

| DIV4                                                                                                                       | Shall be checked for OSCin frequencies greater than 20 MHz.                                           |  |  |

| RESET                                                                                                                      | The registers can be defaulted by checking and unchecking RESET. Software bits will not reflect this. |  |  |

| VCO_R3_LF<br>VCO_R4_LF<br>VCO_C3_C4_LF                                                                                     | Internal loop filter values, also accessible from Clock Outputs tab.                                  |  |  |

| EN_CLKout07                                                                                                                | Enable CLKout bits from CLKout0 to CLKout7. Also accessible from Clock Outputs tab.                   |  |  |

| EN_CLKout_Global Enable all clock outs. If unselected then the EN_CLKouts are overridden and the outputs are all disabled. |                                                                                                       |  |  |

# Program Pins GOE Set Global Output Enable to high or low logic level. SYNC\* Set SYNC\* pin to high or low logic level. TRIGGER Set auxiliary trigger pin to high or low logic level.

- 6. Program the part by clicking "<u>K</u>eyboard Controls"  $\rightarrow$  "Load Device" OR by shortcut "Ctrl+L".

- 7. Make measurements... After programming, the uWire cabling can be unplugged from the evaluation board to minimize noise and EMI.

- 8 SNAU040A

#### OSCin

By default the board is configured to use the on-board crystal oscillator. It is also possible to use the board with a single ended or differential reference source at the OSCin port. Below are several possible configurations for driving OSCin.

| OSCin using on board crystal oscillator [default] |                                                                     |  |  |

|---------------------------------------------------|---------------------------------------------------------------------|--|--|

| 0 ohm                                             | R8, R11, R20 [power to crystal oscillator], R109                    |  |  |

| 39 ohm                                            | R9 [can also be 0 ohm – depends on oscillator output power, 39 ohms |  |  |

|                                                   | to be a voltage divider]                                            |  |  |

| 51 ohm                                            | R15                                                                 |  |  |

| 0.1 uF                                            | C35, C36 (C5 is a 0.1 uF 0402 cap which may be moved to C36)        |  |  |

| Open                                              | C4, C5                                                              |  |  |

|                                                   | R7, R10, R12, R13, R14, R16, R17, R79, R112                         |  |  |

| Differential OSCin setup |                                                              |  |  |

|--------------------------|--------------------------------------------------------------|--|--|

| 0 ohm                    | R7, R8, R10, R13                                             |  |  |

| 100 ohm                  | R44                                                          |  |  |

| 0.1 uF                   | C5, C35 (C36 is a 0.1 uF 0402 cap which may be moved to C5)  |  |  |

| Open                     | C4, C36                                                      |  |  |

| -                        | R11, R12, R14, R15, R16, R79                                 |  |  |

|                          | R20 [remove power from crystal oscillator for noise reasons] |  |  |

| Single ended OSCin setup |                                                              |  |  |

|--------------------------|--------------------------------------------------------------|--|--|

| 0 ohm                    | R7, R8                                                       |  |  |

| 51 ohm                   | R15                                                          |  |  |

| 0.1 uF                   | C35, C36 (C5 is a 0.1 uF 0402 cap which may be moved to C36) |  |  |

| Open                     | C4, C5                                                       |  |  |

| -                        | R10, R11, R12, R13, R14, R16, R17, R79                       |  |  |

|                          | R20 [remove power from crystal oscillator for noise reasons] |  |  |

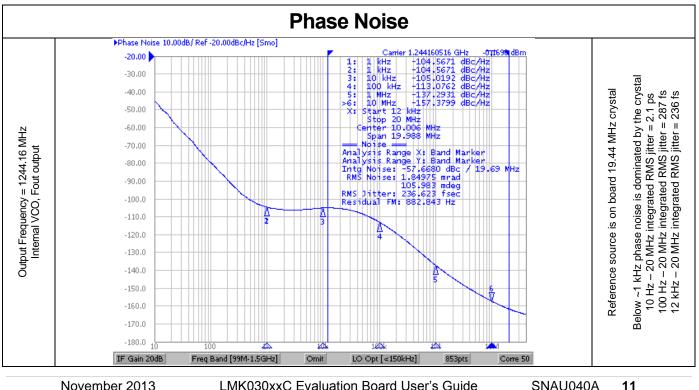

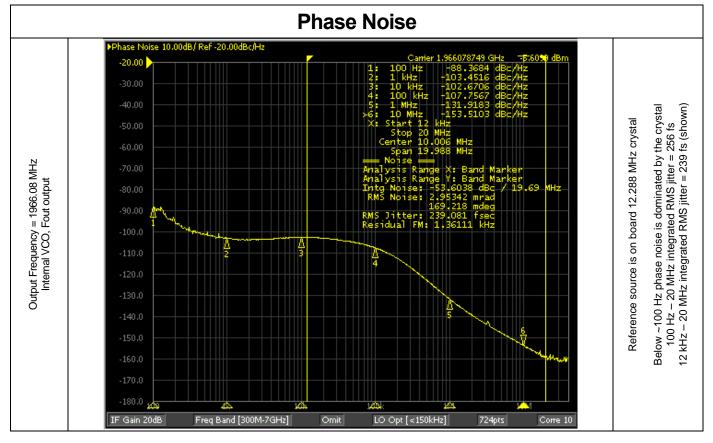

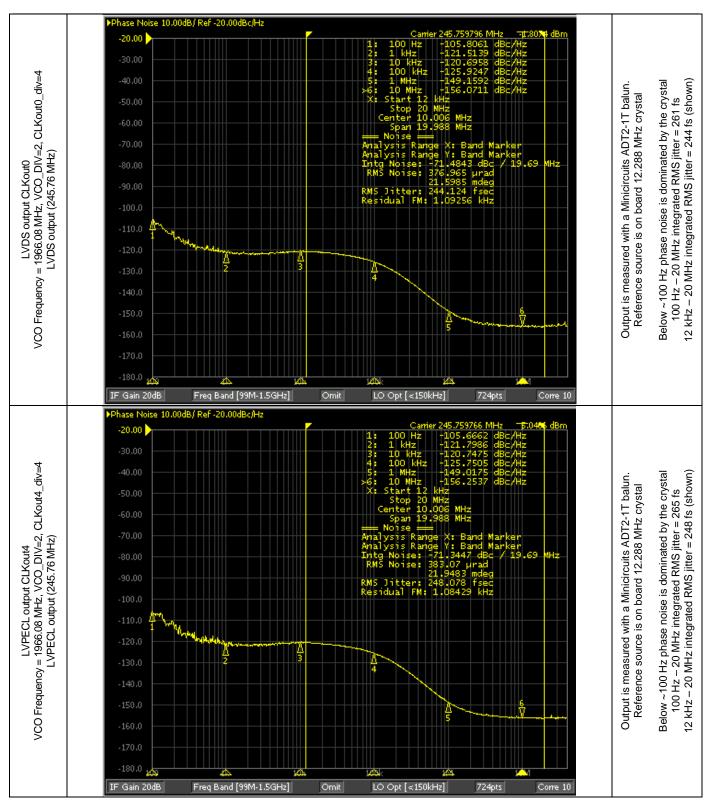

#### Fout

Fout allows direct access to the internal VCO before the clock distribution section. The EN\_Fout bit must be selected to enable Fout. A 3 dB pad is placed on R80, R81, and R82.

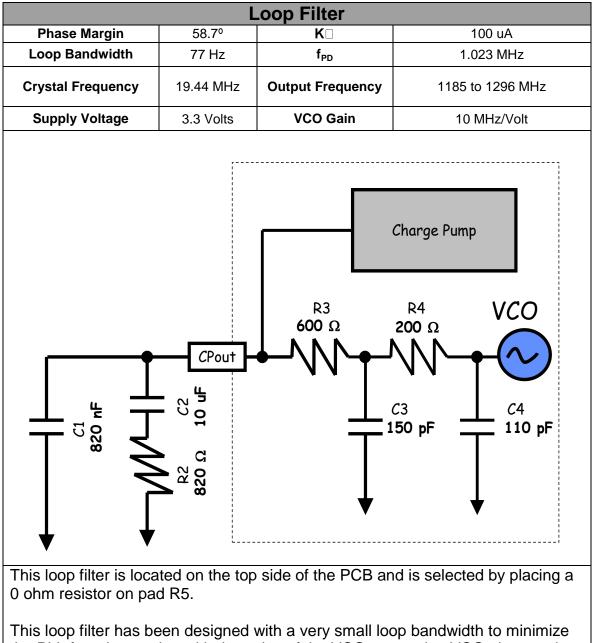

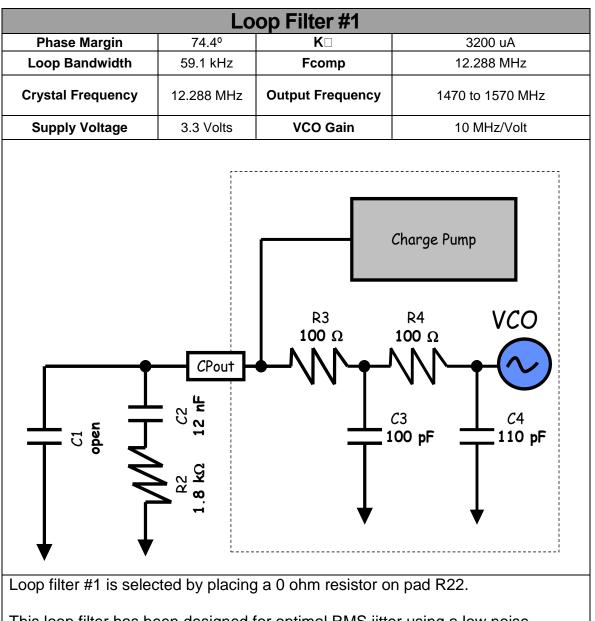

### **Loop Filter**

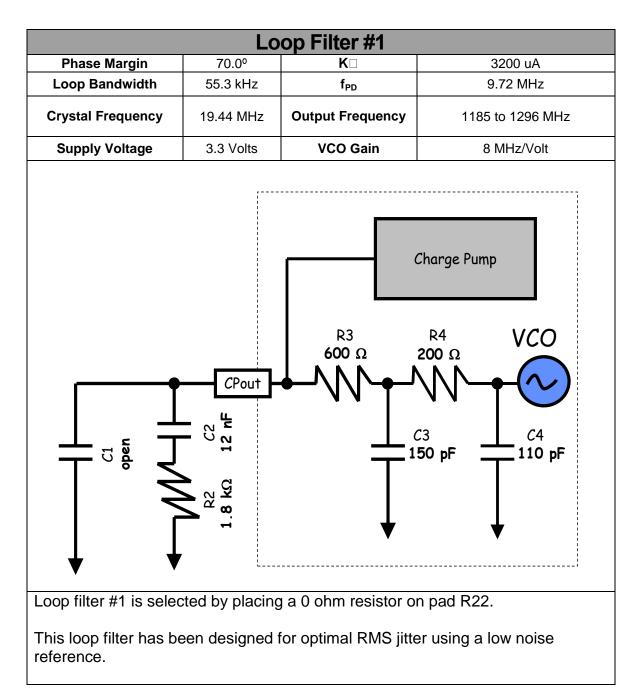

R22 and R5 form a "resistor switch" which allows either one of two different loop filters to be selected.

| Loop Filter                 | Resistor<br>Switch | Loop Filter<br>Components          | Default Loop<br>Bandwidth |

|-----------------------------|--------------------|------------------------------------|---------------------------|

| Loop Filter #1<br>[default] | R22 Shorted        | C1, C2, C2p, R2                    | 59.1 kHz                  |

| Loop Filter #2              | R5 Shorted         | C1_AUX, C2_AUX,<br>C2p_AUX, R2_AUX | 77 Hz                     |

#### Features of the board

- Either one of two loop filters can be selected by shorting either R22 or R5. More info about each loop filter can be found in the General Description and Appendix A.

- Test points for each of the uWire lines are scattered in the lower left corner of the board and include: GOE TP, DATAuWire, CLKuWire, LEuWire, SYNC TP, and LD TP.

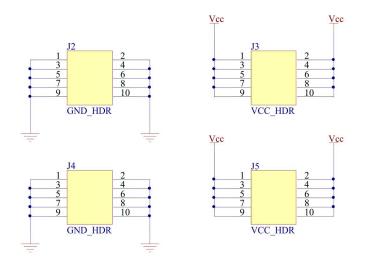

- Ground is located on the unstuffed 10 pin header on the left side of the board. •

- Ground is located on the GND\_tp2 in the upper left corner of the board and GND\_tp1 located to the right of the Vcc SMA connector.

- Ground is located on the bottom side of the board on each pad of the unstuffed 10 pin header GND\_J2.

- Vcc is located on the unstuffed 10 pin header on the upper left side of the board. .

- Vcc is located on VccPlane test point located to the right of the Vcc SMA.

- Vcc is located on the bottom side of the board on each pad of the unstuffed 10 pin header VCC J2

#### **Other Important Notes**

- When changing the OSCin frequency, the OSCin frequency register needs to be changed to match.

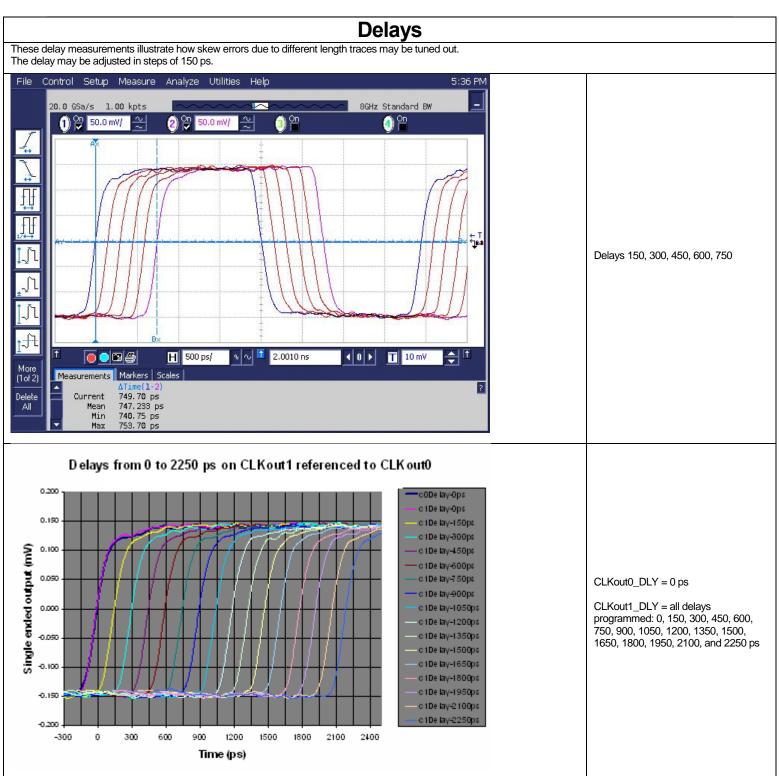

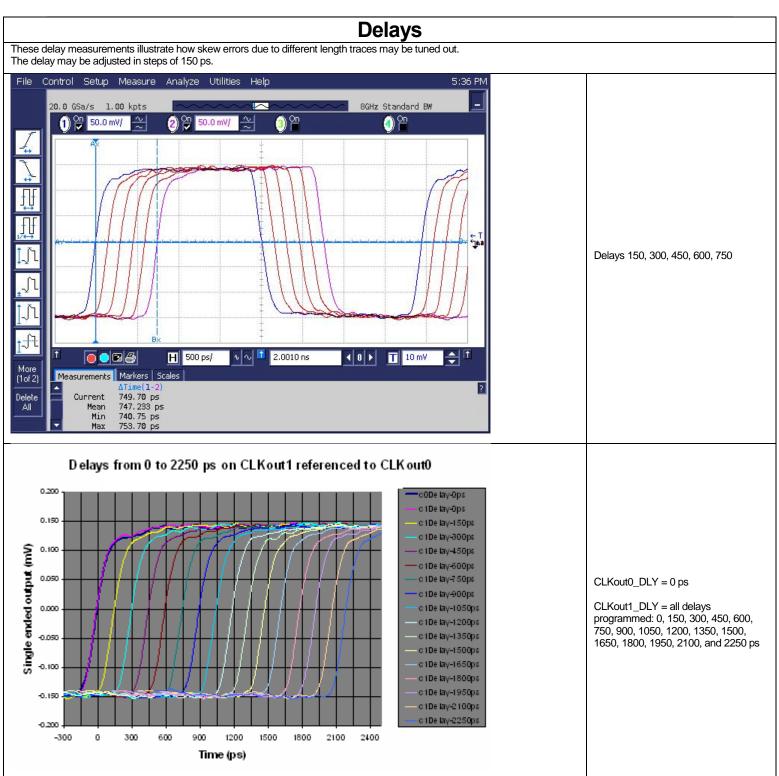

- Toggle the SYNC\* pin to synchronize the clock outputs when in divided mode.

- For both loop filters, a helper silkscreen is offset from the loop filters to help identify the components according to Texas Instruments Incorporated's traditional reference designators associated with loop filters.

#### **Evaluation Board Revision v1.0 Errata**

SYNC\* is labeled on the PCB as SYNC, however the logic of SYNC\* is still active low!

#### Results

November 2013

LMK030xxC Evaluation Board User's Guide Copyright © 2013, Texas Instruments Incorporated www.ti.com

SNAU040A

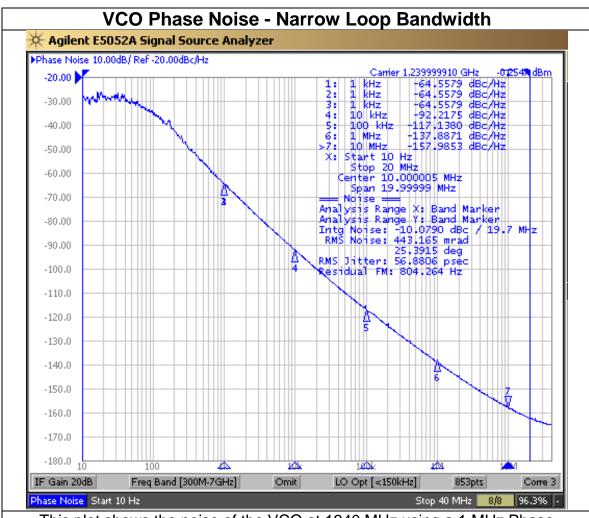

## **VCO Performance**

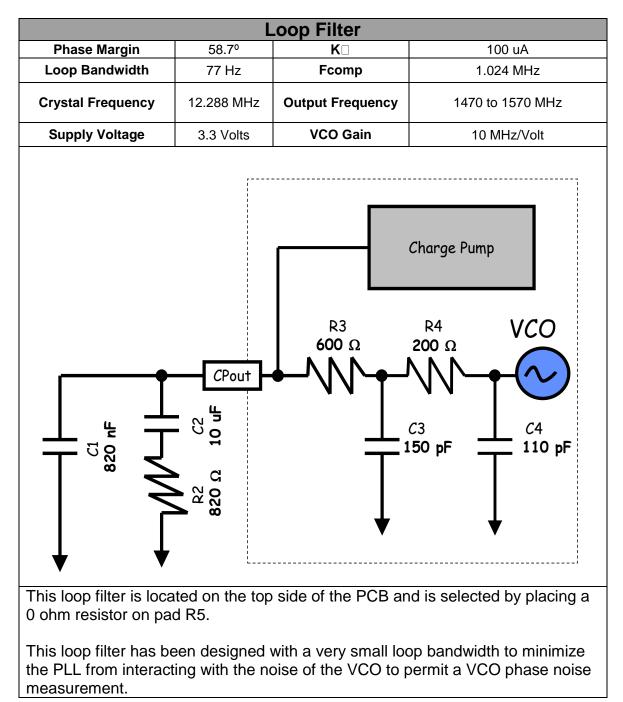

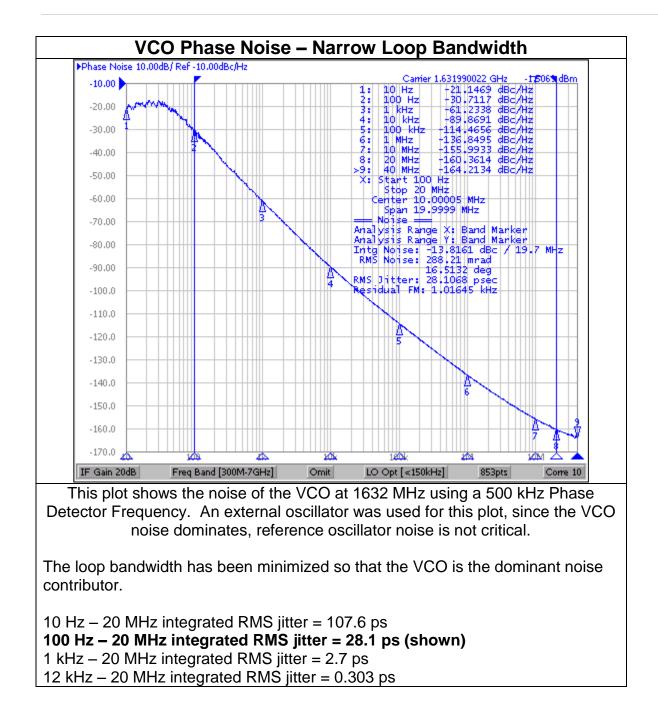

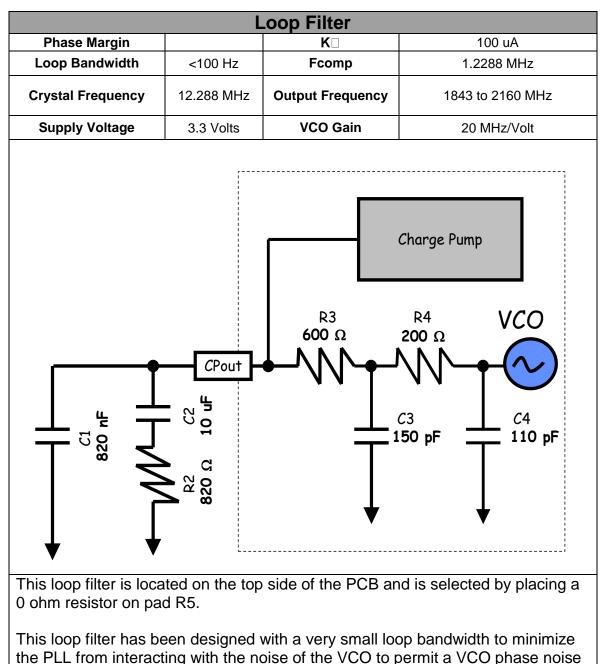

The internal VCO performance is measured by using a narrow bandwidth loop filter. By default the narrow loop bandwidth filter is stuffed as Loop Filter #2 in positions C1\_AUX, C2\_AUX, C2p\_AUX, and R2\_AUX and has a loop bandwidth of 77 Hz.

See the Loop Filter section in Board Options for more detail about switching between the two different loop filters.

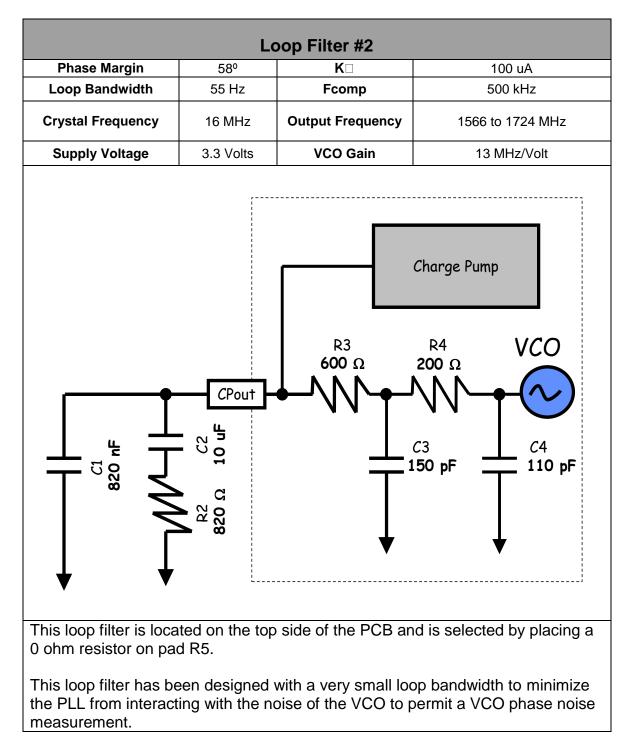

This loop filter has been designed with a very small loop bandwidth to minimize the PLL from interacting with the noise of the VCO to permit a VCO phase noise measurement.

This plot shows the noise of the VCO at 1240 MHz using a 1 MHz Phase Detector Frequency. An external oscillator was used for this plot, since the VCO noise dominates, reference oscillator noise is not critical.

The loop bandwidth has been minimized so that the VCO is the dominant noise contributor.

**10 Hz – 20 MHz integrated RMS jitter = 56.9 ps (shown)** 100 Hz – 20 MHz integrated RMS jitter = 25.0 ps 12 kHz – 20 MHz integrated RMS jitter = 0.304 ps (datasheet)

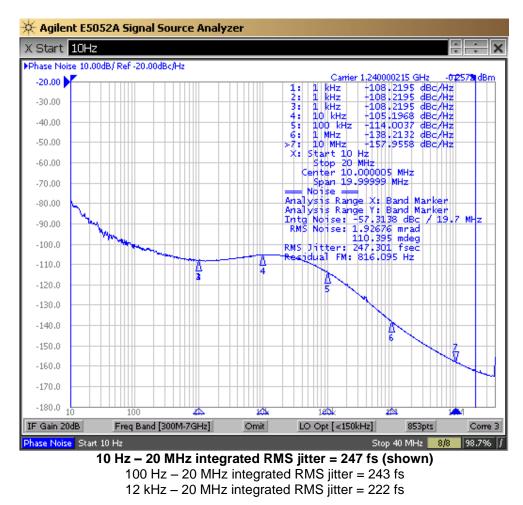

## **Impact of Reference on Phase Noise**

Inside the loop bandwidth of a PLL the phase noise is set by the quality of the reference oscillator used. For this reason it is important to select a reference oscillator suitable for the application.

#### Test Setup

Using the same loop filter as described in the General Description and by driving the OSCin frequency with an ultra low jitter 100 MHz Wetzel Crystal (501-04517D) and setting R = 10 to achieve a phase detector frequency of 10 MHz. A very low integrated RMS jitter of 247 fs is measured vs. the 2.1 ps measured in the Phase Noise section with 19.44 MHz crystal in the bandwidth of 10 Hz to 20 MHz.

#### **Conclusion**

This diagram illustrates how the phase noise inside the loop bandwidth is set by the quality of the reference oscillator used. Phase noise outside the loop bandwidth is set by the VCO noise level.

## LMK03001C Board information

This loop filter has been designed for optimal RMS jitter using a low noise reference.

#### OSCin

By default the board is configured to use the on-board crystal oscillator. It is also possible to use the board with a single ended or differential reference source at the OSCin port. Below are several possible configurations for driving OSCin.

| OSCin using on board crystal oscillator [default] |                                                                     |  |  |

|---------------------------------------------------|---------------------------------------------------------------------|--|--|

| 0 ohm                                             | R8, R11, R20 [power to crystal oscillator], R109                    |  |  |

| 39 ohm                                            | R9 [can also be 0 ohm – depends on oscillator output power, 39 ohms |  |  |

|                                                   | to be a voltage divider]                                            |  |  |

| 51 ohm                                            | R15                                                                 |  |  |

| 0.1 uF                                            | C35, C36 (C5 is a 0.1 uF 0402 cap which may be moved to C36)        |  |  |

| Open                                              | C4, C5                                                              |  |  |

|                                                   | R7, R10, R12, R13, R14, R16, R17, R79, R112                         |  |  |

| Differential OSCin setup |                                                              |  |  |

|--------------------------|--------------------------------------------------------------|--|--|

| 0 ohm                    | R7, R8, R10, R13                                             |  |  |

| 100 ohm                  | R44                                                          |  |  |

| 0.1 uF                   | C5, C35 (C36 is a 0.1 uF 0402 cap which may be moved to C5)  |  |  |

| Open                     | C4, C36                                                      |  |  |

|                          | R11, R12, R14, R15, R16, R79                                 |  |  |

|                          | R20 [remove power from crystal oscillator for noise reasons] |  |  |

| Single ended | Single ended OSCin setup                                     |  |  |

|--------------|--------------------------------------------------------------|--|--|

| 0 ohm        | R7, R8                                                       |  |  |

| 51 ohm       | R15                                                          |  |  |

| 0.1 uF       | C35, C36 (C5 is a 0.1 uF 0402 cap which may be moved to C36) |  |  |

| Open         | C4, C5                                                       |  |  |

| -            | R10, R11, R12, R13, R14, R16, R17, R79                       |  |  |

|              | R20 [remove power from crystal oscillator for noise reasons] |  |  |

#### Fout

Fout allows direct access to the internal VCO before the clock distribution section. The EN\_Fout bit must be selected to enable Fout. A 3 dB pad is placed on R80, R81, and R82.

#### Loop Filter

R22 and R5 form a "resistor switch" which allows either one of two different loop filters to be selected.

| Loop Filter                 | Resistor<br>Switch | Loop Filter<br>Components          | Default Loop<br>Bandwidth |

|-----------------------------|--------------------|------------------------------------|---------------------------|

| Loop Filter #1<br>[default] | R22 Shorted        | C1, C2, C2p, R2                    | 59.1 kHz                  |

| Loop Filter #2              | R5 Shorted         | C1_AUX, C2_AUX,<br>C2p_AUX, R2_AUX | 77 Hz                     |

#### Features of the board

- Either one of two loop filters can be selected by shorting either R22 or R5. More info about each loop filter can be found in the General Description and Appendix A.

- Test points for each of the uWire lines are scattered in the lower left corner of the board and include: GOE\_TP, DATAuWire, CLKuWire, LEuWire, SYNC\_TP, and LD\_TP.

- Ground is located on the unstuffed 10 pin header on the left side of the board.

- **Ground** is located on the GND\_tp2 in the upper left corner of the board and GND\_tp1 located to the right of the Vcc SMA connector.

- Ground is located on the bottom side of the board on each pad of the unstuffed 10 pin header GND\_J2.

- Vcc is located on the unstuffed 10 pin header on the upper left side of the board.

- Vcc is located on VccPlane test point located to the right of the Vcc SMA.

- Vcc is located on the bottom side of the board on each pad of the unstuffed 10 pin header VCC\_J2

#### **Other Important Notes**

- When changing the OSCin frequency, the OSCin frequency register needs to be changed to match.

- Toggle the SYNC\* pin to synchronize the clock outputs when in divided mode.

- For both loop filters, a helper silkscreen is offset from the loop filters to help identify the components

according to Texas Instruments Incorporated's traditional reference designators associated with loop filters.

#### **Evaluation Board Revision v1.0 Errata**

• SYNC\* is labeled on the PCB as SYNC, however the logic of SYNC\* is still active low!

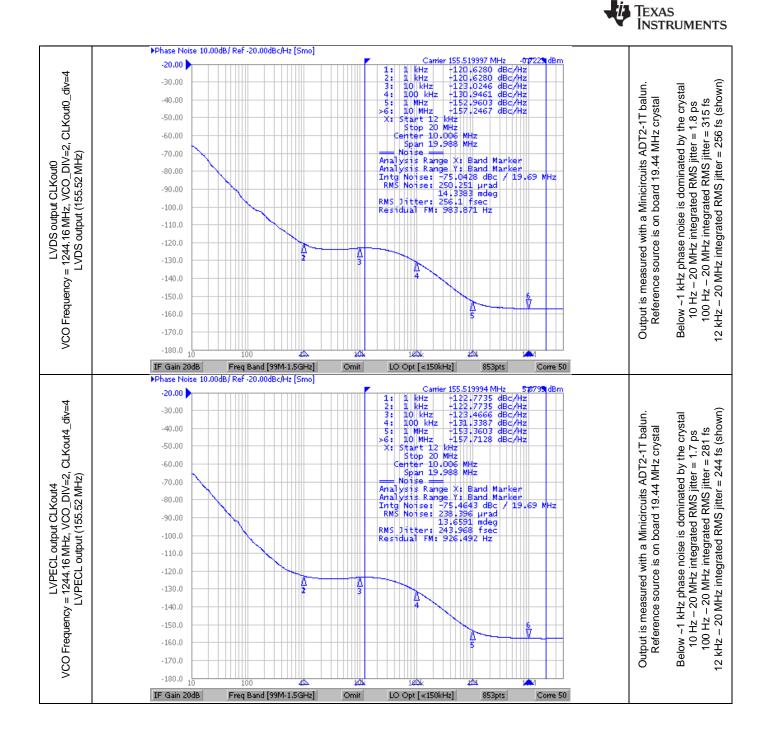

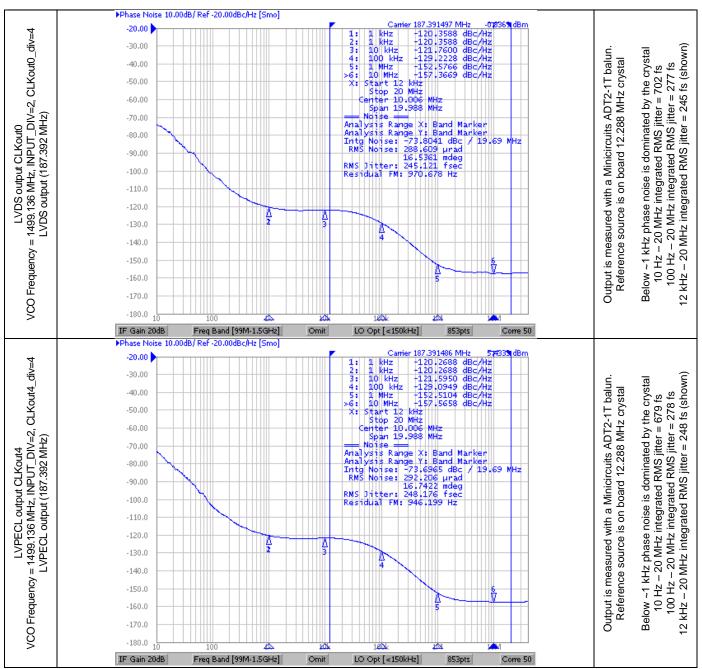

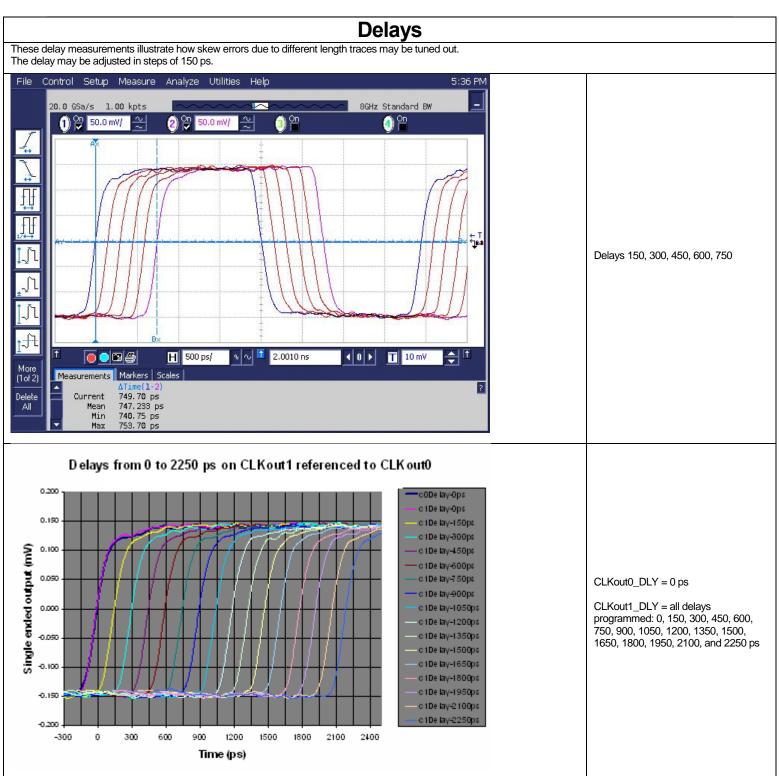

#### Results

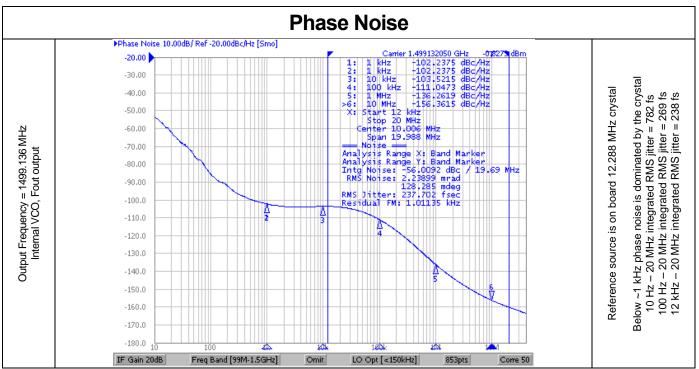

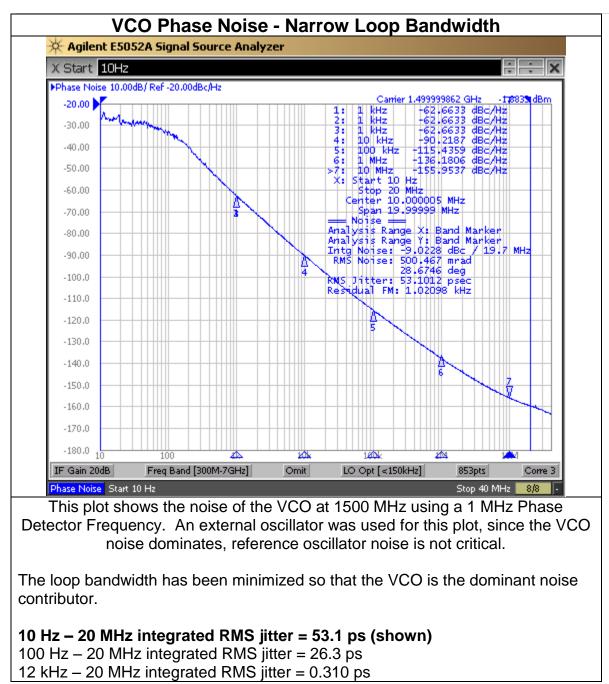

## **VCO Performance**

The internal VCO performance is measured by using a narrow bandwidth loop filter. By default the narrow loop bandwidth filter is stuffed as Loop Filter #2 in positions C1\_AUX, C2\_AUX, C2p\_AUX, and R2\_AUX and has a loop bandwidth of 77 Hz.

See the Loop Filter section in Board Options for more detail about switching between the two different loop filters.

## Impact of Reference on Phase Noise

Inside the loop bandwidth of a PLL the phase noise is set by the quality of the reference oscillator used. For this reason it is important to select a reference oscillator suitable for the application.

#### Test Setup

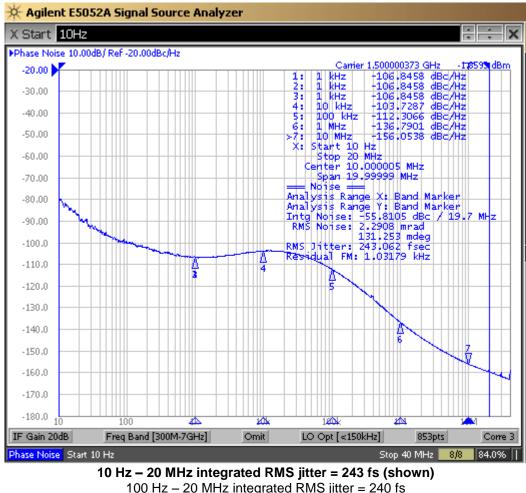

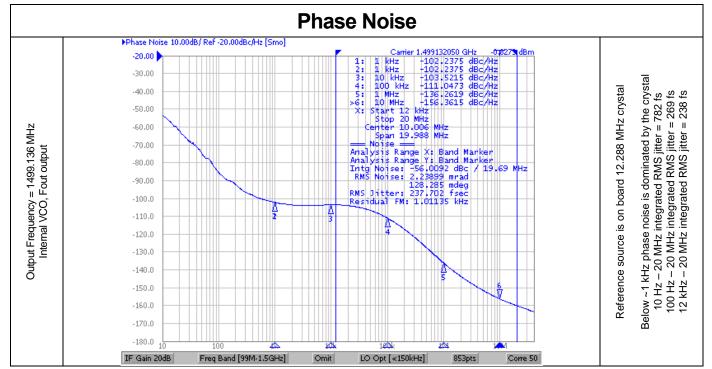

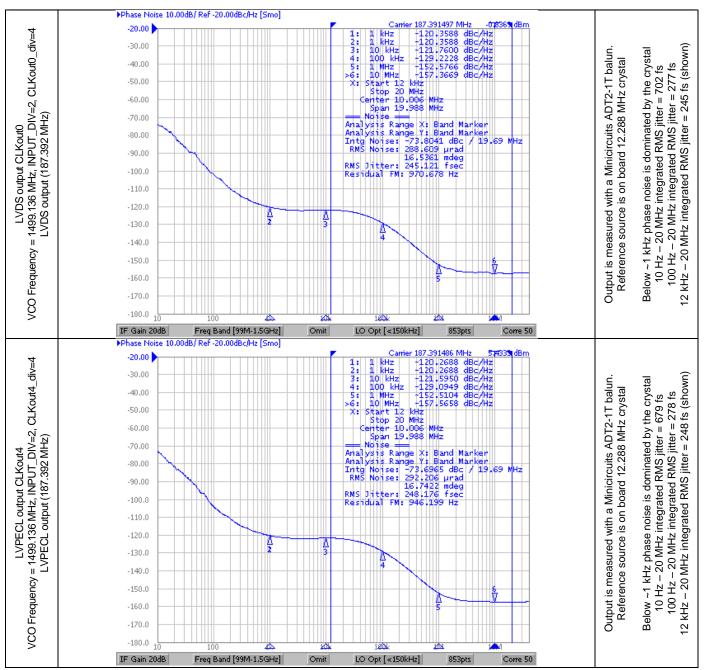

Using the same loop filter as described in the General Description and by driving the OSCin frequency with an ultra low jitter 100 MHz Wetzel Crystal (501-04517D) and setting R = 10 to achieve a phase detector frequency of 10 MHz. A very low integrated RMS jitter of 243 fs is measured vs. the 782 fs measured in the Phase Noise section with 12.288 MHz crystal in the bandwidth of 10 Hz to 20 MHz.

12 kHz - 20 MHz integrated RMS litter = 240 Is 12 kHz - 20 MHz integrated RMS jitter = 220 fs

#### **Conclusion**

This diagram illustrates how the phase noise inside the loop bandwidth is set by the quality of the reference oscillator used. Phase noise outside the loop bandwidth is set by the VCO noise level.

## LMK03002C Board information

#### OSCin

By default the board is configured to use the on-board crystal oscillator. It is also possible to use the board with a single ended or differential reference source at the OSCin port. Below are several possible configurations for driving OSCin.

| OSCin using on board crystal oscillator [default] |                                                                     |  |  |

|---------------------------------------------------|---------------------------------------------------------------------|--|--|

| 0 ohm                                             | R8, R11, R20 [power to crystal oscillator], R109                    |  |  |

| 39 ohm                                            | R9 [can also be 0 ohm – depends on oscillator output power, 39 ohms |  |  |

|                                                   | to be a voltage divider]                                            |  |  |

| 51 ohm                                            | R15                                                                 |  |  |

| 0.1 uF                                            | C35, C36 (C5 is a 0.1 uF 0402 cap which may be moved to C36)        |  |  |

| Open                                              | C4, C5                                                              |  |  |

|                                                   | R7, R10, R12, R13, R14, R16, R17, R79, R112                         |  |  |

| Differential OSCin setup |                                                              |  |  |

|--------------------------|--------------------------------------------------------------|--|--|

| 0 ohm                    | R7, R8, R10, R13                                             |  |  |

| 100 ohm                  | R17                                                          |  |  |

| 0.1 uF                   | C5, C35 (C36 is a 0.1 uF 0402 cap which may be moved to C5)  |  |  |

| Open                     | C4, C36                                                      |  |  |

|                          | R11, R12, R14, R15, R16, R79                                 |  |  |

|                          | R20 [remove power from crystal oscillator for noise reasons] |  |  |

| Single ended OSCin setup |                                                              |  |  |

|--------------------------|--------------------------------------------------------------|--|--|

| 0 ohm                    | R7, R8                                                       |  |  |

| 51 ohm                   | R15                                                          |  |  |

| 0.1 uF                   | C35, C36 (C5 is a 0.1 uF 0402 cap which may be moved to C36) |  |  |

| Open                     | C4, C5                                                       |  |  |

| -                        | R10, R11, R12, R13, R14, R16, R17, R79                       |  |  |

|                          | R20 [remove power from crystal oscillator for noise reasons] |  |  |

#### Fout

Fout allows direct access to the internal VCO before the clock distribution section. The EN\_Fout bit must be selected to enable Fout. A 3 dB pad is placed on R80, R81, and R82.

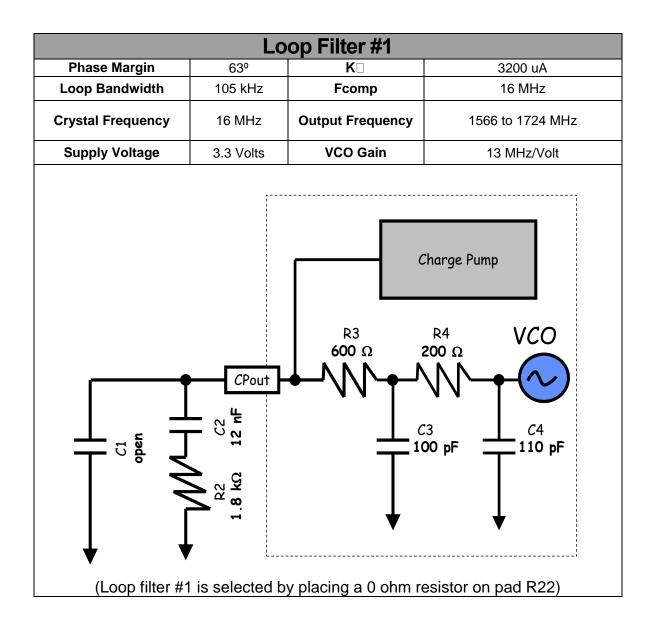

#### Loop Filter

R22 and R5 form a "resistor switch" which allows either one of two different loop filters to be selected.

| Loop Filter                 | Resistor<br>Switch | Loop Filter<br>Components          | Default Loop<br>Bandwidth |

|-----------------------------|--------------------|------------------------------------|---------------------------|

| Loop Filter #1<br>[default] | R22 Shorted        | C1, C2, C2p, R2                    | 105 kHz                   |

| Loop Filter #2              | R5 Shorted         | C1_AUX, C2_AUX,<br>C2p_AUX, R2_AUX | 55 Hz                     |

#### Features of the board

- Either one of two loop filters can be selected by shorting either R22 or R5. More info about each loop filter can be found in the General Description and Appendix A.

- Test points for each of the uWire lines are scattered in the lower left corner of the board and include: GOE\_TP, DATAuWire, CLKuWire, LEuWire, SYNC\_TP, and LD\_TP.

- Ground is located on the unstuffed 10 pin header on the left side of the board.

- **Ground** is located on the GND\_tp2 in the upper left corner of the board and GND\_tp1 located to the right of the Vcc SMA connector.

- **Ground** is located on the bottom side of the board on each pad of the unstuffed 10 pin header GND\_J2.

- Vcc is located on the unstuffed 10 pin header on the upper left side of the board.

- **Vcc** is located on VccPlane test point located to the right of the Vcc SMA.

- Vcc is located on the bottom side of the board on each pad of the unstuffed 10 pin header VCC\_J2

#### **Other Important Notes**

- When changing the OSCin frequency, the OSCin frequency register needs to be changed to match.

- Toggle the SYNC\* pin to synchronize the clock outputs when in divided mode.

- For both loop filters, a helper silkscreen is offset from the loop filters to help identify the components according to Texas Instruments Incorporated's traditional reference designators associated with loop filters.

#### Results

## VCO Performance

The internal VCO performance is measured by using a narrow bandwidth loop filter. By default the narrow loop bandwidth filter is stuffed as Loop Filter #2 in positions C1\_AUX, C2\_AUX, C2p\_AUX, and R2\_AUX and has a loop bandwidth of 55 Hz.

See the Loop Filter section in Board Options for more detail about switching between the two different loop filters.

## Impact of Reference on Phase Noise

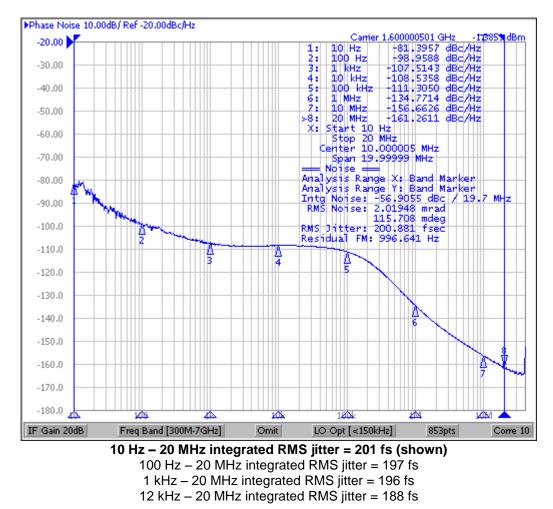

Inside the loop bandwidth of a PLL the phase noise is set by the quality of the reference oscillator used. For this reason it is important to select a reference oscillator suitable for the application.

#### Test Setup

Using the same loop filter as described in the General Description and by driving the OSCin frequency with an ultra low jitter 100 MHz Wetzel Crystal (501-04517D) and setting R = 5 to achieve a phase detector frequency of 20 MHz. A very low integrated RMS jitter of 201 fs is measured vs. the 474 fs measured in the Phase Noise section with 16 MHz crystal in the bandwidth of 10 Hz to 20 MHz.

#### **Conclusion**

This diagram illustrates how the phase noise inside the loop bandwidth is set by the quality of the reference oscillator used. Phase noise outside the loop bandwidth is set by the VCO noise level.

## LMK03033C Board information

#### OSCin

By default the board is configured to use the on-board crystal oscillator. It is also possible to use the board with a single ended or differential reference source at the OSCin port. Below are several possible configurations for driving OSCin.

| OSCin using on board crystal oscillator [default] |                                                                     |  |

|---------------------------------------------------|---------------------------------------------------------------------|--|

| 0 ohm                                             | R8, R11, R20 [power to crystal oscillator], R109                    |  |

| 39 ohm                                            | R9 [can also be 0 ohm – depends on oscillator output power, 39 ohms |  |

|                                                   | to be a voltage divider]                                            |  |

| 51 ohm                                            | R15                                                                 |  |

| 0.1 uF                                            | C35, C36 (C5 is a 0.1 uF 0402 cap which may be moved to C36)        |  |

| Open                                              | C4, C5                                                              |  |

|                                                   | R7, R10, R12, R13, R14, R16, R17, R79, R112                         |  |

| Differential OSCin setup |                  |  |

|--------------------------|------------------|--|

| 0 ohm                    | R7, R8, R10, R13 |  |

| 100 ohm | R44                                                          |  |  |

|---------|--------------------------------------------------------------|--|--|

| 0.1 uF  | C5, C35 (C36 is a 0.1 uF 0402 cap which may be moved to C5)  |  |  |

| Open    | C4, C36                                                      |  |  |

|         | R11, R12, R14, R15, R16, R79                                 |  |  |

|         | R20 [remove power from crystal oscillator for noise reasons] |  |  |

| Single ended OSCin setup |                                                              |  |  |

|--------------------------|--------------------------------------------------------------|--|--|

| 0 ohm                    | R7, R8                                                       |  |  |

| 51 ohm                   | R15                                                          |  |  |

| 0.1 uF                   | C35, C36 (C5 is a 0.1 uF 0402 cap which may be moved to C36) |  |  |

| Open                     | C4, C5                                                       |  |  |

|                          | R10, R11, R12, R13, R14, R16, R17, R79                       |  |  |

|                          | R20 [remove power from crystal oscillator for noise reasons] |  |  |

#### Fout

Fout allows direct access to the internal VCO before the clock distribution section. The EN\_Fout bit must be selected to enable Fout. A 3 dB pad is placed on R80, R81, and R82.

#### Loop Filter

R22 and R5 form a "resistor switch" which allows either one of two different loop filters to be selected.

| Loop Filter                 | Resistor<br>Switch | Loop Filter<br>Components          | Default Loop<br>Bandwidth |

|-----------------------------|--------------------|------------------------------------|---------------------------|

| Loop Filter #1<br>[default] | R22 Shorted        | C1, C2, C2p, R2                    |                           |

| Loop Filter #2              | R5 Shorted         | C1_AUX, C2_AUX,<br>C2p_AUX, R2_AUX |                           |

#### Features of the board

- Either one of two loop filters can be selected by shorting either R22 or R5. More info about each loop filter can be found in the General Description and Appendix A.

- Test points for each of the uWire lines are scattered in the lower left corner of the board and include: GOE\_TP, DATAuWire, CLKuWire, LEuWire, SYNC\_TP, and LD\_TP.

- Ground is located on the unstuffed 10 pin header on the left side of the board.

- Ground is located on the GND\_tp2 in the upper left corner of the board and GND\_tp1 located to the right

of the V<sub>cc</sub> SMA connector.

- **Ground** is located on the bottom side of the board on each pad of the unstuffed 10 pin header GND\_J2.

- V<sub>CC</sub> is located on the unstuffed 10 pin header on the upper left side of the board.

- V<sub>cc</sub> is located on V<sub>cc</sub>Plane test point located to the right of the V<sub>cc</sub> SMA.

- V<sub>cc</sub> is located on the bottom side of the board on each pad of the unstuffed 10 pin header VCC\_J2

#### **Other Important Notes**

- When changing the OSCin frequency, the OSCin frequency register needs to be changed to match.

- Toggle the SYNC\* pin to synchronize the clock outputs when in divided mode.

- For both loop filters, a helper silkscreen is offset from the loop filters to help identify the components

according to Texas Instruments Incorporated's traditional reference designators associated with loop filters.

#### **Evaluation Board Revision v1.0 Errata**

• SYNC\* is labeled on the PCB as SYNC, however the logic of SYNC\* is still active low!

#### **Results**

November 2013

LMK030xxC Evaluation Board User's Guide Copyright © 2013, Texas Instruments Incorporated www.ti.com

SNAU040A 35

TEXAS INSTRUMENTS

#### VCO Performance

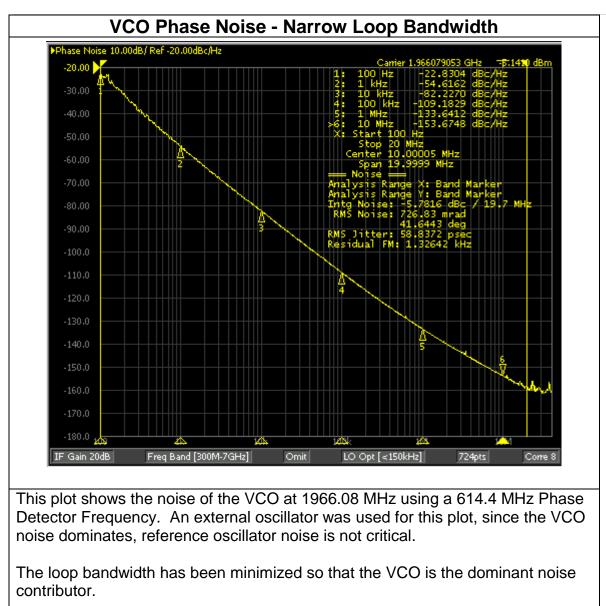

The internal VCO performance is measured by using a narrow bandwidth loop filter. By default the narrow loop bandwidth filter is stuffed as Loop Filter #2 in positions C1\_AUX, C2\_AUX, C2p\_AUX, and R2\_AUX and has a narrow loop bandwidth.

See the Loop Filter section in Board Options for more detail about switching between the two different loop filters.

measurement.

100 Hz – 20 MHz integrated RMS jitter = 58.8 ps (shown)

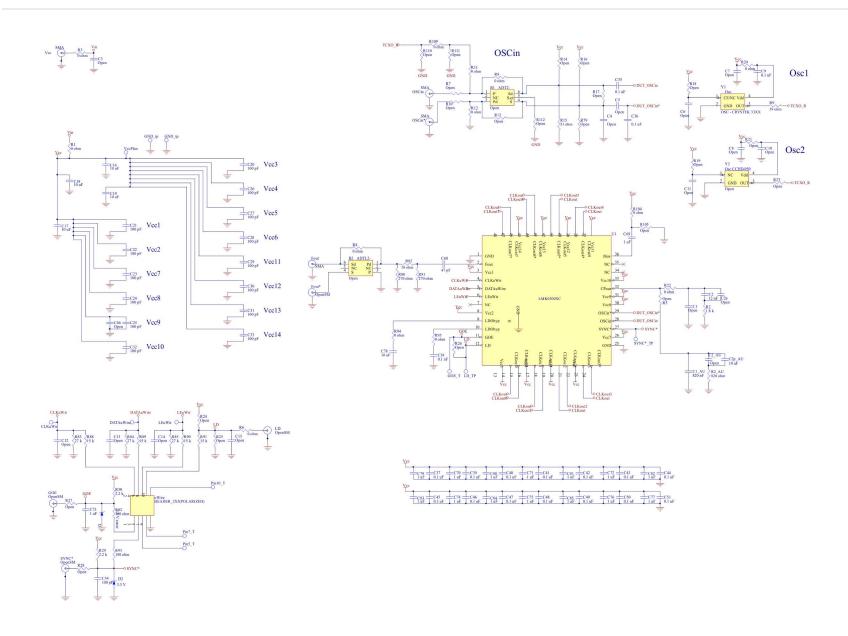

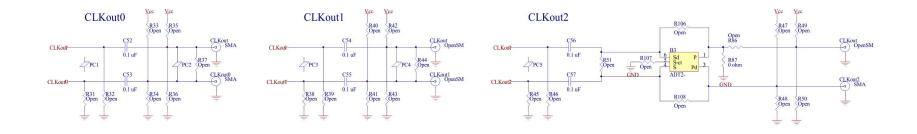

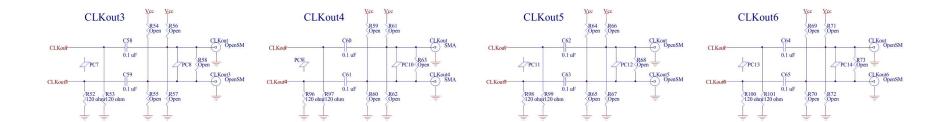

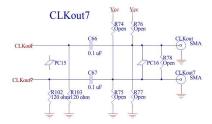

## **Appendix A: Schematics**

40 SNAU040A

SNAU040A **41**

| Part       | Manufacturer | Part Number      | Qnt | Identifier                                                                               |  |  |

|------------|--------------|------------------|-----|------------------------------------------------------------------------------------------|--|--|

| Capacitors |              |                  |     |                                                                                          |  |  |

| 47 pF      | Kemet        | C0603C470J5GAC   | 1   | C68                                                                                      |  |  |

| -          |              |                  |     | C20, C21, C22, C23, C24, C25, C26, C27, C28, C29, C30, C31,                              |  |  |

| 100 pF     | Kemet        | C0402C101J5GAC   | 14  | C32, C33                                                                                 |  |  |

| 100 pF     | Kemet        | C0603C101J5GAC   | 1   | C34                                                                                      |  |  |

| 12 nF      | Kemet        | C0603C123K1RACTU | 1   | C2                                                                                       |  |  |

| 0.1 uF     | Kemet        | C0603C104J3RAC   | 16  | C9, C37, C38, C39, C40, C41, C42, C43, C44, C45, C46, C47, C48, C49, C50, C51            |  |  |

| 0.1 uF     | Kemet        | C0402C104J4RAC   | 18  | C35, C36, C52, C53, C54, C55, C56, C57, C58, C59, C60, C61, C62, C63, C64, C65, C66, C67 |  |  |

| 820 nF     | Kemet        | C0603C824K8PAC   | 1   | C1_AUX                                                                                   |  |  |

| 1 uF       | Kemet        | C0603C105K8VAC   | 16  | C69, C70, C71, C72, C73, C74, C75, C76, C77, C79, C80, C81, C82, C83, C84, C85           |  |  |

| 10 uF      | Kemet        | C0805C106K9PAC   | 5   | C2p_AUX, C16, C17, C18, C19                                                              |  |  |

| 10 uF      | Kemet        | C0805C106K9PAC   | 1   | C78                                                                                      |  |  |

| Resistors  |              |                  |     |                                                                                          |  |  |

| 0 ohm      | Vishay       | CRCW0603000ZRT1  | 10  | R1, R3, R6, R11, R12, R20, R22, R95, R104, R109                                          |  |  |

| 0 ohm      | Yageo        | RC0805JR-070RL   | 2   | R4, R8                                                                                   |  |  |

| 0 ohm      | Vishay       | CRCW0603000ZRT1  | 2   | R87, R94                                                                                 |  |  |

| 18 ohm     | Vishay       | CRCW0603180JRT1  | 1   | R82                                                                                      |  |  |

| 39 ohm     | Vishay       | CRCW0603390JRT1  | 1   | R9                                                                                       |  |  |

| 51 ohm     | Vishay/Dale  | CRCW060351R0JNEA | 1   | R15                                                                                      |  |  |

| 120 ohm    | Vishay       | CRCW0402120RJNED | 10  | R52, R53, R96, R97, R98, R99, R100, R101, R102, R103                                     |  |  |

| 180 ohm    | Vishay       | CRCW0603181JRT1  | 2   | R92, R93                                                                                 |  |  |

| 270 ohm    | Vishay       | CRCW0603271JRT1  | 2   | R80, R81                                                                                 |  |  |

| 820 ohm    | Vishay       | CRCW0603821JRT1  | 1   | R2_AUX                                                                                   |  |  |

| 1.8 k      | Vishay/Dale  | CRCW06031K80JNEA | 1   | R2                                                                                       |  |  |

| 2.2 k      | Vishay/Dale  | CRCW06032K20JNEA | 2   | R29, R30                                                                                 |  |  |

| 15 k       | Vishay       | CRCW0603153JRT1  | 4   | R88, R89, R90, R91                                                                       |  |  |

| 27 k       | Vishay       | CRCW0603273JRT1  | 3   | R83, R84, R85                                                                            |  |  |

## Appendix B: Bill of Materials

| Other         |                  |                       |     |                                                                                                               |

|---------------|------------------|-----------------------|-----|---------------------------------------------------------------------------------------------------------------|

|               |                  | LMK03000C/LMK03001C   |     |                                                                                                               |

|               | Texas            | /                     |     |                                                                                                               |

| LMK030xxC     | Instruments      | LMK03002C/LMK03033C   | 1   | U1                                                                                                            |

| OSC - CRYSTEK |                  |                       |     |                                                                                                               |

| 33xx          | Crystek          | C3391-19.440          | 1   | Y1                                                                                                            |

| ADT2-1T       | Minicircuits     | ADT2-1T               | 1   | B3                                                                                                            |

| <b></b>       | Johnson          |                       |     | CLKout0, CLKout0*, CLKout2*, CLKout4, CLKout4*, CLKout7,                                                      |

| SMA           | Components       | 142-0701-851          | 11  | CLKout7*, Fout, OSCin, OSCin*, Vcc                                                                            |

| 3.3 V zener   | Comchip          | CZRU52C3V3            | 2   | D1, D2                                                                                                        |

|               | Printed Circuits | PCB_LMK0300x rev 1.1, |     |                                                                                                               |

| PCB_LMK0300x  | Corp             | 6-16-2007             | 1   | F1                                                                                                            |

| HEADER_2X5(P  |                  | 52004 840 9           | 4   | . Mire                                                                                                        |

| OLARIZED)     | FCI Electronics  | 52601-S10-8           | 1   |                                                                                                               |

| SPCS-8        | SPC Technology   | SPCS-8                | 4   | Standoffs in the four corners (insert from bottom)                                                            |

| Open          |                  |                       |     |                                                                                                               |

| Open          | -                | Open                  | 2   | B1, B2                                                                                                        |

|               |                  |                       |     | C1, C2_AUX, C6, C7, C8, C10, C11, C12, C13, C14, C15, R5, R7,                                                 |

| _             |                  |                       |     | R10, R14, R16, R17, R18, R19, R21, R23, R24, R25, R26, R27,                                                   |

| Open          | -                | 603                   | 32  | R28, R79, R105, R107, R110, R111, R112                                                                        |

| Open          | -                | 805                   | 1   | С2р                                                                                                           |

| Open          | -                | Open                  | 1   | C3                                                                                                            |

|               |                  |                       |     | C4, C5, R31, R32, R37, R38, R39, R44, R45, R46, R51, R58, R63,                                                |

| Open          | -                | 402                   | 16  | R68, R73, R78                                                                                                 |

|               |                  |                       |     | C86, R33, R34, R35, R36, R40, R41, R42, R43, R47, R48, R49,                                                   |

| 0             |                  |                       | 0.4 | R50, R54, R55, R56, R57, R59, R60, R61, R62, R64, R65, R66,                                                   |

| Open          | -                | 603                   | 34  | R67, R69, R70, R71, R72, R74, R75, R76, R77, R86                                                              |

| OpenSMA       |                  | Open                  | 13  | CLKout1, CLKout1*, CLKout2, CLKout3, CLKout3*, CLKout5,<br>CLKout5*, CLKout6, CLKout6*, Fout*, GOE, LD, SYNC* |

| 1             |                  | HEADER 2X5            | 2   | J2, J4                                                                                                        |

| Open<br>Open  | -                | HEADER_2X5            | 2   |                                                                                                               |

| Open<br>Open  | -                | -                     |     | J3, J5                                                                                                        |

| Open          | -                | 805                   | 3   | R13, R106, R108                                                                                               |

| Open          | -                | Open                  | 1   | Y2                                                                                                            |

# Appendix C: Build Diagram

### **Appendix D: Quick Start on EVM Communication**

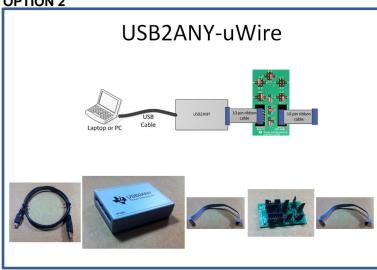

Codeloader is the software used to communicate with the EVM (Please download the latest version from TI.com - http://www.ti.com/tool/codeloader). This EVM can be controlled through the uWire interface on board. There are two options in communicating with the uWire interface from the computer.

**OPTION 1**

Open Codeloader.exe  $\rightarrow$  Click "Select Device"  $\rightarrow$  Click "Port Setup" tab  $\rightarrow$  Click "LPT" (in Communication Mode)

**OPTION 2**

#### The Adapter Board

This table describes the pins configuration on the adapter board for each EVM board (See examples below table)

| EVM                 | Jumper Bank |    |    |    |    |    |    | Code Loader Configuration |                                    |  |

|---------------------|-------------|----|----|----|----|----|----|---------------------------|------------------------------------|--|

| EVIVI               | Α           | В  | С  | D  | E  | F  | G  | Н                         |                                    |  |

| LMX2581             | A4          | B1 | C2 |    | E5 | F1 | G1 | H1                        | BUFEN (pin 1), Trigger (pin 7)     |  |

| LMX2541             | A4          |    | C3 |    | E4 | F1 | G1 | H1                        | CE (pin 1), Trigger (pin 10)       |  |

| LMK0400x            | A0          |    | C3 |    | E5 | F1 | G1 | H1                        | GOE (pin 7)                        |  |

| LMK01000            | A0          |    | C1 |    | E5 | F1 | G1 | H1                        | GOE (pin 7)                        |  |

| LMK030xx            | A0          |    | C1 |    | E5 | F1 | G1 | H1                        | SYNC (pin 7)                       |  |

| LMK02000            | A0          |    | C1 |    | E5 | F1 | G1 | H1                        | SYNC (pin 7)                       |  |

| LMK0480x            | A0          | B2 | C3 |    | E5 | F0 | G0 | H1                        | Status_CLKin1 (pin 3)              |  |

| LMK04816/4906       | A0          | B2 | C3 |    | E5 | F0 | G0 | H1                        | Status_CLKin1 (pin 3)              |  |

| LMK01801            | A0          | B4 | C5 |    | E2 | F0 | G0 | H1                        | Test (pin 3), SYNC0 (pin 10)       |  |

| LMK0482x (prelease) | A0          | B5 | C3 | D2 | E4 | F0 | G0 | H1                        | CLKin1_SEL (pin 6), Reset (pin 10) |  |

| LMX2531             | A0          |    |    |    | E5 | F2 | G1 | H2                        | Trigger (pin 1)                    |  |

| LMX2485/7           | A0          |    | C1 |    | E5 | F2 | G1 | H0                        | ENOSC (pin 7), CE (pin 10)         |  |

| LMK03200            | A0          |    |    |    | E5 | F0 | G0 | H1                        | SYNC (pin 7)                       |  |

| LMK03806            | A0          |    | C1 |    | E5 | F0 | G0 | H1                        |                                    |  |

| LMK04100            | A0          |    | C1 |    | E5 | F1 | G1 | H1                        |                                    |  |

Example adapter configuration (LMK01801)

Open Codeloader.exe  $\rightarrow$  Click "Select Device"  $\rightarrow$  Click "Port Setup" Tab  $\rightarrow$  Click "USB" (in Communication Mode)

\*Remember to also make modifications in "Pin Configuration" Section according to Table above.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                                 | Applications                  |                                   |  |  |  |

|------------------------------|---------------------------------|-------------------------------|-----------------------------------|--|--|--|

| Audio                        | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |  |  |  |

| Amplifiers                   | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |  |  |  |

| Data Converters              | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |  |  |  |

| DLP® Products                | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |  |  |  |

| DSP                          | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |  |  |  |

| Clocks and Timers            | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |  |  |  |

| Interface                    | interface.ti.com                | Medical                       | www.ti.com/medical                |  |  |  |

| Logic                        | logic.ti.com                    | Security                      | www.ti.com/security               |  |  |  |

| Power Mgmt                   | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |  |  |  |

| Microcontrollers             | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |  |  |  |

| RFID                         | www.ti-rfid.com                 |                               |                                   |  |  |  |

| OMAP Applications Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |  |  |  |

| Wireless Connectivity        | www.ti.com/wirelessconnectivity |                               |                                   |  |  |  |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2015, Texas Instruments Incorporated