# LMK04610 Evaluation Module

# **User's Guide**

Literature Number: SNAU201A January 2017–Revised February 2017

### Contents

| Quick Start Guide                     | 4<br>5 |

|---------------------------------------|--------|

|                                       | 5      |

| 1.2 Device Start-Up Sequence          |        |

|                                       | 6      |

| 2 Installing the EVM Control Software |        |

| 3 Using the EVM Control Software      | 7      |

| 3.1 Keyboard Shortcuts                | 7      |

| 3.2 TICS Pro Overview                 | 7      |

| 3.3 TICS Pro with LMK04610 GUI Loaded | 8      |

| 3.4 GUI: Generic Control              | 9      |

| 3.5 GUI: Operating Modes              | 10     |

| 3.6 GUI: OSCin and OSCout             | 11     |

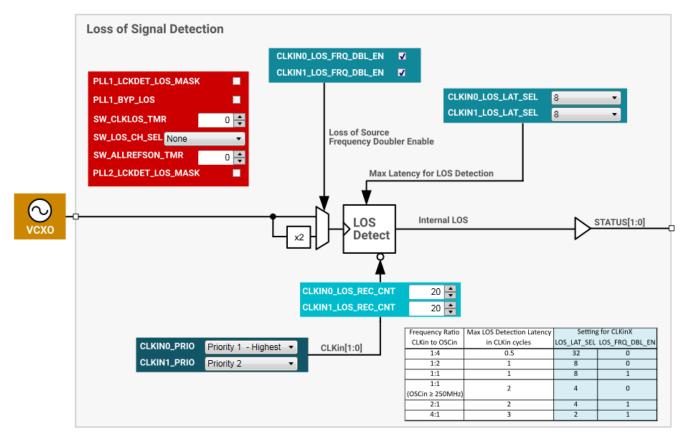

| 3.7 GUI: LOS Control                  | 11     |

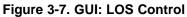

| 3.8 GUI: Holdover Control             | 12     |

| 3.9 GUI: Inputs and PLL1              | 13     |

| 3.10 GUI: PLL2                        | 14     |

| 3.11 GUI: Outputs                     | 15     |

| 3.12 GUI: EVM                         | 16     |

| 4 Configuring the Board               | 17     |

| 4.1 Configuring the Power Supply      | 17     |

| 4.1.1 Supply Plane Source Selection   | 18     |

| 4.1.2 Power Distribution              | 20     |

| 4.1.3 VCXO Supply Connection          | 21     |

| 4.2 Dip Switch Configuration          | 22     |

| 5 LMK04610 EVM Board Schematics       | 23     |

| Revision History                      | 30     |

### Overview

#### **Overview**

The LMK04610EVM features LMK04610 ultra-low noise and low-power JESD204B compliant Dual Loop Jitter Cleaner. With a power consumption of only typical 880 mW with 10 outputs running, LMK04610 supports typical 65 fs jitter (12 kHz to 20 MHz) using a low noise VCXO module. Integrated LDOs provide high PSRR that enables the use of DC-DC converters.

The dual loop architecture consists of two high-performance phase-locked loops (PLL), a low-noise crystal oscillator circuit, and a high-performance voltage controlled oscillator (VCO). The first PLL (PLL1) provides a low-noise jitter cleaner function while the second PLL (PLL2) performs the clock and SYSREF generation. When used with a very narrow loop bandwidth, PLL1 uses the superior close-in phase noise (offsets below 50 kHz) of the VCXO module or the tunable crystal to clean the input clock. The output of PLL1 is used as the clean input reference to PLL2 where it locks the integrated VCO. The loop bandwidth of PLL2 can be optimized to clean the far-out phase noise (offsets above 50 kHz) where the integrated VCO outperforms the VCXO module.

#### **Features**

- Dual Loop Architecture with typical 65 fs rms from 10 kHz to 20 MHz at 122.88-MHz output frequency

- 880 mW typical power consumption for 10 outputs at 122.88 MHz

- JEDEC JESD204B Support

- Jumper configurable supplies with onboard LDOs and DC-DC converters

- GUI platform for full access to device registers

З

Chapter 1 SNAU201A–January 2017–Revised February 2017

### **Quick Start Guide**

### 1.1 Quick Start Description

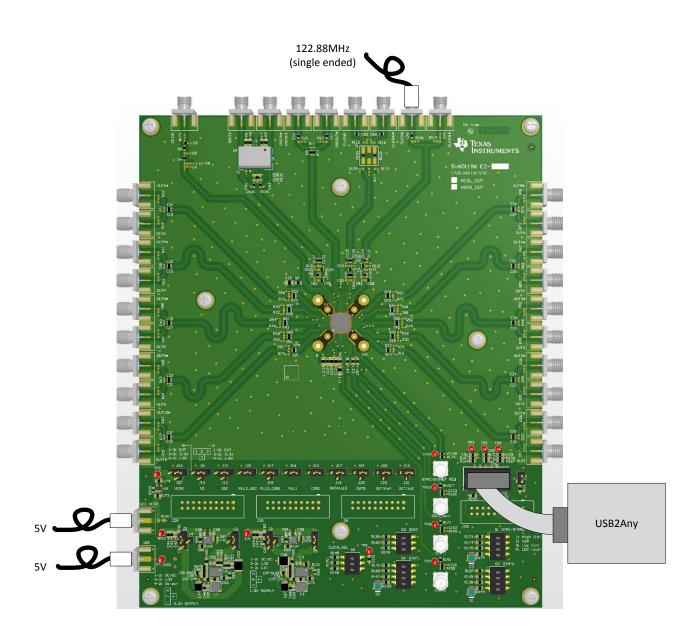

The LMK04610 EVM allows full verification of the device functionality and performance specification. To quickly set up and operate the board with basic equipment, refer to the quick start procedure below and test setup shown in Figure 1-1.

- 1. Place Dip switches S1 to S5 into default position as shown in Figure 4-6

- 2. Connect a supply voltage of 5 V to the VCC and VCC\_VCXO SMA.

- 3. Connect a reference clock to the CLKin1 port from a signal generator or other source. Use 122.88 MHz for default.

- 4. Connect the SPI header to a computer using USB2ANY.

- 5. Program the device with TICS Pro.

- (a) Start TICS Pro

- (b) Select LMK04610 from Select device → Clock Generator/Jitter Cleaner (Dual Loop) → LMK0461x Menu.

- (c) Select from USB Communications  $\rightarrow$  Interface Menu USB2ANY.

- (d) Select default mode from the *Default Configuration* Menu. For the quick start, use *Dual Loop: PLL1* BW= 40Hz REF: CLKin1 (single-ended)

- (e) Ctrl-L must be pressed at least once to load all registers. Alternatively click menu *Keyboard Controls* → *Load Device*.

- (f) Click *Device Start* button in the *Generic* page or use the *Device: DEV\_STARTUP* button from the Tool bar.

- 6. Measurements may be made at an active CLKout port through its SMA connector.

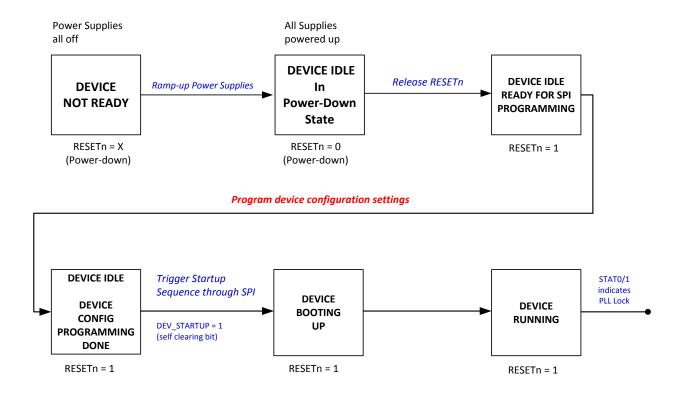

#### 1.2 Device Start-Up Sequence

Figure 1-2. Device Start-Up Sequence

### Installing the EVM Control Software

- 1. Install latest TICS Pro software from web: http://www.ti.com/tool/ticspro-sw

- 2. Start TICS Pro.

- 3. Select Device  $\rightarrow$  Clock Generator/Jitter Cleaner (Dual Loop)  $\rightarrow$  LMK0461x  $\rightarrow$  LMK04610

### Using the EVM Control Software

#### 3.1 Keyboard Shortcuts

CTRL + L => write all registers

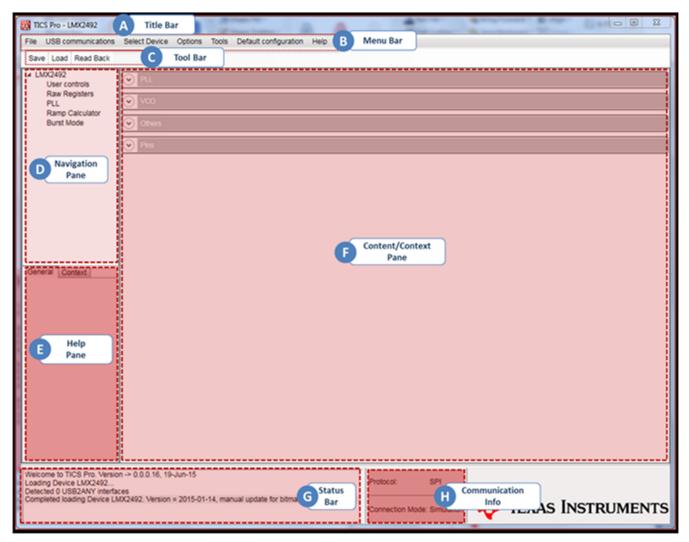

#### 3.2 TICS Pro Overview

Figure 3-1. TICS Pro Overview

Figure 3-2. TICS Pro User Manual

Further information at Help → TICS Pro User Manual

#### 3.3 TICS Pro with LMK04610 GUI Loaded

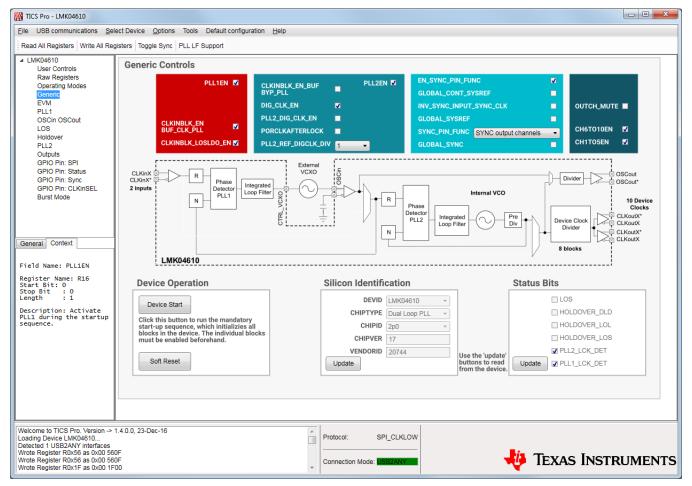

Figure 3-3. TICS Pro With LMK04610 GUI Loaded

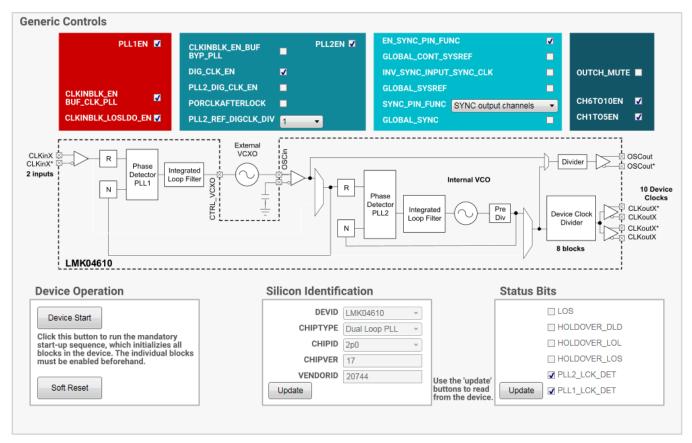

#### 3.4 GUI: Generic Control

Figure 3-4. GUI: Generic Control

GUI: Operating Modes

www.ti.com

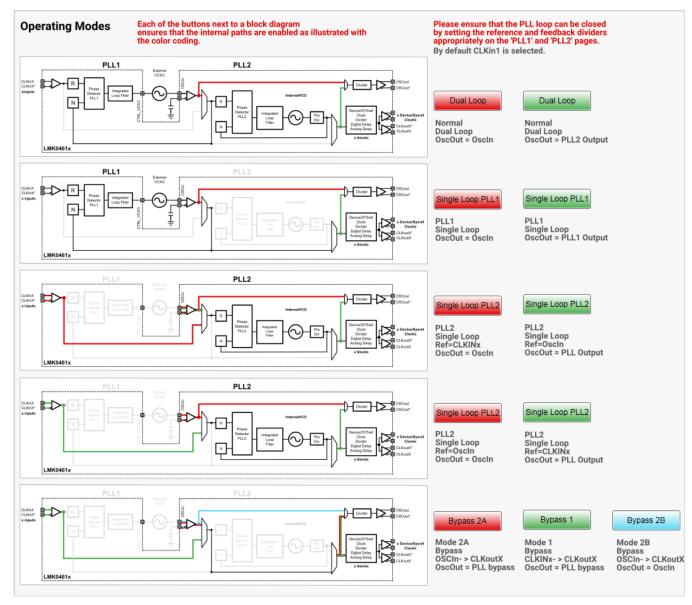

#### 3.5 GUI: Operating Modes

Figure 3-5. GUI: Operating Modes

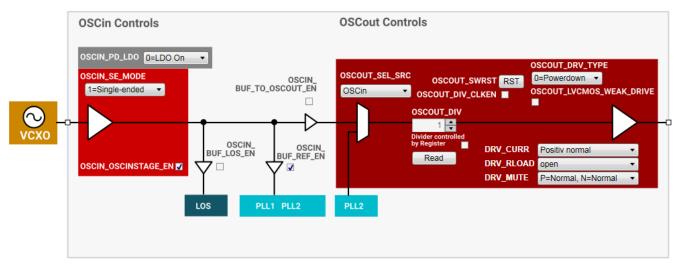

#### 3.6 GUI: OSCin and OSCout

Figure 3-6. GUI: OSCin and OSCout

#### 3.7 GUI: LOS Control

GUI: Holdover Control

www.ti.com

#### 3.8 GUI: Holdover Control

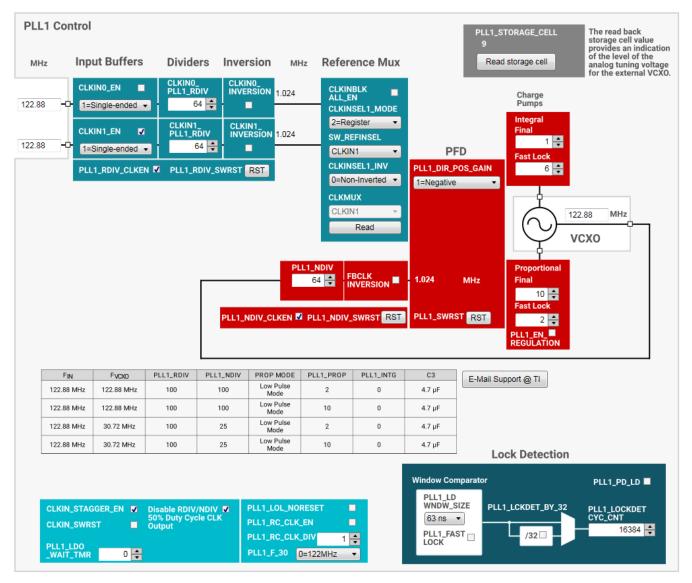

#### 3.9 GUI: Inputs and PLL1

Figure 3-9. GUI: Inputs and PLL1

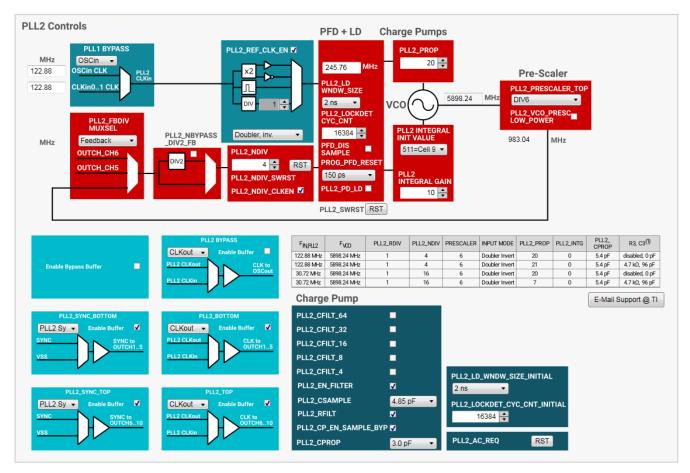

#### 3.10 GUI: PLL2

Figure 3-10. GUI: PLL2

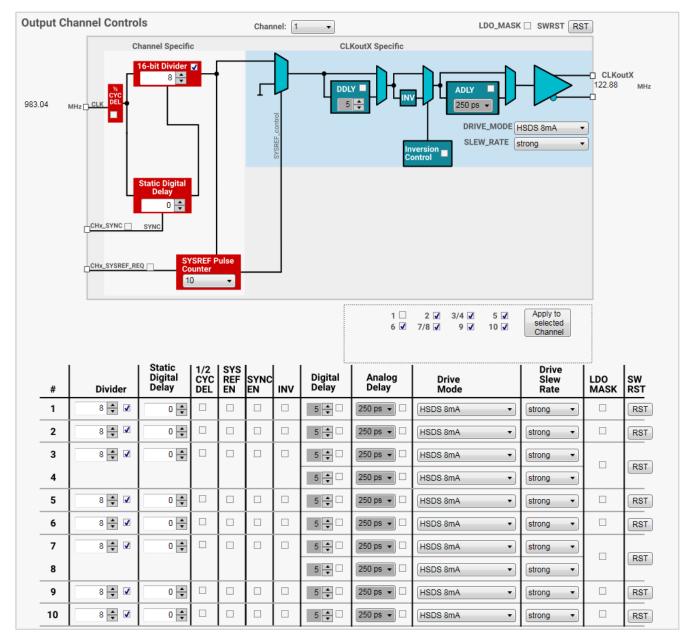

#### 3.11 GUI: Outputs

Figure 3-11. GUI: Outputs

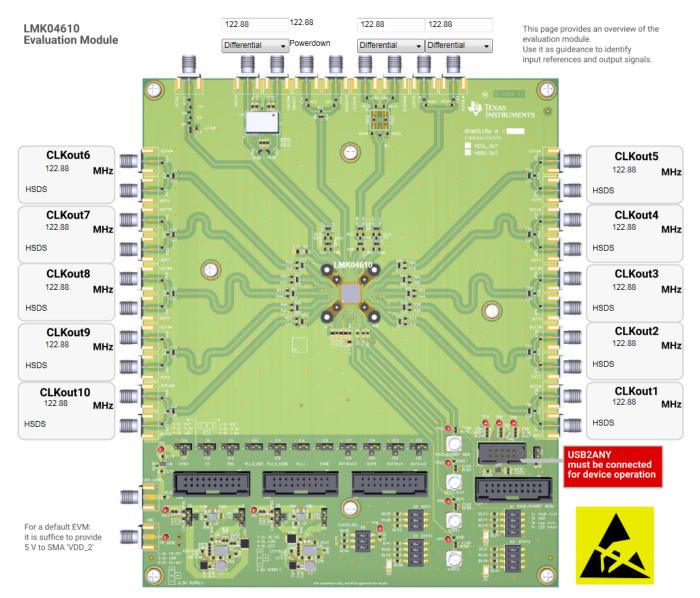

#### 3.12 GUI: EVM

Figure 3-12. GUI: EVM Overview

## Configuring the Board

The LMK04610 is a programmable clock jitter cleaner with many options. The EVM was designed with maximum flexibility so engineers can configure the EVM for operation at its desired mode.

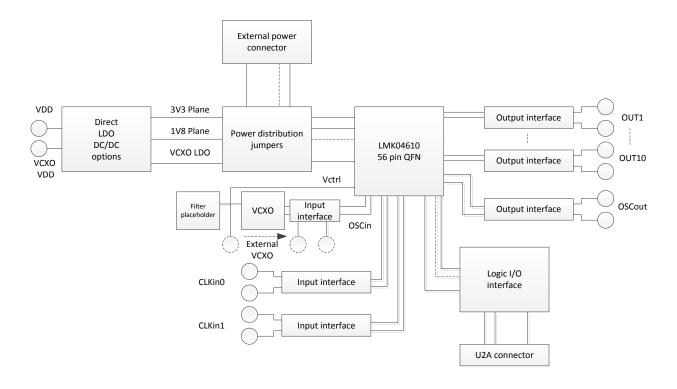

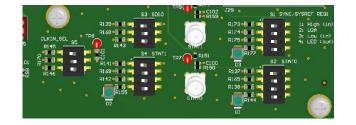

Figure 4-1 shows the connection concept of the LMK04610EVM.

Figure 4-1. EVM Connection Concept

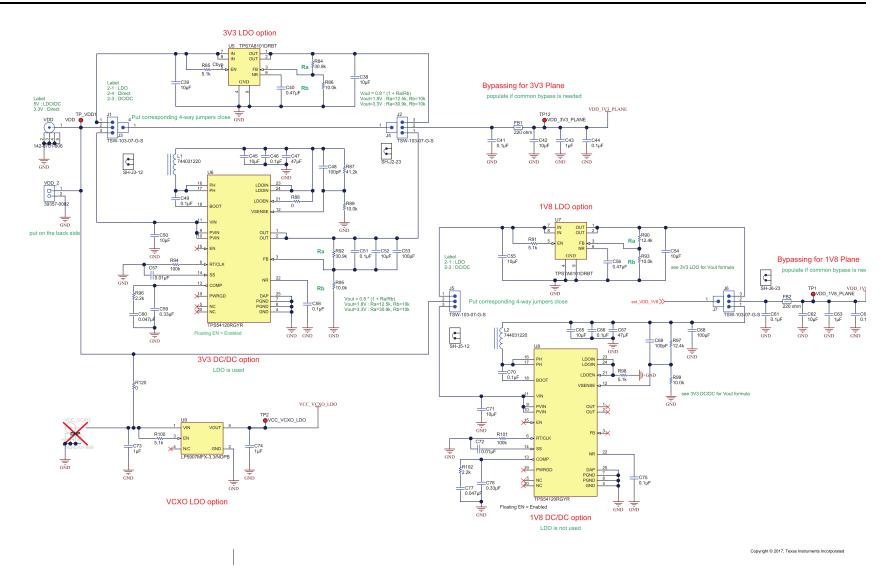

#### 4.1 Configuring the Power Supply

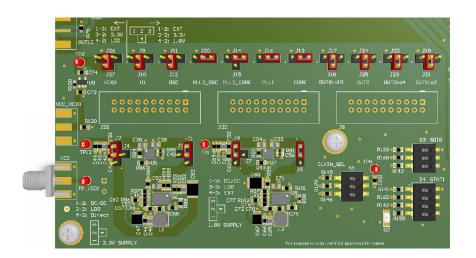

Figure 4-2 shows the default jumper setting to supply 3.3 V and 1.8 V to the device.

The VDD SMA or VDD\_2 terminal block (on the back side of the EVM) is connected to J1 and J5 to provide the external supply voltage for the 3.3-V and 1.8-V supply plane. Connect 5-V external power supply if LDO or DCDC converter is used.

The VDD\_VCXO SMA is directly connected to the VCXO LDO.

Configuring the Power Supply

Figure 4-2. Default Power Supply Connection

#### 4.1.1 Supply Plane Source Selection

Jumper J1 and J2 selects the Power connection for the 3.3-V plane from either the LDO, a DC-DC switcher, or direct from VDD SMA Connector. A 5-V supply needs to be connected to VDD SMA Connector.

| 3.3-V LDO<br>(TPS7A8101)  | J1: 1-2<br>J2: 2-3 | 10   12   C38   C33   1     10   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12   12<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.3-V DC-DC<br>(TPS54120) | J1: 2-3<br>J2: 1-2 | Image: Section of the section of th |

Table 4-1. 3.3-V Supply Plane Connections

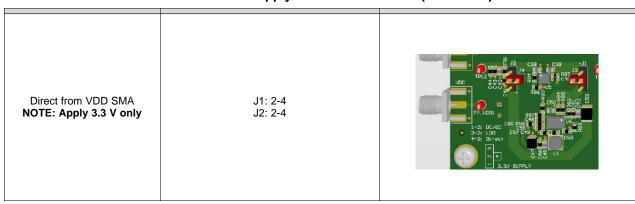

#### Table 4-1. 3.3-V Supply Plane Connections (continued)

Jumper J6 and J5 selects the Power connection for the 1.8-V plane from either a LDO or a DC-DC switcher.

| 1.8-V LDO<br>(TPS7A8101) | J5: 1-2<br>J6: 2-3 | 130<br>130<br>131<br>132<br>133<br>134<br>135<br>135<br>135<br>135<br>135<br>135<br>135<br>135 |

|--------------------------|--------------------|------------------------------------------------------------------------------------------------|

| 1.8-V DC-DC              | J5: 2-3            | J30                                                                                            |

| (TPS54120)               | J6: 1-2            | P1 P2                                                      |

#### Table 4-2. 1.8-V Supply Plane Connections

Configuring the Power Supply

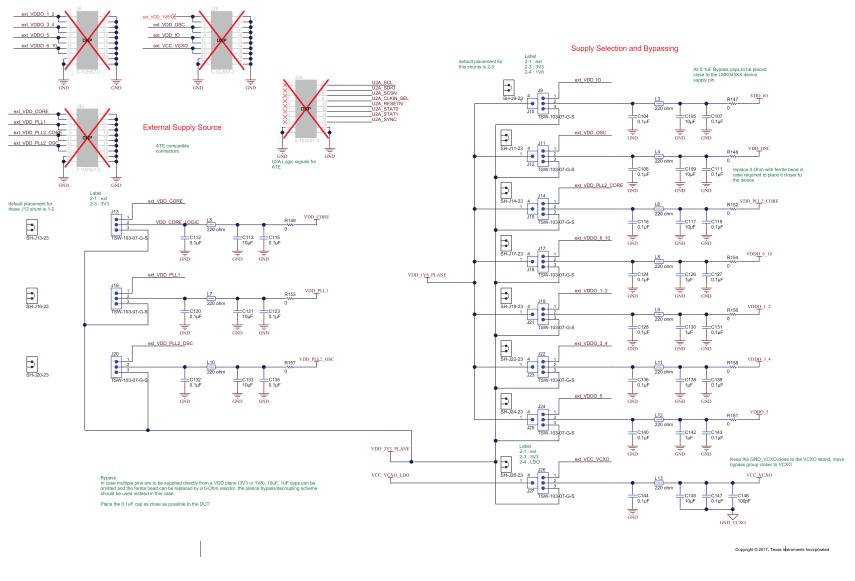

#### 4.1.2 Power Distribution

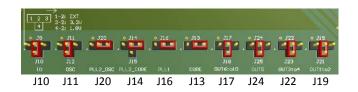

The power distribution jumpers (J9, J11, J13, J14, J16, J17, J19, J20, J22, and J24) are connected to the 3.3-V and 1.8-V supply planes and individual external connections.

#### Figure 4-3. Power Distribution Jumpers

J13 (VDD\_CORE), J16 (VDD\_PLL1), and J20 (VDD\_PLL2\_OSC) selects between 3.3-V supply plane and external supply connection as shown in Figure 4-4.

#### Figure 4-4. J13, J16, J20 Connection Description

J9 (VDD\_IO), J11 (VDD\_OSC), J14 (VDD\_PLL2\_CORE), J17 (VDD\_OUT6to10), J19 (VDD\_OUT1to2), J22 (VDD\_OUT3to4), and J24 (VDD\_OUT5) selects between 3.3-V supply plane, 1.8-V supply plane and external supply connection as shown in Figure 4-5.

#### Figure 4-5. J9, J11, J14, J17, J19, J22, J24 Connection Description

**NOTE:** External supply connection is available on Jumpers J8, J28, and J30.

Configuring the Power Supply

#### www.ti.com

#### 4.1.3 VCXO Supply Connection

The VCXO has its own LDO (LM5907MFX-3.3). A 5-V supply needs to be connected to VCC\_VCXO SMA. Jumper J26 selects between this LDO, the LMK04610 3.3-V supply plane and external supply connection as shown inTable 4-3.

| 3.3-V LDO<br>(LM5907MFX-3.3)                                          | J26: 2-4 | # C35   # C35   # C35   # C32   # C32   # C32   # C23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.3-V supply plane<br>(TPS7A8101 or TPS54120)                         | J26: 2-3 | Image: Control of the control of th |

| External supply connection on<br>Jumper J28<br>NOTE: Apply 3.3 V only | J26: 1-2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### Table 4-3. VCXO Supply Connections

#### 4.2 Dip Switch Configuration

Default configuration of Dip Switches is shown in Table 4-4 or Figure 4-6.

| SWITCH POSITION | S1 SYNC/SYSREF<br>REQ | S2 STAT0 | S3 SDIO | S4 STAT1 | S5 CLKin_SEL |

|-----------------|-----------------------|----------|---------|----------|--------------|

| 1 – High        | OFF                   | OFF      | OFF     | OFF      | OFF          |

| 2 – U2A         | ON                    | ON       | ON      | ON       | ON           |

| 3 – Low         | OFF                   | OFF      | OFF     | OFF      | OFF          |

| 4 – LED         | ON                    | ON       | n/a     | ON       | n/a          |

Figure 4-6. Default Dip Switch Setting

Chapter 5 SNAU201A–January 2017–Revised February 2017

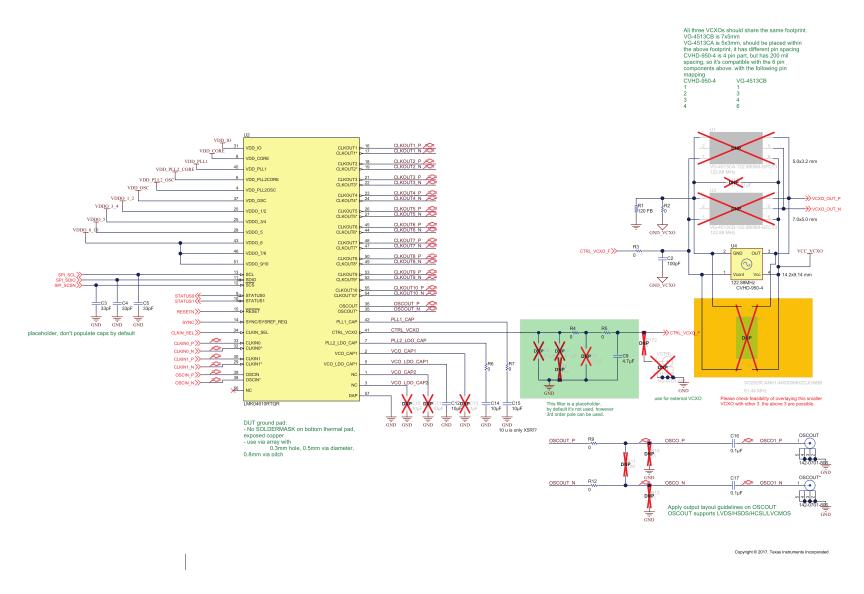

## LMK04610 EVM Board Schematics

#### Figure 5-1. Power Supply Connection

Figure 5-3. LMK04610 Main

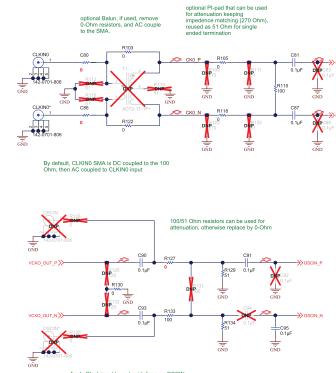

Apply Clock input layout guidelines on OSCIN By default VCXO path (single ended) is AC coupled to OCSIN\_P

By default, CLKIN1 SMA is DC coupled to the 51 Ohm, then AC coupled to CLKIN1 input CLKIN1 is single-ended by default (negative input is connected to 0.1uA)

CLOCK INPUT CLKING.CLKIN1 LAYOUT REQUIREMENTS: \*\*\* CONTROLLED IMPEDANCE \*\*\*\* Rotate as 50-onit (+5% taj Jonend-impedance single-ended PF traces from SMA center pad, and use 50-ohm Zo via structures. \*\*\* LENGTH / SKEW MATCHING \*\*\* \*\*\* LENGTH / SKEW MATCHING \*\*\* \*\*\* LENGTH / SKEW MATCHING \*\*\* \*\*\* Test in Not requirement to match inter-pair skew testeen CLKING path and CLKINF path. \*\*\* Test in Not requirement to match inter-pair skew testeen CLKING path and CLKINF path. \*\*\* Test in Not requirement to match inter-pair skew testeen CLKING path and CLKINF path. \*\*\* Test in SING INFORMATION \*\*\* \*\*\* THELIDING ISOLATION \*\*\* \*\*\* SHELIDING ISOLATION \*\*\* \*\*\* SHELIDING ISOLATION \*\*\* \*\*\* SHELIDING routing layers skind have detarance to not affect controlled impedance of RF traces. \*\*\* Cancerd Rodo of noting layers and tab have detarance of note that 25 with from RF traces. \*\*\* Cancerd Rodo of noting layers isolation have detarance of note that 25 with from RF traces. \*\*\*\* Aveid crossing Digital signalifetum paths with REF input signalifetum paths; if unavoidable, cross at a 90 deg, angle

Copyright © 2017, Texas Instruments Incorporated

Figure 5-4. Inputs

KIND N

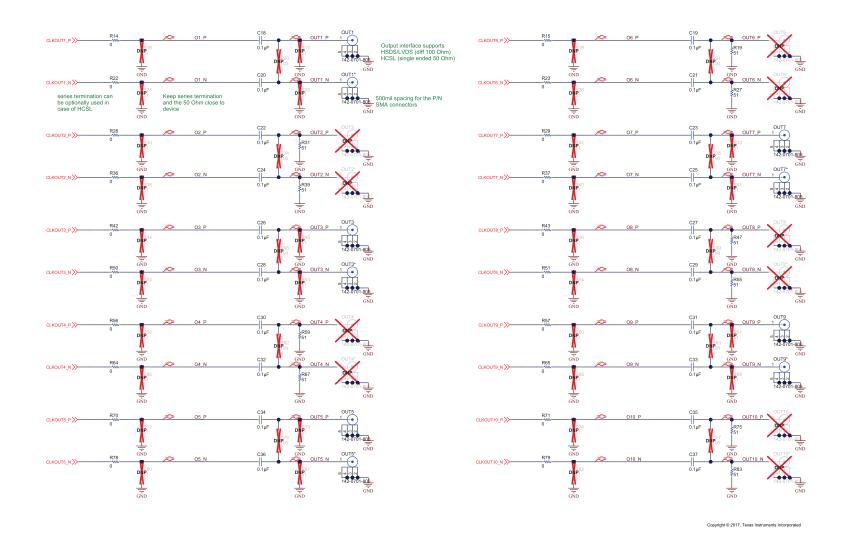

Figure 5-5. Outputs

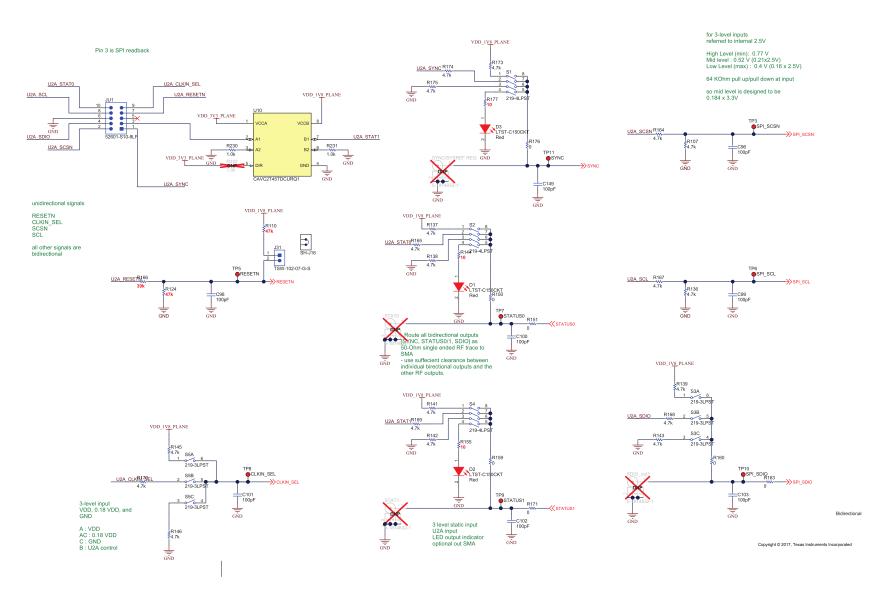

Figure 5-6. Logic/GPIO

**Revision History**

www.ti.com

#### **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | Changes from Original (January 2017) to A Revision             |     |  |

|----|----------------------------------------------------------------|-----|--|

| •  | Updated the text in the Overview section                       | . 3 |  |

| •  | Changed typical rms value from: 60 fs to: 65 fs                | . 3 |  |

| •  | Changed typical power consumption value from: 0.9 W to: 880 mW | . 3 |  |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated