# AN-1539 LM3280 Evaluation Board

## 1 Introduction

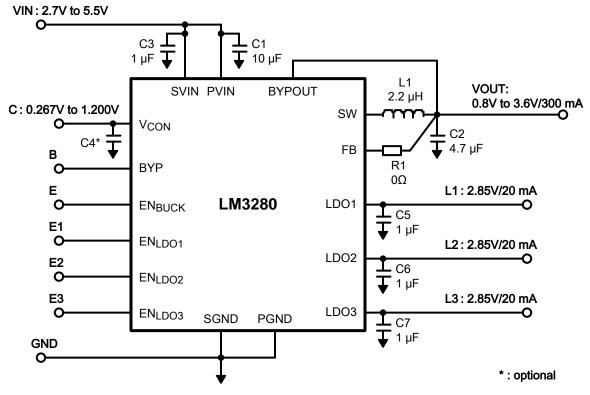

The LM3280 evaluation board, Figure 1, is designed to demonstrate the capability of the LM3280 power management device, which incorporates a step down DC-DC (buck) converter and three LDOs. This application report contains information about the evaluation board. For further information on buck converter topology, device electrical characteristics, and component selection, please refer to *LM3280 Adjustable Step-Down DC-DC Converter and 3 LDOs for RF Power Management* (SNOSAU4).

## 2 General Description

The buck converter coverts high input voltages to lower output voltages with high efficiency through an inductor-based switching topology. It has three operating modes. Fixed-frequency (2MHz) PWM mode operation offers regulated output at high efficiency. Bypass mode operation uses an internal FET switch to connect the input supply voltage directly to the load. Shutdown mode turns the device off and reduces the input supply consumption. The mode selection between PWM and Bypass can be fixed by the BYP pin setting.

The LDO provides a nominal output voltage of 2.85V with a maximum load current capability of 20mA. It has a separate enable pin for each LDO.

#### Figure 1. Evaluation Board Schematic

All trademarks are the property of their respective owners.

# **3** Operating Conditions

The evaluation board operates under the following recommended conditions:

| V <sub>IN</sub> :                       | 2.7V to 5.5V    |                              |

|-----------------------------------------|-----------------|------------------------------|

| V <sub>CON</sub> :                      | 0.267V to 1.20V |                              |

| V <sub>OUT</sub> equation :             |                 | $V_{OUT} = 3 \times V_{CON}$ |

| I <sub>OUT_BUCK</sub>                   | @PWM mode :     | 0mA to 300mA                 |

|                                         | @Bypass mode :  | 0mA to 500mA                 |

| I <sub>OUT_LDO</sub> :                  |                 | 0mA to 20mA                  |

| Ambient temperature (T <sub>A</sub> ) : |                 | -30°C to +85°C               |

# 4 Powering Up

The  $EN_{BUCK}$  pin should be set low to turn off the LM3280 during power-up and under voltage conditions when the  $V_{IN}$  is less than the 2.7V minimum operating voltage.

The LDO can be enabled only after the buck converter is activated. Single LDO must be turned on at the same time.

## 5 BOM for Common Configurations

| Designator | Manufacture | Model          | Description                                                                                                                       |  |

|------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| C1         | TDK         | C2012X5R0J106M | 10µF, 6.3V, 0805 (2012)                                                                                                           |  |

| C2         | TDK         | C1608X5R0J475M | 4.7µF, 6.3V, 0603 (1608)                                                                                                          |  |

| C3         | TDK         | C1608JB1C105K  | 1.0µF, 16V , 0603 (1608)                                                                                                          |  |

| C4         |             |                | 0.1 $\mu$ F, 6.3V, 0603 (1608),<br>* optional: filter for V <sub>CON</sub> . C4 is recommended for a better<br>noise performance. |  |

| C5         | TDK         | C1608JB1C105K  | 1.0μF, 16V , 0603 (1608)                                                                                                          |  |

| C6         | TDK         | C1608JB1C105K  | 1.0µF, 16V , 0603 (1608)                                                                                                          |  |

| C7         | TDK         | C1608JB1C105K  | 1.0µF, 16V , 0603 (1608)                                                                                                          |  |

| L1         | Coilcraft   | DO3314-222MLC  | 2.2 μH, Irms = 1.3A, Rdc = 0.2Ω, 3.5×3.5×1.4 mm                                                                                   |  |

| R1         |             |                | 0Ω, 0603 (1608)                                                                                                                   |  |

| VIN        | Keystone    | 1502-1         | test terminal                                                                                                                     |  |

| VOUT       | Keystone    | 1502-1         | test terminal                                                                                                                     |  |

| GND        | Keystone    | 1502-1         | test terminal                                                                                                                     |  |

# 6 Component Selection Considerations

#### Inductor:

- 1. A 2.2µH inductor with a saturation current rating of over 940mA is recommended.

- 2. The inductor resistance should be less than  $0.2\Omega$  for better efficiency.

- 3. The acceptable inductance tolerance is  $1.55\mu$ H to  $3.1\mu$ H over the operating temperature range.

#### Capacitor:

- 1. The DC bias and temperature characteristics of the capacitor must be considered.

- 2. The lower limit of acceptable C2 capacitance for stable performance is  $3\mu$ F.

- 3. The lower limit of acceptable LDO caps, C5, C6, and C7, is 0.5µF.

- A 10µF capacitor for PVIN and a 1µF capacitor for SVIN are recommended. Smaller capacitance may be acceptable if the VIN line is sufficiently clean. Sufficient evaluation must be done before making a decision to use smaller capacitance.

www.ti.com

# 7 Evaluation Board Layout

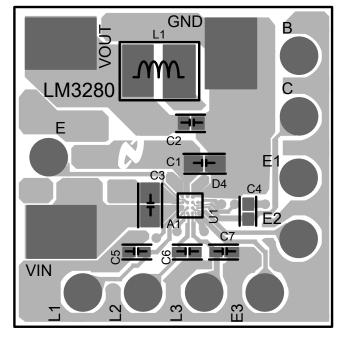

Figure 2. Top Layer

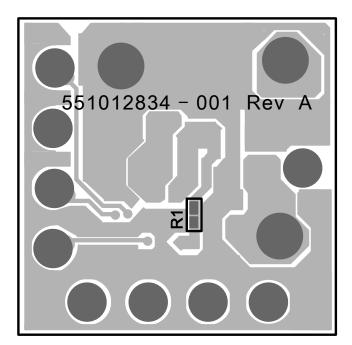

Figure 3. Bottom Layer

#### 8 Board Layout Consideration

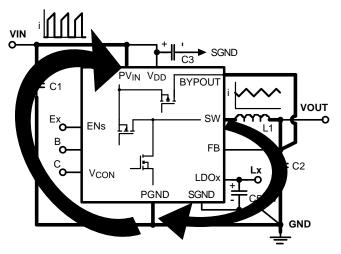

The LM3280 converts higher input voltage to lower output voltage with high efficiency. This is achieved with an inductor-based switching topology. During the first half of the switching cycle, the internal PFET switch turns on, the input voltage is applied to the inductor, and the current flows from PVIN line to the output capacitor (C2) through the inductor. During the second half cycle, the PFET turns off and the internal NFET turns on. The inductor current continues to flow via the inductor from the device PGND line to the output capacitor (C2).

Referring to Figure 4, the LM3280 in PWM mode has two major current loops where pulse and ripple current flow. The loop shown in the left had side is important because pulse current flows in the path. In the loop on the right hand side, the current waveform in this path is triangular. Pulse current has many high-frequency components due to fast di/dt. Triangular ripple current also has wide high-frequency components. Board layout and circuit pattern design of these two loops are key factors for reducing noise radiation and achieving stable operation. Other lines, such as input and output terminals are DC current, Therefore pattern width (current capability) and DCR drop considerations are needed.

Figure 4. Current Loop

# 8.1 Board Layout Guidelines

- 1. Minimize C1, PVIN, and PGND loop. These traces should be as wide and short as possible.

- 2. Minimize L1, C2, SW and PGND loop. These traces also should be wide and short.

- 3. Above layout patterns should be placed on the component side of the PCB to minimize parasitic inductance and resistance due to via-holes. It may be a good idea that the SW to L1 path is routed between C2(+) and C2(-) land patterns. If vias are used in these large current paths, multiple via-holes should be used if possible.

- Connect C1(-), C2(-), and PGND with side GND pattern. This pattern should be short, so C1(-), C2(-), and PGND should be as close as possible. Then connect to a PCB common GND pattern with as many via-holes as possible.

- 5. SGND should not connect directly to PGND. Connecting these pins under the device should be avoided. (If possible, connect SGND to the common port of C1(-), C2(-), and PGND.)

- 6. Place C3 as close to SVIN as possible to avoid noise.

- 7. FB line should be protected from noise. It is a good idea to use an inner GND layer (if available) as a shield.

- It is recommended to connect BYPOUT to VOUT at C2(+) using a separate trace, instead of connecting it directly to the FB for better noise immunity.

- 9. The LDO caps, C5, C6, and C7, should be placed as far away from the buck convertor as possible to suppress high frequency switching noise.

www.ti.com

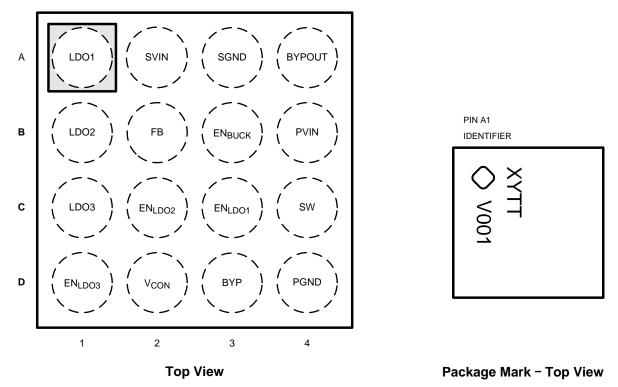

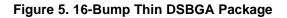

# 9 Connection Diagram and Package Mark Information

www.ti.com

# 10 Pin Descriptions

| Pin # Name |                    | Description                                                                                                                                                                                                                                  |  |  |

|------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| A1         | LDO1               | LDO1 Output.                                                                                                                                                                                                                                 |  |  |

| B1         | LDO2               | LDO2 Output.                                                                                                                                                                                                                                 |  |  |

| C1         | LDO3               | LDO3 Output.                                                                                                                                                                                                                                 |  |  |

| D1         | EN <sub>LDO3</sub> | LDO3 Enable Input. Set this digital input high to turn on LDO3. (EN <sub>BUCK</sub> pin must be also set high.) For turning LDO3 off, set low.                                                                                               |  |  |

| A2         | SVIN               | Analog, Signal and LDO Supply Input.                                                                                                                                                                                                         |  |  |

| B2         | FB                 | Buck Converter Feedback Analog Input. Connect to the output at the output filter capacitor.                                                                                                                                                  |  |  |

| C2         | EN <sub>LDO2</sub> | LDO2 Enable Input. Set this digital input high to turn on LDO2. (EN <sub>BUCK</sub> pin must be also set high.) For turning LDO2 off, set low.                                                                                               |  |  |

| D2         | V <sub>CON</sub>   | Buck Converter Voltage Control Analog Input. This pin controls $V_{OUT}$ in PWM mode. Set: $V_{OUT} = 3 \times V_{CON}$ . Do not leave floating.                                                                                             |  |  |

| A3         | SGND               | Analog, Signal, and LDO Ground.                                                                                                                                                                                                              |  |  |

| B3         | ENBUCK             | Buck Converter Enable Input. Set this digital input high after $V_{IN} > 2.7V$ for normal operation. For shutdown, set low.                                                                                                                  |  |  |

| C3         | EN <sub>LDO1</sub> | LDO1 Enable Input. Set this digital input high to turn on LDO1. (EN <sub>BUCK</sub> pin must be also set high.) For turning LDO1 off, set low.                                                                                               |  |  |

| D3         | BYP                | Forced Bypass Input. Use this digital input to command operation in Bypass mode. Set BYP low for normal operation.                                                                                                                           |  |  |

| A4         | BYPOUT             | Bypass FET Drain. Connect to the output capacitor. Do not leave floating.                                                                                                                                                                    |  |  |

| B4         | PVIN               | Buck Converter Power Supply Voltage Input to the internal P-FET switch and Bypass FET.                                                                                                                                                       |  |  |

| C4         | SW                 | Buck Converter Switch Node connection to the internal P-FET switch and N-FET synchronous rectifier.<br>Connect to an inductor with a saturation current rating that exceeds the maximum Switch Peak Current Limit of the PWM Buck Converter. |  |  |

| D4         | PGND               | Buck Converter Power Ground.                                                                                                                                                                                                                 |  |  |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated