# AN-1868 EMIRR Evaluation Boards for LMV861/LMV862

## 1 General Description

To demonstrate the EMI robustness of the LMV861/LMV862 and to be able to measure the parameter EMIRR, two evaluation boards have been developed; one for each device. This document describes the evaluation boards and explains how to perform EMIRR measurements. Focus is on one of the input pins as those are most sensitive to EMI. Based on symmetry considerations, it can be expected that both inputs have the same EMIRR. For reasons of simplicity of the required schematic the measurement on the IN+ pin is selected. A detailed description on EMI and EMIRR for the other pins can be found in the *AN-1698 A Specification for EMI Hardened Operational Amplifiers Application Report* (SNOA497).

To identify EMI robust op amps, a parameter is defined that quantitatively describes the EMI performance. A quantitative measure enables the comparison and the ranking of op amps on their EMI robustness. The definition of the parameter EMIRR is given by:

$$\mathsf{EMIRR}_{\mathsf{V}_{\mathsf{RF}}_{\mathsf{PEAK}}} = 20 \log \left( \frac{\mathsf{V}_{\mathsf{RF}}_{\mathsf{PEAK}}}{\Delta \mathsf{V}_{\mathsf{OS}}} \right)$$

where  $V_{RF_{PEAK}}$  is the amplitude of the applied unmodulated RF signal (V) and  $\Delta V_{OS}$  is the resulting inputreferred offset voltage shift (V).

## 2 Op Amp Configuration

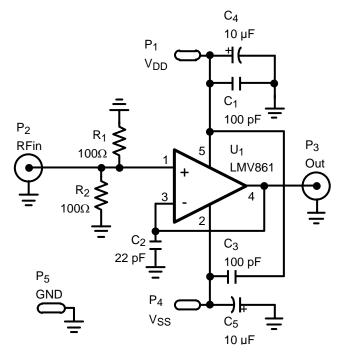

To have best defined RF levels on the pin under test, no op amp feedback elements should be in the RF signal path. Therefore, the op amp is connected in a unity-gain configuration. This yields the lowest level of RF filtering due to a feedback network. Schematics and layouts are included in this document.

## 3 Applying the RF Signal

Care needs to be taken in applying the RF signal to the pin under test. Signals up to a few GHz will be used, so the whole RF signal path needs to match the characteristic impedance of the RF generator. This requires proper coaxial cabling from the generator to the test board. On the test board a 50 $\Omega$  stripline needs to be used to bring the RF signal as close as possible to the pin under test. In this case the stripline can be connected directly from the connector to the IN+ pin. A 50 $\Omega$  termination at the pin under test is also required. For symmetry reasons this is done with two 100 $\Omega$  resistors in parallel, one on each side of the strip line. Setting up the test environment with a 50 $\Omega$  resistor close to the LMV861/LMV862 ensures that the RF levels at the pin under test are well defined. This 50 $\Omega$  resistor is also used to set the bias level of the IN+ pin to ground level. The DC measurements are taken at the output of the op amp. Since the op amp is in the unity gain configuration, the input referred offset voltage shift corresponds one-to-one to the measured output voltage shift.

## 4 Isolating the Other Pins

When the pin under test is tested, the other pins need to be decoupled for RF signals. This ensures that the obtained offset voltage shift is dominantly a result of coupling the RF signal to the pin under test. For this decoupling standard SMD components can be used.

All trademarks are the property of their respective owners.

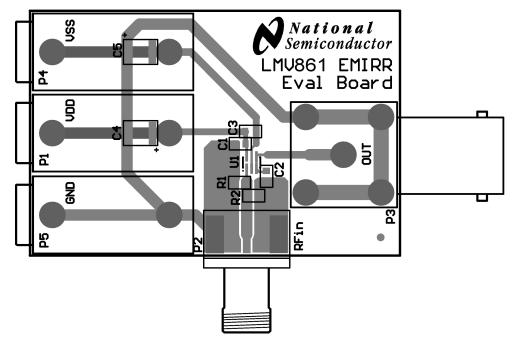

#### 5 Layout Considerations

The layout of the evaluation board requires some attention. For decoupling the supply lines it is suggested that 10 nF capacitors be placed as close as possible to the op amp. For single supply, place a capacitor between V<sup>+</sup> and V<sup>-</sup>. For dual supplies, place one capacitor between V<sup>+</sup> and the board ground, and a second capacitor between ground and V<sup>-</sup>. On the LMV861 evaluation board, the decoupling of the negative pin V<sup>-</sup>is implemented by a capacitor between V<sup>+</sup> and V<sup>-</sup>. This is done for easy routing and to keep connections to the pins short. Even with the LMV861/LMV862's inherent hardening against EMI, it is still recommended to keep the input traces short and as far as possible from RF sources. Then the RF signals entering the chip are as low as possible, and the remaining EMI can be, almost, completely eliminated in the chip by the EMI reducing features of the LMV861/LMV862.

## 6 Measurement Procedure

The measurement procedure is the same for all test circuits. To measure the input referred offset voltage shift needed for calculating the EMIRR, the following procedure can be used:

- 1. Measure  $V_{OUT}$  when the RF signal is off.

- 2. Measure  $V_{OUT}$  when the RF signal is on.

- Translate measured V<sub>OUT</sub> voltages to input referred voltages. Translation is one-to-one in this case since the gain is one in the IN+ test setup.

- 4. Subtract the two measured input referred voltages.

- 5. Verify if the offset shift is above the noise level of the op amp setup and the op amp is not saturated. If this is not the case choose another RF level and start the procedure again.

- 6. Calculate the EMIRR.

- 7. If needed, transform the results to an EMIRR based on a 100 mV  $_{\rm P}$  RF signal.

#### 7 Measurement Results

To show the sensitivity of the IN+ pin two types of measurement results are presented using the LMV861 evaluation board:

- The EMIRR as a function of the *frequency* of the applied signal. The level of the signal is set to the standard level of 100 mV<sub>P</sub> (-20 dBV<sub>P</sub>).

- The EMIRR as a function of the *level* of the applied signal. The frequency is set to four typical values: 400 MHz, 900 MHz, 1.8 GHz, and 2.4 GHz.

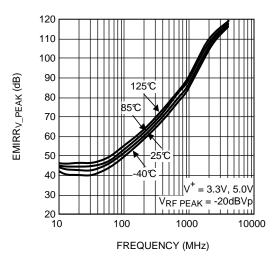

## 7.1 EMIRR Vs. Frequency

Figure 1 depicts the EMIRR versus frequency for the various temperatures. The measurement is performed with a fixed RF level of  $-20 \text{ dBV}_P$  and a varying RF signal frequency. The frequency range is 10 MHz to 4 GHz.

Figure 1. EMIRR vs. Frequency

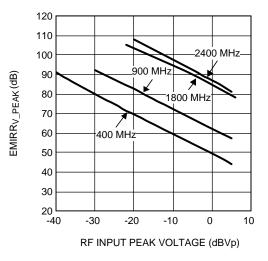

## 7.2 EMIRR Vs. Power

Figure 2 depicts the EMIRR as a function of power at four typical frequencies.

Figure 2. EMIRR vs. Power

In this figure two areas can be distinguished. At the left side of the figure, the EMIRR increases as a function of input level; whereas at the right side the EMIRR decreases as a function of the input level.

The left side of the figure is actually an artifact resulting from the limited accuracy of the measurement setup. For the relatively low input levels, the resulting offset voltage shift is well below the noise level. Thus, when calculating the EMIRR for that region, the ratio of the input level to the noise level is depicted. As the noise level is constant for the setup, an increasing EMIRR is obtained for increasing input signal level.

For the right side, the obtained offset-shift is well above the noise level. As the relation between offset voltage shift and RF input level is quadratic, the ratio as used in the EMIRR is inversely proportional to the RF input level, which is in line with the displayed slope of "-1".

## 8 Bill of Materials

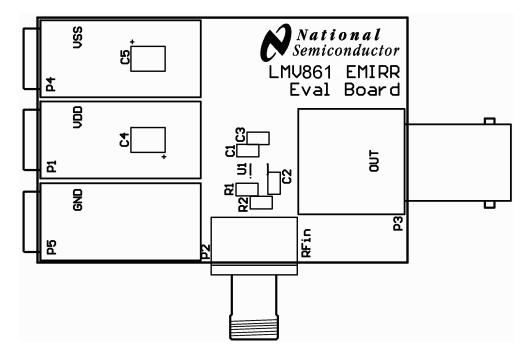

The Bill of Materials (BOM) of the LMV861 evaluation board is given in Table 1.

#### Table 1. LMV861 Bill of Materials

| Designator | Description      | Comment |  |

|------------|------------------|---------|--|

| C1, C3     | 0603 Capacitor   | 100 pF  |  |

| C2         | 0603 Capacitor   | 22 pF   |  |

| C4, C5     | Case_B Capacitor | 10 µF   |  |

| P1         | Connector        | Banana  |  |

| P2         | Connector        | SMA     |  |

| P3         | Connector        | BNC     |  |

| P4         | Connector        | Banana  |  |

| P5         | Connector        | Banana  |  |

| R1, R2     | 0603 Resistor    | 100Ω    |  |

| U1         | SC70             | LMV861  |  |

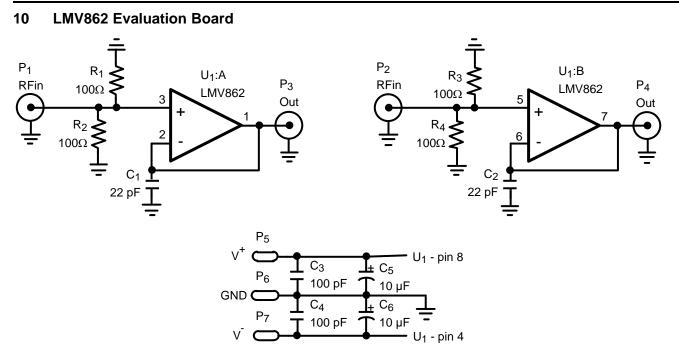

The Bill of Materials (BOM) of the LMV862 evaluation board is given in Table 2.

#### Table 2. LMV862 Bill of Materials

| Designator     | Description      | Comment |  |

|----------------|------------------|---------|--|

| C1, C2         | 0603 Capacitor   | 22 pF   |  |

| C3, C4         | 0603 Capacitor   | 100 pF  |  |

| C5, C6         | Case_B Capacitor | 10 µF   |  |

| P1, P2         | Connector        | SMA     |  |

| P3, P4         | Connector        | BNC     |  |

| P5             | Connector        | Banana  |  |

| P6             | Connector        | Banana  |  |

| P7             | Connector        | Banana  |  |

| R1, R2, R3, R4 | 0603 Resistor    | 100Ω    |  |

| U1             | MSOP             | LMV862  |  |

## 9 LMV861 Evaluation Board

Figure 3. Schematic for LMV861, Coupling RF Signal to the IN+ Pin

LMV861 Evaluation Board

www.ti.com

Figure 4. Layout for LMV861, All Layers

Figure 5. Layout for LMV861, Silk Screen

Figure 6. Schematic for LMV862, Coupling RF Signal to the IN+ Pin

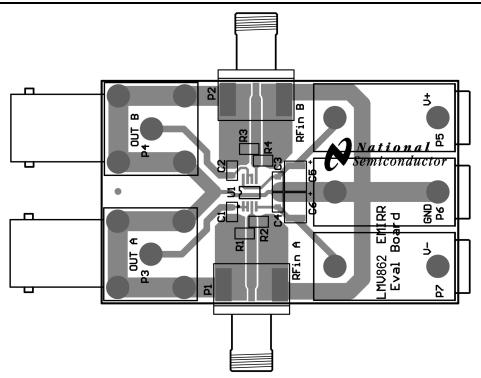

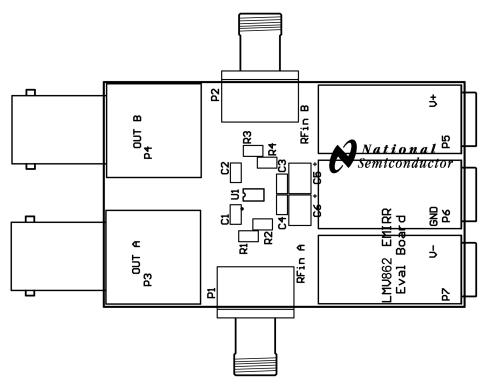

LMV862 Evaluation Board

www.ti.com

Figure 7. Layout for LMV862, All Layers

Figure 8. Layout for LMV862, Silk Screen

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated