# TMS320C82 Transfer Controller User's Guide

Literature Number: SPRU261 June 1998

#### IMPORTANT NOTICE

Texas Instruments and its subsidiaries (TI) reserves the right to make changes to their products or to discontinue any product or service without notice, and advises customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current and complete. All products are sold subject to the terms and conditions of sale at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITIACL APPLICATIONS). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUTABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © June 1998, Texas Instruments Incorporated

# **Contents**

| 1 | Tran | sfer Co  | ntroller Overview                                | . 1-1 |

|---|------|----------|--------------------------------------------------|-------|

|   | 1.1  | Transf   | fer Controller Description                       | . 1-2 |

|   |      | 1.1.1    | Key Features                                     |       |

|   |      | 1.1.2    | Transfer Controller Functions                    | . 1-3 |

|   | 1.2  | Functi   | onal Blocks                                      | . 1-4 |

|   |      | 1.2.1    | Request Queuing and Prioritization Logic         | . 1-4 |

|   |      | 1.2.2    | Cache and Refresh Controller                     | . 1-4 |

|   |      | 1.2.3    | Source / Destination Controllers                 | . 1-4 |

|   |      | 1.2.4    | Internal Memory (Crossbar) Interface             | . 1-5 |

|   |      | 1.2.5    | External Memory Interface                        |       |

|   |      | 1.2.6    | Source/Destination Mux and Alignment and PT FIFO |       |

|   |      | 1.2.7    | Cache Buffer                                     |       |

|   |      | 1.2.8    | Cycle Configuration Cache                        | . 1-6 |

|   | 1.3  | Transf   | fer Controller Registers                         | . 1-7 |

|   |      | 1.3.1    | The REFCNTL Register                             | . 1-7 |

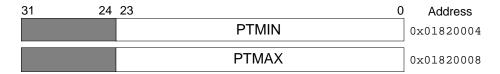

|   |      | 1.3.2    | The PTMIN Register                               |       |

|   |      | 1.3.3    | The PTMAX Register                               |       |

|   |      | 1.3.4    | The FLTSTS Register                              | . 1-9 |

| 2 | Tran | sfer Co  | ntroller Priorities                              | . 2-1 |

|   | 2.1  | Reque    | est Prioritization                               | . 2-2 |

|   | 2.2  | Round    | d-Robin Operation                                | . 2-5 |

|   | 2.3  | Cross    | bar Priority                                     | . 2-6 |

| 3 | Cacl | ne Servi | ce and DEA Requests                              | . 3-1 |

|   | 3.1  | Cache    | e Service Requests                               | . 3-2 |

|   |      | 3.1.1    | PP Cache Miss Servicing                          | . 3-2 |

|   |      | 3.1.2    | PP Cache Service Latency                         | . 3-2 |

|   |      | 3.1.3    | MP Cache Miss Servicing                          | . 3-4 |

|   |      | 3.1.4    | MP Cache Service Latency                         | . 3-4 |

|   | 3.2  | DEA R     | Requests                                      | 3-6 |

|---|------|-----------|-----------------------------------------------|-----|

|   |      | 3.2.1     | PP DEA Requests                               | 3-6 |

|   |      | 3.2.2     | MP DEA Requests                               | 3-6 |

|   |      | 3.2.3     | DEA Service Prioritization                    |     |

|   |      | 3.2.4     | DEA Service Latency                           | 3-7 |

| 4 | Pack | et Trans  | sfer Overview                                 | 4-1 |

|   | 4.1  | Introdu   | uction to Packet Transfers                    | 4-2 |

|   |      | 4.1.1     | Packet Transfer Terminology                   | 4-2 |

|   | 4.2  | Packet    | t Transfer Parameter RAM Usage                | 4-4 |

|   | 4.3  | Initializ | zing a Packet Transfer                        | 4-6 |

|   |      | 4.3.1     | The Linked List Structure                     | 4-6 |

|   |      | 4.3.2     | Packet Transfer Service                       | 4-7 |

| 5 | Shor | t-Form    | Packet Transfers                              | 5-1 |

|   | 5.1  | Short-l   | Form Packet Transfer Overview                 | 5-2 |

|   | 5.2  | Short-l   | Form Packet Transfer Parameter Tables         | 5-3 |

|   | 5.3  | Short-l   | Form Packet Transfer Parameter Fields         | 5-4 |

|   |      | 5.3.1     | Next Entry Address                            | 5-4 |

|   |      | 5.3.2     | Count / Update Value                          |     |

|   |      | 5.3.3     | PT Options                                    |     |

|   |      | 5.3.4     | src Start Address                             |     |

|   |      | 5.3.5     | dst Start Address                             |     |

|   | 5.4  |           | Form Packet Transfer Options Field            |     |

|   |      | 5.4.1     | Short-Form PT Access Mode (PAM) - Bits(18:16) |     |

|   |      | 5.4.2     | Exchange src and dst Parameters (X) - Bit(19) |     |

|   |      | 5.4.3     | Short-Form Packet Transfer (SF) - Bit(20)     |     |

|   |      | 5.4.4     | src Update (SU) - Bit(22)                     |     |

|   |      | 5.4.5     | Reverse A Addressing (RA) - Bit(23)           |     |

|   |      | 5.4.6     | dst Update (DU) - Bit(25)                     |     |

|   |      | 5.4.7     | Interrupt when Finished (I) - Bit(28)         |     |

|   |      | 5.4.8     | Packet Transfer Status(PTS) - Bit(30:29)      |     |

|   |      | 5.4.9     | Stop (S) - Bit(31)                            |     |

| 6 | _    |           | Packet Transfers                              |     |

|   | 6.1  | Long-F    | Form Packet Transfer Overview                 | 6-2 |

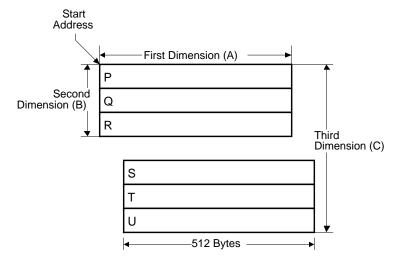

|   | 6.2  | Dimen     | sioned Transfers                              | გ₋3 |

| 6.3 | Guided | l Transfers                                    | 6-5    |

|-----|--------|------------------------------------------------|--------|

|     | 6.3.1  | Guide Tables                                   | 6-5    |

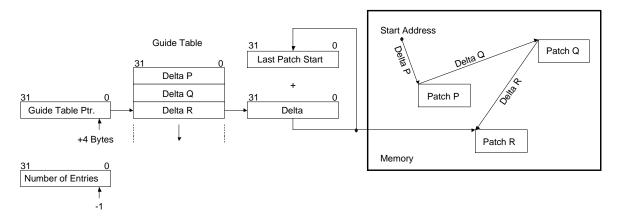

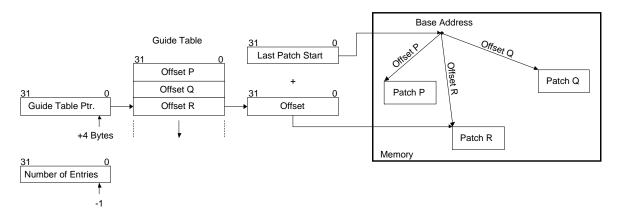

|     | 6.3.2  | Fixed-Patch Guided Transfers                   | 6-6    |

|     | 6.3.3  | Variable-Patch Guided Transfers                | 6-9    |

|     | 6.3.4  | Fill-With Value Transfers                      | . 6-12 |

| 6.4 | Long-F | orm Packet Transfer Parameter Tables           | . 6-14 |

| 6.5 | Long-F | orm Packet Transfer Parameter Fields           | 6-17   |

|     | 6.5.1  | Next Entry Address                             |        |

|     | 6.5.2  | PT Options                                     |        |

|     | 6.5.3  | src / dst Start Address                        |        |

|     | 6.5.4  | src / dst Base Address                         |        |

|     | 6.5.5  | src / dst A Count                              | 6-18   |

|     | 6.5.6  | src / dst B Count                              | 6-19   |

|     | 6.5.7  | src / dst C Count                              | 6-19   |

|     | 6.5.8  | src / dst Number of Entries                    | . 6-19 |

|     | 6.5.9  | src / dst B Pitch                              | 6-19   |

|     | 6.5.10 | src / dst C Pitch                              | 6-20   |

|     | 6.5.11 | src / dst Guide Table Pointer                  | 6-20   |

|     | 6.5.12 | LS and MS Fill Value                           | 6-20   |

|     | 6.5.13 | src Transparency Value                         | 6-20   |

|     | 6.5.14 | Color Register Value                           | . 6-21 |

|     | 6.5.15 | Unused Field                                   | 6-21   |

| 6.6 | Long-F | orm Packet Transfer Options Field              | 6-22   |

|     | 6.6.1  | dst Update Mode (DUM) - Bits (1:0)             | 6-22   |

|     | 6.6.2  | dst Transfer Mode (DTM) - Bits (6:4)           | 6-23   |

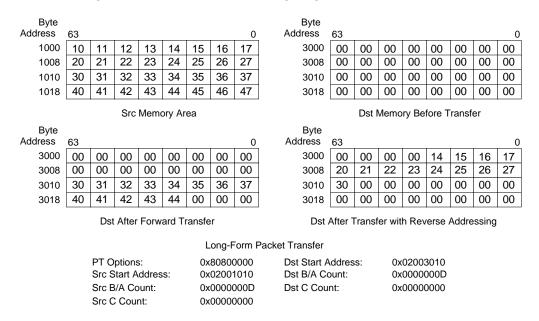

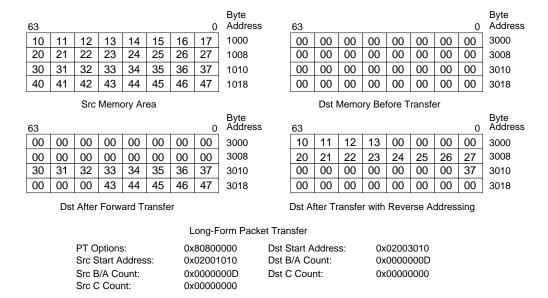

|     | 6.6.3  | src Update Mode (SUM) - Bits (9:8)             | 6-24   |

|     | 6.6.4  | src Transfer Mode (STM) - Bits (14:12)         | 6-25   |

|     | 6.6.5  | Long-Form PT Access Mode (PAM) - Bits (18:16)  | 6-25   |

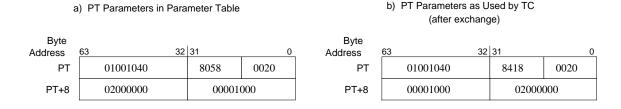

|     | 6.6.6  | Exchange src and dst Parameters (X) - Bit (19) | 6-27   |

|     | 6.6.7  | Short-Form Packet Transfer (SF) - Bit (20)     | 6-29   |

|     | 6.6.8  | Reverse src B Addressing (RSB) - Bit (21)      | 6-30   |

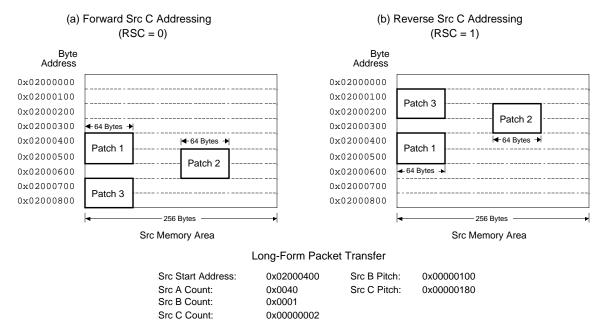

|     | 6.6.9  | Reverse src C Addressing (RSC) - Bit (22)      | 6-30   |

|     | 6.6.10 | Reverse A Addressing (RA) - Bit (23)           | . 6-31 |

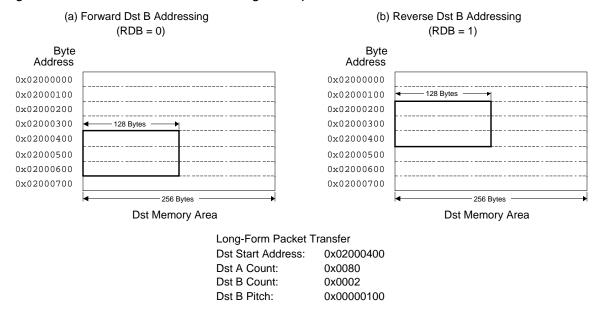

|     | 6.6.11 | Reverse dst B Addressing (RDB) - Bit (24)      | 6-33   |

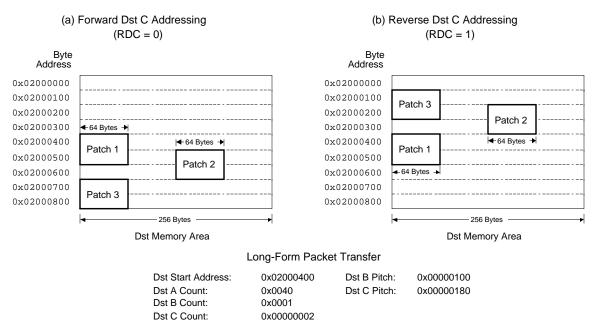

|     | 6.6.12 | Reverse dst C Addressing (RDC) - Bit (25)      |        |

|     | 6.6.13 | Interrupt when Finished (I) - Bit (28)         | 6-34   |

|     | 6.6.14 | Packet Transfer Status(PTS) - Bit(30:29)       | 6-35   |

|     | 6.6.15 | Stop (S) - Bit(31)                             | 6-36   |

|     | 5.51.5 | r (-)(-·)····························          |        |

| 7 | Exte | rnally In                                   | itiated Packet Transfers                                                                                                                                                                                  | 7-1                      |

|---|------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|   | 7.1  | XPT O                                       | verview                                                                                                                                                                                                   | 7-2                      |

|   | 7.2  | Reque                                       | sting XPTs                                                                                                                                                                                                | 7-3                      |

|   | 7.3  | XPT Pa                                      | arameter RAM Usage                                                                                                                                                                                        | 7-4                      |

|   | 7.4  | XPT Se<br>7.4.1<br>7.4.2<br>7.4.3           | ervicing  Long-Form XPT Service  Short-Form XPT Service  XPT Status Codes.                                                                                                                                |                          |

|   | 7.5  | XPT Co<br>7.5.1<br>7.5.2                    | ompletionXPT Completion CodesXPT Errors                                                                                                                                                                   | 7-8                      |

| 8 | Spec | ial Pack                                    | tet Transfer Access Modes                                                                                                                                                                                 | 8-1                      |

|   | 8.1  | Block-\ 8.1.1 8.1.2 8.1.3 8.1.4 8.1.5 8.1.6 | Write Modes Block-Write Type Selection Block-Write Notation 8x Block-Write 4x Block-Write Simulated Block-Write Color Register Loading                                                                    | 8-2<br>8-2<br>8-3<br>8-8 |

|   | 8.2  | Transp                                      | parency Modes                                                                                                                                                                                             | 8-13                     |

|   | 8.3  | Peripho<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4 | eral Device Transfer Mode Programming Peripheral Device Read Packet Transfers Programming Peripheral Device Write Packet Transfers Initiating Peripheral Device Packet Transfers Transfer Synchronization | 8-15<br>8-15<br>8-15     |

|   | 8.4  | Read T<br>8.4.1<br>8.4.2                    | Fransfer Modes          Full Read Transfers          Split Read Transfers                                                                                                                                 | 8-18                     |

| 9 | Pack | et Trans                                    | sfer Operation                                                                                                                                                                                            | 9-1                      |

|   | 9.1  | Packet<br>9.1.1<br>9.1.2                    | Data Transfer                                                                                                                                                                                             | 9-2<br>9-2               |

|   | 9.2  | Contro<br>9.2.1<br>9.2.2<br>9.2.3           | Iling PT Execution Time                                                                                                                                                                                   | 9-4<br>9-5               |

|    | 9.3   | Linked                                                                                            | List Management                                                                                                                                                                                                                                                                           | 9-6                                                                           |

|----|-------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

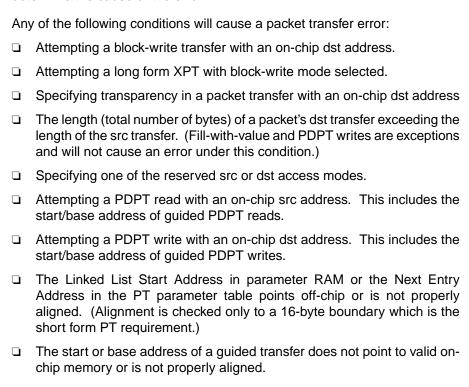

|    | 9.4   | Packet                                                                                            | Transfer Errors                                                                                                                                                                                                                                                                           | 9-8                                                                           |

|    | 9.5   | Packet                                                                                            | Transfer Suspension                                                                                                                                                                                                                                                                       | 9-9                                                                           |

|    |       | 9.5.1                                                                                             | Suspended Long-Form Packet Transfer Parameters                                                                                                                                                                                                                                            | . 9-10                                                                        |

|    |       | 9.5.2                                                                                             | Suspended Short-Form Packet Transfer Parameters                                                                                                                                                                                                                                           | . 9-12                                                                        |

| 10 | Exter | nal Mem                                                                                           | nory Interface                                                                                                                                                                                                                                                                            | . 10-1                                                                        |

|    | 10.1  | Memor                                                                                             | y Interface Signals                                                                                                                                                                                                                                                                       | . 10-2                                                                        |

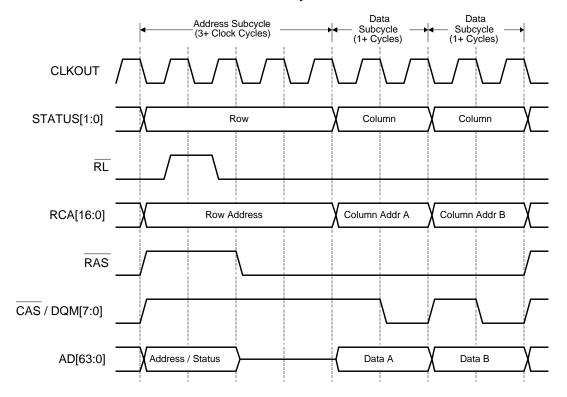

|    | 10.2  | 10.2.1                                                                                            | Al Form of an External Memory Cycle                                                                                                                                                                                                                                                       | . 10-4                                                                        |

|    | 10.3  | 10.3.1<br>10.3.2                                                                                  | y Cycle Configuration                                                                                                                                                                                                                                                                     | . 10-5<br>. 10-6                                                              |

|    | 10.4  | 10.4.1                                                                                            | y Cycle Information                                                                                                                                                                                                                                                                       | . 10-8                                                                        |

|    | 10.5  | 10.5.1<br>10.5.2<br>10.5.3<br>10.5.4<br>10.5.5<br>10.5.6<br>10.5.7<br>10.5.8<br>10.5.9<br>10.5.10 | y Bank Configuration Column Timing Selection Turn-Off Cycle Selection Exception Support Enabling Address Multiplexing PDT Address Bit Replacement. Page Size Bus Size Column-Time Wait State Insertion Block-Write Support New-Time Wait State Insertion Memory Bank Size Priority Level. | 10-11<br>10-12<br>10-13<br>10-15<br>10-16<br>10-18<br>10-19<br>10-20<br>10-20 |

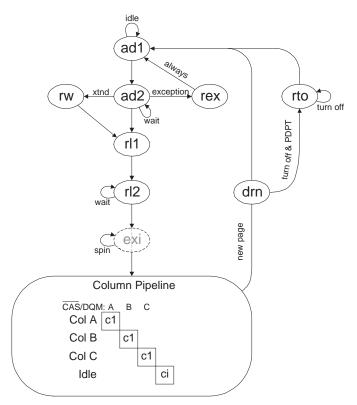

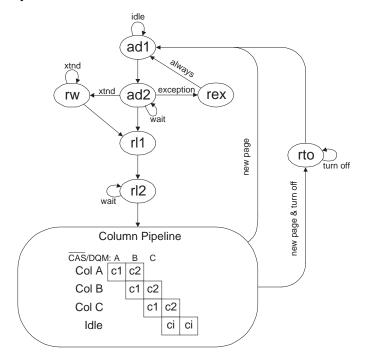

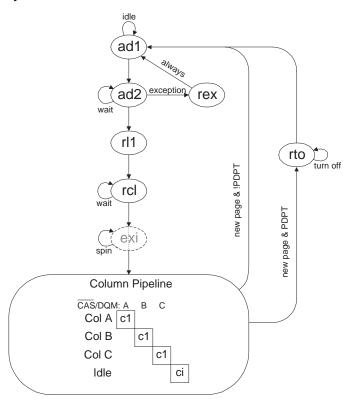

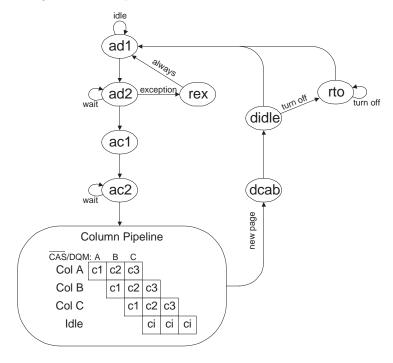

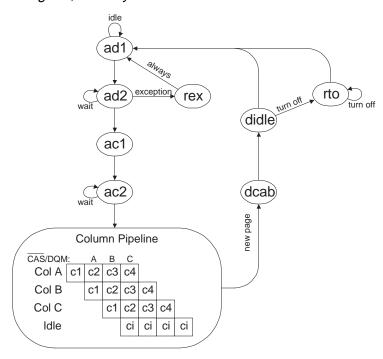

| 11 | Gene  | rating M                                                                                          | lemory Cycles                                                                                                                                                                                                                                                                             | . 11-1                                                                        |

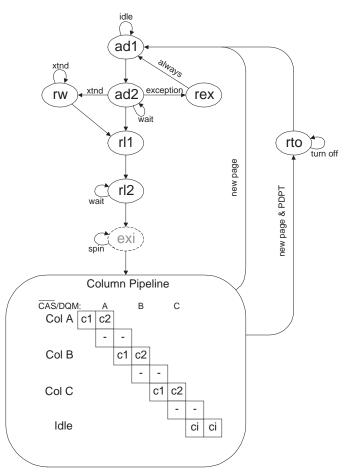

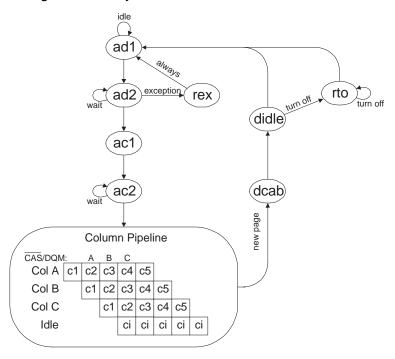

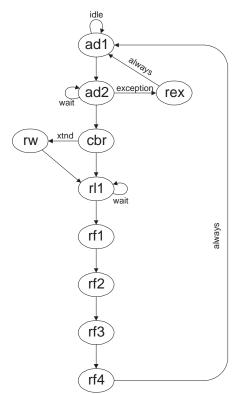

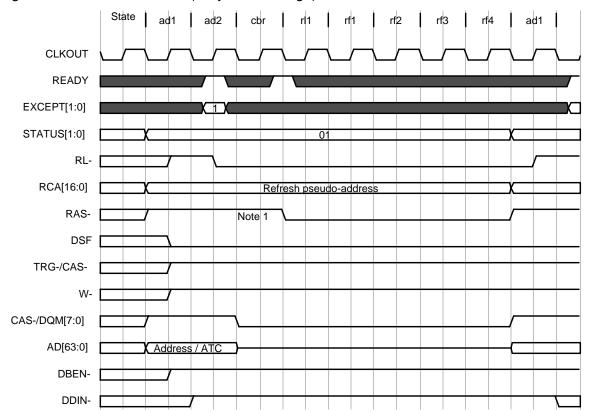

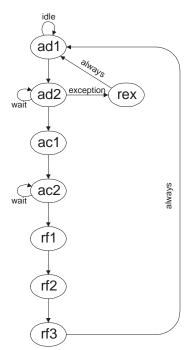

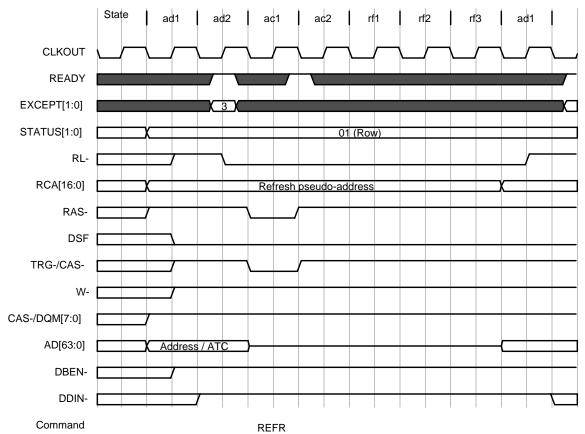

|    | 11.1  | 11.1.1<br>11.1.2                                                                                  | ew of Memory States                                                                                                                                                                                                                                                                       | . 11-4<br>. 11-6                                                              |

|    | 11.2  |                                                                                                   | er Controller Pipelines                                                                                                                                                                                                                                                                   |                                                                               |

|    | 11.3  |          | an External Memory Cycle11-8                         |

|----|-------|----------|------------------------------------------------------|

|    |       |          | Normal Termination                                   |

|    |       | 11.3.2   | Wait States                                          |

|    | 11.4  | Memor    | y Exceptions                                         |

|    |       | 11.4.1   | Flush Cache Entry11-11                               |

|    |       | 11.4.2   | Retry                                                |

|    |       | 11.4.3   | New Page Request                                     |

|    | 11.5  | Faults.  |                                                      |

|    |       |          | Fault Support                                        |

|    |       |          | PP Cache/DEA Faults                                  |

|    |       |          | MP Cache/DEA Faults                                  |

|    |       |          | Packet Transfer Faults                               |

|    |       |          | On-chip Faults                                       |

| 12 | Endia | aness ar | nd Bus Sizing12-1                                    |

| -  |       |          | -                                                    |

|    | 12.1  | •        | d Little-Endian Operation                            |

|    |       |          | External Transfers in Big- and Little-Endian Formats |

|    |       |          | Selecting Endian Format                              |

|    |       |          | Packet Transfer Endian Considerations                |

|    | 12.2  | -        | ic Bus Sizing                                        |

|    |       |          | Big-Endian Bus Sizing                                |

|    |       | 12.2.2   | Little-Endian Bus Sizing                             |

| 13 | Bank  | Configu  | ıration Cycle                                        |

|    | 13.1  | Bank C   | Configuration Cycle Overview                         |

|    |       |          | Bank Configuration Data                              |

|    |       |          | Bank Configuration Address                           |

|    | 13.2  |          | configuration States                                 |

|    | 13.3  | Bank C   | configuration Example                                |

| 14 | DRA   | M Cvcles | s                                                    |

|    | 14.1  | -        | Cycle Overview                                       |

|    | 14.1  |          | DRAM Row Accesses                                    |

|    |       |          |                                                      |

|    |       |          | DRAM Read Cycles                                     |

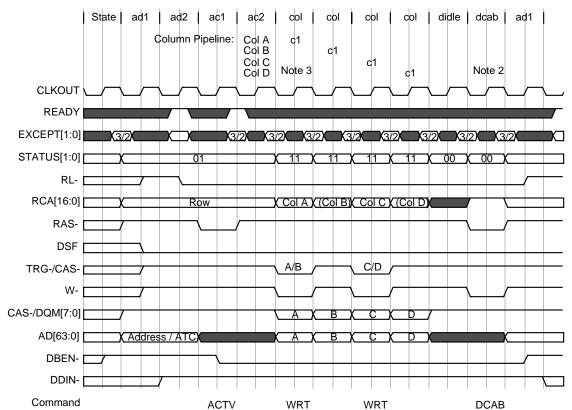

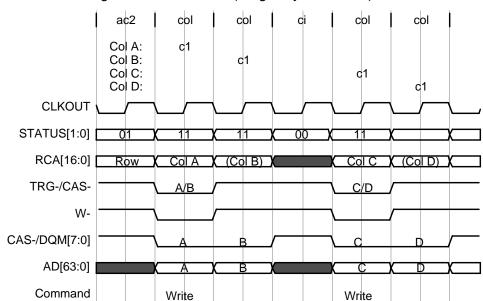

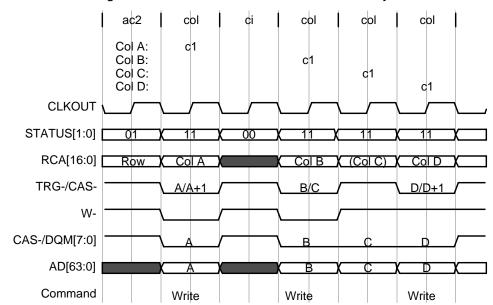

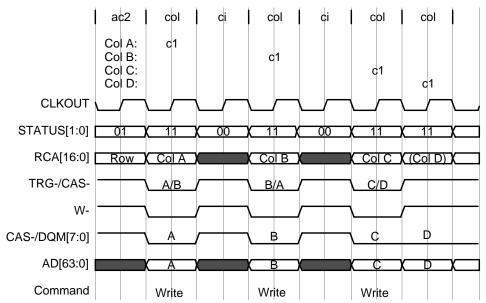

|    |       |          | DRAM Write Cycles                                    |

|    |       |          | · ·                                                  |

|    |       | 14.1.5   | Peripheral Device DRAM Write Cycles                  |

|    | 14.2 | Pipelined 1 Cycle/Column DRAM Cycles                                                                                                                                                                                                                                                           |

|----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 14.3 | Nonpipelined 1 Cycle/Column DRAM Cycles                                                                                                                                                                                                                                                        |

|    | 14.4 | 2 Cycle/Column DRAM Cycles       14-25         14.4.1 2 Cycle/Column DRAM Read       14-25         14.4.2 2 Cycle/Column DRAM Write       14-32                                                                                                                                                |

|    | 14.5 | 3 Cycle/Column DRAM Cycles       14-39         14.5.1 3 Cycle/Column DRAM Read       14-39         14.5.2 3 Cycle/Column DRAM Write       14-48                                                                                                                                                |

| 15 | SRAN | Cycles                                                                                                                                                                                                                                                                                         |

|    | 15.1 | SRAM Cycle Overview.       15-2         15.1.1 SRAM Row Accesses.       15-2         15.1.2 SRAM Read Cycles       15-3         15.1.3 Peripheral Device SRAM Read Cycles       15-3         15.1.4 SRAM Write Cycles       15-3         15.1.5 Peripheral Device SRAM Write Cycles       15-4 |

|    | 15.2 | 1 Cycle/Column Synchronous SRAM Cycles                                                                                                                                                                                                                                                         |

|    | 15.3 | 1 Cycle/Column SRAM Cycles       15-17         15.3.1 1 Cycle/Column SRAM Read       15-17         15.3.2 1 Cycle/Column SRAM Write       15-20                                                                                                                                                |

|    | 15.4 | 2 Cycle/Column SRAM Cycles       15-26         15.4.1 2 Cycle/Column SRAM Read       15-26         15.4.2 2 Cycle/Column SRAM Write       15-32                                                                                                                                                |

|    | 15.5 | 3 Cycle/Column SRAM Cycles       15-40         15.5.1 3 Cycle/Column SRAM Read       15-40         15.5.2 3 Cycle/Column SRAM Write       15-46                                                                                                                                                |

| 16 | SDRA | M Cycles                                                                                                                                                                                                                                                                                       |

|    | 16.1 | SDRAM Cycle Overview       16-2         16.1.1 SDRAM Command Support       16-2         16.1.2 SDRAM Bank Operation       16-3         16.1.3 SDRAM Read Latency       16-3         16.1.4 SDRAM Burst Length       16-3         16.1.5 SDRAM Pin Connections       16-4                       |

|    |      | 10:110 00:10:111:111:1111:1111:1111:111                                                                                                                                                                                                                                                        |

|     | 16.2 | SDRAM     | M Initialization                               | 16-5  |

|-----|------|-----------|------------------------------------------------|-------|

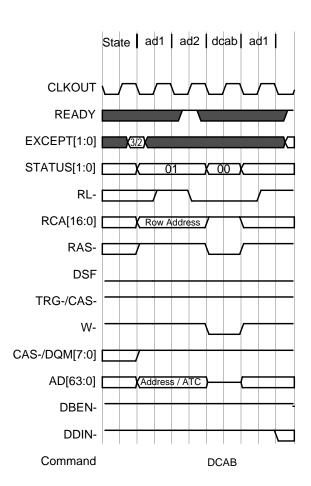

|     |      | 16.2.1    | SDRAM DCAB State Sequence                      | 16-5  |

|     |      | 16.2.2    | SDRAM DCAB Example                             | 16-5  |

|     | 16.3 | SDRAM     | M Mode Register Programming                    | 16-7  |

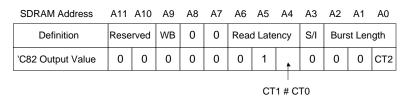

|     |      | 16.3.1    | Mode Register Value                            | 16-7  |

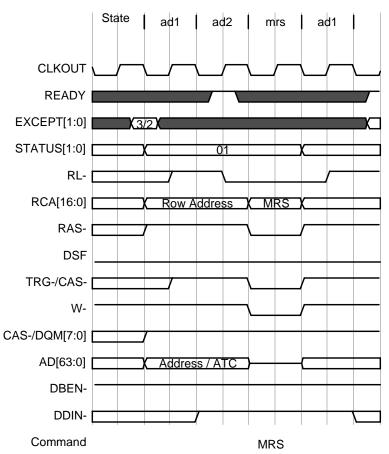

|     |      | 16.3.2    | SDRAM MRS State Sequence                       | 16-8  |

|     |      | 16.3.3    | SDRAM MRS Example                              | 16-8  |

|     | 16.4 | SDRAM     | M Burst Length 1 Cycles                        | 16-10 |

|     |      | 16.4.1    | SDRAM Burst Length 1, Latency 2 Read           | 16-10 |

|     |      | 16.4.2    | SDRAM Burst Length 1, Latency 3 Read           | 16-14 |

|     |      | 16.4.3    | SDRAM Burst Length 1, Latency 4 Read           | 16-18 |

|     |      | 16.4.4    | SDRAM Burst Length 1 Write                     | 16-22 |

|     | 16.5 | SDRAM     | M Burst Length 2 Cycles                        | 16-26 |

|     |      | 16.5.1    | SDRAM Burst Length 2, Latency 2 Read           | 16-26 |

|     |      | 16.5.2    | SDRAM Burst Length 2, Latency 3 Read           | 16-33 |

|     |      | 16.5.3    | SDRAM Burst Length 2, Latency 4 Read           | 16-40 |

|     |      | 16.5.4    | SDRAM Burst Length 2 Write                     | 16-47 |

| 17  | VRAN | /I Cycles | s                                              | 17-1  |

| • • |      | •         |                                                |       |

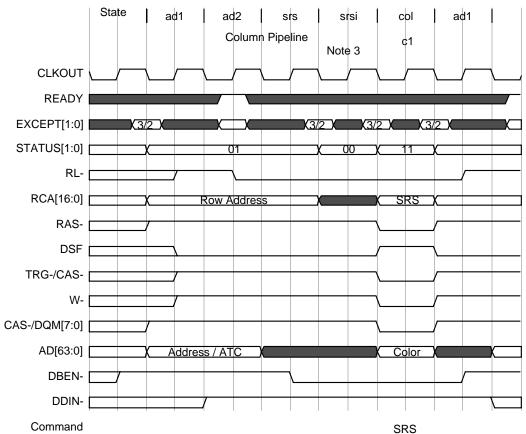

|     | 17.1 |           | Color-Register Access                          |       |

|     |      |           | 1 Cycle/Column LCR Access                      |       |

|     |      |           | 3 Cycle/Column LCR Access                      |       |

|     | 47.0 |           |                                                |       |

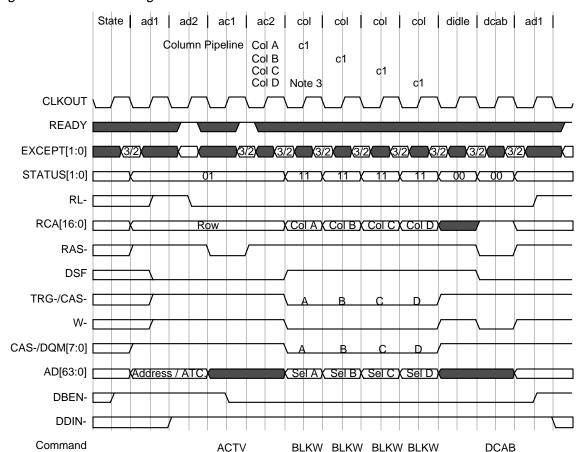

|     | 17.2 |           | Block-Write Access                             |       |

|     |      |           | Pipelined 1 Cycle/Column Block-Write Access    |       |

|     |      |           | Nonpipelined 1 Cycle/Column Block-Write Access |       |

|     |      |           | 2 Cycle/Column Block-Write Access              |       |

|     |      |           | •                                              |       |

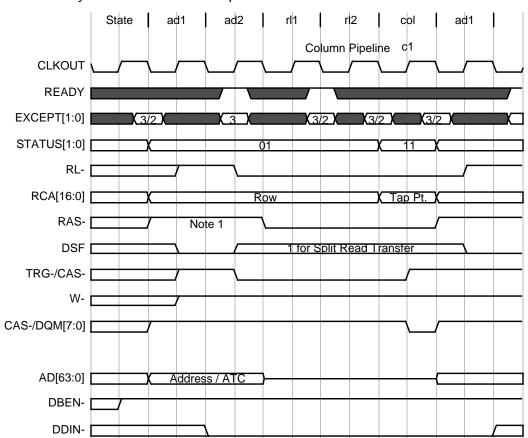

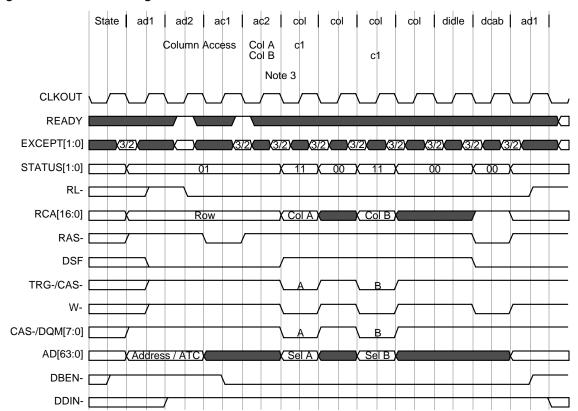

|     | 17.3 |           | Transfer and Split Read Transfer Accesses      |       |

|     |      |           | 1 Cycle/Column Read and Split-Read Transfer    |       |

|     |      |           | 2 Cycle/Column Read and Split-Read Transfer    |       |

|     |      | 17.3.3    | 3 Cycle/Column Read and Split-Read Transfer    | 17-13 |

| 18  | SGR  | AM Cycl   | les                                            | 18-1  |

|     | 18.1 | Specia    | l Register Set                                 | 18-2  |

|     | 18.2 | SGRA      | M Block-Write Access                           | 18-5  |

|     |      | 18.2.1    | Burst Length 1 Block-Write Access              | 18-5  |

|     |      | 18.2.2    | Burst Length 2 Block-Write Access              | 18-6  |

| 19 | Refresh Controller                |                                                                                                                                                       |                      |  |

|----|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

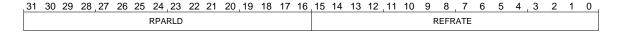

|    | 19.1                              | Refresh Rate                                                                                                                                          | 19-2                 |  |

|    | 19.2                              | Refresh Priority                                                                                                                                      | 19-3                 |  |

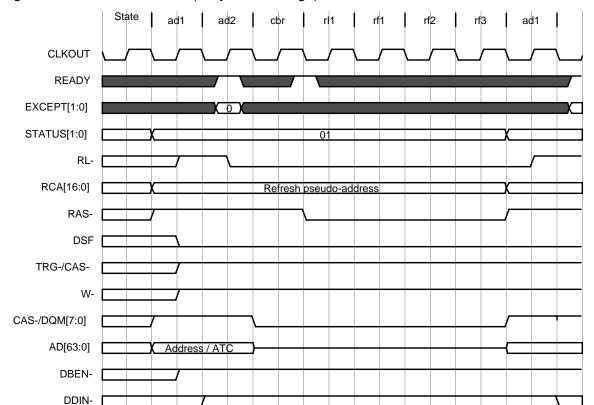

|    | 19.3                              | Programming the Refresh Pseudo-Address                                                                                                                | 19-4                 |  |

|    | 19.4                              | Refresh Cycles  19.4.1 Refresh Timing Selection  19.4.2 DRAM Refresh (3 Cycle RAS High)  19.4.3 DRAM Refresh (4 Cycle RAS High)  19.4.4 SDRAM Refresh | 19-5<br>19-5<br>19-7 |  |

| 20 | Host Interface                    |                                                                                                                                                       |                      |  |

|    | 20.1                              | Host Interface Signals                                                                                                                                | 20-2                 |  |

|    | 20.2                              | Host Handshake Mechanism                                                                                                                              | 20-3                 |  |

|    | 20.3                              | Host Interface Timing                                                                                                                                 | 20-4                 |  |

| 21 | Resetting the Transfer Controller |                                                                                                                                                       |                      |  |

|    | 21.1                              | Hardware Reset. 21.1.1 Normal Reset Sequence 21.1.2 Reset Halt. 21.1.3 Reset High-Impedance. 21.1.4 Endian Initialization.                            | 21-2<br>21-2<br>21-3 |  |

|    | 21.2                              | Software Reset                                                                                                                                        | 21-4                 |  |

| Α  | Packet Transfer Parameter Tables  |                                                                                                                                                       |                      |  |

|    | A.1                               | Long Form Packet Transfer src and dst Operating Modes                                                                                                 | A-2                  |  |

|    | Δ2                                | Long-Form Packet Transfer Parameter Table Listings                                                                                                    | Δ-3                  |  |

# **Figures**

| 1–1  | Transfer Controller Block Diagram                                      | 1-4  |

|------|------------------------------------------------------------------------|------|

| 2–1  | Transfer Controller Request Prioritization                             | 2-2  |

| 2–2  | Crossbar Access Priority                                               | 2-6  |

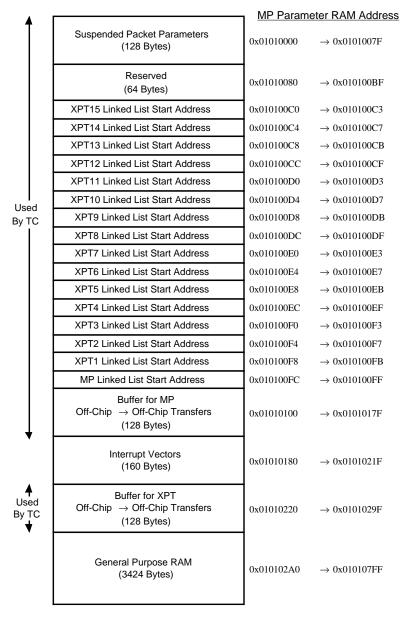

| 4–1  | MP Parameter RAM Contents                                              | 4-4  |

| 4–2  | PP Parameter RAM Contents                                              | 4-5  |

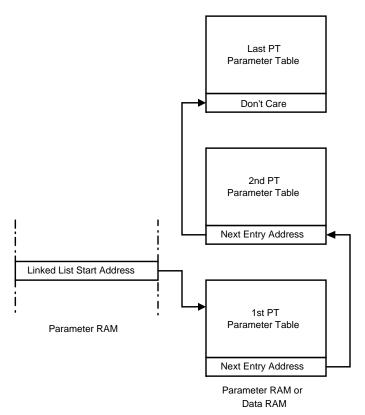

| 4–3  | Linked List Structure                                                  | 4-7  |

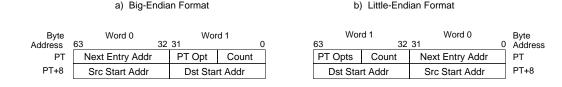

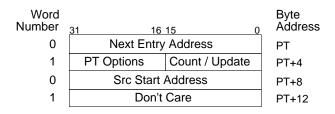

| 5–1  | Short-Form Parameter Table Format                                      | 5-3  |

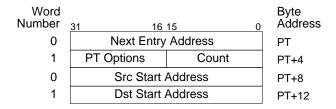

| 5–2  | Short-Form Parameter Table (Endian Independent)                        | 5-3  |

| 5–3  | Short Form PT Options Field                                            | 5-6  |

| 5–4  | Exchanging Short-Form src/dst Parameters (Big Endian)                  | 5-8  |

| 5–5  | Short-Form Reverse Addressing (Big Endian)                             | 5-10 |

| 5–6  | Short-Form Reverse Addressing (Little Endian)                          | 5-11 |

| 6–1  | Dimension Transfer Example                                             | 6-3  |

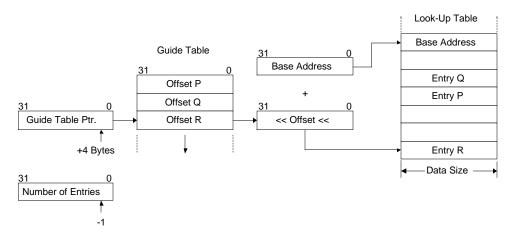

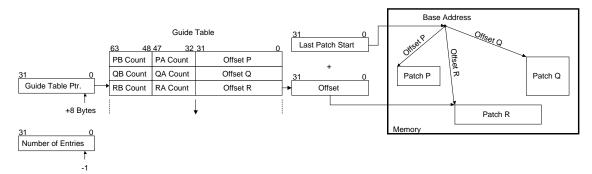

| 6–2  | Fixed-Patch Delta-Guided Transfer Mechanism                            | 6-6  |

| 6–3  | Fixed-Patch Offset-Guided Transfer Mechanism                           | 6-7  |

| 6–4  | Fixed-Patch Offset-Guided LUT Transfer Mechanism                       | 6-9  |

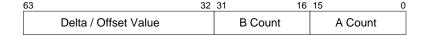

| 6–5  | Variable-Patch Guide Table Format (Big-Endian)                         | 6-9  |

| 6–6  | Variable-Patch Guide Table Format (Little Endian)                      | 6-10 |

| 6–7  | Variable-Patch Guide Table (Endian Independent)                        | 6-10 |

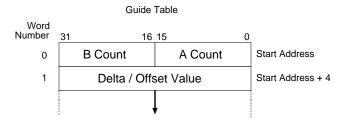

| 6–8  | Variable-Patch Delta-Guided Transfer Mechanism (Big -Endian)           | 6-11 |

| 6–9  | Variable-Patch Offset-Guided Transfer Mechanism (Big-Endian)           | 6-12 |

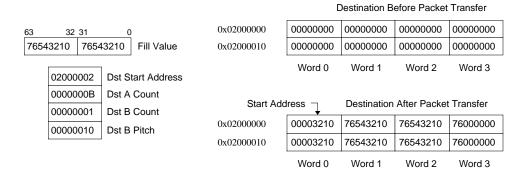

| 6–10 | Fill Transfer Example (Big-Endian)                                     | 6-13 |

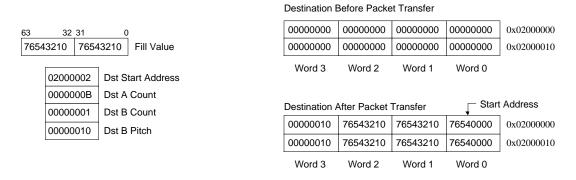

| 6–11 | Fill Transfer Example (Little-Endian)                                  | 6-13 |

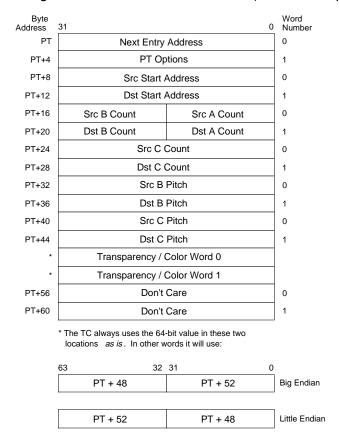

| 6–12 | Dimensioned src (with Transparency) to Dimensioned dst Parameter Table | 6-14 |

| 6–13 | Dimensioned src to Fixed-Patch Guided dst Parameter Table              | 6-15 |

| 6–14 | Dimensioned src to Variable-Patch Guided dst Parameter Table           |      |

| 6–15 | Fill-With-Value src to Dimensioned dst Parameter Table                 | 6-15 |

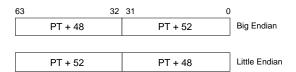

| 6–16 | General Long-Form Parameter Table Format (Endian-Independent)          | 6-16 |

| 6–17 | Long Form PT Options Field                                             | 6-22 |

| 6–18 | Exchanging Long-Form src/dst Parameters (Big Endian)                   | 6-29 |

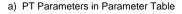

| 6–19 | Reverse src B Addressing Example                                       | 6-30 |

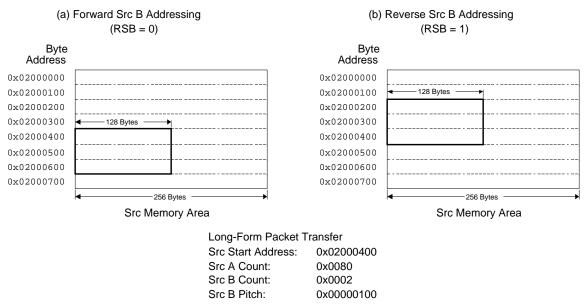

| 6–20 | Reverse src C Addressing                                               | 6-31 |

| 6–21 | Long-Form Reverse A Addressing (Big Endian)                            | 6-32 |

| 6–22 | Long-Form Reverse A Addressing (Little Endian)                         | 6-32 |

| 6–23 | Reverse dst B Addressing Example                                       | 6-33 |

| 6–24  | Reverse dst C Addressing                                                   | 6-34  |

|-------|----------------------------------------------------------------------------|-------|

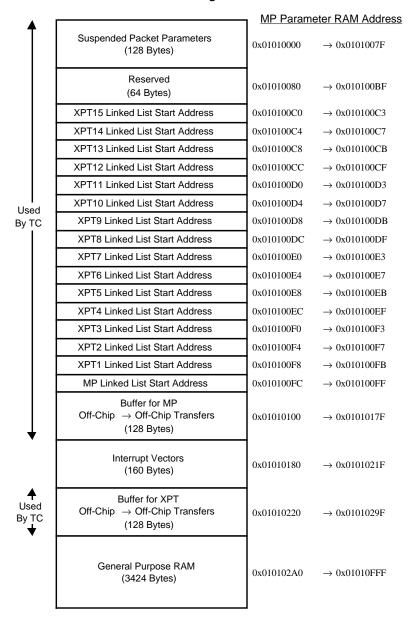

| 7–1   | XPT MP Parameter RAM Usage                                                 | 7-5   |

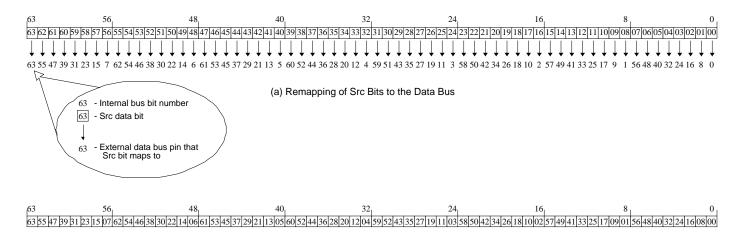

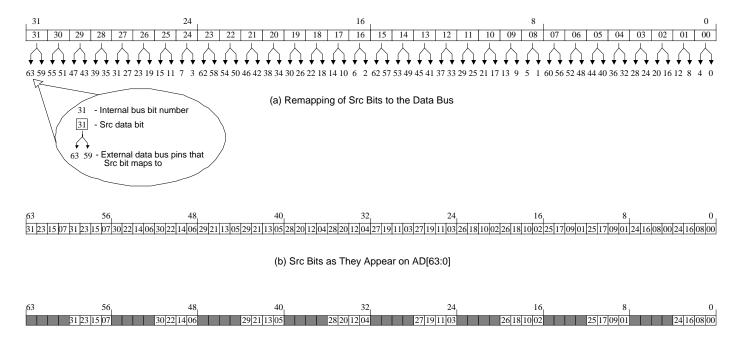

| 8–1   | 8x Block Write Output (Little Endian)                                      | 8-5   |

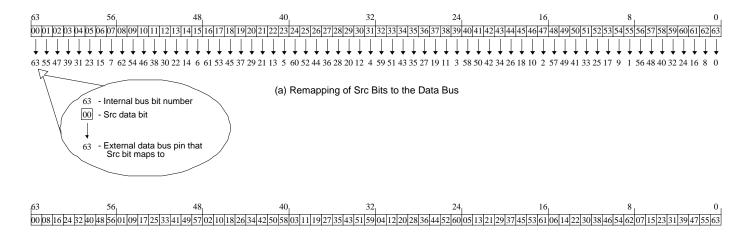

| 8–2   | 8x Block-Write Output (Big Endian)                                         | 8-6   |

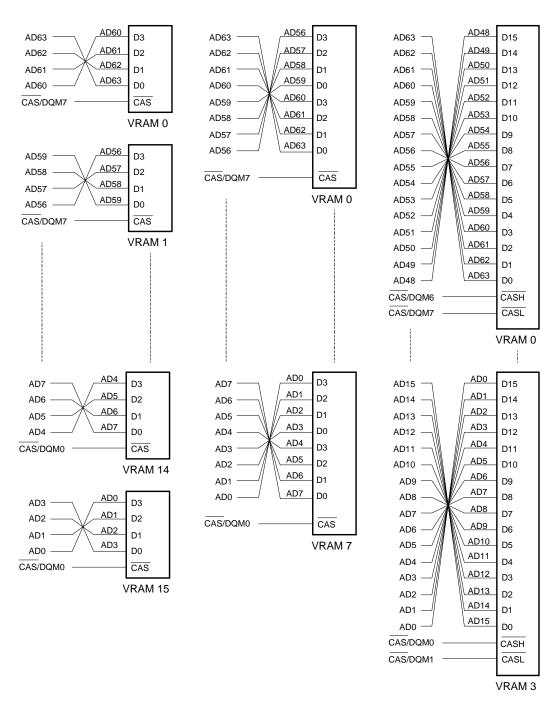

| 8–3   | Data Bus Connections for 4-bit, 8-bit, and 16-bit VRAMs in Big Endian Mode | 8-7   |

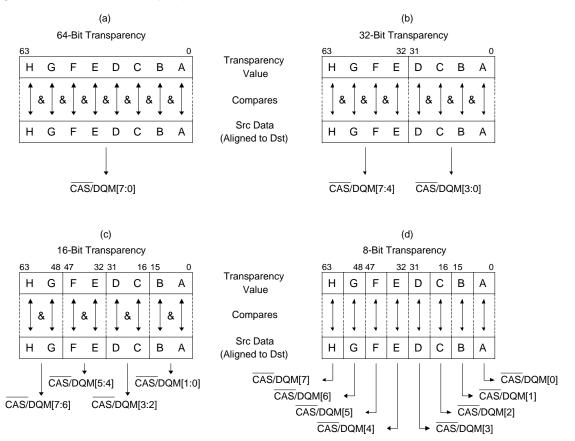

| 8–4   | 4x Block-Write Output (Little Endian)                                      | 8-10  |

| 8–5   | 4x Block-Write Output (Big Endian)                                         | 8-11  |

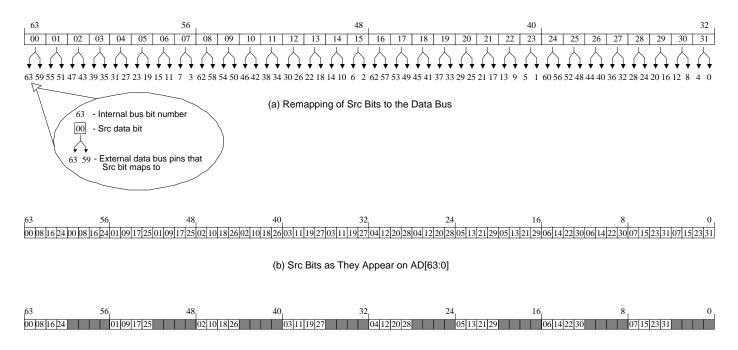

| 8–6   | Transparency Operation                                                     | 8-14  |

| 8–7   | Read Transfer Packet Transfer Parameters                                   | 8-17  |

| 9–1   | Packet Transfer Length Registers                                           | 9-4   |

| 9–2   | Suspended Long-Form Packet Parameters (Big Endian)                         | 9-10  |

| 9–3   | Suspended Long-Form Packet Transfer Parameters (Little Endian)             | 9-11  |

| 9–4   | Suspended Short-Form Packet Transfer Parameters (Big Endian)               | 9-12  |

| 9–5   | Suspended Short-Form Packet Transfer Parameters (Little Endian)            | 9-13  |

| 10–1  | General Form of an External Memory Access                                  | 10-3  |

| 10–2  | Cycle Configuration Cache Structure                                        | 10-5  |

| 10–3  | Cycle Configuration Cache Entry                                            | 10-7  |

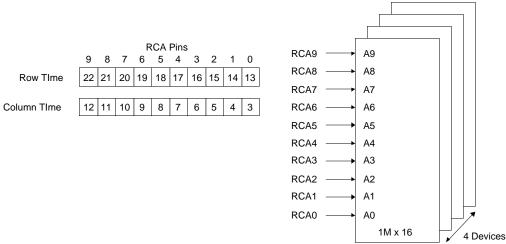

| 10–4  | Address Shift for 1M x 16 DRAM (64-bit Bus)                                | 10-15 |

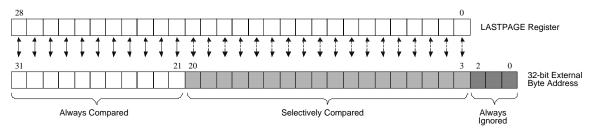

| 10–5  | Page Size Control                                                          | 10-1  |

| 10–6  | Memory Bank Size Address Masking                                           | 10-23 |

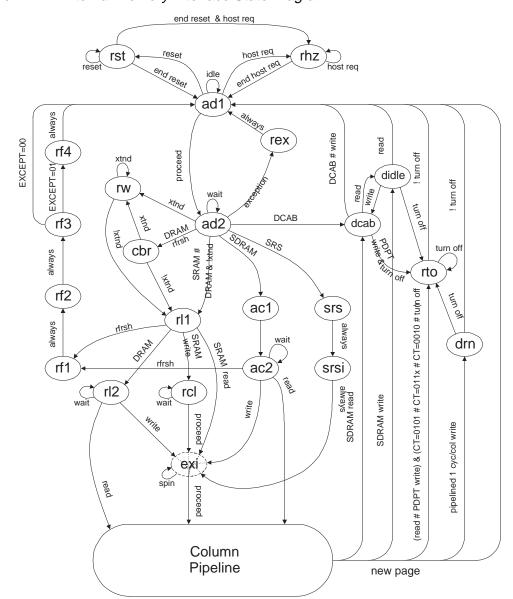

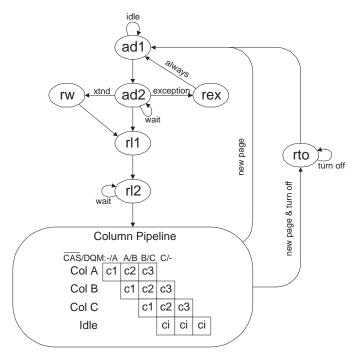

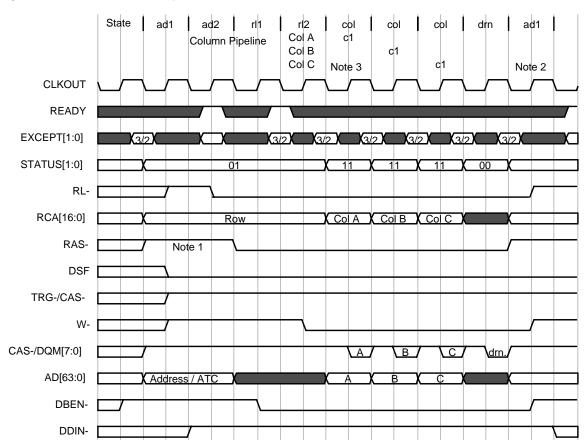

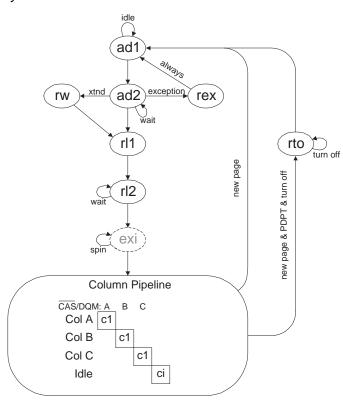

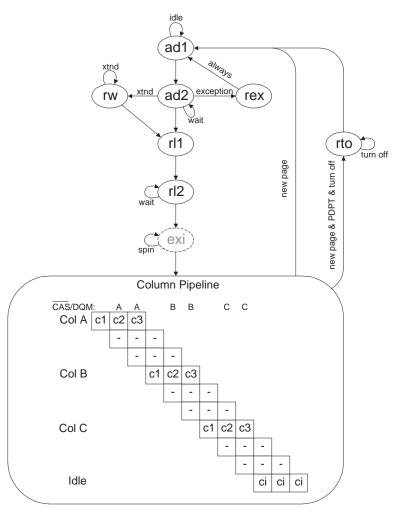

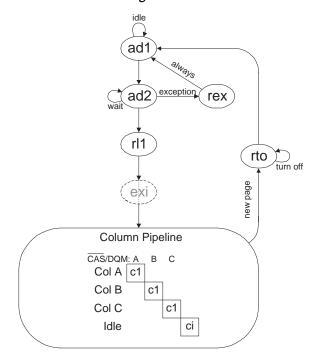

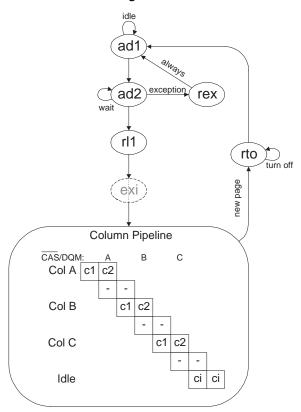

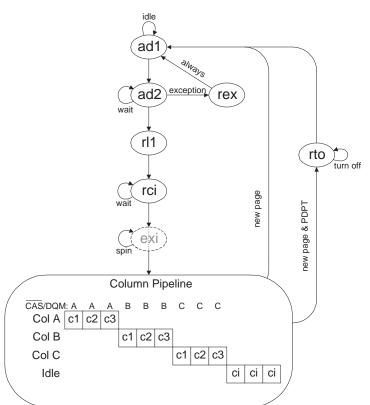

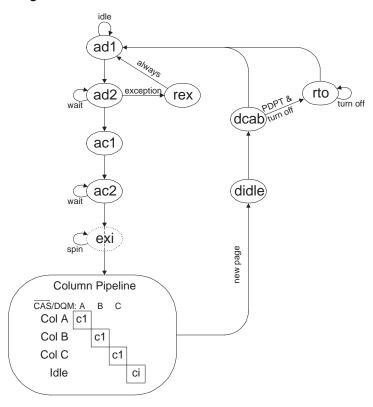

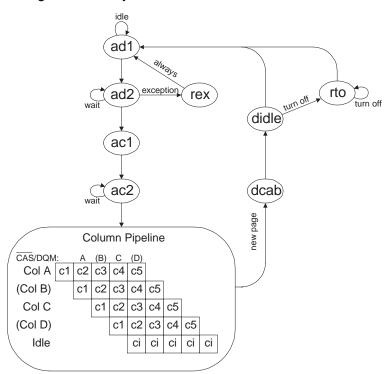

| 11–1  | External Memory Interface State Diagram                                    | 11-3  |

| 12–1  | Big-Endian 64-bit Bus Byte Positions                                       | 12-2  |

| 12–2  | Little-Endian 64-bit Bus Byte Positions                                    | 12-3  |

| 12–3  | Big-Endian 32-Bit Bus Byte Positions                                       | 12-3  |

| 12–4  | Little-Endian 32-bit Bus Byte Positions                                    | 12-4  |

| 12–5  | Big-Endian 16-Bit Bus Byte Positions                                       | 12-4  |

| 12–6  | Little-Endian 16-Bit Bus Byte Positions                                    | 12-5  |

| 12–7  | Big-Endian 8-Bit Bus Byte Positions                                        | 12-5  |

| 12–8  | Little-Endian 8-Bit Bus Byte Positions                                     | 12-5  |

| 12–9  | 64-Bit Big-Endian Transfer Example                                         | 12-8  |

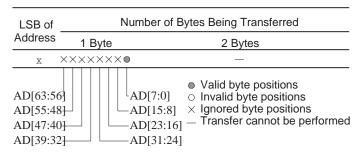

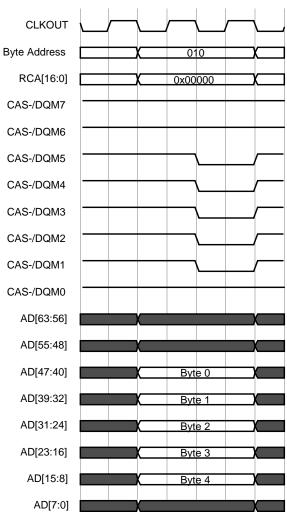

| 12–10 | 32-Bit Big-Endian Transfer Example                                         | 12-9  |

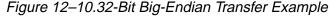

| 12–11 | 16-Bit Big-Endian Transfer Example                                         | 12-10 |

| 12–12 | 8-Bit Big-Endian Transfer Example                                          | 12-11 |

| 12–13 | 64-Bit Little-Endian Transfer Example                                      | 12-12 |

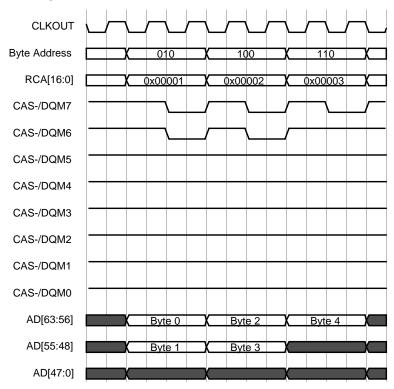

| 12–14 | 32-Bit Little-Endian Transfer Example                                      | 12-13 |

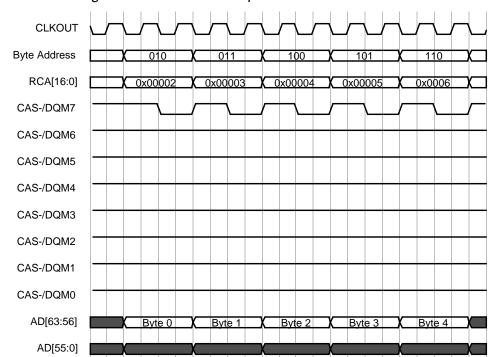

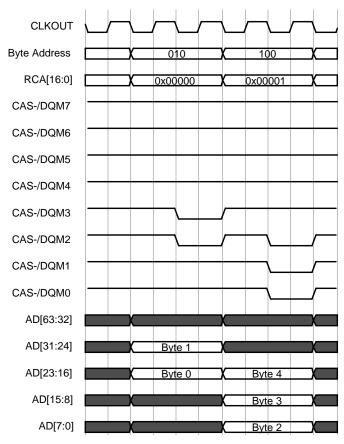

| 12–15 | 16-Bit Little-Endian Transfer Example                                      | 12-14 |

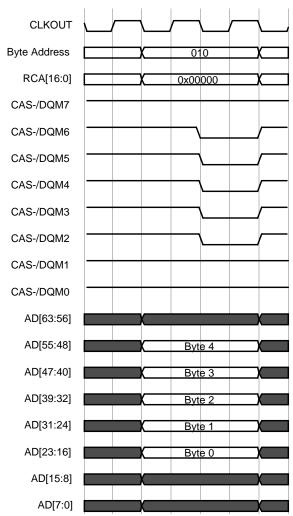

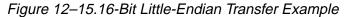

| 12–16 | 8-Bit Little-Endian Transfer Example                                       |       |

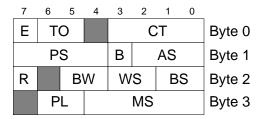

| 13–1  | Bank Configuration Data Format                                             |       |

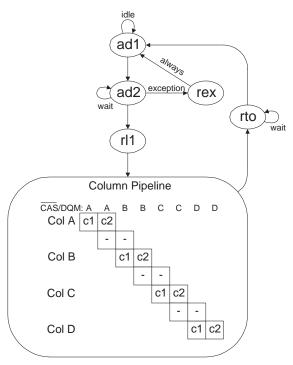

| 13–2  | Bank Configuration States                                                  | 13-3  |

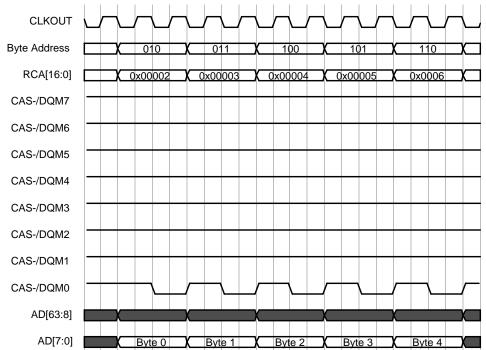

| 13–3  | Bank Configuration                                                         |       |

| 13–4  | Bank Configuration with Wait State and Extra Turn-Off                      |       |

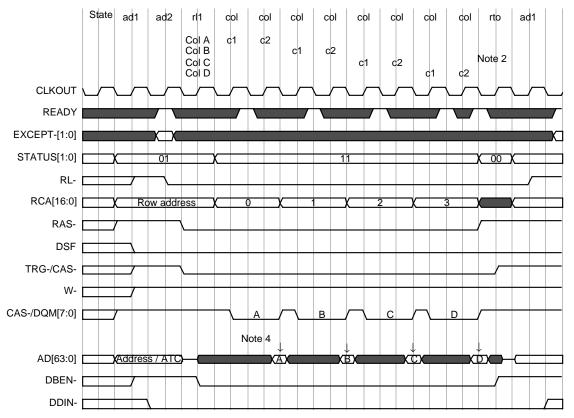

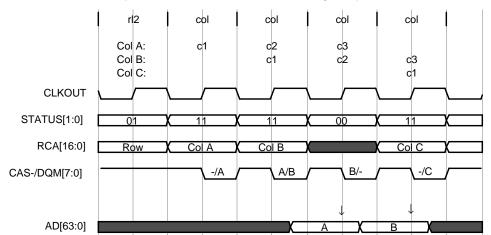

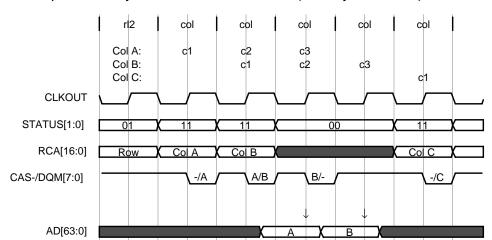

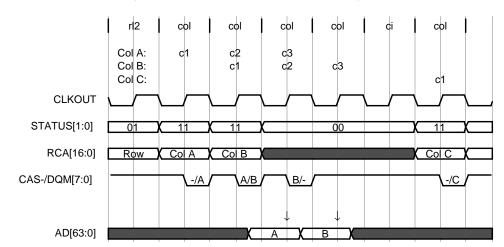

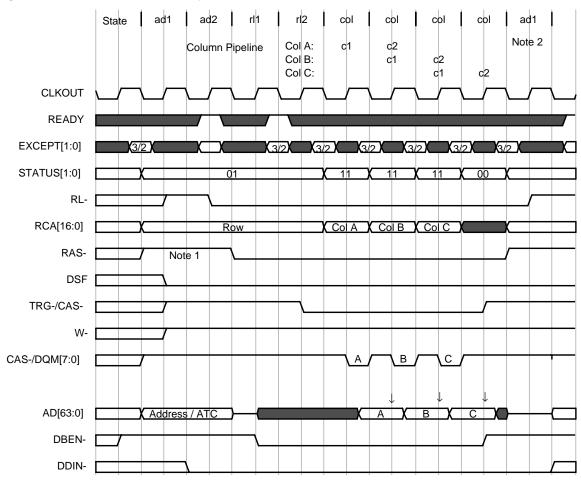

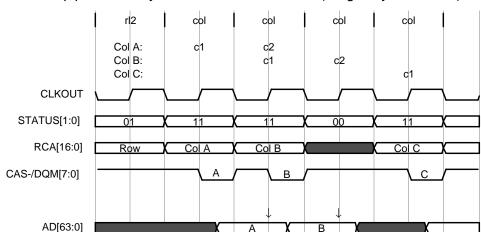

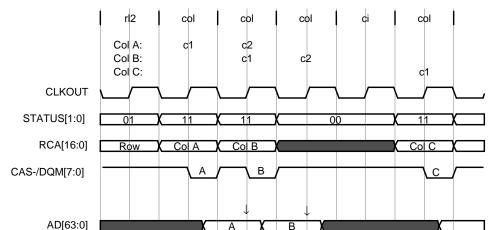

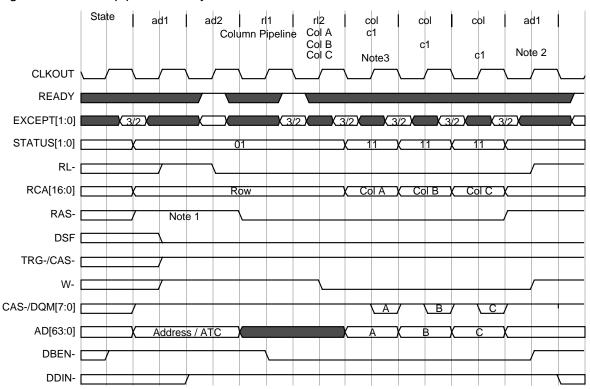

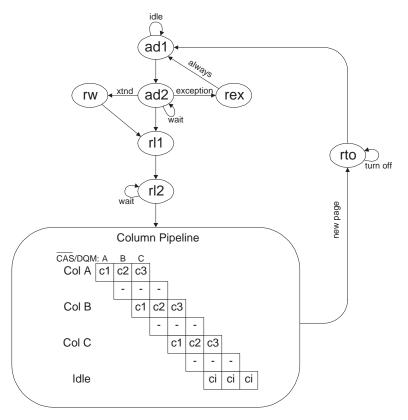

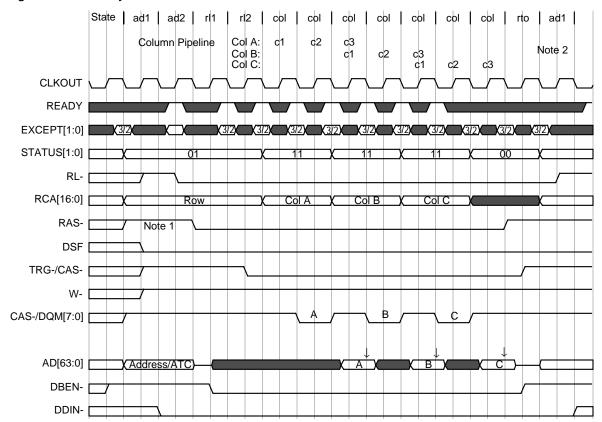

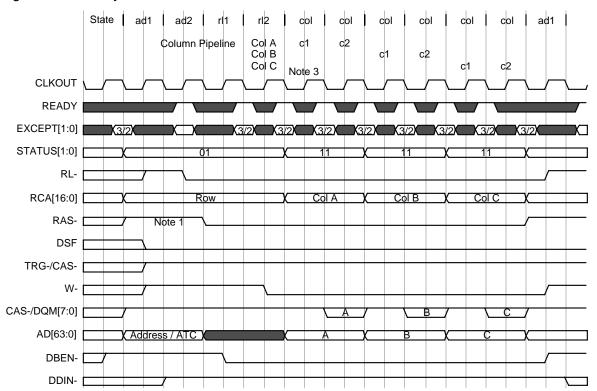

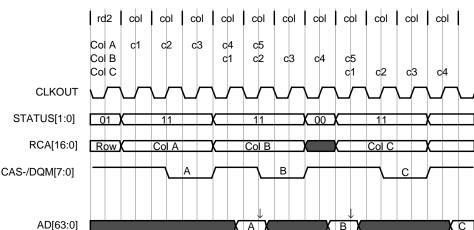

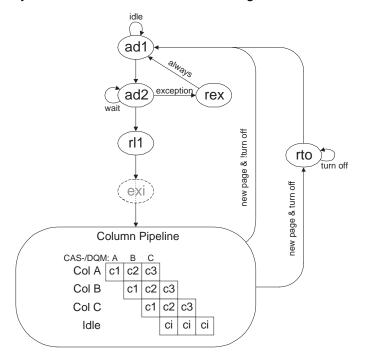

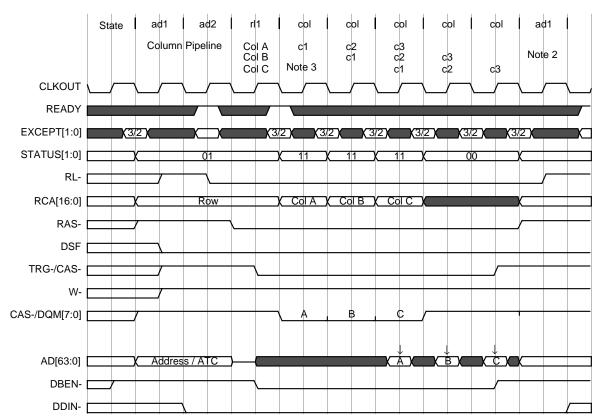

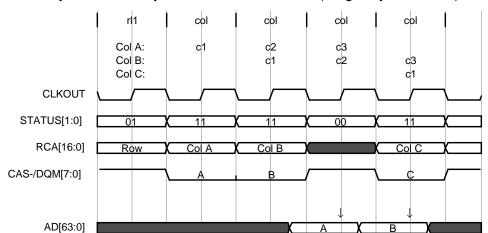

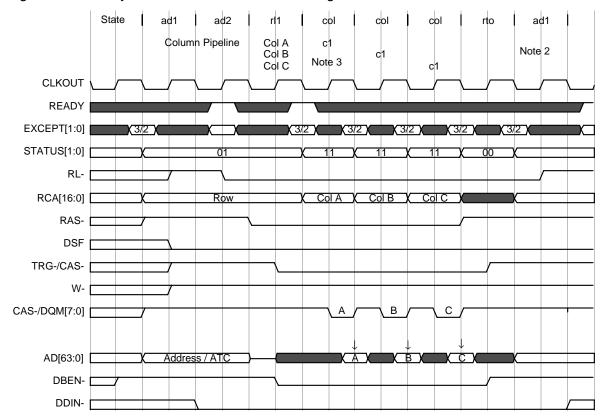

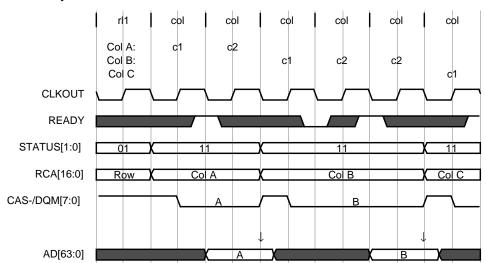

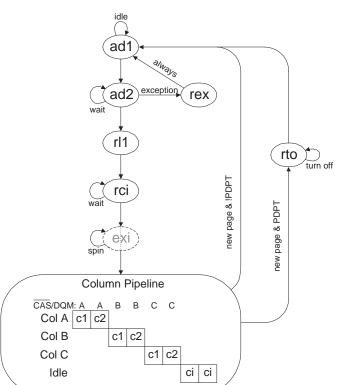

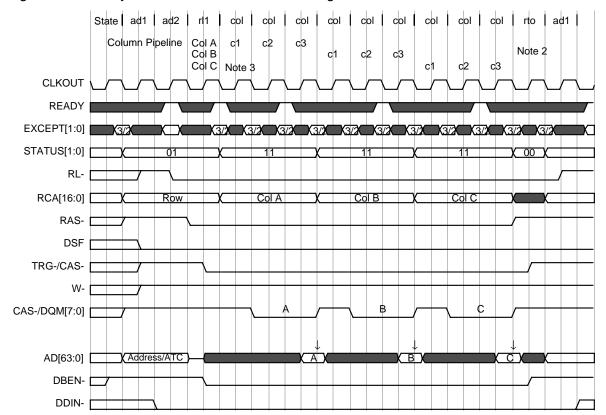

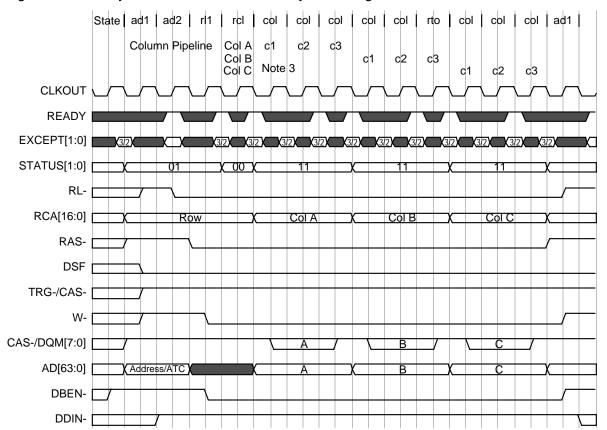

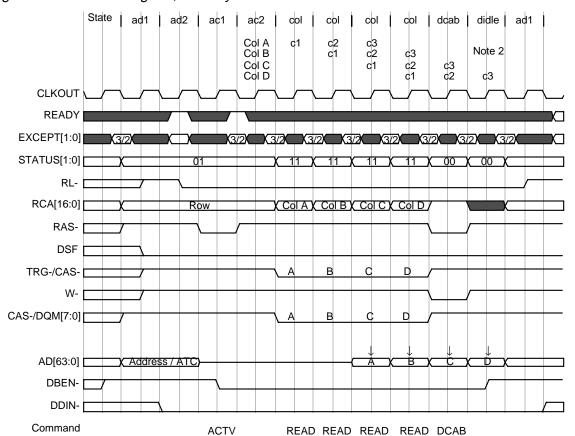

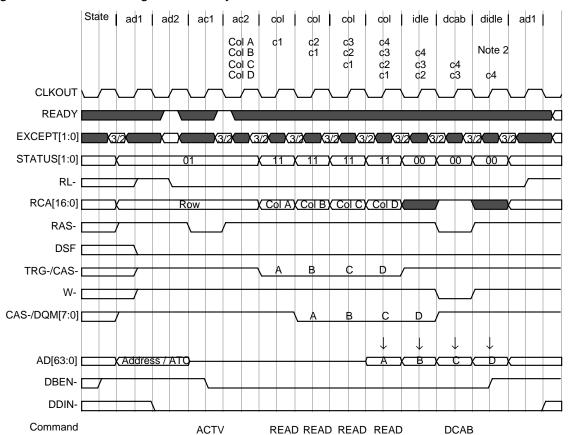

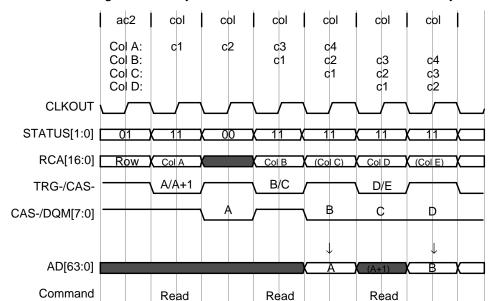

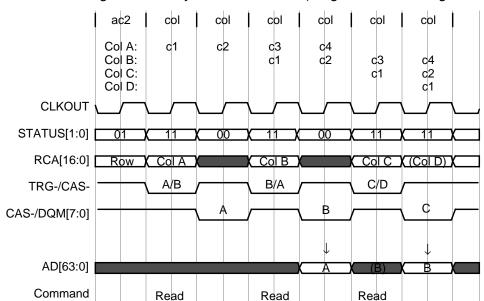

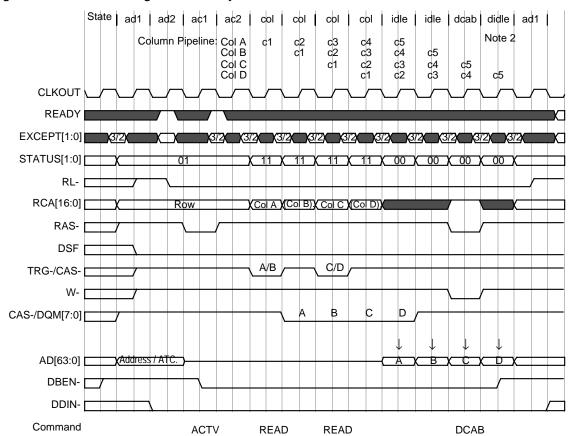

| 14–1  | Pipelined 1 Cycle/Column DRAM Read States                                | 14-5  |

|-------|--------------------------------------------------------------------------|-------|

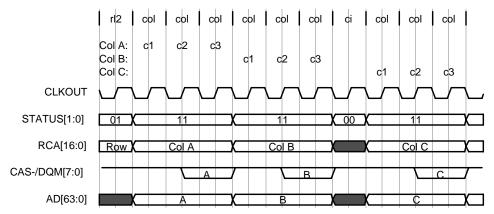

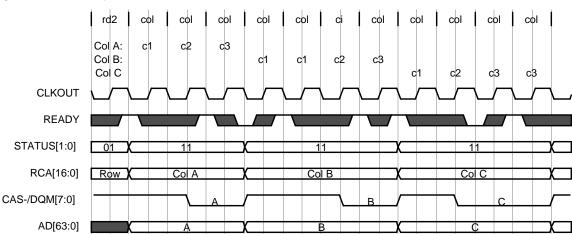

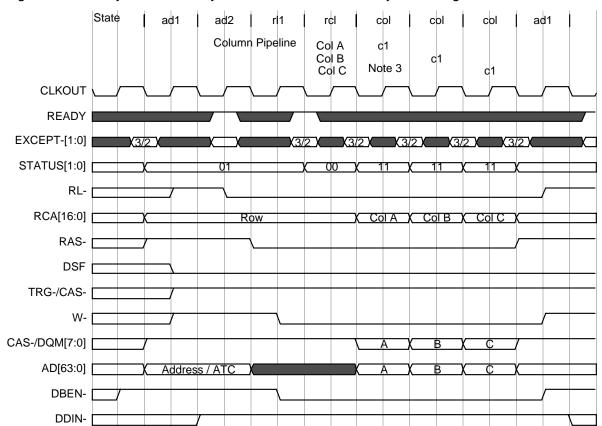

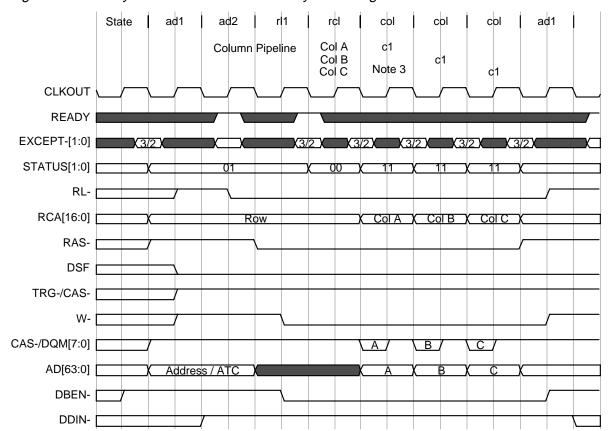

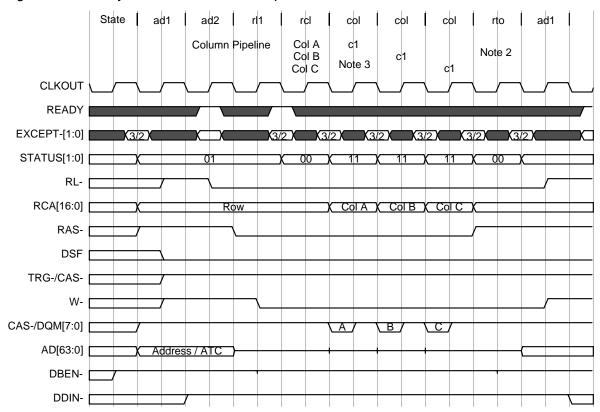

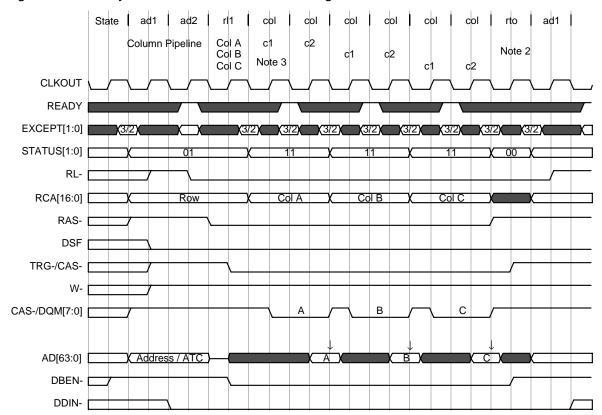

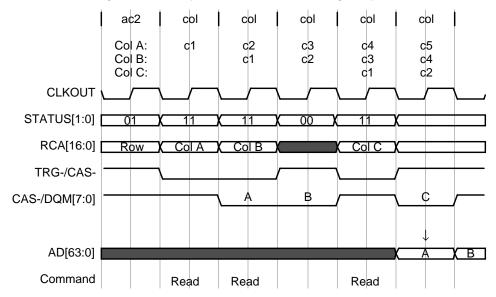

| 14–2  | Pipelined 1 Cycle/Column DRAM Read                                       | 14-7  |

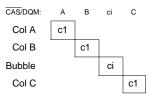

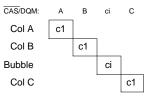

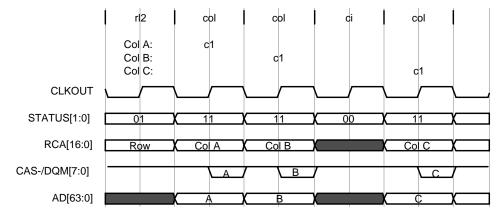

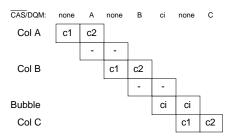

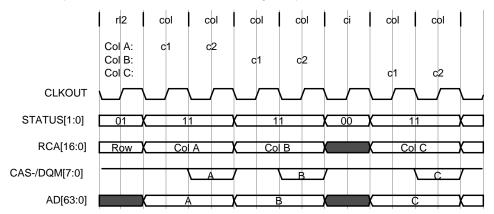

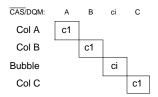

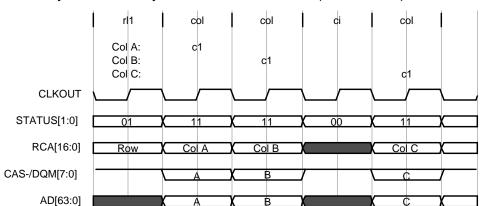

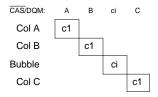

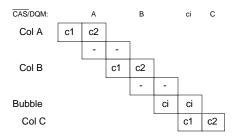

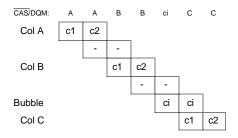

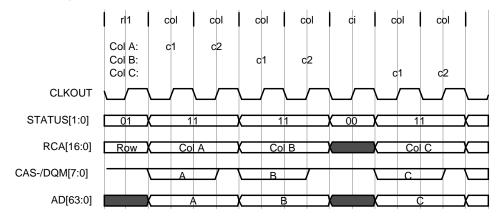

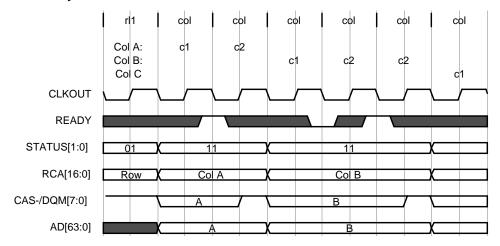

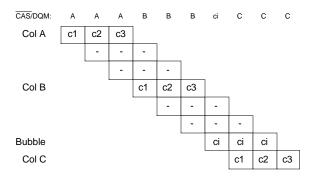

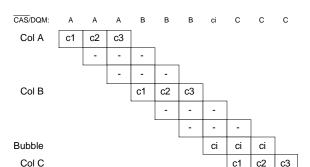

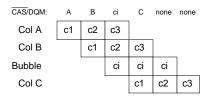

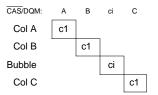

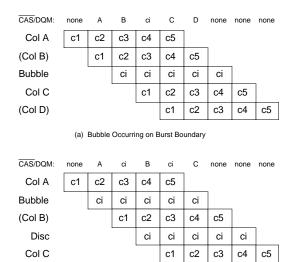

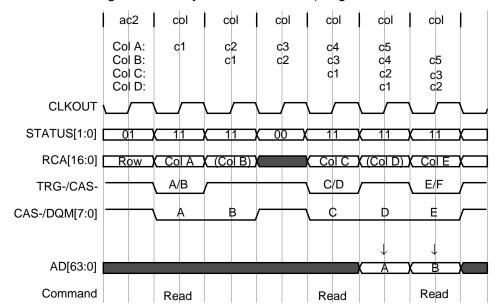

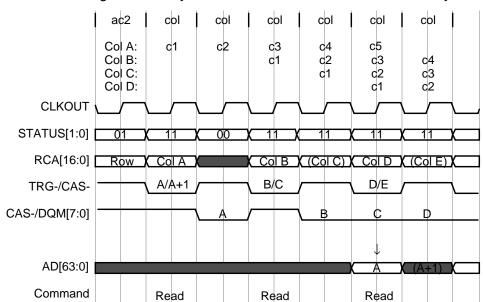

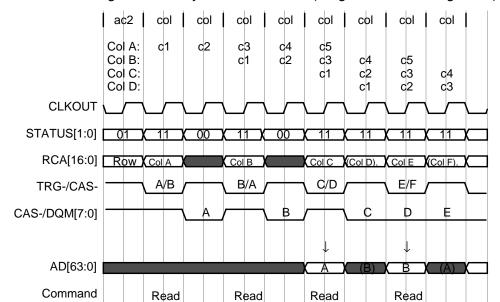

| 14–3  | Effect of Bubbles on Pipelined 1 Cycle/Column DRAM Read Column Pipeline  | 14-8  |

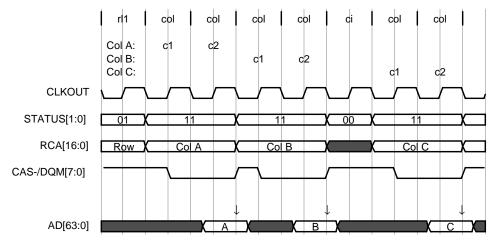

| 14–4  | Pipelined 1 Cycle/Column DRAM Read (Single Cycle Bubble)                 | 14-9  |

| 14–5  | Pipelined 1 Cycle/Column DRAM Read (Two-Cycle Bubble)                    | 14-10 |

| 14–6  | Pipelined 1 Cycle/Column DRAM Read (Multi-Cycle Bubble)                  | 14-11 |

| 14–7  | Pipelined 1 Cycle/Column DRAM Write States                               | 14-12 |

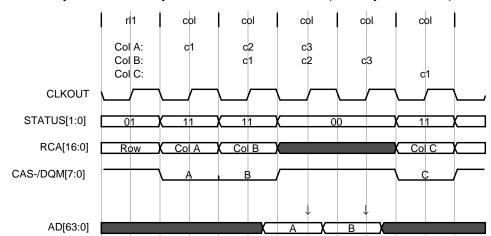

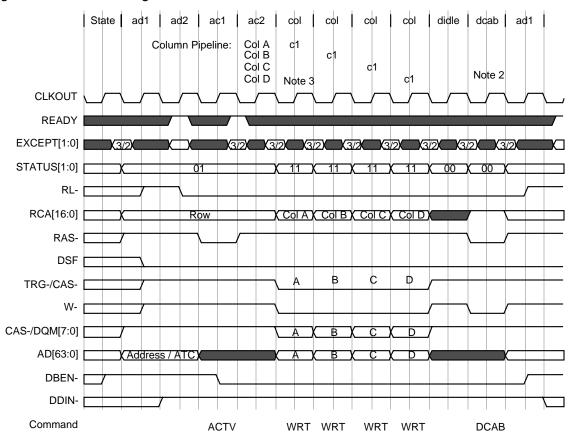

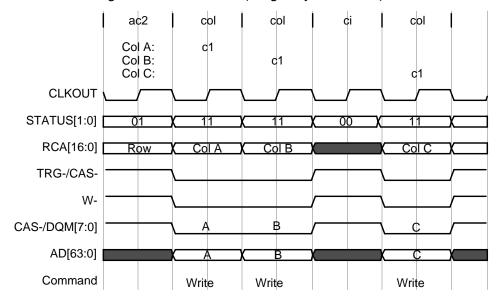

| 14–8  | Pipelined 1 Cycle/Column DRAM Write                                      | 14-14 |

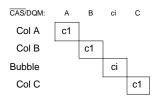

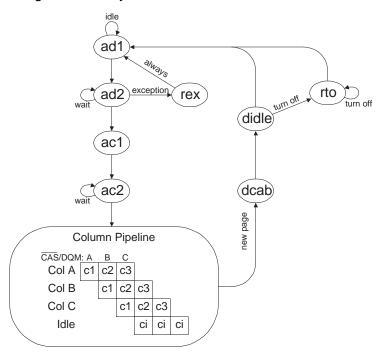

| 14–9  | Effect of Bubbles on Pipelined 1 Cycle/Column DRAM Write Column Pipeline | 14-15 |

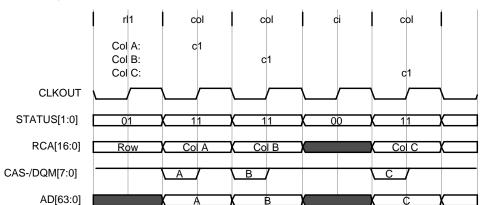

| 14–10 | Pipelined 1 Cycle/Column DRAM Write (With Bubble)                        | 14-15 |

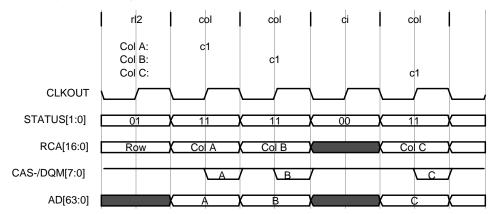

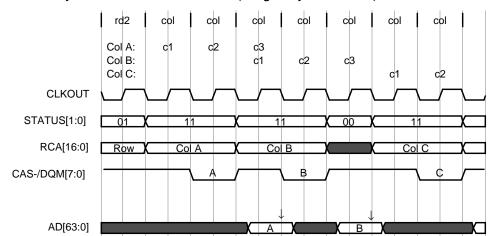

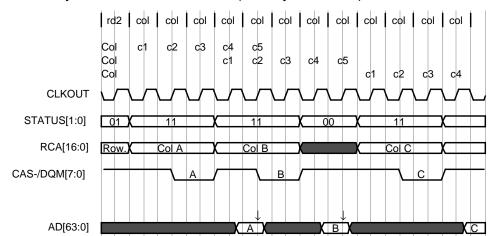

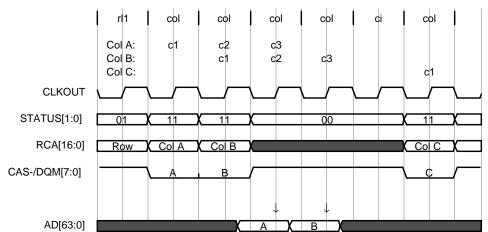

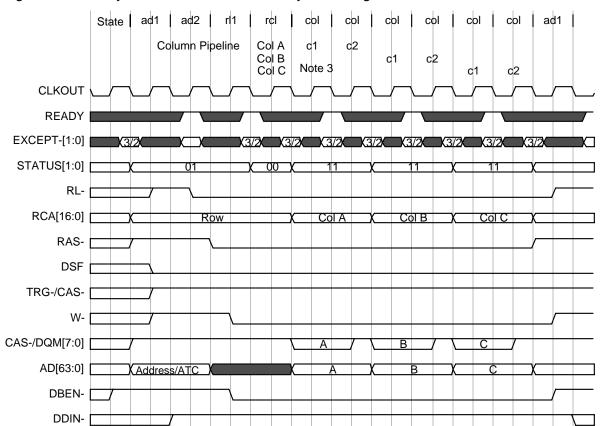

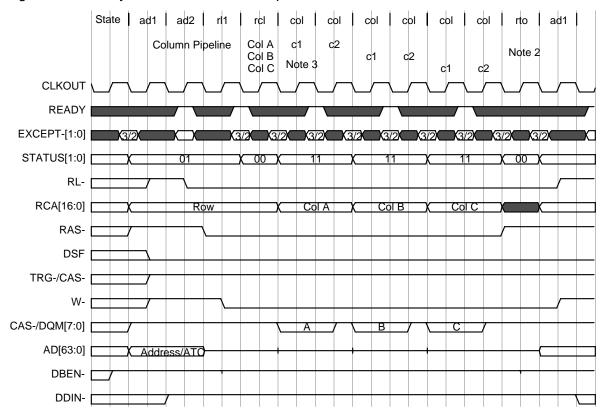

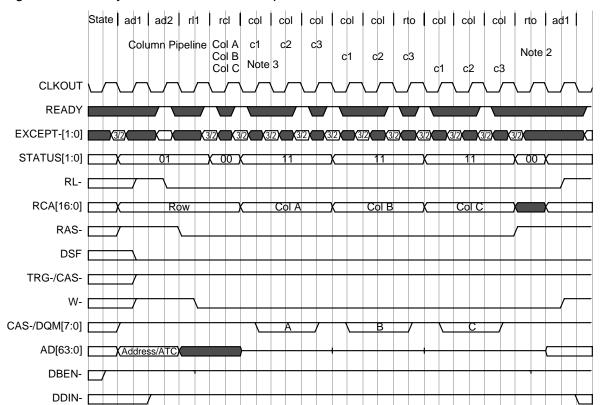

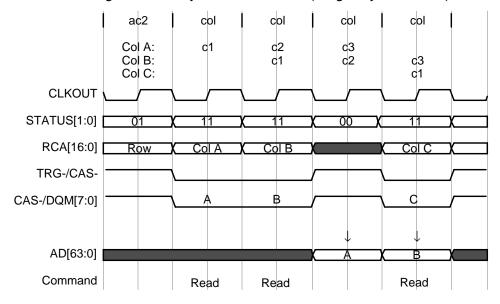

| 14–11 | Nonpipelined 1 Cycle/Column DRAM Read States                             | 14-16 |

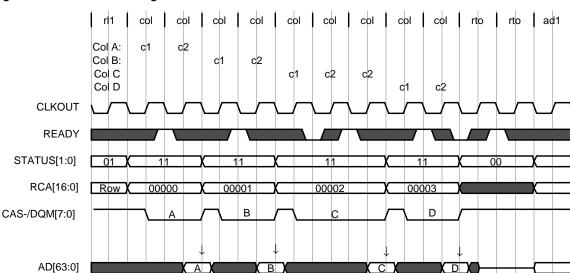

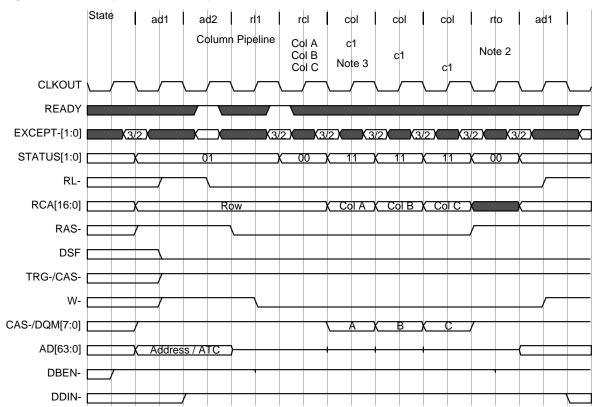

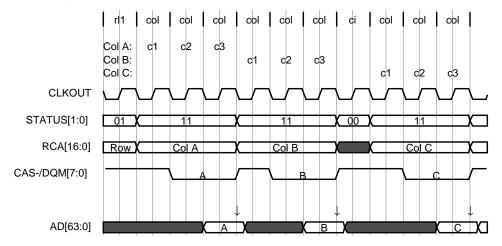

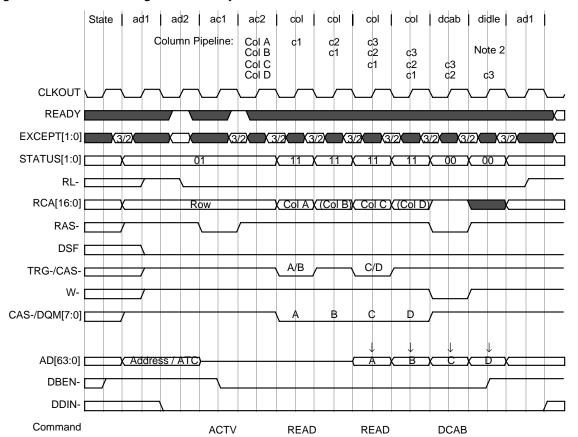

| 14–12 | Nonpipelined 1 Cycle/Column DRAM Read                                    | 14-18 |

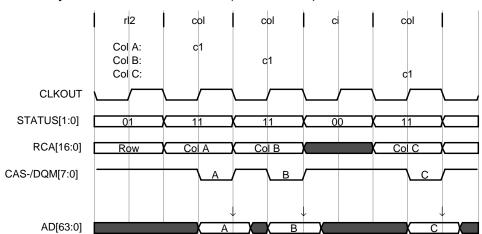

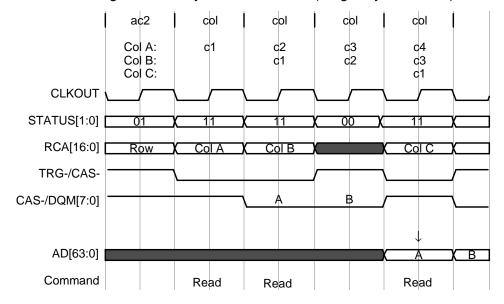

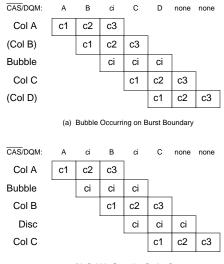

| 14–13 | Effect of Bubbles on Nonpipelined 1 Cyc/Col DRAM Read Column Pipeline    | 14-19 |

| 14–14 | Nonpipelined 1 Cycle/Column DRAM Read (Single-Cycle Bubble)              | 14-20 |

| 14–15 | Nonpipelined 1 Cycle/Col DRAM Read (Multi-Cycle Bubbles)                 | 14-21 |

| 14–16 | Nonpipelined 1 Cycle/Column DRAM Write States                            | 14-22 |

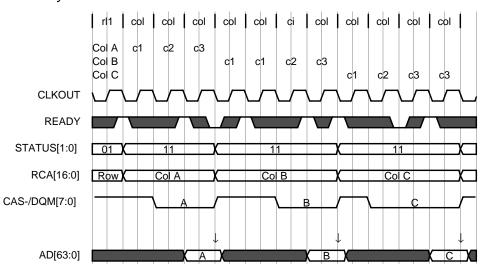

| 14–17 | Nonpipelined 1 Cycle/Column DRAM Write                                   | 14-23 |

| 14–18 | Effect of Bubbles on Nonpipelined 1 Cyc/Col DRAM Write Column Pipeline   | 14-24 |

| 14–19 | Nonpipelined 1 Cycle/Column DRAM Write (with Bubble)                     | 14-24 |

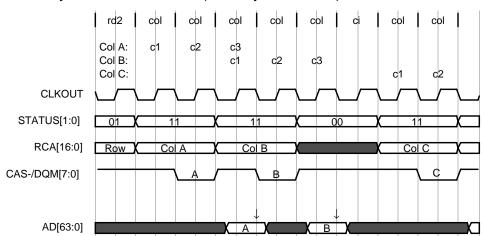

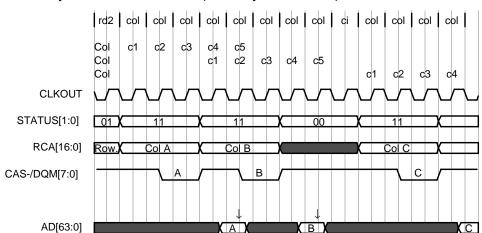

| 14–20 | 2 Cycle/Column DRAM Read States                                          | 14-25 |

| 14–21 | 2 Cycle/Column DRAM Read                                                 | 14-27 |

| 14–22 | Effect of Bubbles on 2 Cycle/Column DRAM Read Column Pipeline            | 14-28 |

| 14–23 | 2 Cycle/Column DRAM Read (Single-Cycle Bubble)                           | 14-29 |

| 14–24 | 2 Cycle/Col DRAM Read (Multi-Cycle Bubbles)                              | 14-30 |

| 14–25 | Effect of Wait States on 2 Cycle/Column DRAM Read Column Pipeline        | 14-31 |

| 14–26 | 2 Cycle/Column DRAM Read with Wait States                                | 14-32 |

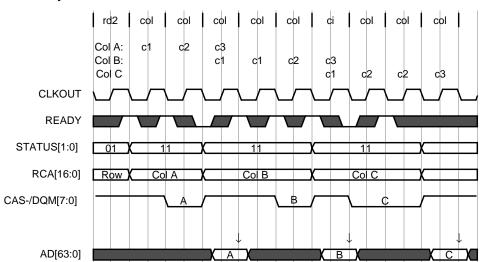

| 14–27 | 2 Cycle/Column DRAM Write States                                         | 14-33 |

| 14–28 | 2 Cycle/Column DRAM Write                                                | 14-35 |

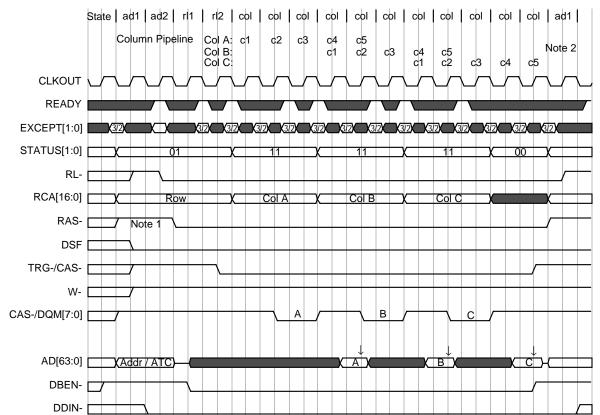

| 14–29 | Effect of Bubbles on 2 Cycle/Column DRAM Write Column Pipeline           | 14-36 |

| 14–30 | 2 Cycle/Column DRAM Write (Single-Cycle Bubble)                          | 14-36 |

| 14–31 | Effect of Wait States on 2 Cycle/Column DRAM Write Column Pipeline       | 14-37 |

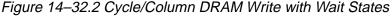

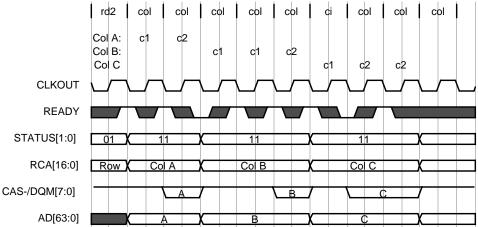

| 14–32 | 2 Cycle/Column DRAM Write with Wait States                               | 14-38 |

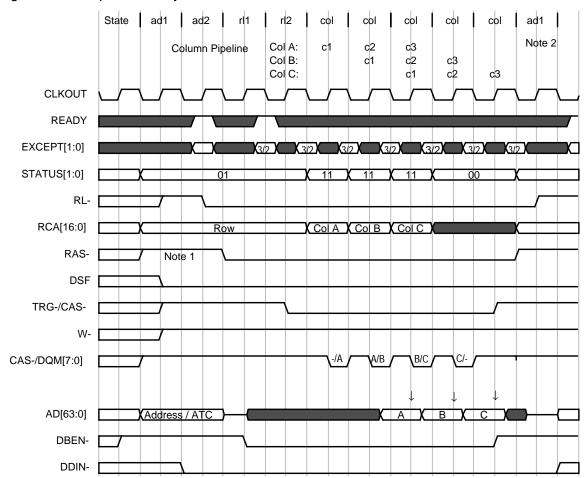

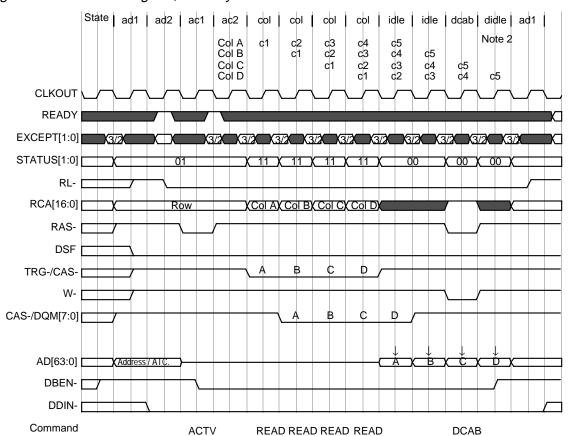

| 14–33 | 3 Cycle/Column DRAM Read States                                          | 14-40 |

| 14–34 | 3 Cycle/Column DRAM Read                                                 | 14-42 |

| 14–35 | Effect of Bubbles on 3 Cycle/Column DRAM Read Column Pipeline            | 14-43 |

| 14–36 | 3 Cycle/Column DRAM Read (Single-Cycle Bubble)                           | 14-44 |

| 14–37 | 3 Cycle/Column DRAM Read (Two-Cycle Bubble)                              | 14-45 |

| 14–38 | 3 Cycle/Col DRAM Read (Multi-Cycle Bubbles)                              |       |

| 14–39 | Effect of Wait States on 3 Cycle/Column DRAM Read Column Pipeline        | 14-47 |

| 14–40 | 3 Cycle/Column DRAM Read with Wait States                                | 14-48 |

| 14–41 | 3 Cycle/Column DRAM Write States                                         | 14-49 |

| 14–42 | 3 Cycle/Column DRAM Write                                           | 14-51 |

|-------|---------------------------------------------------------------------|-------|

| 14–43 | Effect of Bubbles on 3 Cycle/Column DRAM Write Column Pipeline      | 14-52 |

| 14–44 | 3 Cycle/Column DRAM Write (with Bubble)                             | 14-52 |

| 14–45 | Effect of Wait States on 3 Cycle/Column DRAM Write Column Pipeline  | 14-53 |

| 14–46 | 3 Cycle/Column DRAM Write with Wait States                          | 14-54 |

| 15–1  | 1 Cycle/Column Synchronous SRAM Read State Diagram                  | 15-5  |

| 15–2  | 1 Cycle/Column Synchronous SRAM Read Timing                         | 15-7  |

| 15–3  | Effect of Bubbles on 1 Cycle/Column Synchronous SRAM Read Pipeline  | 15-8  |

| 15–4  | 1 Cycle/Column Synchronous SRAM Read (Single Cycle Bubble)          | 15-9  |

| 15–5  | 1 Cycle/Column Synchronous SRAM Read (Two-Cycle Bubble)             | 15-10 |

| 15–6  | 1 Cycle/Column Synchronous SRAM Read (Multi-Cycle Bubble)           | 15-11 |

| 15–7  | 1 Cycle/Column Synchronous SRAM Write States                        | 15-12 |

| 15–8  | 1 Cycle/Column Synchronous SRAM Write Cycle Timing                  | 15-14 |

| 15–9  | 1 Cycle/Column Synchronous SRAM Peripheral Device Write             | 15-15 |

| 15–10 | Effect of Bubbles on 1 Cycle/Column Synchronous SRAM Write Pipeline | 15-15 |

| 15–11 | 1 Cycle/Column Synchronous SRAM Write (With Bubble)                 | 15-16 |

| 15–12 | 1 Cycle/Column SRAM Read State Diagram                              | 15-17 |

| 15–13 | 1 Cycle/Column SRAM Read Timing                                     | 15-19 |

| 15–14 | Effect of Bubbles on 1 Cycle/Column SRAM Read Pipeline              | 15-19 |

| 15–15 | 1 Cycle/Column SRAM Read (With Bubble)                              | 15-20 |

| 15–16 | 1 Cycle/Column SRAM Write States                                    | 15-21 |

| 15–17 | 1 Cycle/Column SRAM Write Cycle Timing                              | 15-23 |

| 15–18 | 1 Cycle/Column SRAM Peripheral Device Write                         | 15-24 |

| 15–19 | Effect of Bubbles on 1 Cycle/Column SRAM Write Pipeline             | 15-24 |

| 15–20 | 1 Cycle/Column SRAM Write (With Bubble)                             | 15-25 |

| 15–21 | 2 Cycle/Column SRAM Read State Diagram                              | 15-27 |

| 15–22 | 2 Cycle/Column SRAM Read Timing                                     | 15-29 |

| 15–23 | Effect of Bubbles on 2 Cycle/Column SRAM Read Pipeline              | 15-30 |

| 15–24 | 2 Cycle/Column SRAM Read (With Bubble)                              | 15-30 |

| 15–25 | Effect of Wait States on 2 Cycle/Column SRAM Read Pipeline          | 15-31 |

| 15–26 | 2 Cycle/Column SRAM Read with Wait State                            | 15-32 |

| 15–27 | 2 Cycle/Column SRAM Write States                                    | 15-33 |

| 15–28 | 2 Cycle/Column SRAM Write Cycle Timing                              | 15-35 |

| 15–29 | 2 Cycle/Column SRAM Peripheral Device Write                         | 15-36 |

| 15-30 | Effect of Bubbles on 2 Cycle/Column SRAM Write Pipeline             | 15-37 |

| 15–31 | 2 Cycle/Column SRAM Write (With Bubble)                             | 15-37 |

| 15–32 | Effect of Wait States on 2 Cycle/Column Write Pipeline              | 15-38 |

| 15–33 | 2 Cycle/Column Write with Wait State                                | 15-39 |

| 15–34 | 3 Cycle/Column SRAM Read State Diagram                              | 15-41 |

| 15–35 | 3 Cycle/Column SRAM Read Timing                                     | 15-43 |

| 15–36 | Effect of Bubbles on 3 Cycle/Column SRAM Read Pipeline              | 15-44 |

| 15–37 | 3 Cycle/Column SRAM Read (With Bubble)                                    | . 15-44 |

|-------|---------------------------------------------------------------------------|---------|

| 15–38 | Effect of Wait States on 3 Cycle/Column SRAM Read Pipeline                | . 15-45 |

| 15–39 | 3 Cycle/Column SRAM Read with Wait State                                  | . 15-46 |

| 15–40 | 3 Cycle/Column SRAM Write States                                          | . 15-47 |

| 15–41 | 3 Cycle/Column SRAM Write Cycle Timing                                    | . 15-49 |

| 15–42 | 3 Cycle/Column SRAM Peripheral Device Write                               | . 15-50 |

| 15–43 | Effect of Bubbles on 3 Cycle/Column SRAM Write Pipeline                   |         |

| 15–44 | 3 Cycle/Column SRAM Write (With Bubble)                                   | . 15-51 |

| 15–45 | Effect of Wait States on 3 Cycle/Column Write Pipeline                    | . 15-52 |

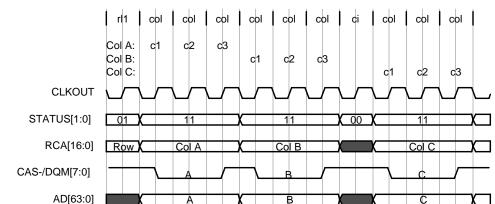

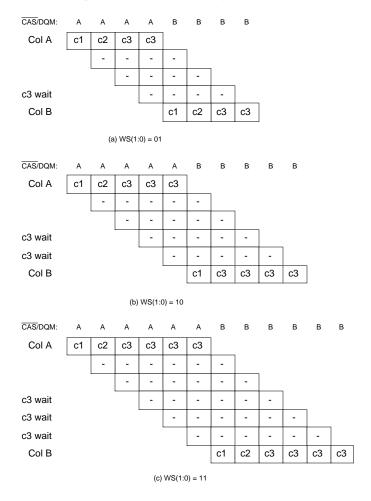

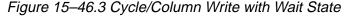

| 15–46 | 3 Cycle/Column Write with Wait State                                      | . 15-53 |

| 16–1  | SDRAM Power-Up DCAB State Sequence                                        | 16-5    |

| 16–2  | SDRAM DCAB                                                                | 16-6    |

| 16–3  | MRS Value Generation                                                      | 16-7    |

| 16–4  | SDRAM MRS State Sequence                                                  | 16-8    |

| 16–5  | SDRAM MRS                                                                 | 16-9    |

| 16–6  | SDRAM Burst Length 1, Latency 2 Read States                               | . 16-10 |

| 16–7  | Burst Length 1, Latency 2 SDRAM Read                                      | . 16-12 |

| 16–8  | Effect of Bubbles on Burst Length 1, Latency 2 SDRAM Read Column Pipeline | . 16-13 |

| 16–9  | Burst Length 1, Latency 2 SDRAM Read (Single Cycle Bubble)                | . 16-13 |

| 16–10 | SDRAM Burst Length 1, Latency 3 Read States                               | . 16-14 |

| 16–11 | Burst Length 1, Latency 3 SDRAM Read                                      | . 16-16 |

| 16–12 | Effect of Bubbles on Burst Length 1, Latency 3 SDRAM Read Column Pipeline | . 16-17 |

| 16–13 | Burst Length 1, Latency 3 SDRAM Read (Single Cycle Bubble)                | . 16-17 |

| 16–14 | SDRAM Burst Length 1, Latency 4 Read States                               | . 16-18 |

| 16–15 | Burst Length 1, Latency 4 SDRAM Read                                      | . 16-20 |

| 16–16 | Effect of Bubbles on Burst Length 1, Latency 4 SDRAM Read Column Pipeline | . 16-21 |

| 16–17 | Burst Length 1, Latency 4 SDRAM Read (Single Cycle Bubble)                | . 16-21 |

| 16–18 | SDRAM Burst Length 1, Write States                                        | . 16-22 |

| 16–19 | Burst Length 1 SDRAM Write                                                | . 16-24 |

| 16–20 | Effect of Bubbles on Burst Length 1, SDRAM Write Column Pipeline          | . 16-25 |

| 16–21 | Burst Length 1, SDRAM Write (Single Cycle Bubble)                         | . 16-25 |

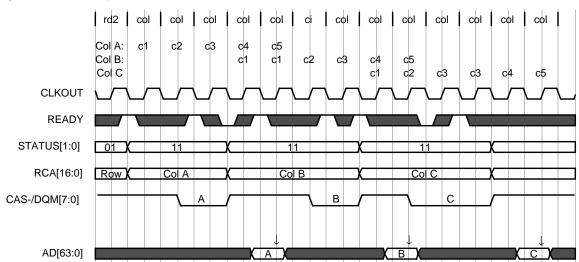

| 16–22 | SDRAM Burst Length 2, Latency 2 Read States                               | . 16-27 |

| 16-23 | Burst Length 2, Latency 2 SDRAM Read                                      | . 16-29 |

| 16–24 | Effect of Bubbles on Burst Length 2, Latency 2 SDRAM Read Column Pipeline | . 16-30 |

| 16–25 | Burst Length 2, Latency 2 SDRAM Read (Single Bubble Between Bursts)       | . 16-31 |

| 16–26 | Burst Length 2 Latency 2 SDRAM Read with Burst Discontinuity              | . 16-32 |

| 16–27 | Burst Length 2, Latency 2 SDRAM Read (Single Bubble During Burst)         | . 16-33 |

| 16–28 | SDRAM Burst Length 2, Latency 3 Read States                               | . 16-34 |

| 16–29 | Burst Length 2, Latency 3 SDRAM Read                                      | . 16-36 |

| 16–30 | Effect of Bubbles on Burst Length 2, Latency 3 SDRAM Read Column Pipeline | . 16-37 |

| 16–31 | Burst Length 2, Latency 3 SDRAM Read (Single Bubble Between Bursts)       | . 16-38 |

| 16–32 | Burst Length 2 Latency 3 SDRAM Read with Burst Discontinuity              | 16-39 |

|-------|---------------------------------------------------------------------------|-------|

| 16–33 | Burst Length 2, Latency 3 SDRAM Read (Single Bubble During Burst)         | 16-40 |

| 16–34 | SDRAM Burst Length 2, Latency 4 Read States                               | 16-41 |

| 16–35 | Burst Length 2, Latency 4 SDRAM Read                                      | 16-43 |

| 16–36 | Effect of Bubbles on Burst Length 2, Latency 4 SDRAM Read Column Pipeline | 16-44 |

| 16–37 | Burst Length 2, Latency 4 SDRAM Read (Single Bubble Between Bursts)       | 16-45 |

| 16–38 | Burst Length 2 Latency 4 SDRAM Read with Burst Discontinuity              | 16-46 |

| 16–39 | Burst Length 2, Latency 4 SDRAM Read (Single Bubble During Burst)         | 16-47 |

| 16–40 | SDRAM Burst Length 2, Write States                                        | 16-48 |

| 16–41 | Burst Length 2 SDRAM Write                                                | 16-50 |

| 16–42 | Effect of Bubbles on Burst Length 2, SDRAM Write Column Pipeline          | 16-51 |

| 16–43 | Burst Length 2 SDRAM Write (Single Cycle Bubble)                          | 16-52 |

| 16–44 | Burst Length 2 SDRAM Write with Burst Discontinuity                       | 16-53 |

| 16–45 | Burst Length 2 SDRAM Write (Single Bubble During Burst)                   | 16-54 |

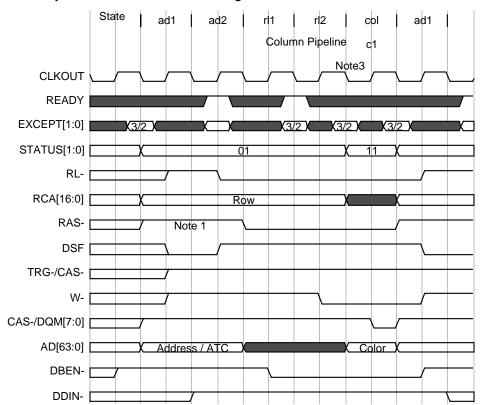

| 17–1  | 1 Cycle/Column Load Color Register                                        | 17-3  |

| 17–2  | 2 Cycle/Column Load Color Register                                        | 17-4  |

| 17–3  | 3 Cycle/Column Load Color Register                                        | 17-5  |

| 17–4  | Pipelined 1 Cycle/Column Block-Write                                      | 17-7  |

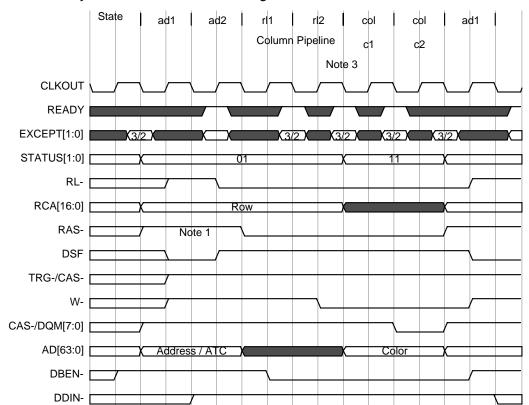

| 17–5  | Nonpipelined 1 Cycle/Column Block-Write                                   | 17-8  |

| 17–6  | 2 Cycle/Column Block-Write                                                | 17-9  |

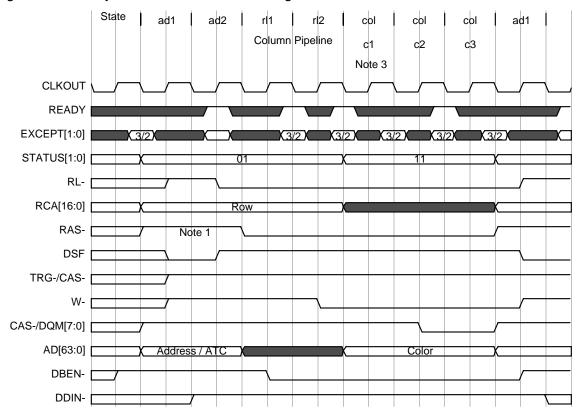

| 17–7  | 3 Cycle/Column Block-Write                                                | 17-10 |

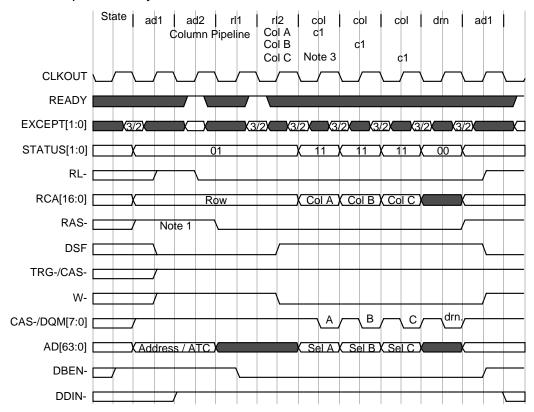

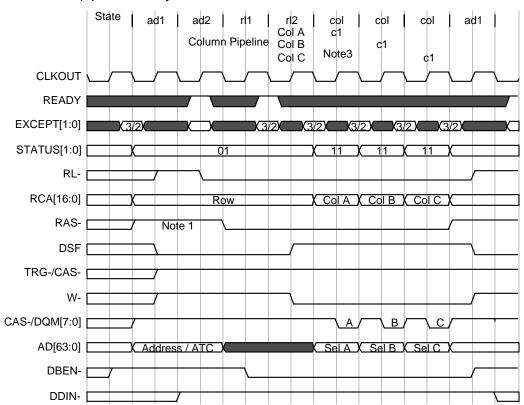

| 17–8  | 1 Cycle/Column Read or Split-Read Transfer                                | 17-12 |

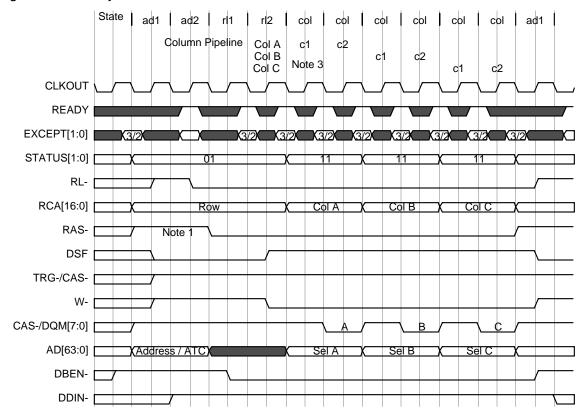

| 17–9  | 2 Cycle/Column Read or Split-Read Transfer                                | 17-13 |

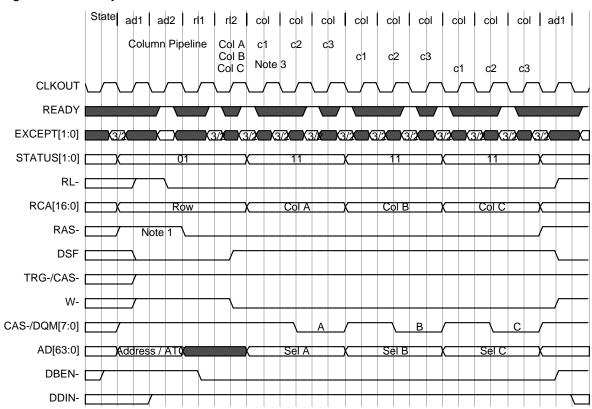

| 17–10 | 3 Cycle/Column Read or Split-Read Transfer                                | 17-14 |

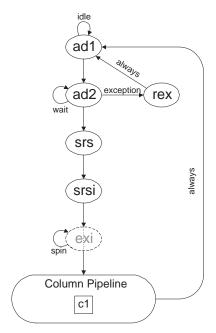

| 18–1  | Special Register Set Address Output                                       | 18-2  |

| 18–2  | Special Register Set States                                               | 18-3  |

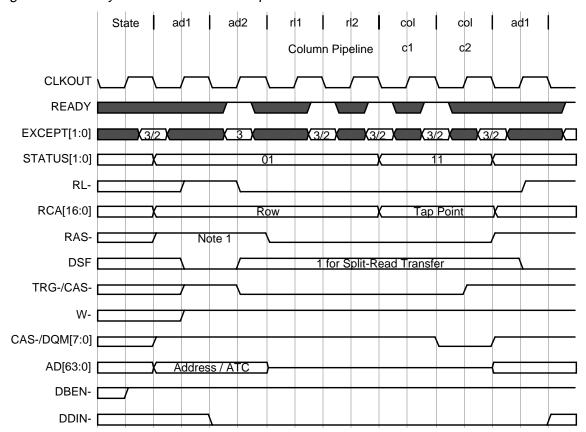

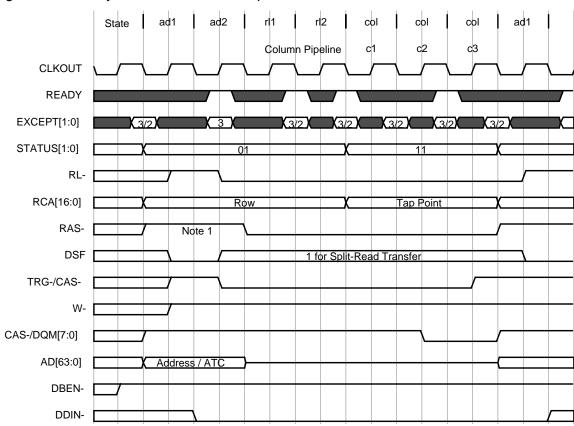

| 18–3  | Special Register Set                                                      | 18-4  |

| 18–4  | Burst Length 1 Block-Write                                                | 18-6  |

| 18–5  | Burst Length 2 Block-Write                                                | 18-7  |

| 19–1  | DRAM Refresh States(3 Cycle RAS High)                                     | 19-6  |

| 19–2  | DRAM Refresh (3 Cycle RAS High)                                           | 19-7  |

| 19–3  | DRAM Refresh States(4 Cycle RAS High)                                     | 19-8  |

| 19–4  | DRAM Refresh (4 Cycle RAS High)                                           | 19-9  |

| 19–5  | SDRAM Refresh States                                                      | 19-10 |

| 19–6  | SDRAM Refresh                                                             | 19-11 |

| 20–1  | Host Interface Timing                                                     | 20-4  |

| A-1   | Dimensioned src to Dimensioned dst                                        | A-3   |

| A-2   | Dimensioned src to Fixed-Patch, Delta-Guided dst                          | A-3   |

| A-3   | Dimensioned src to Fixed-Patch, Offset-Guided dst                         | A-4   |

| A-4   | Dimensioned src to Variable-Patch, Delta-Guided dst                       |       |

| A-5   | Dimensioned src to Variable-Patch, Offset-Guided dst                      |       |

| A–6  | Dimensioned src with Peripheral Device Read                              | A-5          |

|------|--------------------------------------------------------------------------|--------------|

| A-7  | Fixed-Patch, Delta-Guided src to Dimensioned dst                         | A-5          |

| A–8  | Fixed-Patch, Delta-Guided src to Fixed-Patch, Delta-Guided dst           | A-5          |

| A-9  | Fixed-Patch, Delta-Guided src to Fixed-Patch, Offset-Guided dst          | A-6          |

| A-10 | Fixed-Patch, Delta-Guided src to Variable-Patch, Delta-Guided dst        | A-6          |

| A-11 | Fixed-Patch, Delta-Guided src to Variable-Patch, Offset-Guided dst       | A-6          |

| A-12 | Fixed-Patch, Delta-Guided src with Peripheral Device Read                | A <b>-</b> 7 |

| A-13 | Fixed-Patch, Offset-Guided src to Dimensioned dst                        | A <b>-</b> 7 |

| A-14 | Fixed-Patch, Offset-Guided src to Fixed-Patch, Delta-Guided dst          | A-7          |

| A-15 | Fixed-Patch, Offset-Guided src to Fixed-Patch, Offset-Guided dst         | A-8          |

| A-16 | Fixed-Patch, Offset-Guided src to Variable-Patch, Delta-Guided dst       | A-8          |

| A-17 | Fixed-Patch, Offset-Guided src to Variable-Patch, Offset-Guided dst      | A-8          |

| A-18 | Fixed-Patch, Offset-Guided src with Peripheral Device Read               | A-9          |

| A-19 | Fixed-Patch, Offset-Guided, LUT src to Dimensioned dst                   | A-9          |

| A-20 | Fixed-Patch, Offset-Guided, LUT src to Fixed-Patch, Delta-Guided dst     | A-9          |

| A-21 | Fixed-Patch, Offset-Guided, LUT src to Fixed-Patch, Offset-Guided dst    | A-10         |

| A-22 | Fixed-Patch, Offset-Guided, LUT src to Variable-Patch, Delta-Guided dst  | A-10         |

| A-23 | Fixed-Patch, Offset-Guided, LUT src to Variable-Patch, Offset-Guided dst | A-10         |

| A-24 | Fixed-Patch, Offset-Guided, LUT src with Peripheral Device Read          | A-11         |

| A-25 | Variable-Patch, Delta-Guided src to Dimensioned dst                      | A-11         |

| A-26 | Variable-Patch, Delta-Guided src to Fixed-Patch, Delta-Guided dst        | A-11         |

| A-27 | Variable-Patch, Delta-Guided src to Fixed-Patch, Offset-Guided dst       | A-12         |

| A-28 | Variable-Patch, Delta-Guided src to Variable-Patch, Delta-Guided dst     | A-12         |

| A-29 | Variable-Patch, Delta-Guided src to Variable-Patch, Offset-Guided dst    | A-12         |

| A-30 | Variable-Patch, Delta-Guided src with Peripheral Device Read             |              |

| A-31 | Variable-Patch, Offset-Guided src to Dimensioned dst                     | A-13         |

| A-32 | Variable-Patch, Offset-Guided src to Fixed-Patch, Delta-Guided dst       | A-13         |

| A-33 | Variable-Patch, Offset-Guided src to Fixed-Patch, Offset-Guided dst      | A-14         |

| A-34 | Variable-Patch, Offset-Guided src to Variable-Patch, Delta-Guided dst    | A-14         |

| A-35 | Variable-Patch, Offset-Guided src to Variable-Patch, Offset-Guided dst   | A-14         |

| A-36 | Variable-Patch, Offset-Guided src with Peripheral Device Read            | A-15         |

| A-37 | Fill with Value src to Dimensioned dst                                   | A-15         |

| A-38 | Fill with Value src to Fixed-Patch, Delta-Guided dst                     |              |

| A-39 | Fill with Value src to Fixed-Patch, Offset-Guided dst                    | A-16         |

| A-40 | Fill with Value src to Variable-Patch, Delta-Guided dst                  | A-16         |

| A-41 | Fill with Value src to Variable-Patch, Offset-Guided dst                 | A-16         |

| A-42 | Peripheral Device Write to Dimensioned dst                               |              |

| A-43 | Peripheral Device Write to Fixed-Patch, Delta-Guided dst                 | A-17         |

| A-44 | Peripheral Device Write to Fixed-Patch, Offset-Guided dst                |              |

| A-45 | Peripheral Device Write to Variable-Patch, Delta-Guided dst              | A-18         |

| A-46 | Peripheral Device Write to Variable-Patch, Offset-Guided dst             | A-18         |

# **Tables**

| 1–1   | Transfer Controller Register Map                    | 1-7   |

|-------|-----------------------------------------------------|-------|

| 3–1   | PP Instruction Cache Service, Minimum Latencies     | 3-2   |

| 3–2   | MP Cache Service, Minimum Latencies                 | 3-4   |

| 3–3   | DEA Service, Minimum Latencies                      | 3-8   |

| 5–1   | Short-From PT Access Modes                          | 5-6   |

| 5–2   | Exchange src/dst Parameter Word Swap                | 5-8   |

| 5–3   | Exchange src/dst PT Options Bit Swap                | 5-8   |

| 5–4   | Packet Transfer Status (PTS) Coding                 | 5-12  |

| 6–1   | LUT Transfer A Count Format                         | 6-8   |

| 6–2   | dst Update Mode (DUM)                               | 6-23  |

| 6–3   | dst Transfer Mode (DTM)                             | 6-24  |

| 6–4   | src Update Mode (SUM)                               | 6-24  |

| 6–5   | src Transfer Mode (STM)                             | 6-25  |

| 6–6   | Long-From PT Access Modes                           | 6-26  |

| 6–7   | Exchange src/dst Parameter Word Swap (long-Form PT) | 6-27  |

| 6–8   | Exchange src/dst PT Options Bit Swap (Long-Form PT) | 6-28  |

| 6–9   | Packet Transfer Status (PTS) Coding                 | 6-35  |

| 7–1   | XPT Request Codes                                   | 7-3   |

| 8–1   | Block-Write Selection                               | 8-2   |

| 8–2   | Transparency Mode Selection                         | 8-13  |

| 8–3   | Read Transfer Mode Selection                        | 8-17  |

| 10–1  | Memory Cycle Status Codes                           | 10-8  |

| 10–2  | Row-Time Access Type Codes                          | 10-9  |

| 10–3  | Cycle Timing Selection                              | 10-11 |

| 10–4  | Turn-Off Cycle Selection                            | 10-12 |

| 10–5  | RCA Addressing Multiplexing                         | 10-13 |

| 10–6  | PDT Address Bit Replacement                         | 10-16 |

| 10–7  | Page Size Selection                                 | 10-17 |

| 10–8  | Bus Size Selection                                  | 10-18 |

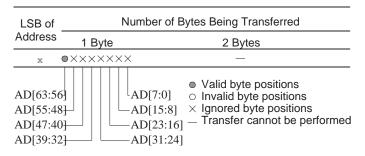

| 10–9  | AD[63:0] Bus Usage                                  | 10-19 |

| 10–10 | Column-Time Wait State Selection                    | 10-20 |

| 10–11 | Block-Write Mode Selection                          | 10-20 |

| 10–12 | Row Time Wait State Selection                       | 10-21 |

| 10–13 | Memory Bank Size                                    | 10-22 |

| 10–14 | Priority Level Codes                                | 10-23 |

| 11–1 | Row-Time Exception Encoding                 | 11-10  |

|------|---------------------------------------------|--------|

| 11–2 | Column-Time Exception Codes                 |        |

| 14–1 | DRAM Cycle Timing Selection                 | . 14-2 |

| 15–1 | SRAM Cycle Timing Selection                 | . 15-2 |

| 16–1 | SRAM Cycle Timing Selection                 | . 16-2 |

| 16–2 | SDRAM Pin Connections                       | . 16-4 |

| 19–1 | Refresh Timing Selection                    | . 19-5 |

| A-1  | Long form src and dst Transfer Combinations | A-2    |

### Chapter 1

# **Transfer Controller Overview**

The TMS320C82's *Transfer Controller* (TC) is a programmable controller responsible for moving data on and off chip. The TC contains the 'C82's memory interface allowing it to interface directly to various memory devices and peripherals. The TC also acts as a DMA controller for the 'C82's processors (the MP and PPs) and peripherals by performing autonomous block data transfers (called packet transfers) between on-chip and/or off-chip memory.

Topics in this chapter include:

|   | Topi | ic F                            | Page |

|---|------|---------------------------------|------|

|   | 1.1  | Transfer Controller Description | .1-2 |

| ı |      | Functional Blocks               |      |

|   | 1.3  | Transfer Controller Registers   | .1-7 |

|   |      |                                 |      |

#### 1.1 Transfer Controller Description

The TMS320C82 Transfer Controller (TC) is a flexible, high performance data transfer machine that provides the mechanism for moving data between on-chip and off-chip memory. The TC serves as a DMA controller by transferring data blocks as requested by the Master Processor (MP), Parallel Processors (PPs) or external peripheral devices. These autonomous transfers increase processor performance by freeing the MP and PPs to continue instruction execution while the TC transfers the data.

The TC contains a memory controller that provides address and control signals to interface directly to DRAMs, SDRAMs, SRAMs, ROMs and peripherals. The memory controller includes a unique cycle configuration cache that maintains configuration information for each of the memory and peripheral devices contained in the system. This allows the timing of each memory access to be tailored to the requirements of the device being accessed, thus minimizing access times.

Key features of the T C include:

#### 1.1.1 Key Features

| <br>,                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 64-bit data transfers  ■ Dynamic bus sizing for 8-, 16-, 32-, or 64-bit devices                                                                                                                                                                                                                                                                       |

| 32-bit addressing  ■ 4-GByte address range  ■ Multiplexed row/column address bus for direct DRAM and SDRAM interface                                                                                                                                                                                                                                  |

| <ul> <li>Memory configuration cache</li> <li>Stores memory configuration and timing information for up to six different memories and peripherals</li> <li>Auto-loads memory configuration on first access to each bank.</li> <li>Multi-level Least Recently Used (LRU) replacement algorithm allows prioritization of system memory banks.</li> </ul> |

| Up to 480 MByte/sec data transfer rate                                                                                                                                                                                                                                                                                                                |

| Versatile addressing capabilities                                                                                                                                                                                                                                                                                                                     |

| Intelligent queueing and prioritization of data transfer requests                                                                                                                                                                                                                                                                                     |

| Big or little endian operation (selected at reset)                                                                                                                                                                                                                                                                                                    |

#### 1.1.2 Transfer Controller Functions

Since the TC provides the only access to off-chip memory, it is responsible for all data movement and memory interface functions. These functions include:

MP and PP Instruction Cache Fills

MP Data Cache Fills and Dirty Subblock Write-back

MP and PP requested packet transfers (PTs)

Externally initiated packet transfers (XPTs)

MP and PP Direct External Accesses (DEAs)

DRAM and SDRAM Refresh

External Bus Requests

Cache operations are requested automatically by the cache logic contained within each processor. The TC moves the requested instructions or data from memory to the appropriate subblock in the cache array of the requesting processor. The TC will also write back the dirty subblocks of the MP's data cache when required by the MP.

Packet transfers (PTs) move blocks of data from one location to another. They are most frequently used to transfer data into or out of the PP data RAMs. The TC performs packet transfers when requested by the processors. Packet transfers may also be initiated by external devices. These XPTs can be used to assist in system I/O by transferring data between on-chip or system memory and I/O buffers such as video or audio data FIFOs.

During direct external accesses (DEAs) the TC transfers data directly between off-chip memory and processor registers. These cycles are generated by MP or PP load or store instructions. They allow the PPs to directly access off-chip memory and let the MP by-pass it's data cache to access off-chip memory directly.

External bus requests cause the TC to place memory interface signals into high impedance so that they may be driven directly by a host processor or another device.

DRAM refresh cycles keep system memory devices refreshed. These are generated automatically by the TC's programmable refresh controller. Refresh may be disabled in systems which do not use dynamic memory.

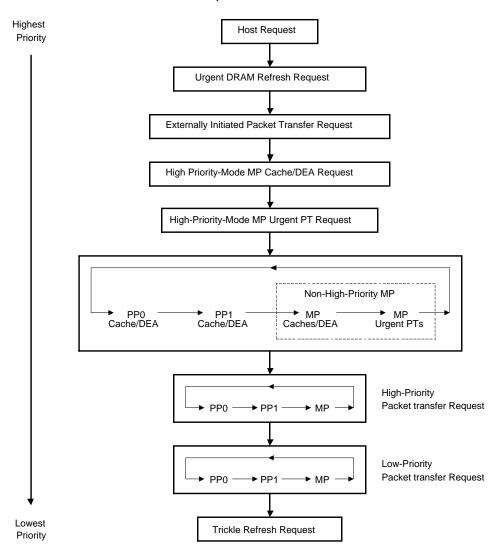

The various requests to the TC are prioritized by importance. When necessary, the TC will time-multiplex the memory interface between requests to ensure that all requests get serviced.

#### 1.2 Functional Blocks

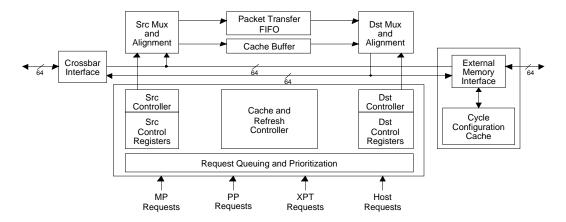

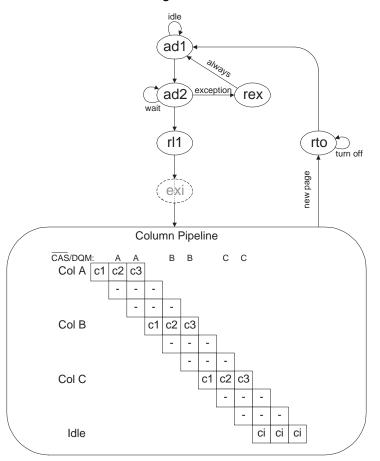

Figure 1–1. shows a high-level block diagram of the Transfer Controller. A brief description of each of the major blocks follows the diagram.

Figure 1–1. Transfer Controller Block Diagram

#### 1.2.1 Request Queuing and Prioritization Logic

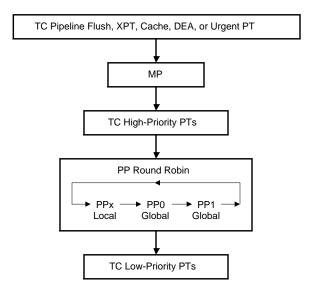

The TC evaluates all requests from the MP, PPs, XPT pins, and host interface pins and services them based on a fixed prioritization scheme. When multiple requests of the same priority are pending, the TC services them on a round-robin basis.

#### 1.2.2 Cache and Refresh Controller

The TC contains a programmable refresh controller that automatically generates DRAM refresh cycles as required by the external memory system. The TC's cache control logic generates the addresses necessary to perform cache fills (and write-backs) as requested by the MP and PPs.

#### 1.2.3 Source / Destination Controllers

The TC contains two independent controllers that handle packet transfers:

☐ The **source controller** generates the addresses necessary to fetch the packet data from the source memory. When a packet transfer request is submitted to the TC, the transfer has a number of parameters specifying how the source data is to be accessed. These parameters are loaded into the source control registers and are used to generate the source addresses.

☐ The **destination controller** generates the addresses needed to write the packet data into the destination memory area. A set of parameters similar to those of the source controller are loaded into the destination control registers to generate the destination addresses.

The source and destination controllers can address both on-chip and off-chip memory.

#### 1.2.4 Internal Memory (Crossbar) Interface

The TC's internal memory interface provides access to on-chip memory via the 'C82's crossbar. The 64-bit crossbar bus can transfer zero to eight bytes per cycle. Each crossbar access requires two clock cycles to complete (assuming no contention) but a new access can begin on every cycle.

#### 1.2.5 External Memory Interface

The external memory interface provides access to all off-chip memory and peripherals. A state sequencer generates the control signals and cycle timing necessary to interface to a variety of memory and peripheral devices. The 64-bit external data bus can transfer up to eight bytes per cycle.

#### 1.2.6 Source/Destination Mux and Alignment and PT FIFO