# TMS320C62x Multichannel Evaluation Module Reference Guide

Literature Number: SPRU308 February 1999

### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

# **Preface**

# Read This First

### About This Manual

This manual provides technical reference information for the TMS320C62x ('C62x) multichannel evaluation module (McEVM). It includes support software documentation, application programming interface (API) references, and hardware descriptions for the 'C62x McEVM.

The 'C62x McEVM is a peripheral component interconnect (PCI) plug-in card that is compliant with the *PCI Local Bus Specification Revision 2.1*. The 'C62x McEVM helps you evaluate characteristics of the 'C62x digital signal processor (DSP) to determine if it meets your application requirements. It is a high-performance platform targeted for multichannel telecom and datacom applications. The 'C62x McEVM is intended for use in a PCI expansion slot inside the PC  $^{\text{TM}}$ . It can also be operated outside the PC on a desktop or lab bench with the use of an external power supply and emulator (XDS510 or XDS510WS). The power supply and emulator are not included in the kit.

'C62x McEVM support software and APIs enable you to use the board to create applications for the 'C62x. Software utilities are provided with the 'C62x McEVM for board diagnostics, board configuration, and common object file format (COFF) DSP application loading. McEVM schematics and logic equations are included in this manual to ease your hardware development efforts and reduce time to market.

This manual assumes that you are familiar with working in a Windows 95<sup>TM</sup>, Windows 98<sup>TM</sup>, or a Windows NT<sup>TM</sup> environment and understand general and technical PC terminology. This manual specifically addresses the 'C62x McEVM and its support software. Detailed information about the 'C62x DSP and TI code development support tools is provided separately (see the *Related Documentation From Texas Instruments* section in this *Preface* for a list of documents and ordering information). For up-to-date information on the 'C62x McEVM, as well as related products, visit the 'C6000 website at http://www.ti.com/sc/c6000/.

### How to Use This Manual

This reference guide provides the following types of information about the 'C62x McEVM:

- Chapter 1 describes the theory of operation for the 'C62x EVM hardware, including key component identification, detailed information about each functional area, and interface descriptions.

- Chapter 2 describes the host support software utilities. It includes a complete API reference that allows you to write your own applications for the 'C62x McEVM and also includes example applications that use the API calls.

- Chapter 3 describes the DSP support software. It includes an overview of all the DSP support software components and a complete API reference that allows you to write your own DSP applications for the 'C62x McEVM. Examples applications that use the API calls are also provided.

- Reference material, consisting of Appendixes A through E, provides quick reference information for the 'C62x McEVM:

- Appendix A provides the McEVM connector pinouts.

- Appendix B contains the McEVM schematics.

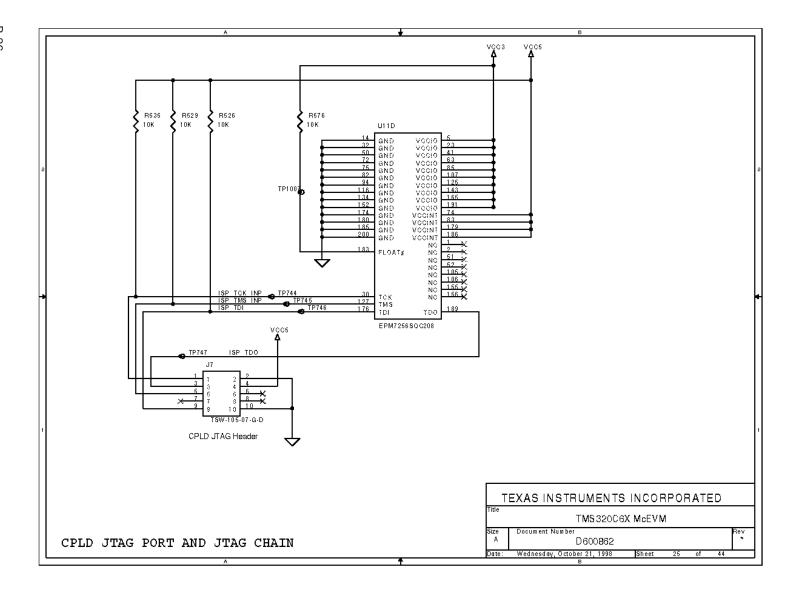

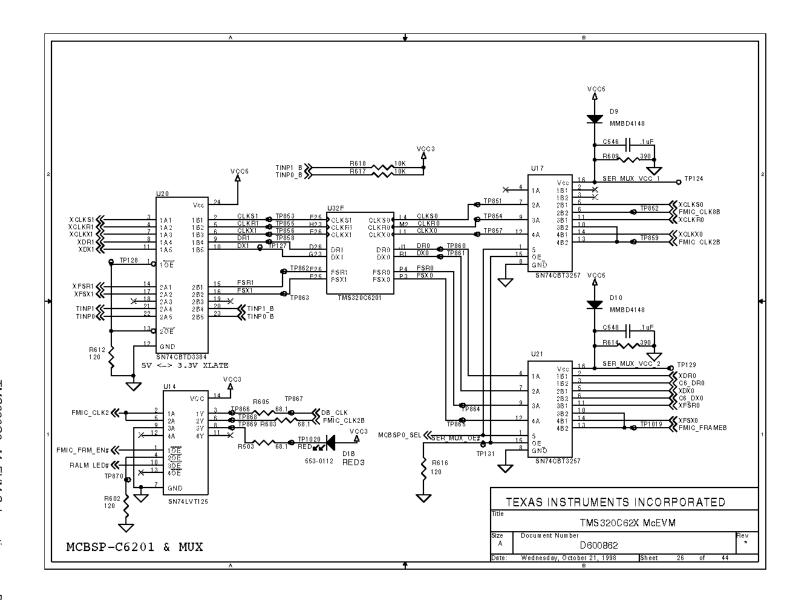

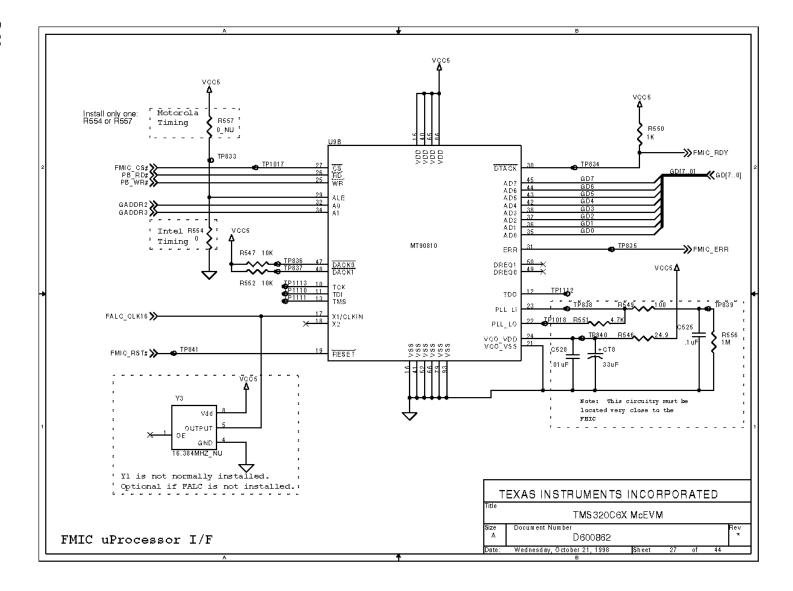

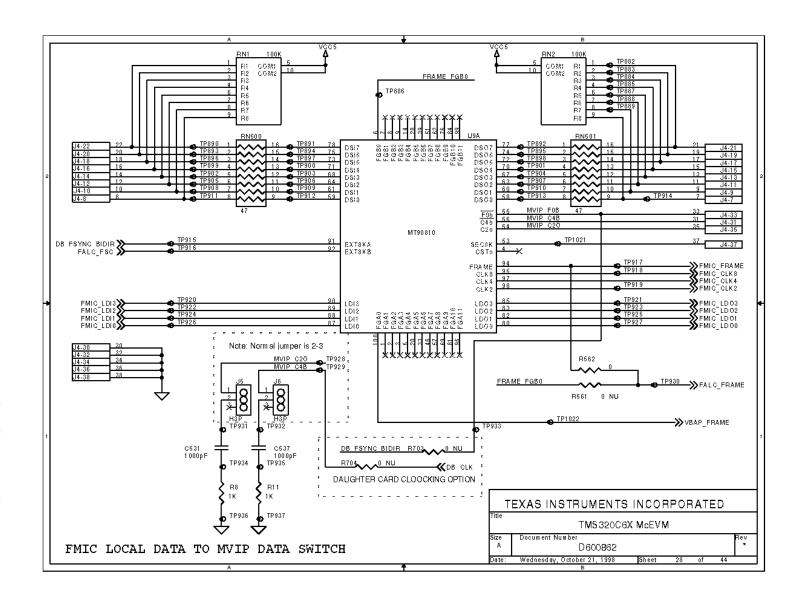

- Appendix C provides the McEVM complex programmable logic device (CPLD) equations.

- Appendix D summarizes the McEVM PCI configuration EEPROM.

- Appendix E provides a glossary of terms used in this manual.

### **Notational Conventions**

This document uses the following conventions:

☐ Program listings, program examples, and interactive displays are shown in a special typeface. Some examples use a bold version for emphasis; interactive displays use a bold version to distinguish commands that you enter from items that the system displays (such as prompts, command output, error messages, etc.).

Here is a sample program listing with the evm6x\_close() function highlighted for emphasis:

```

#include <windows.h>

#include <evm6xdll.h>

...

HANDLE h_board;

h_board = evm6x_open( 0, FALSE );

if ( h_board == INVALID_HANDLE_VALUE )

{

exit(-1);

}

...

evm6x_close( h_board );

```

☐ In syntax descriptions, the instruction or command is in a **bold face**, and parameters are in *italics*. Portions of a syntax that are in **bold** should be entered as shown; portions of a syntax that are in *italics* describe the type of information that should be entered. Here is an example of a command syntax:

### evm6xldr filename

☐ Square brackets ( [ and ] ) identify an optional parameter. If you use an optional parameter, you specify the information within the brackets; you do not enter the brackets themselves. Here is an example of a command that has optional parameters.

### evm6xtst [options] [log\_filename]

evm6xtst is the command. This command has two optional parameters, indicated by *options* and *log\_filename*.

□ Device pins often are represented in groups. Device pin group notation consists of the pin name followed by brackets containing the range of pins included in the group. A colon separates the numbers in the range. For example, GD[31:0] represents the global data bus pins on a device.

☐ The TMS320C62x family of devices is referred to as the 'C62x. The following abbreviations are used in this manual for TI devices on the 'C62x McEVM:

| Abbreviation | <b>Device Definition</b> |

|--------------|--------------------------|

| 'C6201       | TMS320C6201              |

| 'ALVCH16244  | SN74ALVCH16244           |

| 'CBT3257     | SN74CBT3257              |

| 'CBTD3384    | SN74CBTD3384             |

| 'LVT125      | SN74LVT125               |

| 'ALVCH16245  | SN74LVCH16245            |

# Information About Cautions and Warnings

This book contains cautions and warnings.

This is an example of a caution statement.

A caution statement describes a situation that could potentially damage your software or equipment.

This is an example of a warning statement.

A warning statement describes a situation that could potentially cause harm to <u>you</u>.

The information in a caution or a warning is provided for your protection. Please read each caution and warning carefully.

### Related Documentation From Texas Instruments

The following books describe the 'C62x processor and related support tools. To obtain a copy of any of these TI documents, call the Texas Instruments Literature Response Center at (800)477–8924. When ordering, please identify the book by its title and literature number.

- **TMS320C6000** Assembly Language Tools User's Guide (literature number SPRU186) describes the assembly language tools (assembler, linker, and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for the 'C6000 generation of devices.

- TMS320C6x C Source Debugger User's Guide (literature number SPRU188) tells you how to invoke the 'C6x simulator and emulator versions of the C source debugger interface. This book discusses various aspects of the debugger, including command entry, code execution, data management, breakpoints, profiling, and analysis.

- **TMS320C6000 Optimizing C Compiler User's Guide** (literature number SPRU187) describes the 'C6000 C compiler and the assembly optimizer. This C compiler accepts ANSI standard C source code and produces assembly language source code for the 'C6000 generation of devices. The assembly optimizer helps you optimize your assembly code.

- **TMS320C6000 CPU and Instruction Set Reference Guide** (literature number SPRU189) describes the 'C6000 CPU architecture, instruction set, pipeline, and interrupts for these digital signal processors.

- TMS320C6201/C6701 Peripherals Reference Guide (literature number SPRU190) describes common peripherals available on the TMS320C6201/C6701 digital signal processors. This book includes information on the internal data and program memories, the external memory interface (EMIF), the host port, multichannel buffered serial ports, direct memory access (DMA), clocking and phase-locked loop (PLL), and the power-down modes.

- **TMS320C6000 Programmer's Guide** (literature number SPRU198) describes ways to optimize C and assembly code for the TMS320C6000 DSPs and includes application program examples.

- **TMS320C6000 Technical Brief** (literature number SPRU197) gives an introduction to the 'C6000 platform of digital signal processors, development tools, and third-party support.

- **XDS51x** Emulator Installation Guide (literature number SPNU070) describes the installation of the XDS510™, XDS510PP™, and XDS510WS™ emulator controllers. The installation of the XDS511™ emulator is also described.

- TMS320 DSP Development Support Reference Guide (literature number SPRU011) describes the TMS320 family of digital signal processors and the tools that support these devices. Included are code-generation tools (compilers, assemblers, linkers, etc.) and system integration and debug tools (simulators, emulators, evaluation modules, etc.). Also covered are available documentation, seminars, the university program, and factory repair and exchange.

- TMS320C6x Peripheral Support Library Programmer's Reference (literature number SPRU273) describes the contents of the 'C6x peripheral support library of functions and macros. It lists functions and macros both by header file and alphabetically, provides a complete description of each, and gives code examples to show how they are used.

- **TMS320C62x Multichannel Evaluation Module User's Guide** (literature number SPRU285) is a high-performance, multichannel telephony platform for the development, analysis, and testing of 'C62x digital signal processor (DSP) algorithms and applications. The 'C62x McEVM allows you to evaluate the 'C62x DSP and algorithms to determine if they meet your application requirements.

- **TMS320C6201, TMS320C6201B Digital Signal Processors Data Sheet** (literature number SPRS051) describes the features of the TMS320C6201 and TMS320C6201B fixed-point DSPs and provides pinouts, electrical specifications, and timings for the devices.

#### Related Documentation

For up-to-date information on the 'C62x McEVM, as well as related products, visit the 'C6000 website at:

http://www.ti.com/sc/docs/dsps/tools/c6000/index.htm

You can use the following specification to supplement this reference guide:

**PCI Local Bus Specification Revision 2.1**, PCI Special Interest Group, June 1, 1995.

http://www.pcisig.com/specs.html

MVIP-90 Reference Manual, GO-MVIP, Inc. 1990 (http://www.mvip.org/MemOrder.htm)

The MVIP Book, GO-MVIP, Inc., ISBN 0-936648-76-7.

### **Trademarks**

320 Hotline On-line, VelociTI, XDS510, XDS510PP, XDS510WS, and XDS511 are trademarks of Texas Instruments Incorporated.

ABEL and Synario are registered trademarks of the DATA I/O Corporation.

Altera, ByteBlaster, and MAX+ PLUS are trademarks of the Altera Corporation.

AMCC is a registered trademark of Applied Micro Circuits Corporation.

IBM and PC are trademarks of International Business Machines Corporation.

Intel and Pentium are trademarks of Intel Corporation.

Microsoft, Windows, and Windows NT are registered trademarks of Microsoft Corporation.

MVIP, MVIP-90, MVIP Bus and Multi-Vendor Integration Protocol are trademarks of GO-MVIP, Inc.

OpenWindows, Solaris, and SunOS are trademarks of Sun Microsystems, Inc.

SPARCstation is a trademark of SPARC International, Inc., but licensed exclusively to Sun Microsystems, Inc.

X Window System is a trademark of the Massachusetts Institute of Technology.

Before contacting Texas Instruments Technical Support, please have the

# **Obtaining Technical Support**

| foll | owing information available:                                                                                                                                                                                                                                                |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Assembly number of your 'C62x McEVM (D600860-0001) located on the bottom side of the board $$                                                                                                                                                                               |

|      | Revision number of your 'C62x McEVM located in parentheses next to the assembly number on the bottom side of the board                                                                                                                                                      |

|      | Serial number located on the bottom side of the board                                                                                                                                                                                                                       |

|      | Record of the 'C62x McEVM confidence test utility results that identifies potential problems and other revision numbers (software, EEPROM, CPLD). <i>TMS320C62x McEVM User's Guide,</i> Chapter 3, <i>Running the Board Confidence Test</i> , explains how to run the test. |

|      | Computer's PCI BIOS brand name and version number                                                                                                                                                                                                                           |

| Amount of memory in your computer system                                                                        |                                                                              |  |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|

| Version of the software and operating environment you are using such as Windows NT 4.0                          |                                                                              |  |

| Version of the code generation tools you are using                                                              |                                                                              |  |

| Ver                                                                                                             | sion of the debugger you are using                                           |  |

| If you are using Windows 95, print out a report of your system configuration by performing the following steps: |                                                                              |  |

| 1)                                                                                                              | Right click on the My Computer icon on the desktop.                          |  |

| 2)                                                                                                              | Select the Properties menu item.                                             |  |

| 3)                                                                                                              | Select the Device Manager tag.                                               |  |

| 4)                                                                                                              | Select the Print button.                                                     |  |

| 5)                                                                                                              | Select the System summary radio button.                                      |  |

| 6)                                                                                                              | Click on the OK button to print a system resource summary.                   |  |

|                                                                                                                 | ou are using Windows NT, perform the following steps to get system prmation: |  |

| 1)                                                                                                              | Select the Run menu item from the Windows NT Start menu.                     |  |

| 2)                                                                                                              | Type winmsd at the Open prompt, and press Enter.                             |  |

| 3)                                                                                                              | Select the Resources tab of the Windows NT Diagnostics window.               |  |

| 4)                                                                                                              | Click on the Print button to get a report.                                   |  |

| 5)                                                                                                              | Click on OK at the Create Report window.                                     |  |

| Ha                                                                                                              | ve this system resource summary available when you contact technical         |  |

### Note:

support.

Check the system resource summary to see if the IRQ assigned to TI TMS320C62x McEVM is shared with another device. If it is, this is probably the problem.

Once you have this information ready, contact Texas Instruments Technical Support as specified in the *If You Need Assistance* section that follows.

## If You Need Assistance . . .

| World-Wide Web Sites                                         |                      |                                                             |

|--------------------------------------------------------------|----------------------|-------------------------------------------------------------|

| TI Online                                                    | http://www.ti.com    | 2                                                           |

|                                                              | http://www.ti.con    | n/sc/docs/pic/home.htm                                      |

| Semiconductor Product Information Center (PIC) DSP Solutions | http://www.ti.con    | ·                                                           |

| 320 Hotline On-line™                                         |                      | n/sc/docs/dsps/support.htm                                  |

| 320 Hottille Off-life                                        | Tittp://www.ti.com   | n/sc/docs/dsps/support.nun                                  |

| North America, South America, Cer                            | ntral America        |                                                             |

| Product Information Center (PIC)                             | (972) 644-5580       |                                                             |

| TI Literature Response Center U.S.A.                         | (800) 477-8924       |                                                             |

| Software Registration/Upgrades                               | (214) 638-0333       | Fax: (214) 638-7742                                         |

| U.S.A. Factory Repair/Hardware Upgrades                      | (281) 274-2285       |                                                             |

| U.S. Technical Training Organization                         | (972) 644-5580       |                                                             |

| DSP Hotline                                                  |                      | Email: dsph@ti.com                                          |

| DSP Internet BBS via anonymous ftp to ftp://ftp              | .ti.com/pub/tms320   | 0bbs                                                        |

| Europe, Middle East, Africa                                  |                      |                                                             |

| European Product Information Center (EPIC) H                 | lotlines:            |                                                             |

| Multi-Language Support +                                     | 33 1 30 70 11 69     | Fax: +33 1 30 70 10 32                                      |

| Email: epic@ti.com                                           |                      |                                                             |

| Deutsch +49 8161 80 33 11 or +                               | 33 1 30 70 11 68     |                                                             |

| 3 -                                                          | 33 1 30 70 11 65     |                                                             |

|                                                              | 33 1 30 70 11 64     |                                                             |

|                                                              | 33 1 30 70 11 67     |                                                             |

|                                                              | 33 1 30 70 11 99     |                                                             |

|                                                              | 33 4 93 22 25 40     |                                                             |

| Europe Customer Training Helpline                            |                      | Fax: +49 81 61 80 40 10                                     |

| Asia-Pacific                                                 |                      |                                                             |

| Literature Response Center                                   | +852 2 956 7288      | Fax: +852 2 956 2200                                        |

| Hong Kong DSP Hotline                                        | +852 2 956 7268      | Fax: +852 2 956 1002                                        |

| Korea DSP Hotline                                            | +82 2 551 2804       | Fax: +82 2 551 2828                                         |

| Korea DSP Modem BBS                                          | +82 2 551 2914       |                                                             |

| Singapore DSP Hotline                                        |                      | Fax: +65 390 7179                                           |

|                                                              | +886 2 377 1450      | Fax: +886 2 377 2718                                        |

|                                                              | +886 2 376 2592      |                                                             |

| Taiwan DSP Internet BBS via anonymous ftp to                 | ttp://dsp.ee.tit.edu | u.tw/pub/TI/                                                |

| Japan                                                        |                      |                                                             |

| Product Information Center +0120-81-                         | -0026 (in Japan)     | Fax: +0120-81-0036 (in Japan)                               |

| +03-3457-0972 or (INTL                                       | ) 813-3457-0972      | Fax: +03-3457-1259 or (INTL) 813-3457-1259                  |

| DSP Hotline +03-3769-8735 or (INTL                           | ,                    | Fax: +03-3457-7071 or (INTL) 813-3457-7071                  |

| DSP BBS via Nifty-Serve                                      | Type "Go TIASP"      |                                                             |

| Documentation                                                |                      |                                                             |

| When making suggestions or reporting errors in               | documentation, ple   | ease include the following information that is on the title |

| page: the full title of the book, the publication da         |                      | S S S S S S S S S S S S S S S S S S S                       |

| Mail: Texas Instruments Incorporated                         |                      | Email: dsph@ti.com                                          |

| Technical Documentation Services, M                          | MS 702               |                                                             |

| P.O. Box 1443                                                |                      |                                                             |

| Houston, Texas 77251-1443                                    |                      |                                                             |

|                                                              |                      |                                                             |

**Note:** When calling a Literature Response Center to order documentation, please specify the literature number of the book.

# **Contents**

| 1 | TMS                                                                      | 320C62x | McEVM Hardware                                   | 1-1  |

|---|--------------------------------------------------------------------------|---------|--------------------------------------------------|------|

|   | Describes the TMS320C62x McEVM hardware components and how they operate. |         |                                                  |      |

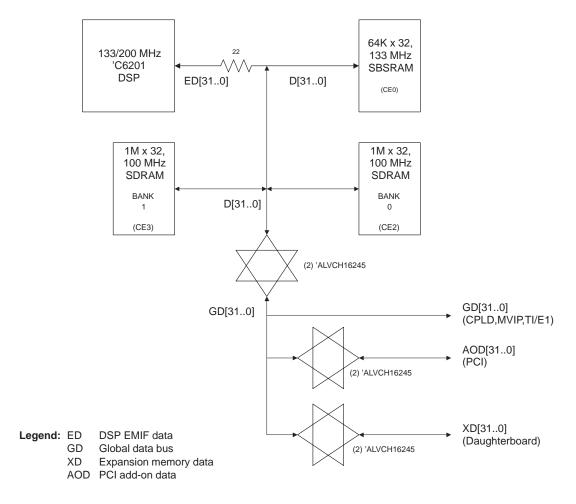

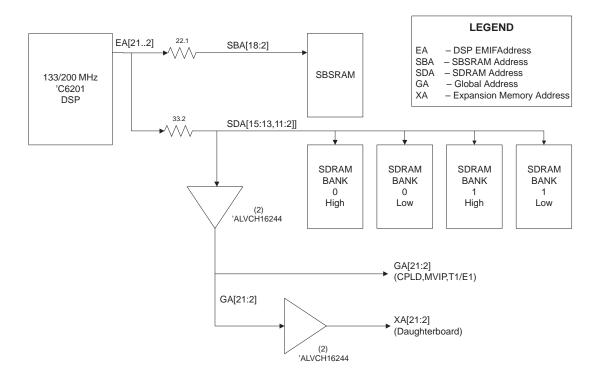

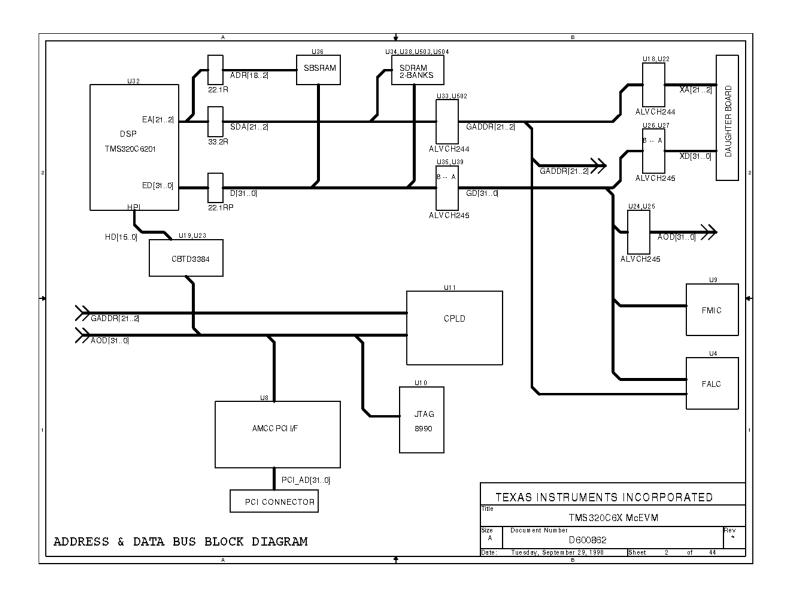

|   | 1.1                                                                      | TMS32   | 20C62x McEVM Hardware Detailed Block Diagram     | 1-2  |

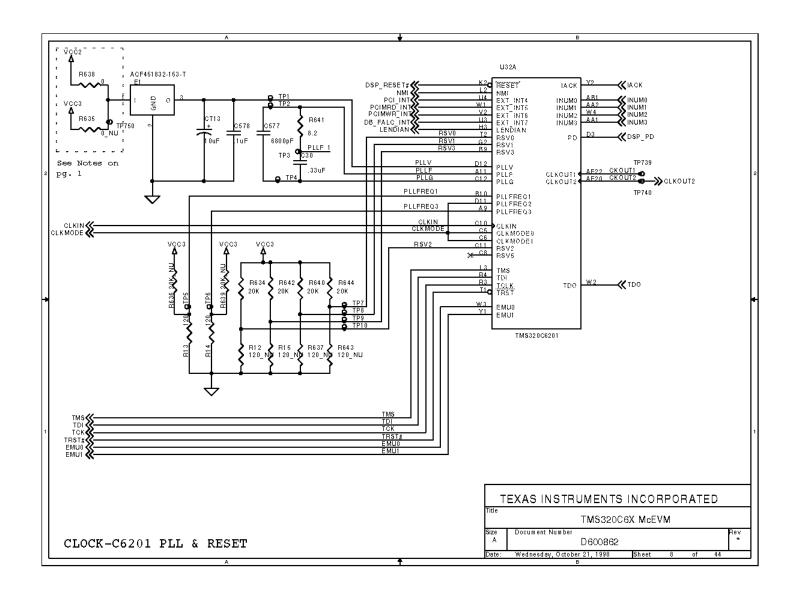

|   | 1.2                                                                      |         | 20C6201 DSP                                      |      |

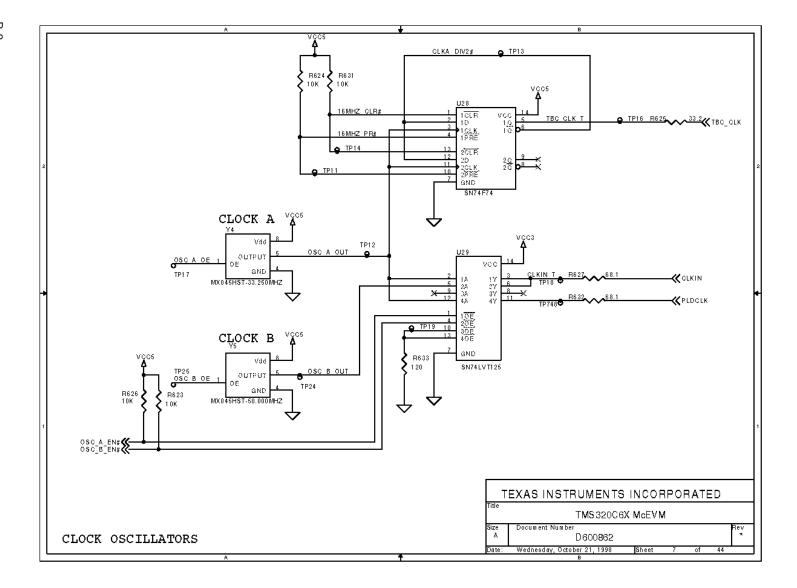

|   | 1.3                                                                      |         | locks                                            |      |

|   | 1.4                                                                      |         | al Memory                                        |      |

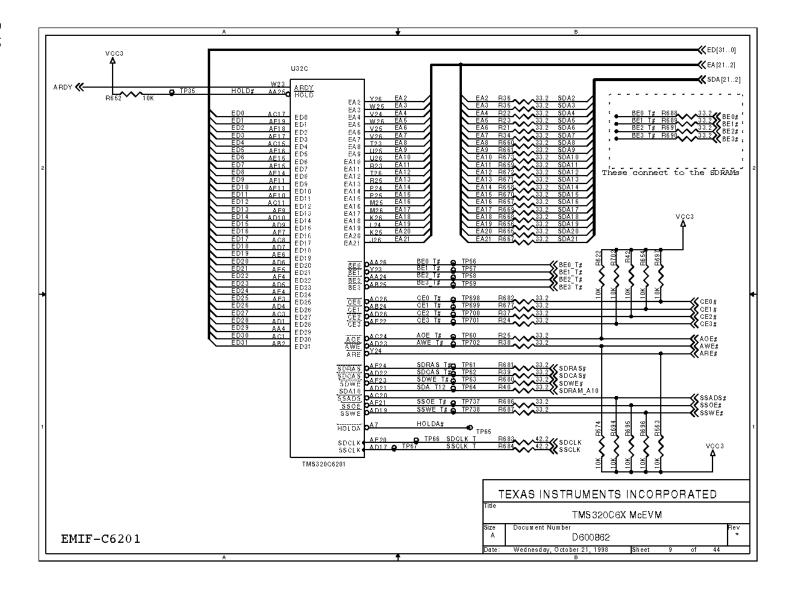

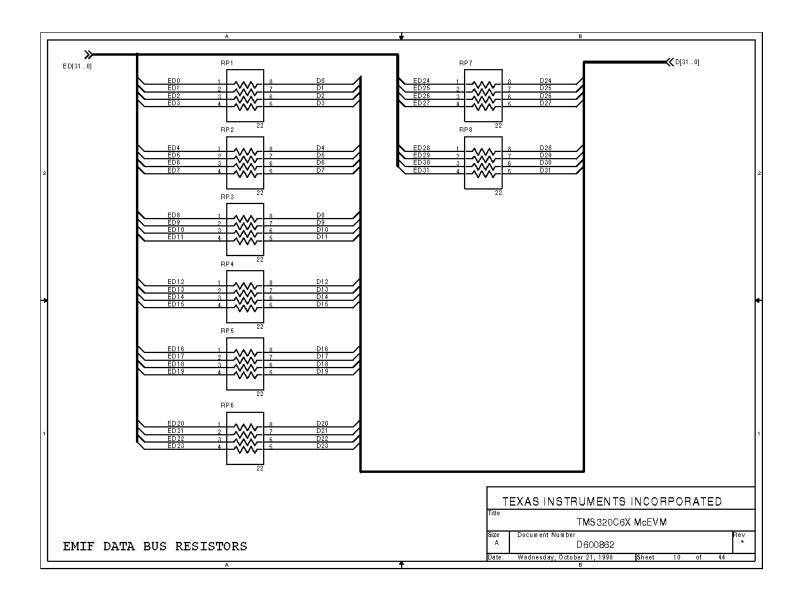

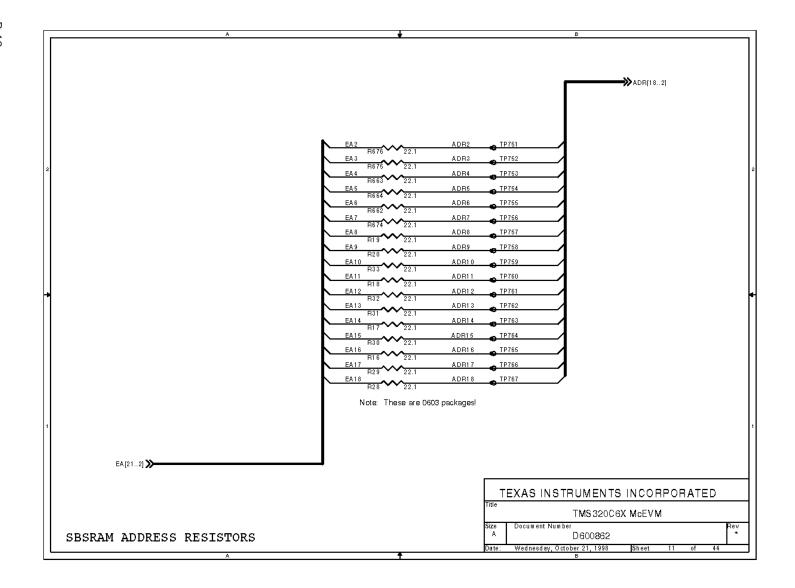

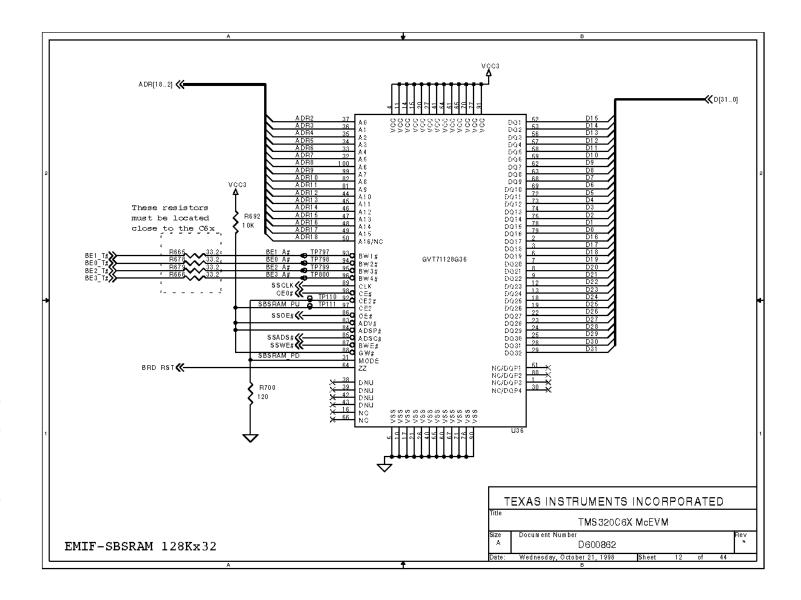

|   |                                                                          | 1.4.1   | SBSRAM                                           |      |

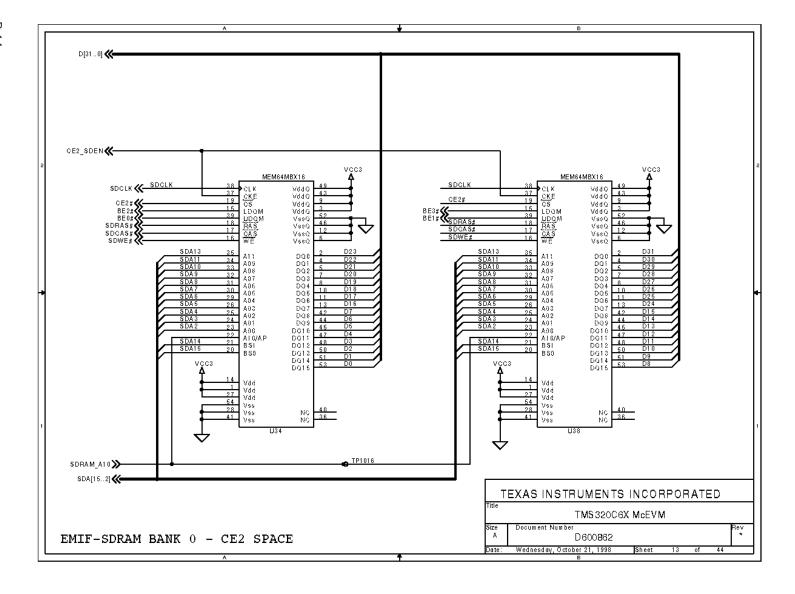

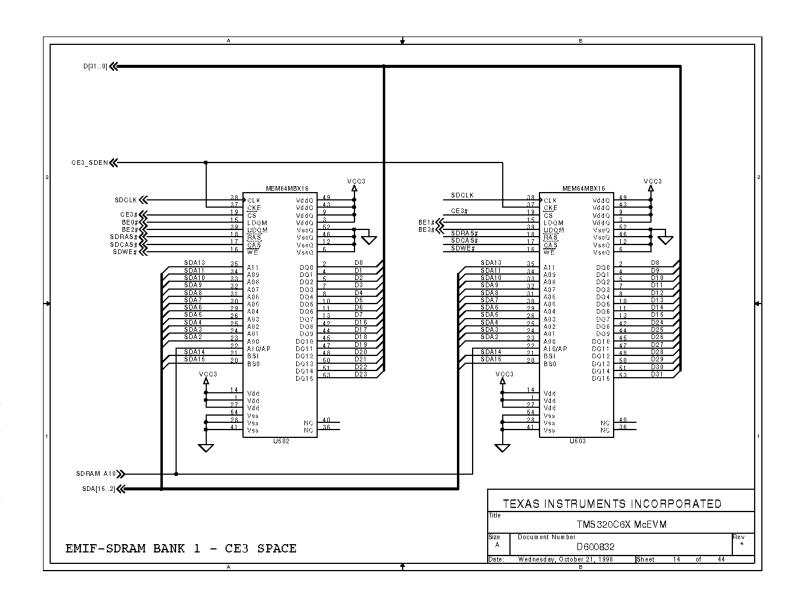

|   |                                                                          | 1.4.2   | SDRAM                                            | 1-11 |

|   |                                                                          | 1.4.3   | Expansion Memory                                 | 1-12 |

|   |                                                                          | 1.4.4   | DSP Memory Maps                                  |      |

|   |                                                                          | 1.4.5   | DSP EMIF Registers                               |      |

|   | 1.5                                                                      | Expans  | sion Interfaces                                  |      |

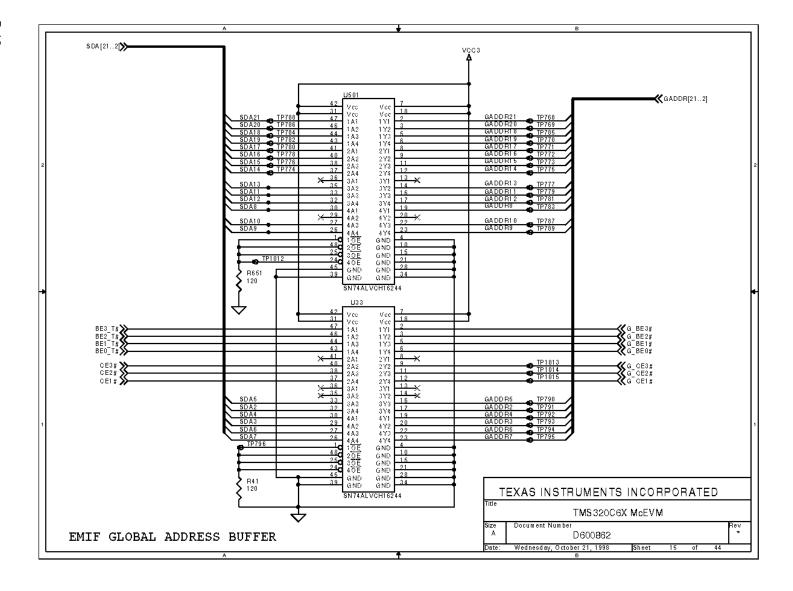

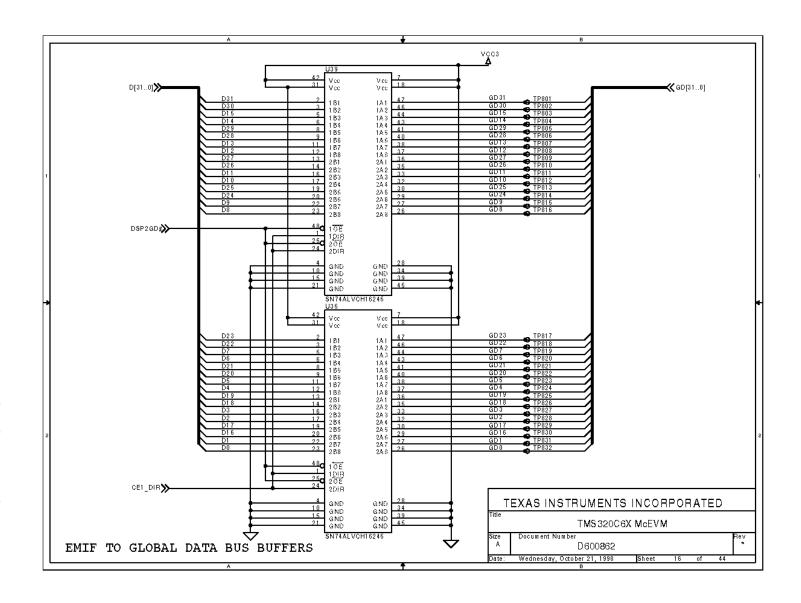

|   |                                                                          | 1.5.1   | Expansion Memory Interface                       | 1-18 |

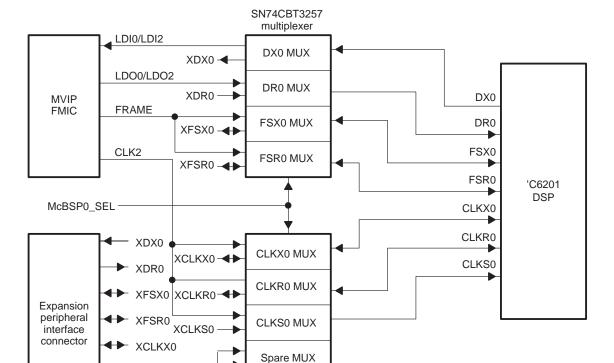

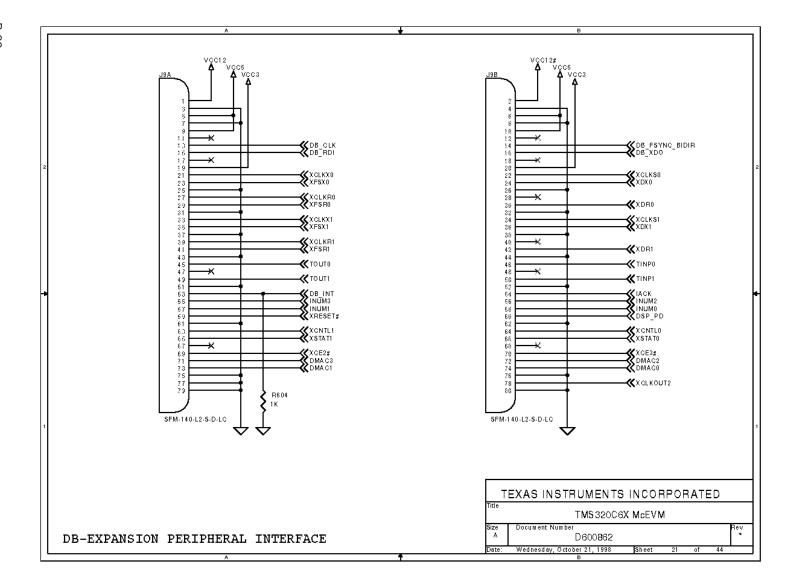

|   |                                                                          | 1.5.2   | Expansion Peripheral Interface                   | 1-19 |

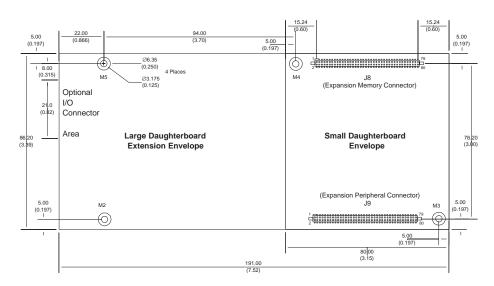

|   |                                                                          | 1.5.3   | Daughterboard                                    | 1-21 |

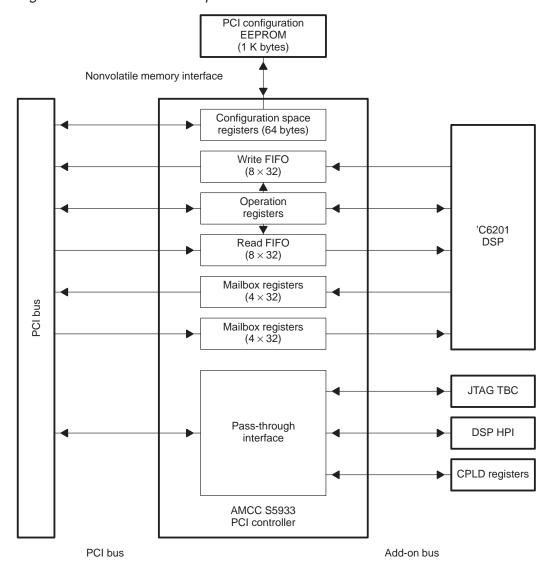

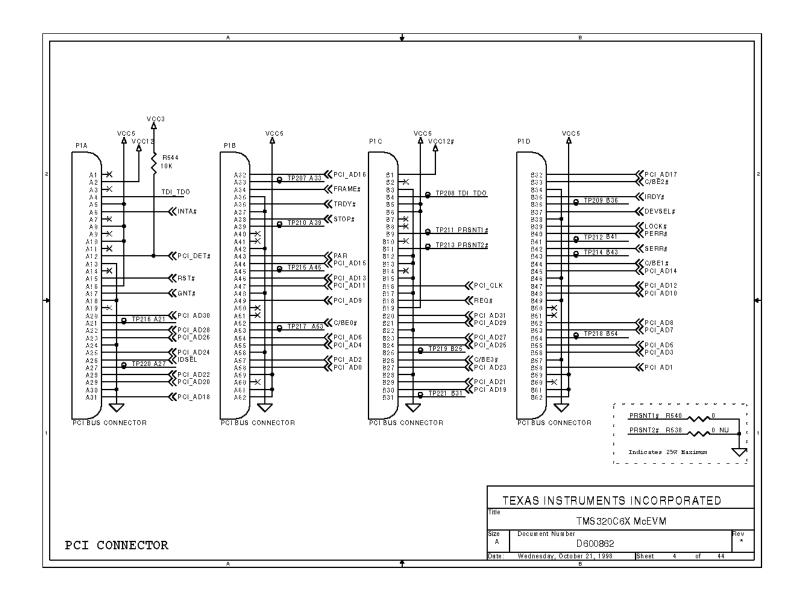

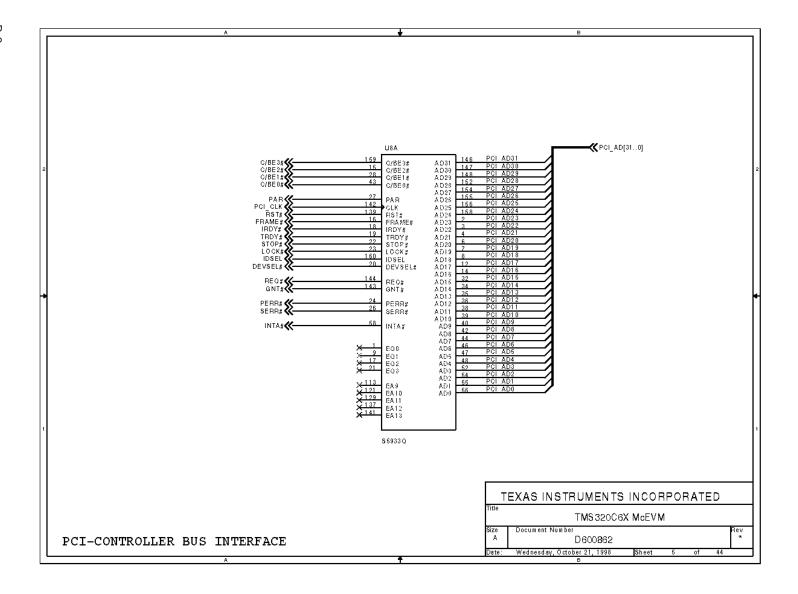

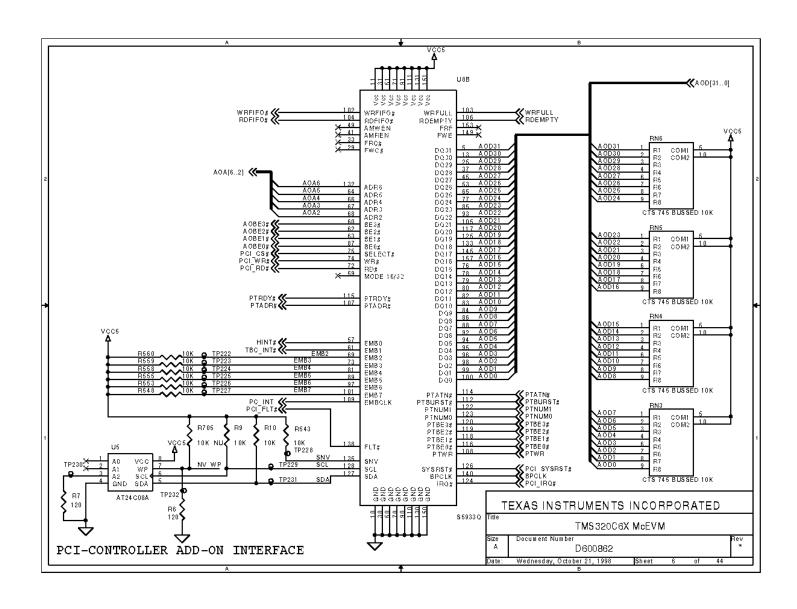

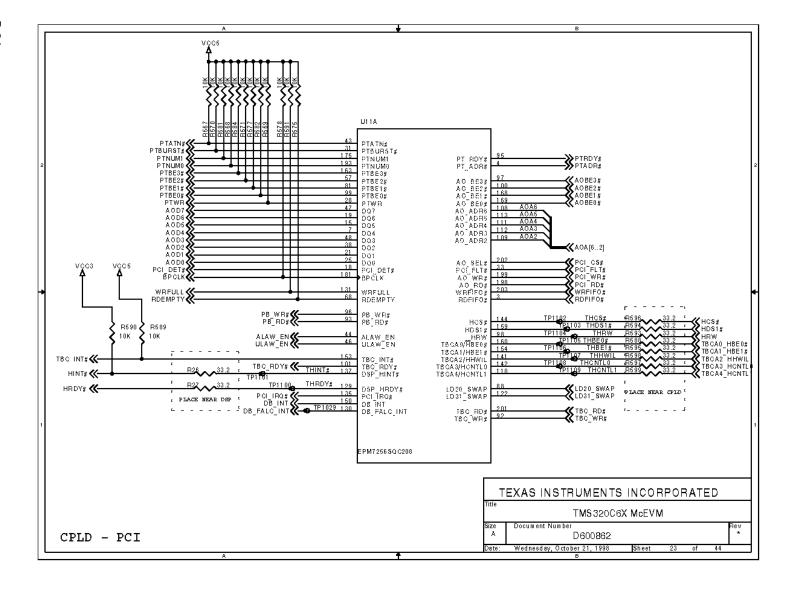

|   | 1.6                                                                      | PCI Int | erface                                           | 1-23 |

|   |                                                                          | 1.6.1   | PCI Interface Implementation                     | 1-24 |

|   |                                                                          | 1.6.2   | PCI Controller Operation Registers               | 1-28 |

|   |                                                                          | 1.6.3   | PCI Add-On Bus Operation Registers               | 1-29 |

|   |                                                                          | 1.6.4   | PCI Slave Support                                |      |

|   |                                                                          | 1.6.5   | PCI Master Support                               | 1-33 |

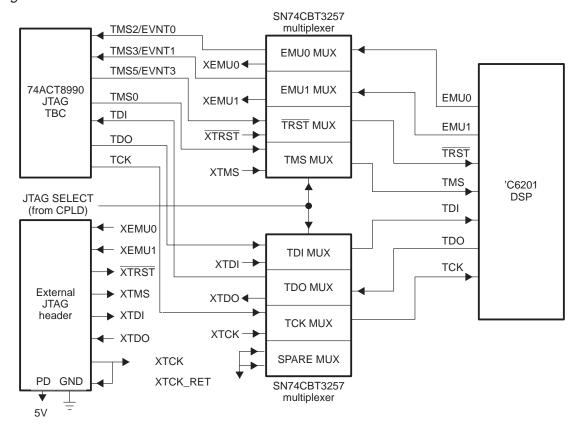

|   | 1.7                                                                      | JTAG E  | Emulation                                        | 1-38 |

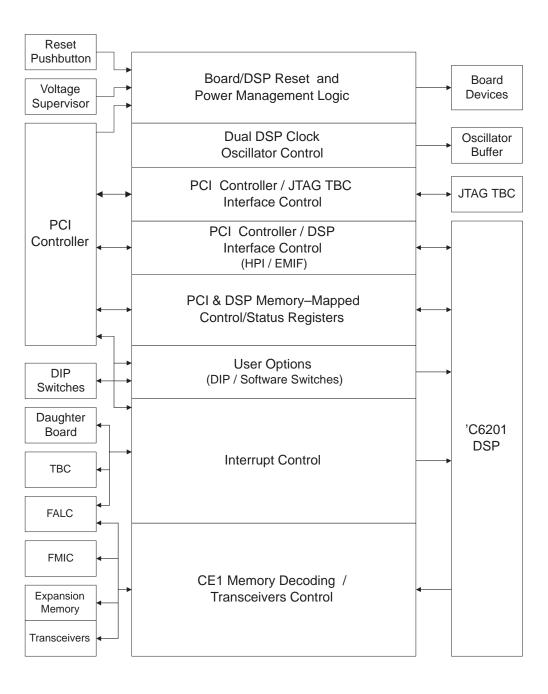

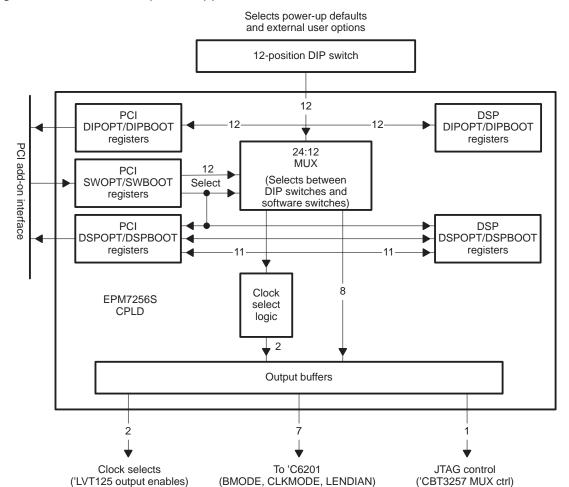

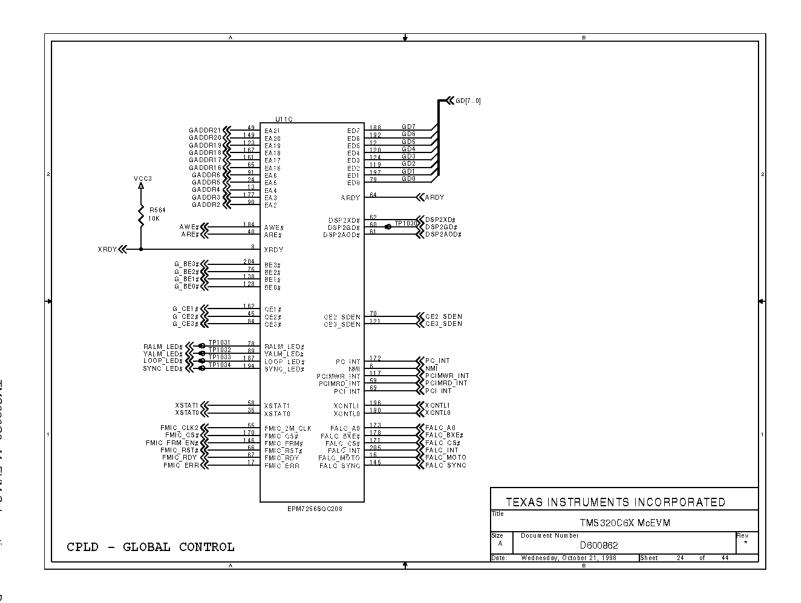

|   | 1.8                                                                      | Progra  | mmable Logic                                     | 1-40 |

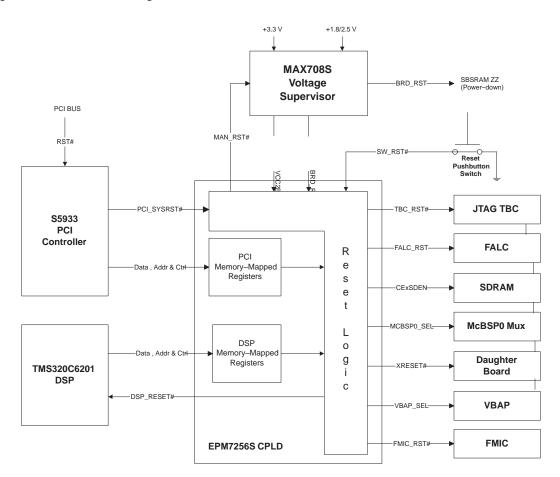

|   |                                                                          | 1.8.1   | Reset Control                                    | 1-42 |

|   |                                                                          | 1.8.2   | Power Management                                 | 1-44 |

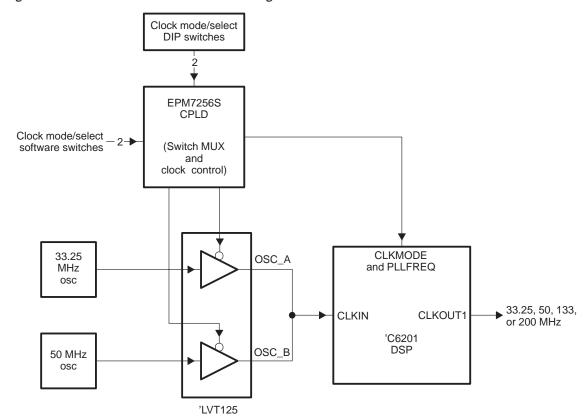

|   |                                                                          | 1.8.3   | Dual DSP Clock Oscillator Control                | 1-45 |

|   |                                                                          | 1.8.4   | PCI Controller/JTAG TBC Interface Control        | 1-46 |

|   |                                                                          | 1.8.5   | PCI Controller/DSP Interface Control             | 1-47 |

|   |                                                                          | 1.8.6   | PCI Memory-Mapped Board Control/Status Registers | 1-48 |

|   |                                                                          | 1.8.7   | DSP Memory-Mapped Control/Status Registers       | 1-58 |

|   |                                                                          | 1.8.8   | PCI and DSP Interrupt Control                    | 1-71 |

|   |                                                                          | 1.8.9   | CE1 Memory Decoding/Data Transceivers Control    | 1-74 |

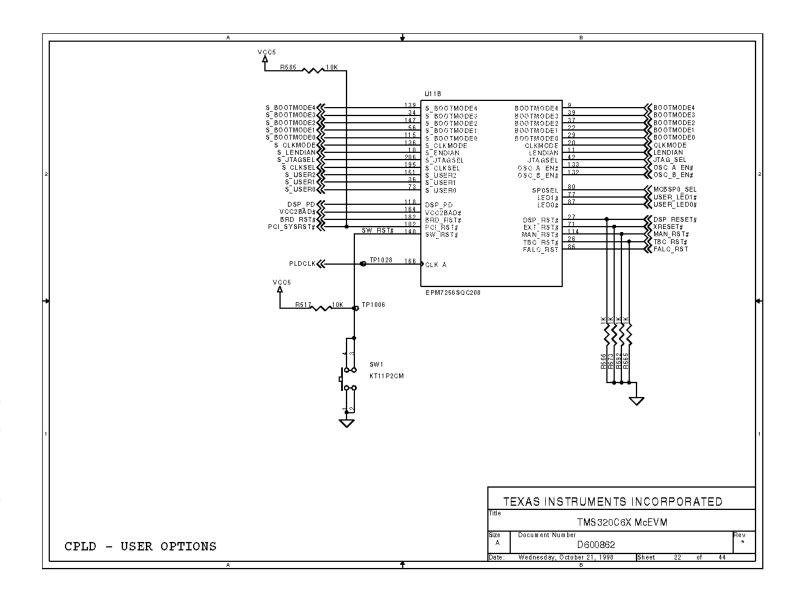

|   |                                                                          | 1.8.10  | User Options Control                             | 1-74 |

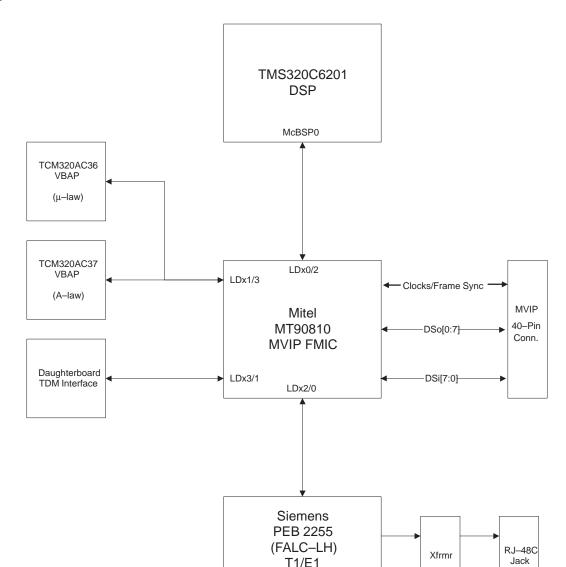

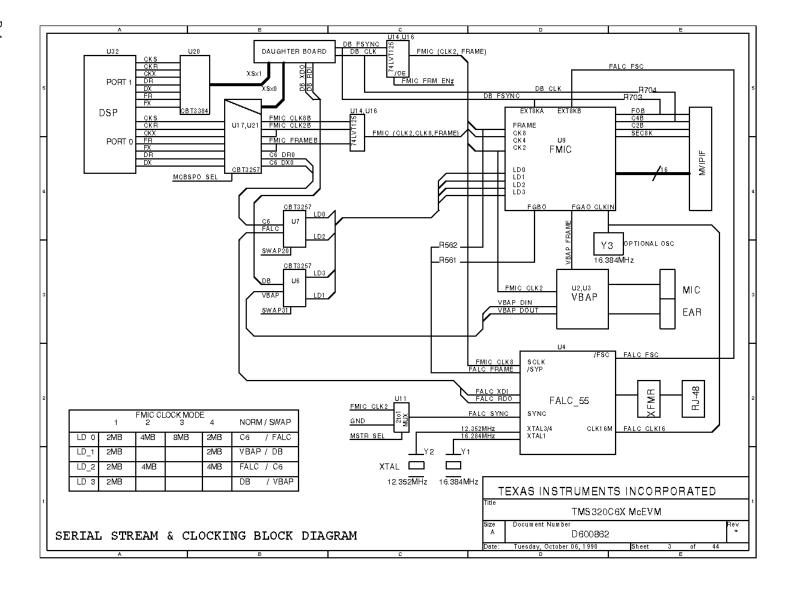

|   | 1.9                                                                      | MVIP I  | nterface and Switch                              | 1-78 |

|   | 1.10                                                                     | T1/E1   | Interface                                        | 1-82 |

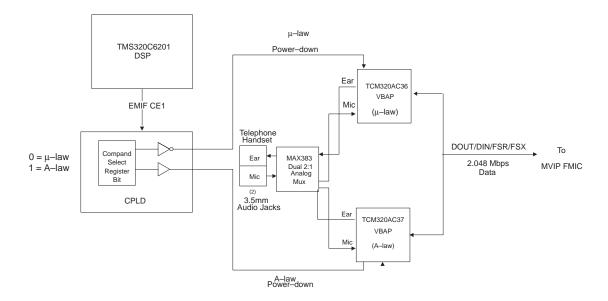

|   | 1.11<br>1.12                                       | Handset Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

|---|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

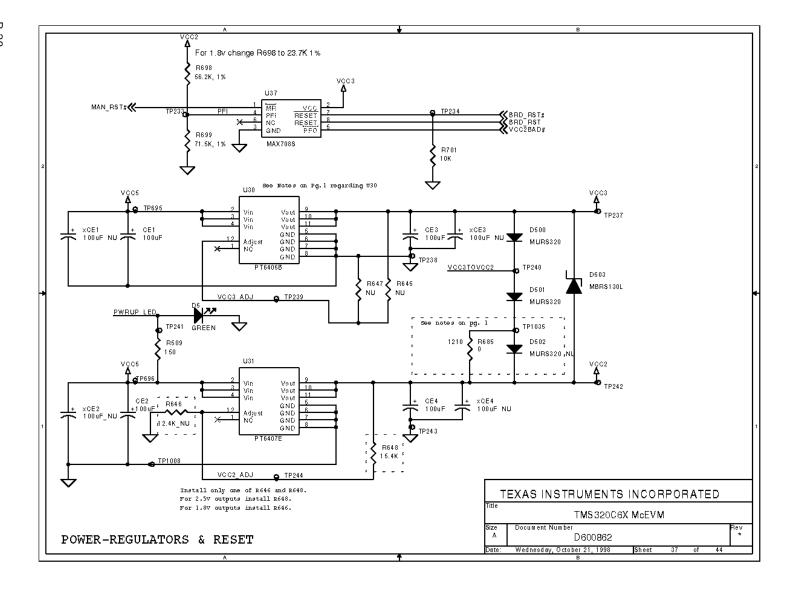

|   | 1.12                                               | 1.12.1 3.3-V Voltage Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|   |                                                    | 1.12.2 1.8-V Voltage Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

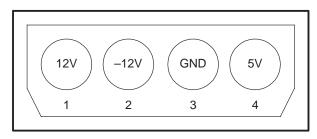

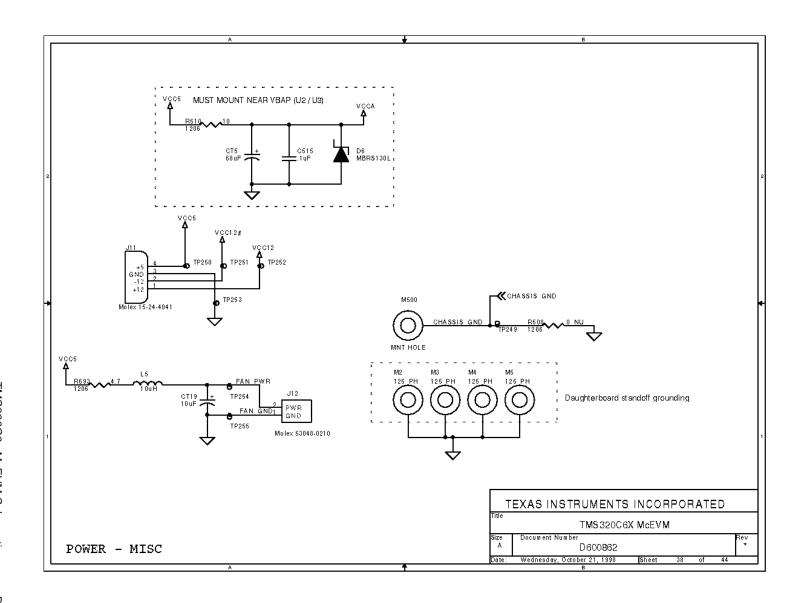

|   |                                                    | 1.12.3 External Power Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

|   |                                                    | 1.12.4 Fan Power Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

|   | 1.13                                               | Voltage Supervision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

|   | 1.14                                               | User Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|   |                                                    | 1.14.1 DIP Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

|   |                                                    | 1.14.2 Jumper Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

|   | 1.15                                               | Indicators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| 2 |                                                    | 320C62x McEVM Host Support Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-1                                                                              |

|   |                                                    | ribes the McEVM host support software components and low-level Windows drivers;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

|   | •                                                  | des an alphabetical summary of the Win32 DLL API functions and examples of how the /M host support software can be used by user-generated Win32 applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

|   | 2.1                                                | Host Support Software Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-2                                                                              |

|   | 2.2                                                | McEVM Low-Level Windows Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

|   | 2.3                                                | McEVM Win32 DLL API                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

|   |                                                    | 2.3.1 McEVM Win32 DLL API Data Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

|   |                                                    | 2.3.2 McEVM Win32 DLL API Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

|   | 2.4                                                | McEVM Host Support Software Example 2-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

|   |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |