# TMS320C6000 Imaging Developer's Kit (IDK) User's Guide

Literature Number: SPRU494A September 2001

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of that third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

### Preface

### **Read This First**

#### About This Manual

The Imaging Developer's Kit (IDK) has been developed as a platform for development and demonstration of image/video processing applications on TMS320C6000<sup>™</sup> DSPs. The IDK is based on the floating point C6711 DSP may also be useful to developers using this platform to develop other algorithms for image, video, graphics processing.

#### How to Use This Manual

This document contains the following chapters:

- Chapter 1 Introduction, provides information about the function and process of the Imaging Developer's Kit (IDK).

- Chapter 2 Hardware Architecture, describes the IDK hardware architecture.

- Chapter 3 Software Architecture Applications Framework, describes the multiple software architecture levels of the IDK.

- Chapter 4 Software Architecture Algorithms Creation, describes algorithm creation in the software architecture.

- Chapter 5 Demonstration Scenarios, describes the demonstration scenarios currently included in the IDK.

- Chapter 6 C6000 DSP Image/Video Processing Applications, describes C6000 DSPs used in image/video processing applications.

- Chapter 7 Testing and Compliance, describes how the initial versions of the IDK meet the testing and compliance requirements.

- Appendix A FPGA Interfaces, describes the FPGA interfaces to the DSP EMIF through an asynchronous SRAM interface.

- Appendix B Scaling Filters Algorithm, describes the scaling filters algorithm.

- □ Appendix C Using Image Data Manager, Demonstrates how to use the DMA streaming routines to implement a sliding window.

- ❑ Appendix D 2D Wavelet Transform Algorithm Example, describes a 2D wavelet transform algorithm.

- □ Appendix E eXpressDSP APIs for IDK Demonstrations, provides the APIs pertinent to IDK demonstrations.

#### **Related Documentation From Texas Instruments**

The following references are provided for further information:

#### **Documentation:**

*TMS320C6000 Imaging Developer's Kit (IDK) Video Device Driver User's Guide* (Literature number SPRU499)

TMS320C6000 Imaging Developer's Kit (IDK) Programmer's Guide (Literature number SPRU495)

#### **IDK Software Architecture Information:**

For ImageLIB Information go to:

http://www.ti.com and navigate to the appropriate site.

#### C6000 JPEG Information:

- □ *TMS320C6000 JPEG Implementation* Application Report (Literature number SPRA704)

- Optimizing JPEG on the TMS320C6211 With 2-Level Cache Application Report (Literature number SPRA705)

#### C6000 H.263 Information:

- □ *H.263 Decoder: TMS320C6000 Implementation* Application Report (Literature number SPRA703)

- □ *H.263 Encoder: TMS320C6000 Implementation* Application Report (Literature number SPRA721)

# Contents

| 1 | Desci                                  | <b>luction</b><br>ibes how the Imaging Developer's Kit (IDK) has been developed as a platform for devel-<br>nt and demonstration of image/video processing applications on TMS320C6000 DSPs.                                                                                                                                                                                                                   |                                                                                                   |

|---|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

|   | 1.1<br>1.2                             | Overview       IDK as a Rapid Prototyping Platform         1.2.1       Rapid Prototyping Software Suite         1.2.2       Rapid Prototyping Hardware                                                                                                                                                                                                                                                         | 1-3<br>1-3                                                                                        |

| 2 |                                        | vare Architecture                                                                                                                                                                                                                                                                                                                                                                                              | 2-1                                                                                               |

|   | 2.1<br>2.2<br>2.3                      | Daughtercard Description<br>Video Capture<br>Video Display                                                                                                                                                                                                                                                                                                                                                     | 2-4                                                                                               |

| 3 |                                        | vare Architecture – Applications Framework                                                                                                                                                                                                                                                                                                                                                                     | 3-1                                                                                               |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6 | Framework for Combining eXpressDSP-Compliant AlgorithmsThe IALG InterfaceIntegrating an Algorithm into the Channel ManagerChannel Manager Object TypesChannel Manager Memory Management3.5.1C6711 DSK Memory Architecture3.5.2Data Memory Requirements of IDK Algorithms3.5.3Internal and External Heaps3.5.4Creation and Deletion of an Algorithm Instance3.5.5Parent Instance Support3.6.1API Reference3.5.2 | 3-6<br>3-8<br>3-9<br>3-12<br>3-12<br>3-12<br>3-12<br>3-12<br>3-13<br>3-14<br>3-15<br>3-16<br>3-17 |

| 4 |                                        | vare Architecture – Algorithms Creation                                                                                                                                                                                                                                                                                                                                                                        | 4-1                                                                                               |

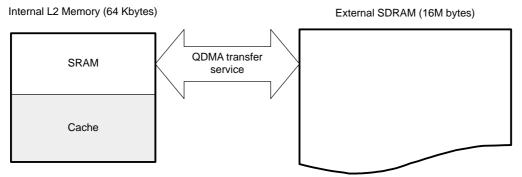

|   | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | ibes algorithm creation in the software architecture.         Overview         eXpressDSP API Wrapper         Algorithm         Image Processing Functions         4         ImageLIB or Custom Kernels         4         Image Data Manager                                                                                                                                                                   | 4-4<br>4-8<br>I-10<br>I-15                                                                        |

| 5 | Demo                | onstrati                                                                                                                                                                     | on Scenarios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-1                                                                                                                                                                                                                                         |

|---|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Desc                | ribes the                                                                                                                                                                    | e demonstration scenarios currently included in the IDK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                             |

|   | 5.1                 | JPEG                                                                                                                                                                         | Loop-Back Demonstration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-2                                                                                                                                                                                                                                         |

|   |                     | 5.1.1                                                                                                                                                                        | Data I/O and User Input Specifics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                             |

|   |                     | 5.1.2                                                                                                                                                                        | Signal Processing Operations Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                             |

|   |                     | 5.1.3                                                                                                                                                                        | eXpressDSP APIs for JPEG Loop-Back Demonstration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                             |

|   | 5.2                 | H.263                                                                                                                                                                        | Multichannel Decoder Demonstration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                             |

|   |                     | 5.2.1                                                                                                                                                                        | Data I/O and User Input Specifics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                             |

|   |                     | 5.2.2                                                                                                                                                                        | Signal Processing Operations Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                             |

|   |                     | 5.2.3                                                                                                                                                                        | eXpressDSP APIs for H.263 Multichannel Decoder Demonstration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                             |

|   | 5.3                 | Image                                                                                                                                                                        | Processing Demonstration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-8                                                                                                                                                                                                                                         |

|   |                     | 5.3.1                                                                                                                                                                        | Data I/O and User Input Specifics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                             |

|   |                     | 5.3.2                                                                                                                                                                        | Signal Processing Operations Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                             |

|   |                     | 5.3.3                                                                                                                                                                        | eXpressDSP APIs for Image Processing Demonstration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                             |

|   | 5.4                 | H.263                                                                                                                                                                        | Loop-Back Demonstration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                             |

|   |                     | 5.4.1                                                                                                                                                                        | Data I/O and User Input Specifics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                             |

|   |                     | 5.4.2                                                                                                                                                                        | Signal Processing Operations Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                             |

|   |                     | 5.4.3                                                                                                                                                                        | eXpressDSP APIs for H.263 Loop-Back Demonstration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-13                                                                                                                                                                                                                                        |

|   | 5.5                 | 2D Wa                                                                                                                                                                        | velet Transform Demonstration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                             |

|   |                     | 5.5.1                                                                                                                                                                        | Data I/O and User Input Specifics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-14                                                                                                                                                                                                                                        |

|   |                     | 5.5.2                                                                                                                                                                        | Signal Processing Operations Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-14                                                                                                                                                                                                                                        |

|   |                     | 5.5.3                                                                                                                                                                        | eXpressDSP APIs for 2D Wavelet Transform Demonstration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                             |

|   |                     |                                                                                                                                                                              | or proceder if a relief 2B travelet transform Bennenbalation internet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                             |

| 6 | C600                |                                                                                                                                                                              | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                             |

| 6 |                     | 0 DSP I                                                                                                                                                                      | mage/Video Processing Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                             |

| 6 | Desc                | <b>0 DSP I</b><br>ribes C6                                                                                                                                                   | mage/Video Processing Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-1                                                                                                                                                                                                                                         |

| 6 | Desci<br>6.1        | <b>0 DSP I</b><br>ribes C6<br>Overvi                                                                                                                                         | mage/Video Processing Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ••••••••••••••••••••••••••••••••••••••                                                                                                                                                                                                      |

| 6 | Desc                | <b>0 DSP I</b><br>ribes C6<br>Overvi<br>JPEG                                                                                                                                 | mage/Video Processing Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-1<br>6-2<br>6-3                                                                                                                                                                                                                           |

| 6 | Desci<br>6.1        | <b>0 DSP I</b><br>ribes C6<br>Overvi<br>JPEG<br>6.2.1                                                                                                                        | mage/Video Processing Applications         6000 DSPs used in image/video processing applications.         ew         Encoder         JPEG Encoder Algorithm Level Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6-1<br>6-2<br>6-3<br>6-3                                                                                                                                                                                                                    |

| 6 | Desci<br>6.1        | 0 DSP I<br>ribes C6<br>Overvi<br>JPEG<br>6.2.1<br>6.2.2                                                                                                                      | mage/Video Processing Applications         S000 DSPs used in image/video processing applications.         ew         Encoder         JPEG Encoder Algorithm Level Description         JPEG Encoder Capabilities and Restrictions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6-1<br>6-2<br>6-3<br>6-3<br>6-5                                                                                                                                                                                                             |

| 6 | Desci<br>6.1        | 0 DSP I<br>ribes C6<br>Overvi<br>JPEG<br>6.2.1<br>6.2.2<br>6.2.3                                                                                                             | mage/Video Processing Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-1<br>6-2<br>6-3<br>6-3<br>6-5<br>6-6                                                                                                                                                                                                      |

| 6 | Desci<br>6.1        | 0 DSP I<br>ribes C6<br>Overvi<br>JPEG<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4                                                                                                    | mage/Video Processing Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-1<br>6-2<br>6-3<br>6-3<br>6-5<br>6-6<br>6-7                                                                                                                                                                                               |

| 6 | Desc.<br>6.1<br>6.2 | 0 DSP In<br>ribes C6<br>Overvi<br>JPEG<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5                                                                                          | mage/Video Processing Applications         5000 DSPs used in image/video processing applications.         ew         Encoder         JPEG Encoder Algorithm Level Description         JPEG Encoder Capabilities and Restrictions         JPEG Encoder API         JPEG Encoder Performance         Further Information on JPEG Encoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6-1<br>6-2<br>6-3<br>6-3<br>6-5<br>6-6<br>6-7<br>6-8                                                                                                                                                                                        |

| 6 | Desci<br>6.1        | 0 DSP In<br>ribes C6<br>Overvi<br>JPEG<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>JPEG                                                                                  | mage/Video Processing Applications         S000 DSPs used in image/video processing applications.         ew         Encoder         JPEG Encoder Algorithm Level Description         JPEG Encoder Capabilities and Restrictions         JPEG Encoder API         JPEG Encoder Performance         Further Information on JPEG Encoder         Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6-1<br>6-2<br>6-3<br>6-3<br>6-5<br>6-6<br>6-7<br>6-8<br>6-9                                                                                                                                                                                 |

| 6 | Desc.<br>6.1<br>6.2 | 0 DSP In<br>ribes C6<br>Overvi<br>JPEG<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>JPEG<br>6.3.1                                                                         | mage/Video Processing Applications         6000 DSPs used in image/video processing applications.         ew         Encoder         JPEG Encoder Algorithm Level Description         JPEG Encoder Capabilities and Restrictions         JPEG Encoder API         JPEG Encoder Performance         Further Information on JPEG Encoder         Decoder         JPEG Decoder Algorithm Level Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6-1<br>6-2<br>6-3<br>6-3<br>6-3<br>6-5<br>6-6<br>6-7<br>6-8<br>6-9<br>6-9                                                                                                                                                                   |

| 6 | Desc.<br>6.1<br>6.2 | 0 DSP In<br>ribes C6<br>Overvi<br>JPEG<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>JPEG<br>6.3.1<br>6.3.2                                                                | mage/Video Processing Applications.         6000 DSPs used in image/video processing applications.         ew         Encoder         JPEG Encoder Algorithm Level Description         JPEG Encoder Capabilities and Restrictions         JPEG Encoder API         JPEG Encoder Performance         Further Information on JPEG Encoder         JPEG Decoder Algorithm Level Description         JPEG Decoder Capabilities and Restrictions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6-1<br>6-2<br>6-3<br>6-3<br>6-3<br>6-5<br>6-6<br>6-7<br>6-8<br>6-9<br>6-9<br>6-11                                                                                                                                                           |

| 6 | Desc.<br>6.1<br>6.2 | 0 DSP In<br>ribes C6<br>Overvi<br>JPEG<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>JPEG<br>6.3.1<br>6.3.2<br>6.3.3                                                       | mage/Video Processing Applications         6000 DSPs used in image/video processing applications.         ew         Encoder         JPEG Encoder Algorithm Level Description         JPEG Encoder Capabilities and Restrictions         JPEG Encoder API         JPEG Encoder Performance         Further Information on JPEG Encoder         Decoder         JPEG Decoder Algorithm Level Description         JPEG Decoder Algorithm Level Description         JPEG Decoder Algorithm Level Description         JPEG Decoder API                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-1<br>6-2<br>6-3<br>6-3<br>6-5<br>6-5<br>6-6<br>6-7<br>6-8<br>6-9<br>6-9<br>6-11<br>6-12                                                                                                                                                   |

| 6 | Desc.<br>6.1<br>6.2 | 0 DSP In<br>ribes C6<br>Overvi<br>JPEG<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>JPEG<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4                                              | mage/Video Processing Applications.         6000 DSPs used in image/video processing applications.         ew         Encoder         JPEG Encoder Algorithm Level Description         JPEG Encoder Capabilities and Restrictions         JPEG Encoder API         JPEG Encoder Performance         Further Information on JPEG Encoder         Decoder         JPEG Decoder Capabilities and Restrictions         JPEG Decoder Algorithm Level Description         JPEG Decoder Performance         JPEG Decoder Algorithm Level Description         JPEG Decoder Algorithm Level Description         JPEG Decoder Performance         JPEG Decoder Performance         JPEG Decoder Performance         JPEG Decoder Performance                                                                                                                                                                                                                                                                             | 6-1<br>6-2<br>6-3<br>6-3<br>6-5<br>6-5<br>6-6<br>6-7<br>6-8<br>6-9<br>6-9<br>6-11<br>6-12<br>6-14                                                                                                                                           |

| 6 | Desc.<br>6.1<br>6.2 | 0 DSP In<br>ribes C6<br>Overvi<br>JPEG<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>JPEG<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5                                     | mage/Video Processing Applications.         6000 DSPs used in image/video processing applications.         ew         Encoder         JPEG Encoder Algorithm Level Description         JPEG Encoder Capabilities and Restrictions         JPEG Encoder API         JPEG Encoder Performance         Further Information on JPEG Encoder         Decoder         JPEG Decoder Capabilities and Restrictions         JPEG Decoder API         JPEG Decoder API         JPEG Decoder Algorithm Level Description         JPEG Decoder API         JPEG Decoder Performance         JPEG Decoder Performance         JPEG Decoder Performance         JPEG Decoder Performance         JPEG Decoder API         JPEG Decoder Performance         Further Information on JPEG Decoder                                                                                                                                                                                                                               |                                                                                                                                                                                                                                             |

| 6 | Desc.<br>6.1<br>6.2 | 0 DSP In<br>ribes C6<br>Overvi<br>JPEG<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>JPEG<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5<br>H.263                            | mage/Video Processing Applications.         6000 DSPs used in image/video processing applications.         ew         Encoder         JPEG Encoder Algorithm Level Description         JPEG Encoder Capabilities and Restrictions         JPEG Encoder API         JPEG Encoder Performance         Further Information on JPEG Encoder         JPEG Decoder Algorithm Level Description         JPEG Decoder Performance         JPEG Decoder Performance         JPEG Decoder Performance         JPEG Decoder Performance         Further Information on JPEG Decoder         Further Information on JPEG Decoder         Encoder                                                                                                                                                                                                                        | 6-1            6-3            6-3            6-3            6-5            6-6            6-7            6-8            6-9            6-11            6-12            6-14            6-15                                                 |

| 6 | Desc.<br>6.1<br>6.2 | 0 DSP In<br>ribes C6<br>Overvi<br>JPEG<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>JPEG<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5<br>H.263<br>6.4.1                   | mage/Video Processing Applications.         6000 DSPs used in image/video processing applications.         ew         Encoder         JPEG Encoder Algorithm Level Description         JPEG Encoder Capabilities and Restrictions         JPEG Encoder API         JPEG Encoder Performance         Further Information on JPEG Encoder         Decoder         JPEG Decoder Algorithm Level Description         JPEG Decoder Algorithm Level Description         JPEG Decoder Performance         Further Information on JPEG Encoder         JPEG Decoder Algorithm Level Description         JPEG Decoder Performance         Further Information on JPEG Decoder         Encoder         H.263 Encoder Algorithm Level Description | 6-1                                                                                                                                                                                                                                         |

| 6 | Desc.<br>6.1<br>6.2 | 0 DSP In<br>ribes C6<br>Overvi<br>JPEG<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>JPEG<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5<br>H.263<br>6.4.1<br>6.4.2          | mage/Video Processing Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-1                                                                                                                                                                                                                                         |

| 6 | Desc.<br>6.1<br>6.2 | 0 DSP In<br>ribes C6<br>Overvi<br>JPEG<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>JPEG<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5<br>H.263<br>6.4.1<br>6.4.2<br>6.4.3 | mage/Video Processing Applications.         6000 DSPs used in image/video processing applications.         ew         Encoder         JPEG Encoder Algorithm Level Description         JPEG Encoder Capabilities and Restrictions         JPEG Encoder API         JPEG Encoder Performance         Further Information on JPEG Encoder         Decoder         JPEG Decoder Capabilities and Restrictions         JPEG Decoder Algorithm Level Description         JPEG Decoder Capabilities and Restrictions         JPEG Decoder Performance         Further Information on JPEG Encoder         JPEG Decoder Capabilities and Restrictions         JPEG Decoder API         JPEG Decoder API         JPEG Decoder API         JPEG Decoder Performance         Further Information on JPEG Decoder         Encoder         H.263 Encoder Algorithm Level Description         H.263 Encoder Capabilities and Restrictions         H.263 Encoder Capabilities and Restrictions         H.263 Encoder API     | 6-1            6-2            6-3            6-3            6-5            6-6            6-7            6-8            6-9            6-11            6-12            6-14            6-15            6-15            6-17            6-18 |

| 6 | Desc.<br>6.1<br>6.2 | 0 DSP In<br>ribes C6<br>Overvi<br>JPEG<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>JPEG<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5<br>H.263<br>6.4.1<br>6.4.2          | mage/Video Processing Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-1                                                                                                                                                                                                                                         |

|   | 6.5                             | H.263 Decoder       6-21         6.5.1       H.263 Decoder Algorithm Level Description       6-21         6.5.2       H.263 Decoder Capabilities and Restrictions       6-24         6.5.3       H.263 Decoder API       6-24         6.5.4       H.263 Decoder Performance       6-26 |

|---|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 6.6                             | 6.5.5Further Information on H.263 Decoder6-27ImageLIB – Library of Optimized Kernels6-286.6.1Further Information on ImageLIB6-35                                                                                                                                                       |

| 7 |                                 | and Compliance                                                                                                                                                                                                                                                                         |

| Α |                                 | InterfacesA-1ibes the FPGA interfaces to the DSP EMIF through an asynchronous SRAM interface.A-2I2C InterfaceA-2EMIF ASRAM InterfaceA-3A.2.1CE SelectionA-3A.2.2IDK Memory MapA-3A.2.3FPGA Control RegistersA-5                                                                        |

| В |                                 | ng Filters Algorithm                                                                                                                                                                                                                                                                   |

| С | -                               | Image Data Manager C-1<br>nstrates how to use the DMA streaming routines to implement a sliding window.                                                                                                                                                                                |

| D |                                 | avelet Transform Algorithm Example D-1<br>ibes a 2D wavelet transform algorithm.                                                                                                                                                                                                       |

| Е | -                               | essDSP APIs for IDK Demonstrations E-1                                                                                                                                                                                                                                                 |

|   | E.1<br>E.2<br>E.3<br>E.4<br>E.5 | eXpressDSP API OverviewE-2eXpressDSP API for Pre-Scale FilterE-3eXpressDSP API for Color Space ConversionE-5eXpressDSP API for Image Processing FunctionsE-7eXpressDSP API for Wavelet TransformE-9                                                                                    |

# Figures

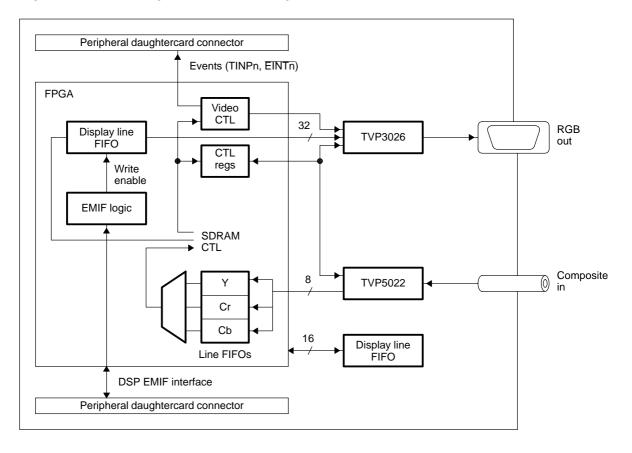

| 2–1  | IDK daughtercard Block Diagram                                           | 2-3  |

|------|--------------------------------------------------------------------------|------|

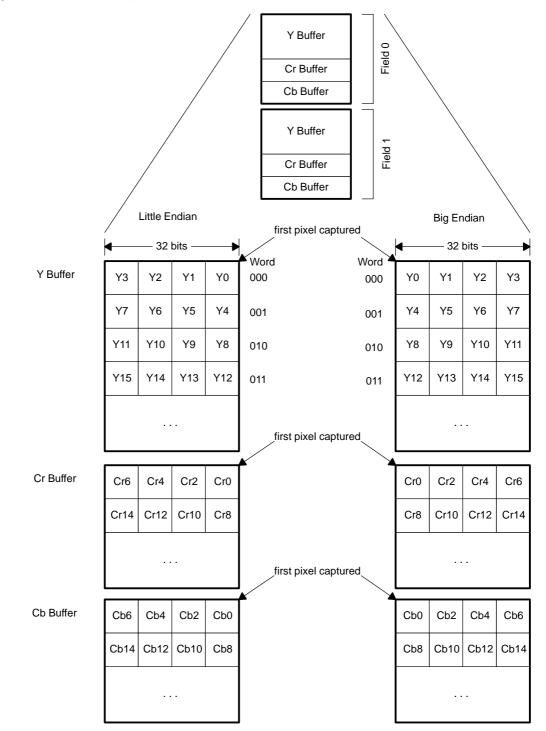

| 2–2  | NTSC Capture (1 of 3 frames shown)                                       | 2-5  |

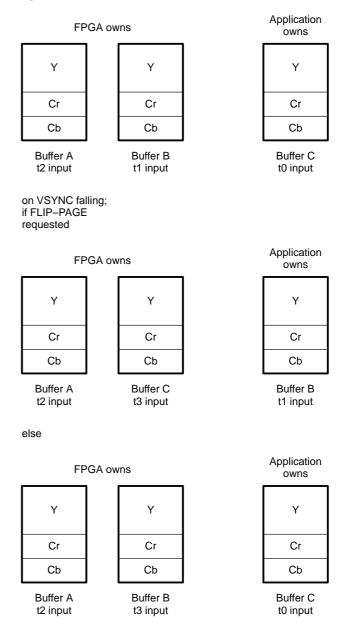

| 2–3  | Capture Buffer Management                                                | 2-7  |

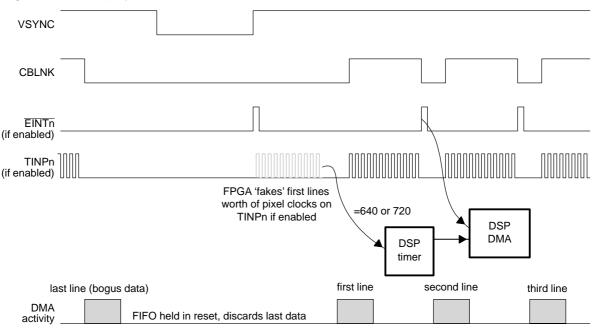

| 2–4  | Display Event Generation                                                 | 2-11 |

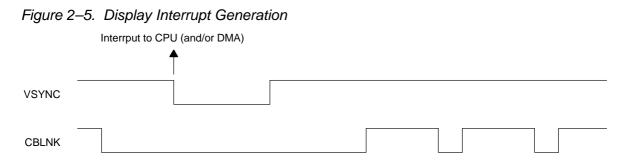

| 2–5  | Display Interrupt Generation                                             | 2-12 |

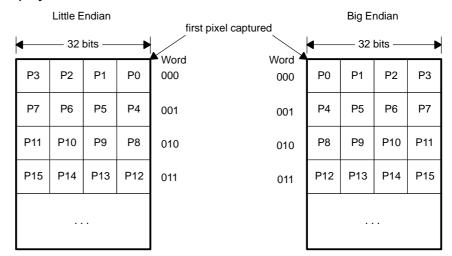

| 2–6  | GRAY8 Display Buffer Format                                              | 2-13 |

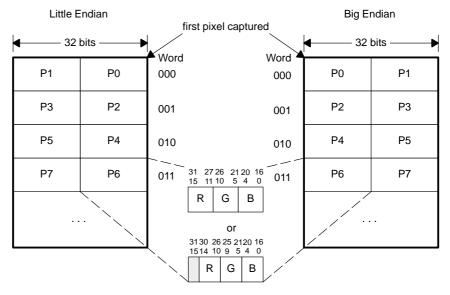

| 2–7  | RGB16 Display Buffer Format                                              | 2-13 |

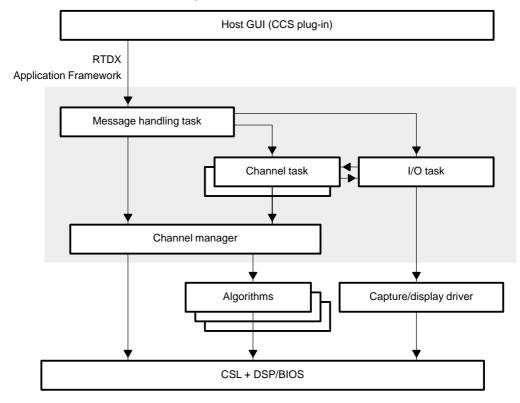

| 3–1  | IDK Demo Block Diagram                                                   | 3-3  |

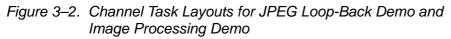

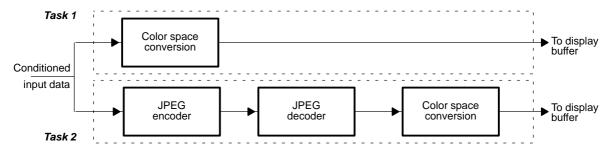

| 3–2  | Channel Task Layouts for JPEG Loop-Back Demo and Image Processing Demo . |      |

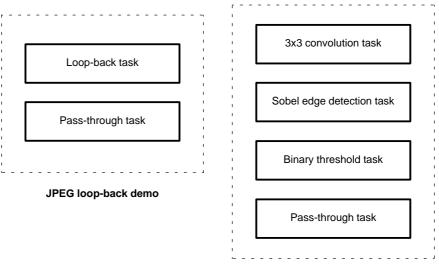

| 3–3  | JPEG Loop-Back Channel                                                   |      |

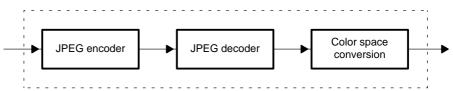

| 3–4  | JPEG Loop-Back Demo Channels and I/O Buffers                             | 3-11 |

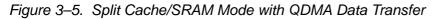

| 3–5  | Split Cache/SRAM Mode with QDMA Data Transfer                            | 3-12 |

| 4–1  | Software Architecture for ImageLIB Functions-Based Standard Algorithms   |      |

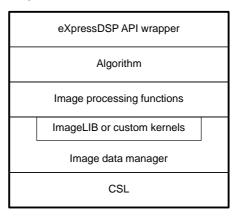

| 4–2  | 2D Wavelet Transform                                                     | 4-3  |

| 5–1  | JPEG Loop-Back Demonstration                                             | 5-2  |

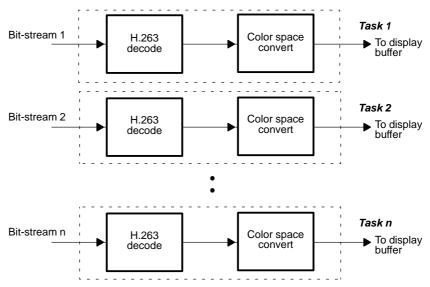

| 5–2  | Multichannel H.263 Decode Demonstration                                  | 5-5  |

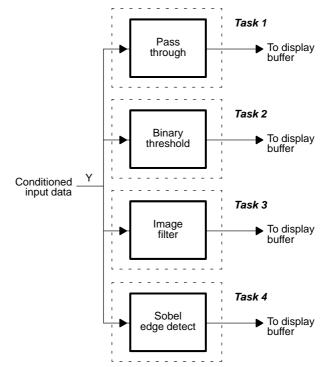

| 5–3  | Image Processing Demonstration                                           | 5-8  |

| 5–4  | Image Processing Demonstration Display                                   | 5-8  |

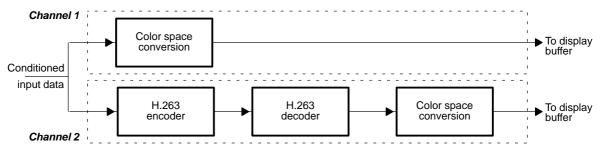

| 5–5  | H.263 Loop-Back Demonstration                                            | 5-11 |

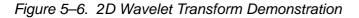

| 5–6  | 2D Wavelet Transform Demonstration                                       | 5-14 |

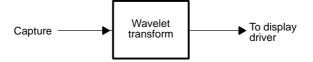

| 5–7  | 2D Wavelet Transform Components                                          | 5-14 |

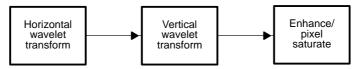

| 6–1  | JPEG Encoder                                                             | 6-3  |

| 6–2  | Raster Scanned Image Data                                                | 6-3  |

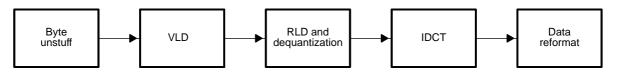

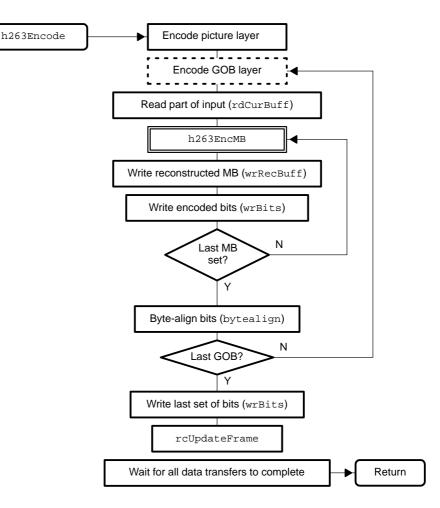

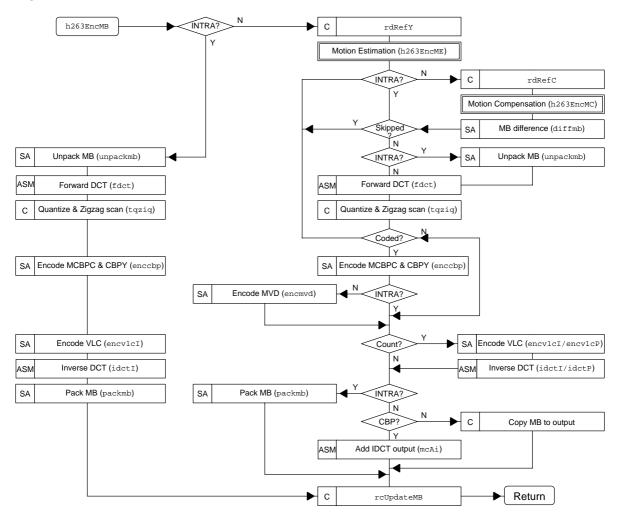

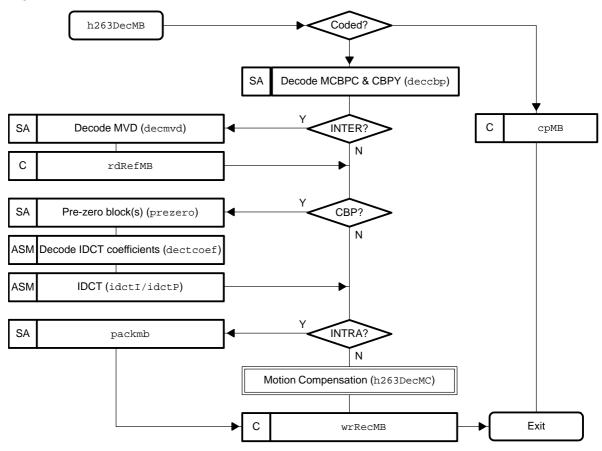

| 6–3  | Reformatted Image Data                                                   | 6-3  |