# Powering AMIC110, AMIC120, AM335x, and AM437x with TPS65216

System designs utilizing the TPS65216 Power Management IC must follow this user's guide for connectivity with the following processors:

- Sitara™ AMIC110 and AMIC120 industrial communications processors

- Sitara AM335x and AM437x Arm<sup>®</sup> application processors

### Contents

| 1 | TPS65216 Overview                         | 2  |

|---|-------------------------------------------|----|

| 2 | Connection Diagram for AMIC110            | 3  |

|   | 2.1 Power Rails for AMIC110               | 4  |

| 3 | Connection Diagram for AM335x             | 5  |

|   | 3.1 Power Rails for AM335x                | 6  |

| 4 | Connection Diagram for AMIC120 and AM437x | 7  |

|   | 4.1 Power Rails for AMIC120 and AM437x    | 9  |

| 5 | Power Rails for RTC Domain                | 10 |

| 6 | TPS65216 Supply Sequencing                |    |

| 7 | Memory Voltage Selection                  | 12 |

| 8 | Warm Reset                                |    |

| 9 | Pullup Resistors                          | 12 |

### List of Figures

| 1 | AMIC110 Connection Diagram                        | 3  |

|---|---------------------------------------------------|----|

| 2 | AM335x Connection Diagram                         | 5  |

| 3 | AMIC120 and AM437x Connection Diagram             | 7  |

| 4 | AMIC120 and AM437x Connection Diagram With LPDDR2 | 8  |

| 5 | Power Rails for RTC Domain                        | 10 |

| 6 | TPS65216 Sequencing Diagram                       | 11 |

| 7 | TPS65216 Warm Reset Functionality                 | 12 |

## List of Tables

| 1 | Power Rails for AMIC110            | 4  |

|---|------------------------------------|----|

| 2 | Power Rails for AM335x             | 6  |

| 3 | Power Rails for AMIC120 and AM437x | 9  |

| 4 | TPS65216 Strobe Sequence           | 11 |

| 5 | DCDC3 Voltage Selection            | 12 |

## Trademarks

Sitara is a trademark of Texas Instruments.

Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

2

#### 1 **TPS65216 Overview**

The TPS65216 is an integrated Power Management IC for Sitara processors:

- Power sequencing for Sitara AMIC, AM3, and AM4 processors •

- Three DC-DC step-down converters ٠

- One LDO and one Load-Switch

- Active output discharge on all supplies ٠

- Integrated voltage supervisor ٠

- Power fail comparator for external or system supply ٠

## 2 Connection Diagram for AMIC110

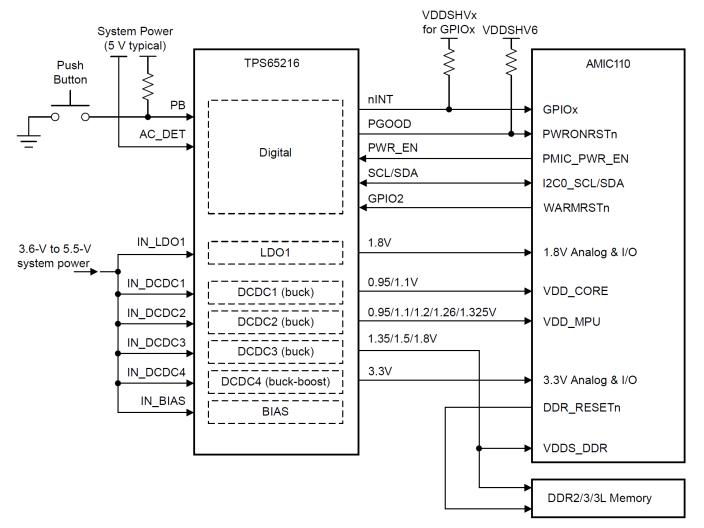

Figure 1 describes the supply mapping between AMIC110 and the TPS65216. Any ICs on the board that interface with AMIC110 should use DCDC4 for 3.3 V I/O supply and LDO1 for 1.8 V I/O supply.

Figure 1. AMIC110 Connection Diagram

4

## 2.1 Power Rails for AMIC110

| TPS65216 | Voltage (V)             | AMIC110                |

|----------|-------------------------|------------------------|

| DCDC1    | 0.95/1.1                | VDD_CORE               |

| DCDC2    | 0.95/1.1/1.2/1.26/1.325 | VDD_MPU                |

| DCDC3    | 1.35/1.5                | VDDS_DDR<br>DDR3L/DDR3 |

| DCDC4    | 2.2                     | VDDSHVx (3.3 V)        |

| DCDC4    | DCDC4 3.3               | VDDA3P3V_USB0/1        |

|          |                         | VDDS                   |

|          |                         | VDDS_RTC               |

|          | 1.8                     | VDDSHVx (1.8 V)        |

|          |                         | VDDS_SRAM_CORE_BG      |

| LDO1     |                         | VDDS_SRAM_MPU_BB       |

| LDOT     |                         | VDDS_PLL_DDR           |

|          |                         | VDDS_PLL_CORE_LCD      |

|          |                         | VDDS_OSC               |

|          |                         | VDDA1P8V_USB0/1        |

|          |                         | VDDA_ADC               |

## Table 1. Power Rails for AMIC110

## 3 Connection Diagram for AM335x

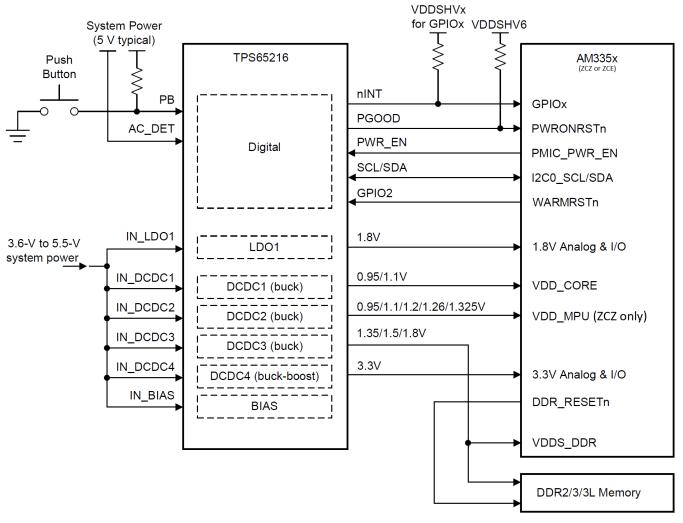

Figure 2 shows the connections between AM335x and the TPS65216. When using the ZCE package, VDD\_CORE and VDD\_MPU are combined on the device. The combined supply input should be connected to DCDC1 and DCDC2 can be left not-connected. Any ICs on the board that interface with AMIC110 should use DCDC4 for 3.3 V I/O supply and LDO1 for 1.8 V I/O supply.

Figure 2. AM335x Connection Diagram

Connection Diagram for AM335x

6

## 3.1 Power Rails for AM335x

| TPS65216 | Voltage (V)             | AM335x                 |

|----------|-------------------------|------------------------|

| DCDC1    | 0.95/1.1                | VDD_CORE               |

| DCDC2    | 0.95/1.1/1.2/1.26/1.325 | VDD_MPU                |

| DCDC3    | 1.35/1.5                | VDDS_DDR<br>DDR3L/DDR3 |

| DCDC4    | 2.2                     | VDDSHVx (3.3 V)        |

| DCDC4    | 3.3                     | VDDA3P3V_USB0/1        |

|          |                         | VDDS                   |

|          |                         | VDDS_RTC               |

|          |                         | VDDSHVx (1.8 V)        |

|          |                         | VDDS_SRAM_CORE_BG      |

| 1001     |                         | VDDS_SRAM_MPU_BB       |

| LDO1     | 1.8                     | VDDS_PLL_DDR           |

|          |                         | VDDS_PLL_CORE_LCD      |

|          |                         | VDDS_OSC               |

|          |                         | VDDA1P8V_USB0/1        |

|          |                         | VDDA_ADC               |

## Table 2. Power Rails for AM335x

Connection Diagram for AMIC120 and AM437x

## 4 Connection Diagram for AMIC120 and AM437x

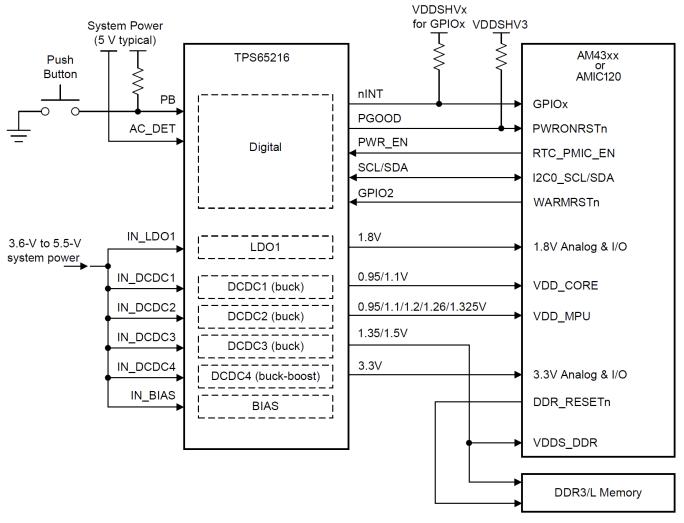

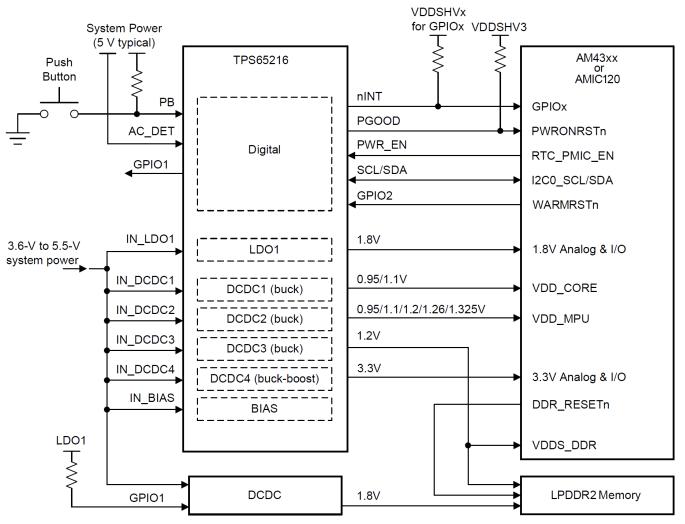

Figure 3 shows the connections between AM437x or AMIC120 and the TPS65216. If LPDDR2 memory is used, an additional 1.8 V supply is required. GPIO1 is programmed to properly sequence the additional supply and should be tied to the external supply's enable pin as seen in Figure 4. To adjust the DCDC3 voltage for each DDR type, see Section 7.

Figure 3. AMIC120 and AM437x Connection Diagram

Connection Diagram for AMIC120 and AM437x

8

www.ti.com

Figure 4. AMIC120 and AM437x Connection Diagram With LPDDR2

Connection Diagram for AMIC120 and AM437x

## www.ti.com

## 4.1 Power Rails for AMIC120 and AM437x

Table 3 matches the AMIC120 power terminals with the appropriate power rail from the TPS65216. It also matches for AM437x.

| TPS65216 | Voltage (V)             | AM437x                        |

|----------|-------------------------|-------------------------------|

| DCDC1    | 0.95/1.1                | VDD_CORE                      |

| DCDC2    | 0.95/1.1/1.2/1.26/1.325 | VDD_MPU                       |

| DCDC3    | 1.2/1.35/1.5            | VDDS_DDR<br>LPDDR2/DDR3L/DDR3 |

|          | 3.3                     | VDDSHVx(3.3 V)                |

| DCDC4    |                         | VDDA3P3V_USB0/1               |

|          |                         | VDDS3P3V_IOLDO                |

|          |                         | VDDS                          |

|          |                         | VDDS_RTC                      |

|          | LDO1 1.8                | VDDSHVx(1.8 V)                |

|          |                         | VDDS_SRAM_CORE_BG             |

|          |                         | VDDS_SRAM_MPU_BB              |

| 1001     |                         | VDDS_PLL_DDR                  |

| EDOT     |                         | VDDS_PLL_CORE_LCD             |

|          |                         | VDDS_OSC                      |

|          |                         | VDDA1P8V_USB0/1               |

|          |                         | VDDA_ADC0/1                   |

|          |                         | VDDS_PLL_MPU                  |

|          |                         | VDDS_CLKOUT                   |

### Table 3. Power Rails for AMIC120 and AM437x

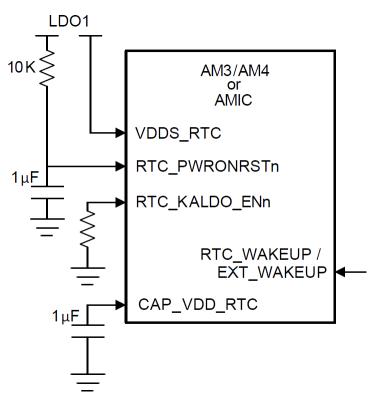

#### 5 **Power Rails for RTC Domain**

For normal RTC operation during the Sitara processor ACTIVE state, see Figure 5. The connection diagram can stay the same if the RTC is not used; the RTC does not need to be explicitly disabled. The resistor + capacitor on RTC\_PWRONRSTn is required to ensure the 1.8 V supply is stable before reset release. Connecting RTC\_PWRONRSTn directly to 1.8 V causes unpredictable behavior.

This diagram does not support the RTC-only power state. RTC data is lost when LDO1 and the processor is powered off. To keep RTC data in between power states a dedicated, always-on 1.8 V supply for VDDS\_RTC is required. This can be done by following the below diagram except replace LDO1 with an always-on 1.8 V supply.

Figure 5. Power Rails for RTC Domain

TPS65216 Supply Sequencing

## www.ti.com

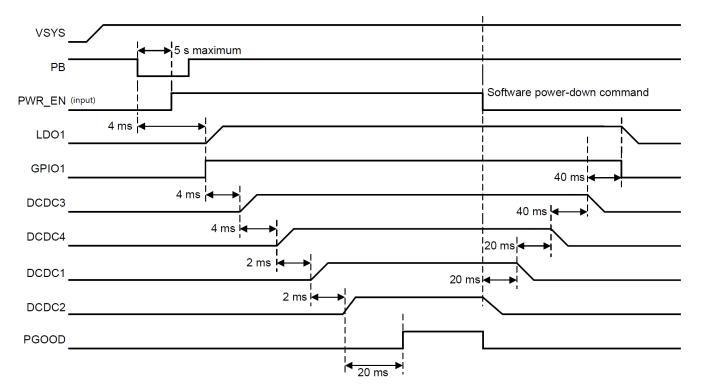

## 6 TPS65216 Supply Sequencing

The TPS65216 supply sequencer is controlled by a series of strobes with a 2 or 4 ms delay in between. A visual reference for the power-up and power-down sequence of the TPS65216 is shown in Figure 6. For a table of the strobes and assignments, see Table 4. No changes to the defaults are required; this sequence is designed for AMIC110, AMIC120, AM335x, and AM437x.

Figure 6. TPS65216 Sequencing Diagram

The power-up sequence is defined by a series of ten strobes and nine delay times. Each output rail is assigned to a strobe to determine the order in which the rails are enabled. The delay time in-between strobes is 2 ms by default. Table 4 lists the default strobe assignments for TPS65216.

The power-down sequence is the reverse of the power-up sequence. However, strobe 1 and 2 are not included in the power-down. Any supplies assigned to strobe 1 or 2 will remain powered on at the end of the power-down sequence.

| Strobe 1  |       |

|-----------|-------|

| Strobe 2  |       |

| Strobe 3  | LDO1  |

| Stible 5  | GPIO1 |

| Strobe 4  |       |

| Strobe 5  | DCDC3 |

| Strobe 6  |       |

| Strobe 7  | DCDC4 |

| Strobe 8  | DCDC1 |

| Strobe 9  | DCDC2 |

| Strobe 10 |       |

## 7 Memory Voltage Selection

DCDC3 can be configured to support a variety of DDR memory voltages. The desired voltage can be selected by placing a 1% resistor to ground on the DC34\_SEL pin. Table 5 lists the available memory voltages and the needed resistor for each.

| Memory | DCDC3 Voltage (V) | Resistor (kΩ)     |

|--------|-------------------|-------------------|

| LPDDR2 | 1.2               | 0 (tie to ground) |

| DDR3L  | 1.35              | 12.1              |

| DDR3   | 1.5               | 20                |

| DDR2   | 1.8               | 31.6              |

## Table 5. DCDC3 Voltage Selection

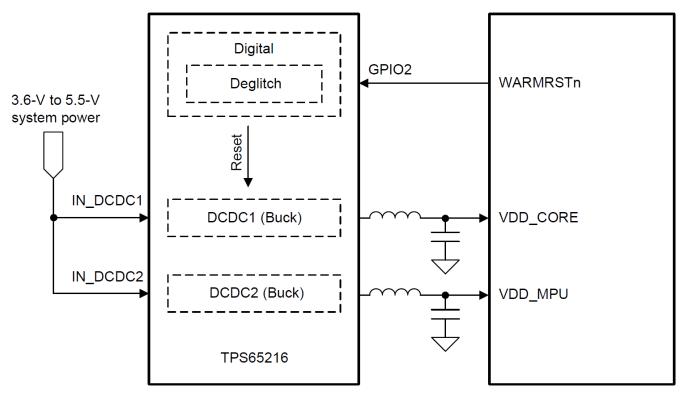

## 8 Warm Reset

The TPS65216 supports warm reset functionality that is enabled by default and can be disabled through I2C. When enabled, asserting GPIO2 low causes DCDC1 and DCDC2 to slew back to their default value of 1.1 V.

Figure 7. TPS65216 Warm Reset Functionality

## 9 Pullup Resistors

The TPS65216 PMIC uses open-drain outputs for nINT, PGOOD, SCL, and SDA. These signals should be pulled up using the same supply that powers VDDSHVx for each signal on the Sitara SoC. For example. I2C0 on AM335x is in the VDDSHV6 I/O domain. This VDDSHV6 is supplied by DCDC4 at 3.3 V. Therefore, I2C0 SCL and SDA should be pulled up to 3.3 V from DCDC4. If VDDSHV6 was operating at 1.8 V supplied by LDO1, then I2C0 SCL and SDA should be pulled up to 1.8 V from LDO1.

The PB input needs to operate at all times so it should be pulled up to VSYS.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated