# Test Report: PMP30600-AH 20-A Automotive Pre-Regulator Reference Design

# TEXAS INSTRUMENTS

#### Description

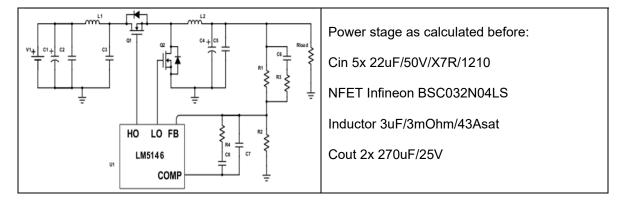

This reference design is a 100W synchronous buck converter primarily to supply automotive loads. The IC is LM5146-Q1 in fixed frequency operation at 250 kHz to ensure low noise operation. To minimize conducted emissions an input filter prevents from reflected ripple. Furthermore a RC snubber attenuates noise in the RF band to reduce radiated emissions. To reduce system EMI the design is prepared either to synchronize other converters (output) or just to be externally synchronized (input). The power stage itself withstands surge voltages up to 36Vpk.

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

# **1** Test Prerequisites

# 1.1 Voltage and Current Requirements

| PARAMETER                      | SPECIFICATIONS |

|--------------------------------|----------------|

| Input Voltage Range            | 6 V to 18 V    |

| Output Voltage                 | 5 V            |

| Maximum Output Current         | 20 A           |

| Calculated Switching Frequency | 250 kHz        |

# Table 1. Voltage and Current Requirements

#### 1.2 Considerations\*

2

This circuit is realized on PCB PMP30600RevA

# 2 Testing and Results

#### 2.1 Efficiency Graphs

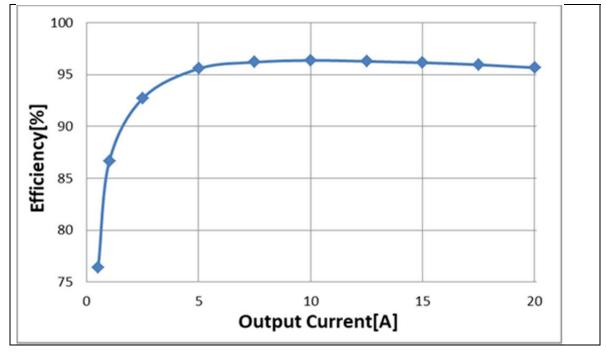

The efficiency is shown in the Figure 1 below. The input voltage was set to 14V

Figure 1

**Full load efficiency 95.65%**, calculated 95.9%; Deviation by self heating of inductor and switching losses

Maximum efficiency 96.36% at 10A.

Efficiency ≥95% in a range 5A to 20A, so 25% load to 100% load

#### 2.2 Load Regulation

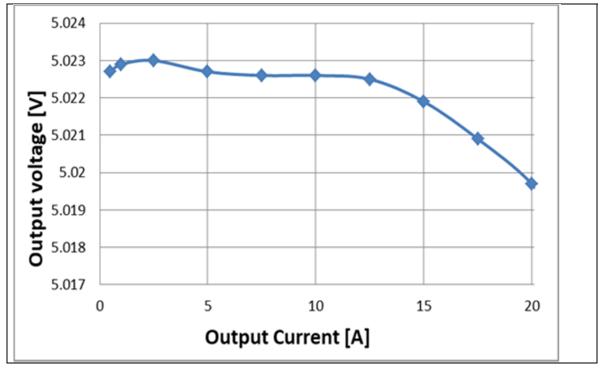

The load regulation of the output is shown in the Figure 2 below. The input voltage was set to 14V.

Min. Vout 5.0179V, max Vout 5.0229V,

Output voltage variation 5.0mV, so 0.1%, negligible.

#### 2.3 Thermal Images

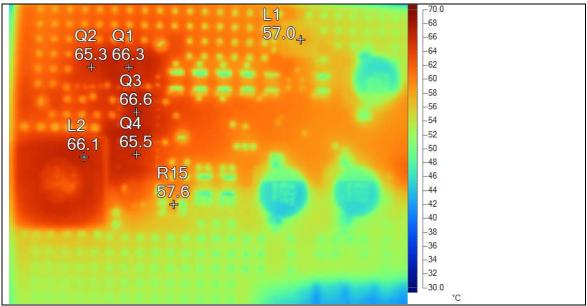

Thermal image at 14V input and full load 20Amp after 20 minutes continuous operation [Rt = 23c]:

| Name | Temperature |

|------|-------------|

| Q1   | 66.3°C      |

| Q2   | 65.3°C      |

| Q3   | 66.6°C      |

| Q4   | 65.5°C      |

| L1   | 57.0°C      |

| L2   | 66.1°C      |

| R15  | 57.6°C      |

Temperature rise is below 50K, a proper design of the power stage with maximum efficiency results in relaxed thermal stress because inductor and MOSFETs are almost same temperature; good balance.

#### 2.4 Dimensions

The extensions of the board are 79 mm x 62 mm

3 Waveforms

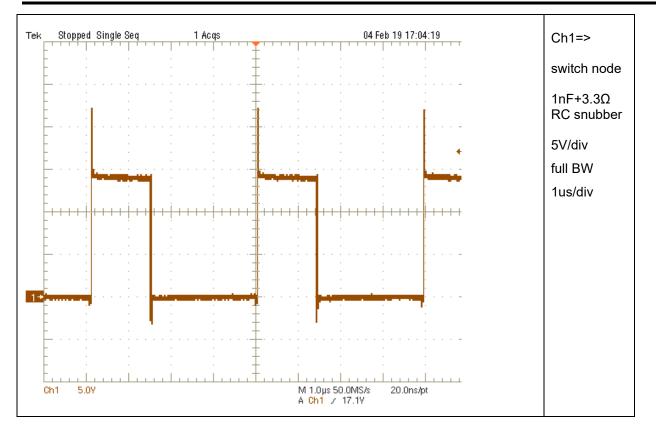

#### 3.1 Switching

#### 3.1.1 Low Side FET

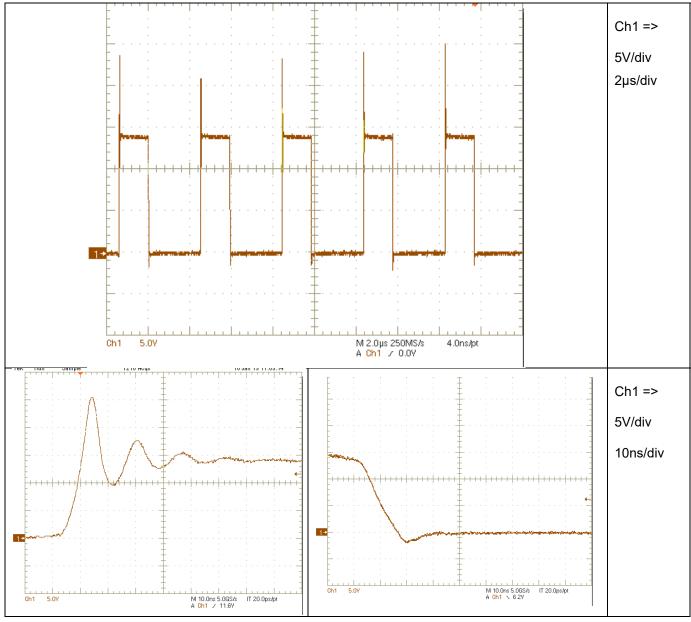

With input voltage set to 14V and 20A lout results in the waveform shown in Figure 3

Figure 3

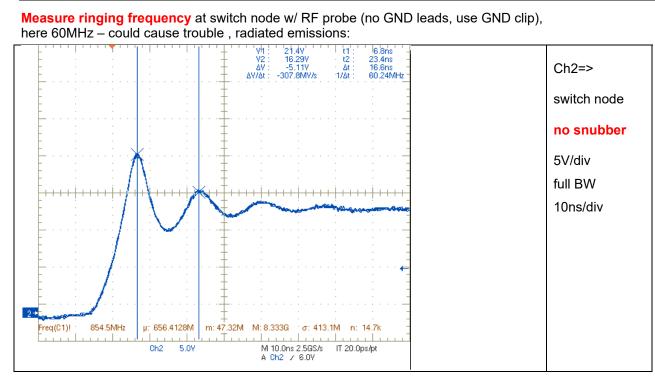

Maximum input voltage is 26V and the overshoot is around 12V. Vds rating of BSC032N04LS is 40V – enough margins. RC snubber circuit was implemented to demonstrate RF suppression:

6

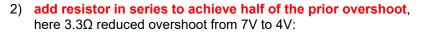

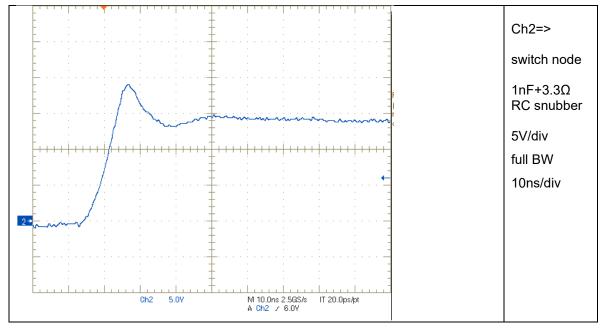

# 1) add capacitor from switch node to GND to achieve half of the prior frequency, here 1nF

Clamping network 1nF / 3.3 Ohm reduces RF content at the switch node, less EMI !

FXAS

www.ti.com

**ISTRUMENTS**

By experience could be said that a drop in efficiency from 0.2% to 0.5% is typically caused by adding the RC snubber circuit. For a medium power design like PMP30600 geometry 1206 or 1210 might fit, but for high power designs be aware of losses up to 500mW:

- 0603 <100mW

- 0805 <150mW

- 1206 <200mW

- 1210 <250mW

- 1812 <500mW

- 2010 <750mW

- 2512 <1W

8

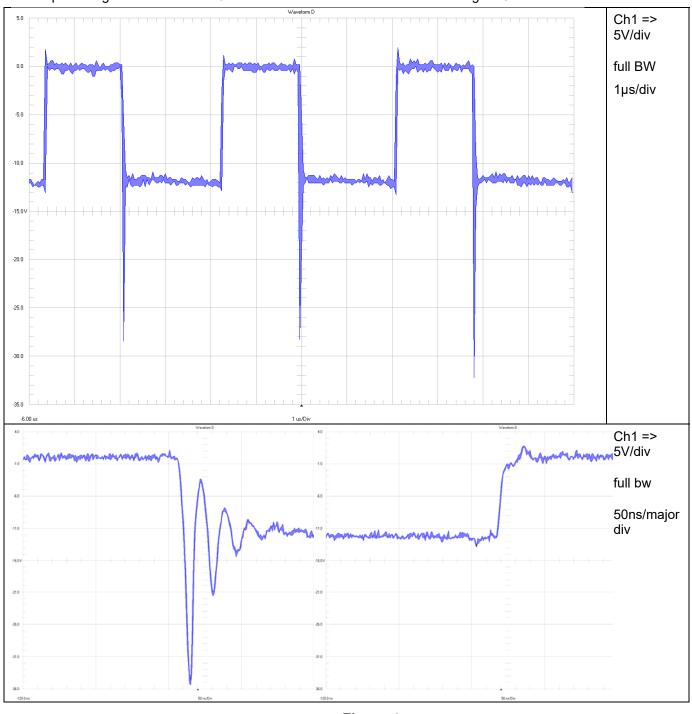

#### 3.1.2 High-Side FET referenced to Vin

With input voltage set to 12V and 20A lout results in the waveform shown in Figure 3

Figure 4

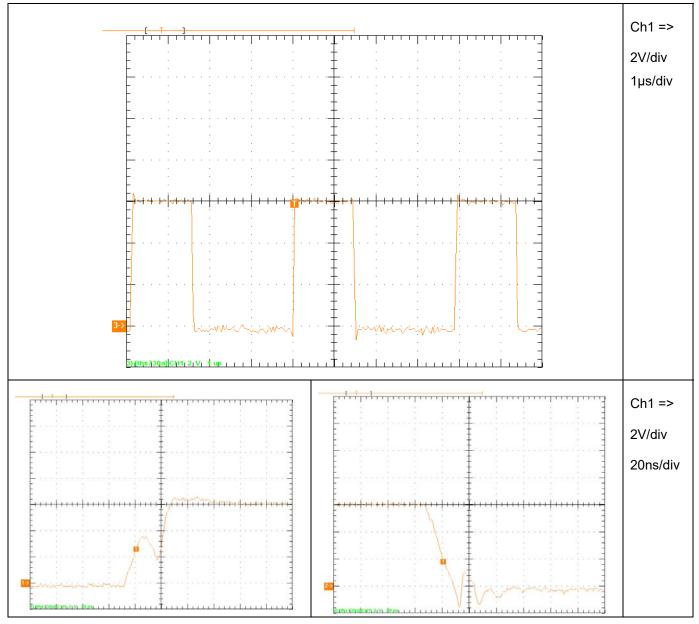

## 3.1.3 Gate-Source of High-Side FET

With input voltage set to 14V and 20A lout results in the waveform shown in Figure 3.

Figure 5 High side

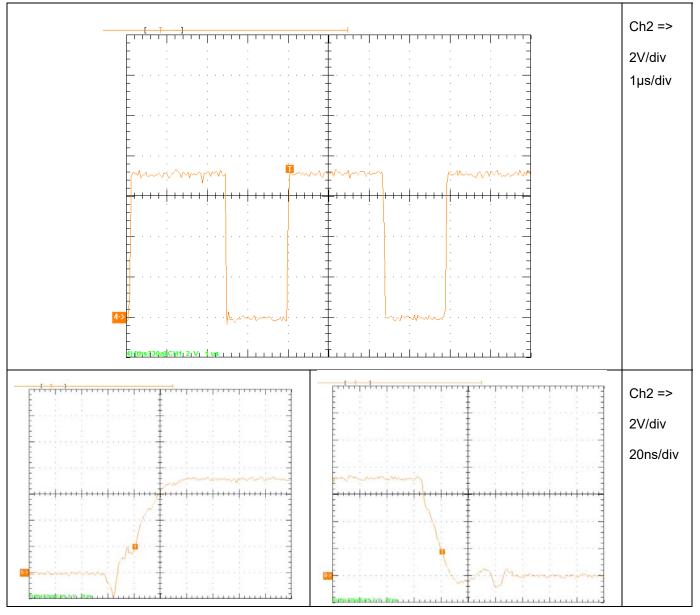

#### 3.1.4 Gate Source of Low-Side FET

Figure 6 Low side

#### 3.2 Output Voltage Ripple

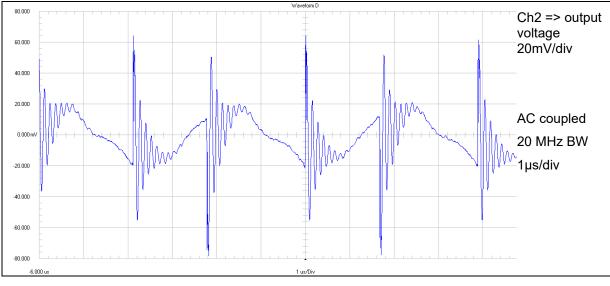

The output ripple voltage is shown in Figure 7. The image was taken with 20A load 12V at the input. The output ripple voltage is less than 50mV except noise.

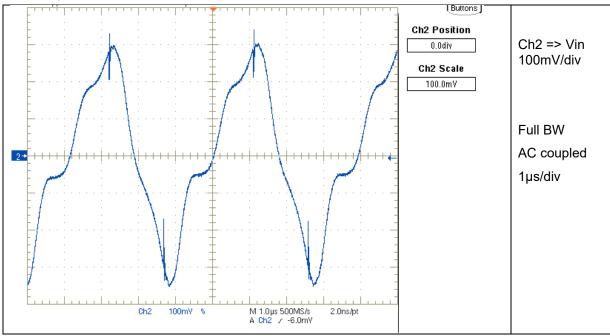

#### 3.3 Input Voltage Ripple

The input ripple voltage is shown in **Error! Reference source not found.**. This was taken with 20A full load 14V at the input.

Input voltage ripple is around 650mV

Reflected ripple = conducted emissions, EMI

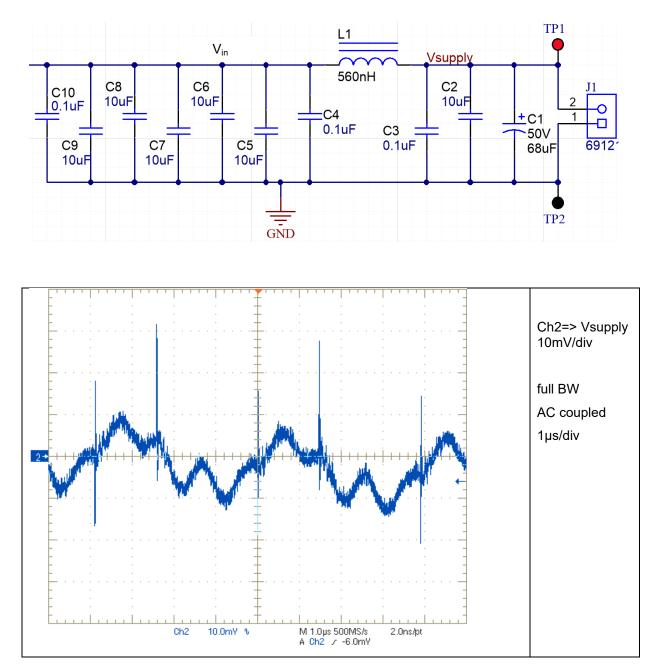

Finally the input voltage by using PI filter 68uF – 0.56uH – 5x 10uF; A small ceramic capacitor 100nF was added to the electrolytic to suppress glitches:

Input voltage is reduced to 20mV; reduction rate is 1/30.

A tremendous reduction of reflected ripple resulted in better EMI behavior !

The inductor prevents the source from seeing the pulse currents – less conducted emissions.

#### 3.4 Bode Plot

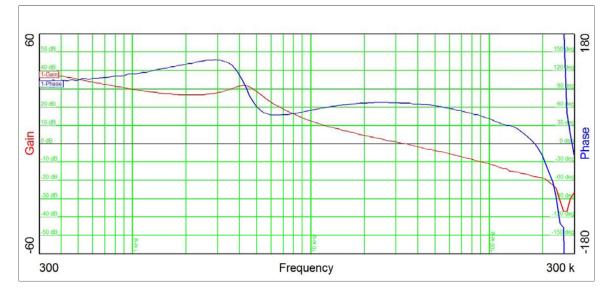

Figures below shows the loop response with 20A load and 14V input - fco=32kHz

The crossover frequency 32kHz fits exactly to the first calculation by hand, the phase margin is more than 60 degrees. Slope at crossover is close to -1.

#### **REMEMBER:**

This analysis is a small signal analysis, shows the small signal behavior of the power supply.

The only true analysis is a large signal analysis, the system response on a load transient!

#### 3.5 Load Transients

#### 4 Load Transients

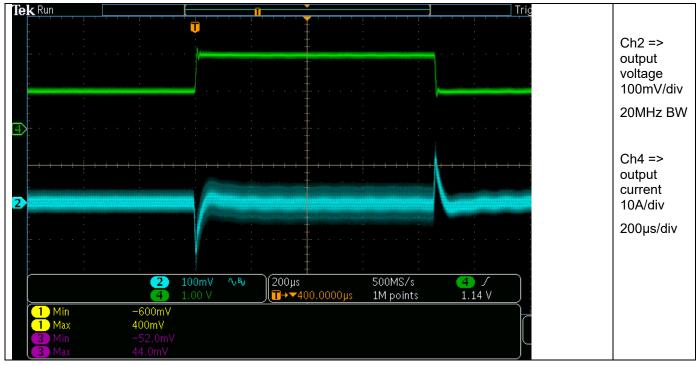

The Figure 9 shows the response to load transients. The load is switching from 10A to 20A. The input voltage was set to 14V

Figure 9

The voltage drop caused by 10A is around 150mV, so around 3% of the output voltage 5V; The combination output capacitor to loop bandwidth matches.

A proper calculation of the error amplifier compensation results in a stable design. For series production a phase margin >60 degrees and a gain margin <-15dB is recommended.

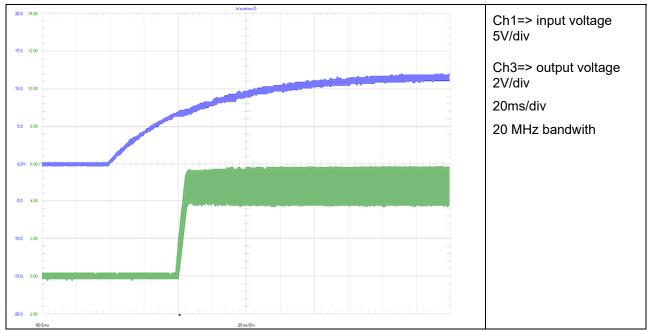

#### 4.1 Start-up Sequence

The startup waveform is shown in the Figure 10. The input voltage was set at 12V, with 20A load at the output. The power supply was enabled

#### 4.2 Shutdown Sequence

16

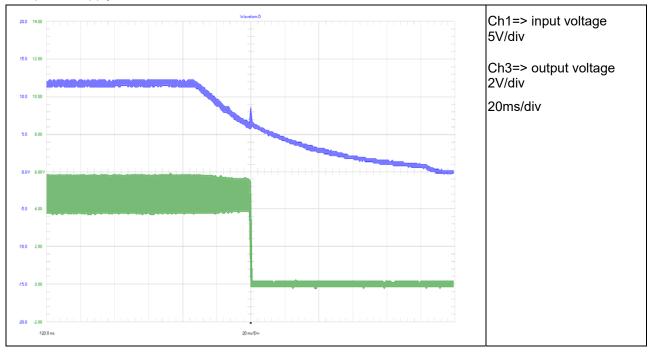

The shutdown waveform is shown in the Figure 11. The input voltage was set at 12V, with 20A load at the output. The power supply was disabled.

Figure 11

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (https://www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated