Design Guide: TIDA-00300

# Isolated Power Architecture Reference Design for Communication and Analog Input/Output Modules

## Description

This reference design includes multiple approaches for generation of isolated power supplies for different protection relay modules. Isolated supply for analog input, binary input, and communication modules is generated using an isolated DC/DC converter with output headroom for connecting to an LDO and configurable output. Additionally, this design showcases LDOs for regulating the supplies, monitoring the DC voltage status using a voltage detector, and input or output overload protection using load switches.

#### Resources

TIDA-00300 UCC12050, TPS782, TPS760, TLV713 SN6505B, SN6501, TPS709, TPS61220 ISOW7841, TPS763, TPS22944, TLV3012 REF3025, LM5017, TPS7A47, TPS7A16 ISO7741, ISO1541, TPS55010, TVS3300 DCH010515D, DCH010505S, REF3425 Design Folder Product Folder Product Folder Product Folder Product Folder Product Folder Product Folder

#### **Features**

- Multiple approaches for generation of isolated power supplies for analog input, binary input, and communication module using transformer driver, power module, or isolated DC/DC

- Use of isolated DC/DC converter simplifies system design, provides flexibility in configuring the output, and improves reliability

- Multiple approaches for generation of isolated power supplies for analog input or output module including split-rail power supplies using a DC/DC converter and LDOs, Fly-Buck™ converters, splitrail DC/DC, and LDOs

- Synchronous SPI interface using digital isolator and I<sup>2</sup>C interface using digital isolators with bidirectional SDA and unidirectional SCL

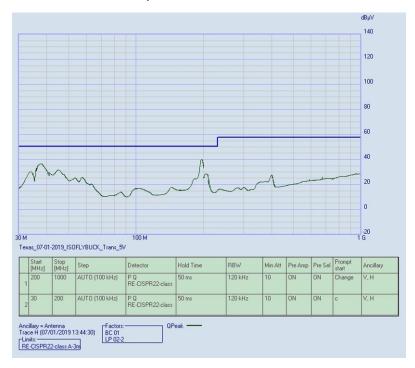

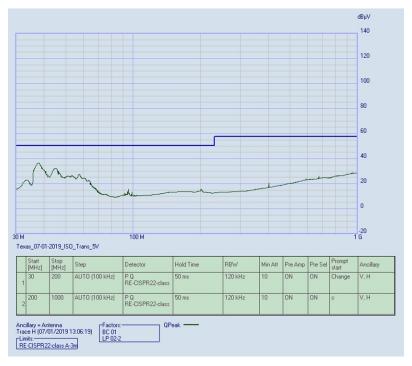

- The boards are tested for the EMI pre-compliance requirement and the EMC pre-compliance by interfacing to the TIDA-00227 design

## **Applications**

- AC analog input module

- · Communication module

- Multifunction relay

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

Resources (Continued) www.ti.com

## 1 Resources (Continued)

TLV742P, TLV704, TPS22960, SN74LVC1G14

Product Folder

TPS62821, DCR010505, LP2985-N, TPS3897

Product Folder

TPS3895, TPS7A39, DCP010505B, TPS7A3001-EP

Product Folder

LM5160, TPS65130, LM27762, REF3025

Product Folder

OPA2376, REF5025, LM4040, TPS22917

Product Folder

### 2 System Description

#### 2.1 Need for Isolation

Industrial electronic equipment commonly uses galvanic isolators to protect systems and users from potentially hazardous voltages. Industrial equipment must operate reliably in the harshest environments, where strong electromagnetic fields, surges, fast transients, and high noise floors are normal. This environment presents challenges for designing reliable isolation circuits that deliver error-free operation over long equipment lifetimes. Over many decades, optocouplers have been the default signal isolation device, but recent breakthroughs in silicon isolation technology have spawned smaller, faster, and more reliable and cost-effective solutions that have already begun supplanting optocouplers in many end applications.

## **Benefits of Digital Isolators**

- Higher integration: smaller size and lower cost per channel on multi-channel versions

- Higher performance: faster, tighter timing, and substantially lower power

- Longer service life: no wear-out mechanisms as in optocouplers

- Higher reliability: operating parameters remain stable over VDD, temperature, and device age

- High CMTI: an isolation signal path that is fully differential and a high receiver selectivity for CMTI greater than 15 kV/μs

- Low EMI

- High electric-field immunity: >20 V/m, as measured by independent laboratories

- Industry-leading ESD tolerance: 3-kV HBM on all devices

- · Lower external bill-of-materials

- Easy to use: single-chip, complete isolation solution

## 2.2 I/Os in Smart Grid

A number of IEDs or protection relays are used in smart grid and protection systems. These IEDs and protection relays have following I/Os:

- RTD inputs

- DC voltage transducers (0 to 10 V)

- DC current transducers (4 to 20 mA)

- Binary inputs and outputs

The number of inputs vary depending on the application. If the application requires more I/Os and protection relay has a limited number of I/Os, external expansion modules are used to increase the number of I/Os.

Isolation In Smart Grid

The previously-described external expansion modules are standalone devices that sense any of the listed inputs and provide the information to the IED and protection relay through RS-485 communication. These expansion devices need the following isolation:

- Communication

- Power supply, as they are operated from an auxiliary DC input

www.ti.com System Description

Isolation for the previously mentioned I/Os

The required number of I/Os also varies with application and vary from 8 to 16. To control each I/O, an individual isolated channel is required. Alternative to isolating individual channel is to use serial communication with expansion options on the non-isolated side. I2C, a 2-wire communication technology, is commonly used for such applications. Many I2C expanders are available as part of the TI expander portfolio for this kind of application.

I2C is a simple, low-bandwidth, short-distance protocol. Most available I2C devices operate at speeds up to 400 Kbps, with some venturing up into the low megahertz range. I2C can easily link multiple devices together because it has a built-in addressing scheme.

#### I2C advantages are:

- Requires only two bus lines (SDA and SCL)

- No strict baud rate requirements, the master generates a bus clock

- · Simple master/slave relationships between all components

- Each device connected to the bus is software-addressable by a unique address

- A true multi-master bus providing arbitration and collision detection

Analog inputs are interfaced with analog-to-digital converters (ADCs), and analog outputs are generated through digital-to-analog converters (DACs). Most of the ADCs and DACs are available with SPI.

SPIs can daisy chain multiple devices. An advantage of daisy chaining is the reduced requirement for number of chip selects. Many SPI-based ADCs and DACs are available as part of TI's portfolio.

In most applications, these modules work on auxiliary supply. The available auxiliary input for smart grid applications is 24 V. For safety reasons, isolate the auxiliary modules. To generate the required supply voltages, a switching regulator is used. When digital isolators are used to isolate SPI and I2C as previously described, an isolated and a non-isolated supply are required to function.

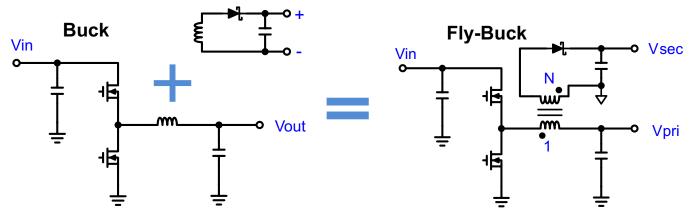

To generate both the isolated and non-isolated supply, a synchronous buck regulator with Fly-Buck topology can be used. The Fly-Buck topology can generated both isolated and non-isolated voltages with good regulation.

The ADC and DAC require different supply voltages to operate. Most common supply voltages used are ±15 V, 5 V, 3.3 V. The output of the Fly-Buck is an unregulated output. LDOs are used to regulate voltages to the required levels.

An isolated buck converter (Fly-Buck) uses a synchronous buck converter with coupled inductor windings to create isolated outputs. Isolated converters utilizing Fly-Buck topology use a smaller transformer for an equivalent power transfer as the transformer primary and secondary turns ratios are better matched. An optocoupler or auxiliary winding is not needed as the secondary output closely tracks the primary output voltage, resulting in a smaller solution size and cost.

System Description www.ti.com

## 2.3 Isolation Types

The signal isolation can be achieved by:

Optical coupling: The transmission of light across a transparent nonconductive barrier, such as an air gap, to achieve isolation. The main benefits of optical coupling (optocoupling) are that light is inherently immune to external electric or magnetic fields, and optical coupling allows for transfer of steady-state information. The disadvantages of optocouplers include speed limitations, power dissipation, and the degradation of the LED. The advantage of inductive coupling is the possible difference in commonmode and differential transfer characteristics

- Inductive coupling: Uses a changing magnetic field between two coils to communicate across an isolation barrier. The most common example is the transformer where the strength of the magnetic field depends on the coil structure (number of turns/unit length) of the primary and secondary windings, the permittivity of the magnetic core, and the current magnitude.

- Capacitive coupling: Uses a changing electric field to transmit information across the isolation barrier.

The material between the capacitor plates is a dielectric insulator and forms the isolation barrier. The

plate size, the distance between the plates, and the dielectric material determine the electrical

properties. The benefits of using a capacitive isolation barrier are efficiency, in both size and energy

transfer, and immunity to magnetic fields.

## 2.4 Digital Isolator

Digital isolators use innovative circuitry to isolate standard digital signals at signaling rates of DC to over 100 Mbps. The TI family of isolators use capacitive coupling. The capacitive coupling solution uses proven and cost-effective manufacturing processes and provides an inherent immunity to magnetic fields.

#### **Device Selection**

System performance requirements have the most impact on the selection of an isolation device. Other considerations include space constraints and cost.

## **Data Rate Requirements**

System data rate requirements are likely to be the single most important parameter for device selection. If a system uses high data rates, such as the high speed PROFIBUS protocol, the minimum data rate speed requirement of 9.6 Mbps narrows the device selection to the high performance products available. Conversely, if the RS-485 network runs at much lower data rate speeds, the possible device selection options widens.

Device costs typically rise in proportion to data rate performance. Therefore, a designer must take care not to specify a device with more performance than is required. However, low performance device selection can make future system performance upgrades more costly and involved, because all devices not compatible with upgraded system data speeds require replacement.

## **Space Requirements**

Space constraints are a second area of concern that can also limit a designer's choices. Maximum dimension requirements are a concern for virtually all applications. However, some implementations can be severely space-limited. Fortunately, there are solutions for these situations.

## **Cost Requirements**

Cost constraints and concerns are a reality in virtually all system design work, and therefore must be considered. Cost considerations can have an effect on the design choices for a system. As noted previously, isolator device cost rises in proportion with data rate performance. Specifying a device with only the system performance required can reduce costs. Other cost issues include a consideration of the number of devices used.

www.ti.com System Description

Additional cost benefits of integrating as many channels into one device include reduction in board space and assembly costs. A lower device count results in smaller boards. Also, lower device count typically results in a less complex board layout. The combination of smaller boards and less complex layout reduces board costs. In addition, circuit board assembly costs typically decrease proportionally as the number of devices required for the board assembly process decreases. Therefore, designing with fewer devices results in lower manufacturing costs.

**Table 1. Comparison of Different Signal Isolation Techniques**

| PARAMETER                                | ОРТО       | MAGNETIC        | CAPACITIVE      |

|------------------------------------------|------------|-----------------|-----------------|

| Sampling rate (Mbps)                     | 50         | 150             | 150             |

| Propagation delay time (ns)              | 20         | 32              | 12              |

| Pulse width distortion (ns)              | 2          | 2               | 1.5             |

| Channel-to-channel skew (ns)             | 16         | 2.0             | 1.6             |

| Part-to-part skew (ns)                   | 20         | 10              | 2               |

| ESD on all pins (kV)                     | ±2         | ±2              | ±4              |

| CM transient immunity (kV/µs)            | 20         | 25              | 25              |

| Temperature (°C)                         | -45 to 125 | -40 to 125      | -55 to 125      |

| MTTF at 125°C, 90% confidence            | 8          | 1746            | 2255            |

| FIT at 125°C, 90% confidence             | 14391      | 65              | 50              |

| Magnetic immunity at 1 kHz (Wb/m²)       | _          | 10 <sup>2</sup> | 10 <sup>8</sup> |

| Radiated electromagnetic field immunity  |            |                 |                 |

| IEC61000-4-3 (80 to 1000 MHz)            | _          | Fails           | Complies        |

| MIL-STD 461E RS-103 (30 to 1000 MHz)     | _          | Fails           | Complies        |

| High-voltage lifetime expectancy (years) | <5         | <10             | >28             |

#### 2.5 Isolation Communication Module

TI has a large portfolio of isolators that gives flexibility to select the isolator based on some of the previously mentioned selection criteria.

This design guide demonstrates using TI devices for the following applications:

- · Isolation of I2C interface

- Isolation of SPI

- Power Supply Isolation

- · LDOs to regulate the supply voltages

TI has a large portfolio of isolation devices for power and signal isolation. TI also has a large portfolio of linear dropout regulators. All the relevant design files like schematics, BOM, layer plots, Altium files, and Gerber files have also been provided to the user (see Section 10).

The following care has to be taken while using this design:

- Power Supply outputs: The power supply outputs are not protected. A suitable SMD fuse can be used based on the application need. This design provides options to mount the SMD fuse.

- Surge protection: This reference design is a sub-system and is expected to be an integral part of expansion module. So, no surge protection is provided.

- A high-voltage isolation test has not been performed. All the devices and PCB design are done considering the required isolation.

System Description www.ti.com

## 2.6 Isolated DC-DC Converter UCC12050 Advantages

Some of the advantages of using an isolated DC/DC converter include:

- Fully integrated high-efficiency isolated DC-DC converter

- Regulated 5.0-V or 3.3-V output with selectable 400-mV headroom voltage to power an LDO

- Extended ambient temperature range: -40°C to +125°C

- · Short circuit tolerant and provides thermal shutdown

- Extended ambient temperature range: -40°C to +125°C

The UCC12050 provides extra features such as an enable pin, synchronization of switching frequency among multiple devices, and selection of isolated output voltages.

www.ti.com Design Features

## 3 Design Features

The primary objective is to create a reference design platform to showcase different approaches to generation of isolated power-supply rails including a split-rail supply required for communication, analog input, and analog output modules from 24-V or 5-V DC input using a DC/DC converter with integrated FET, split-rail DC/DC converter, isolated power module, and transformer driver. The design additionally features generation of a stable reference using low drift references, diagnostics of input voltage, synchronous communication using digital isolators, and input protection using load switches. Table 2 lists the typical requirements:

Table 2. System Specifications for TIDA-00300

| PART NUMBER | NAME                                                                                    | DESCRIPTION                                                                             |

|-------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 1           | SPI interface                                                                           | 4-wire , up to 4Mbps                                                                    |

| 2           | I2C interface                                                                           | Bidirectional data , unidirectional clock , up to 100 Kbps                              |

| 3           | Fly-Buck converter<br>Output voltages                                                   | Isolated: > 18 V, < -18 V, > 7 V<br>Non-isolated > 9 V                                  |

| 4           | Input voltage, connection                                                               | 24-V DC nominal input, screw-type terminal                                              |

| 5           | Regulators (LDOs)                                                                       | Isolated: 15 V, –15 V, 5 V; Non-isolated: 3.3 V                                         |

| 6           | Protection                                                                              | Undervoltage lockout for Fly-Buck converter Supply input reversal                       |

| 7           | Host input connection                                                                   | 8-pin screw type terminal block                                                         |

| 8           | Output connection                                                                       | 8-pin screw type terminal block for signal<br>4-pin screw type terminal block for power |

| 9           | Indication                                                                              | LED indications for 15-V, –15-V, and 5-V isolated power supplies                        |

| 10          | Generation of isolated supplies using DC/DC power module                                | ±15 V , 6 V, 5 V , 3.3 V                                                                |

| 11          | Generation of isolated supplies using transformer driver and LDO                        | ±13 V , ±12 V, 6 V, 5 V, 3.3 V                                                          |

| 12          | Generation of isolated supplies using isolated DC/DC with configurable outputs          | 5.4 V, 5 V , 3.7 V, 3.3 V                                                               |

| 13          | Generation of isolated supplies using digital isolator with integrated power            | 5.4 V, 5 V , 3.3 V                                                                      |

| 14          | Generation of split-rail supplies using isolated DC/DC converter with integrated FETS   | ±15 V, 5 V                                                                              |

| 15          | Generation of isolated split rail using wide input synchronous buck, Fly-Buck converter | ±18 V, ±15 V, 5 V                                                                       |

| 16          | Generation of stable reference output using series or shunt reference                   | 2.5 V                                                                                   |

|             | +                                                                                       | +                                                                                       |

## 4 TI Device Mapping to Reference Design Functionalities

This section provides details of device mapping to functionalities for the following boards:

- Isolated power supply for communication module

- Isolated power supply for analog IO module

- Isolated synchronous communication with split-rail power supplies

## 4.1 Isolated Power Supply for Communication Module

Table 3 provides details of the TI devices and functionalities implemented in this reference design for generating isolated power supplies for the communication module.

Table 3. Details of Functions and Devices Used for Implementing Power Supplies for Communication Module

| FUNCTION                                                                           | DEVICES                                                                                                               | DESCRIPTION                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Isolated 5-V and 3.3-V supply generation using power module                        | DCR010505P, DCP010505BP,<br>LP2985AIM5-3.3, TPS78233                                                                  | Generation of isolated, regulated and unregulated DC supply using isolated DC/DC converter modules and LDOs                                                                                                                       |

| Isolated 5-V, 3.3-V, and ±12-V supply generation using transformer driver          | SN6505B, SN6501, TPS70933,<br>TPS76050, TPS7A3901                                                                     | Generation of isolated supply including split-rail power supply for analog input module using transformer driver and LDOs                                                                                                         |

| Isolated 5.4-V, 5-V, and 3.3-V supply using digital isolator with integrated power | ISOW7841, TPS22944, TPS61220,<br>TPS76350, TPS62821                                                                   | Generation of isolated using digital isolator with integrated power, DC/DC converter to boost the output and LDOs to regulate the output                                                                                          |

| Generation of regulated DC supplies with diagnostics                               | UCC12050, SN74LVC1G14,<br>SN74LVC1G14, CSD17571Q2,<br>TPS22960, TLV74233, TLV70450,<br>TLV71333, TPS3897, SN74LVC1G17 | Generation of isolated power supplies with configurable output<br>and regulating the output using LDOs including 5-V and 3.3-V<br>output with input overload protection, voltage level detection and<br>voltage status indication |

## 4.2 Wide Input Isolated Power Supply for Analog IO Modules

Table 4 provides details of the TI devices and functionalities implemented in this reference design for generating isolated power supplies for analog IO modules.

Table 4. Details of Functions and Devices Used for Implementing Power Supply for Analog IO Modules

| FUNCTION                                                                             | DEVICES                                                                                         | DESCRIPTION                                                                                                              |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Generation of isolated 5 V and ±15 V using DC/DC, split-rail DC/DC, and power module | TVS3300, LM5160, TVS0500,<br>TPS22917, SN6505B, TPS2400,<br>DCH010515D, DCH010505S,<br>TPS65130 | Generation of split-rail power supply for analog input and analog output from 24-V or 5-V DC input with input protection |

| Generation of regulated 3.3 V, ±5 V and ±12 V using LDOs                             | LM27762, TPS7A3901, TLV70433,<br>TVS1400                                                        | Generation of regulated split-rail supplies from unregulated split-rail supplies                                         |

| Generation of stable reference                                                       | REF5025, REF3025A, REF3425,<br>OPA2376, LM4040AIM3-2.5                                          | Generation of stable reference using series or shunt reference                                                           |

## 4.3 Isolated Synchronous Communication With Split-Rail Power Supplies

Table 5 provides details of the TI devices and functionalities implemented in this reference design for generating isolated power supplies for analog IO module and isolated synchronous communication.

Table 5. Details of Functions and Devices Used for Implementing Power Supply and Synchronous Communication

| FUNCTION                                                | DEVICES                                                          | DESCRIPTION                                                                                                               |

|---------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Generation of 5 V and ±15 V from 24-V input using DC/DC | TVS3300, LM5017, TPS70933,<br>TPS7A4700, TPS7A3001,<br>TPS7A1650 | Generation of split-rail power supply output from 12- or 24-V input using isolated DC/DC converter with integrated switch |

| Generation of 5 V and ±15 V from 5-V input using DC/DC  | TPS55010, TVS0500, LP2985-                                       | Generation of split-rail power supply output from a 5-V input using isolated DC/DC converter with integrated switch       |

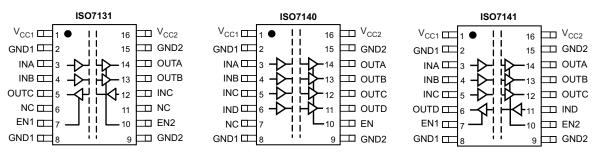

| Isolated SPI interface                                  | ISO7741, ISO7141                                                 | Digital isolator with basic or reinforced isolation to implement SPI with varying speed                                   |

| Isolated I2C interface                                  | ISO1541D                                                         | Digital isolators to implement I2C interface with varying speed                                                           |

## 5 System Overview

Some of the key requirements for designing the isolated power architecture for protection relay modules include:

- 1. Generation of isolated 5 V or 3.3 V with output headroom allowing usage of LDOs for applications in an analog input module or communication module

- Generation of the required supply rails (5 V to ±14 V, ±14 V to ±12 V, 5 V to ±5 V for analog IO and 5 V and 3.3 V for communication) with high efficiency and scalable load current using 5-V, 12-V, or 24-V input

- 3. Operation of the supply over wide range for applications using external auxiliary supply

- 4. Generation of isolated power supplies with high efficiency

- 5. Generation of stable reference (Series or Shunt) with buffer and low temperature drift

- 6. Isolation of SPI signals with varying speed and low current consumption

- 7. Isolation of I2C interface signals with varying speed

- 8. Generation of isolated power supplies with low EMI for ease of design

- 9. Diagnostics including LEDs and voltage detection

The TIDA-00300 reference design provides solutions to the previous requirements and also solves some of the design challenges associated with the design of isolated power architecture for protection relay modules.

System Overview www.ti.com

## 5.1 Block Diagram

Block diagram for the boards used for generating power supplies used for isolated communication and isolated IO modules are discussed in this section.

## 5.1.1 Isolated Power Supply for Communication Module

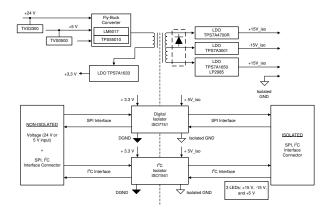

Figure 1 shows multiple approaches to generation of isolated power supply for low-speed wired communication modules.

Figure 1. Isolated Power Supply Architecture for Communication Modules

www.ti.com System Overview

## 5.1.1.1 Generation of Isolated 5-V, 5.4-V, 3.3-V, or 3.7-V Supply Using Isolated DC/DC With Protection and Diagnostics

This design has the following functionality:

- Configuration of output voltage using output select pin and resistors

- Generation of regulated 5-V and 3.3-V supplies

- · Protection of 5-V input using a load switch

- · Voltage detector to indicate the isolated supply status

## 5.1.1.2 Isolated 5-V and 3.3-V Supply Generation Using Power Module

This design has the following functionality:

- Generation of 5-V DC power supply from 5-V input using an unregulated power module

- Generation of 5-V DC power supply from 5-V input using a regulated power module

- Generation of regulated 3.3-V output using LDO

## 5.1.1.3 Isolated 5-V, 3.3-V and ±12-V Supply Generation Using Transformer Driver

This design has the following functionality:

- Generation of isolated 3.3 V or 5 V from 5-V input using a transformer driver

- Generation of split-rail ±12-V supply from 5-V input using a transformer driver

## 5.1.1.4 Isolated 5.4-V, 5-V and 3.3-V Supply Using Digital Isolator With Integrated Power

This design has the following functionality:

- Generation of isolated 5 V from 5-V input using digital isolators with integrated power

- Generation of isolated 5.4 V, regulated 5 V, 3.3 V from 5 V

## 5.1.2 Wide Input Isolated Power Supply for Analog IO Modules

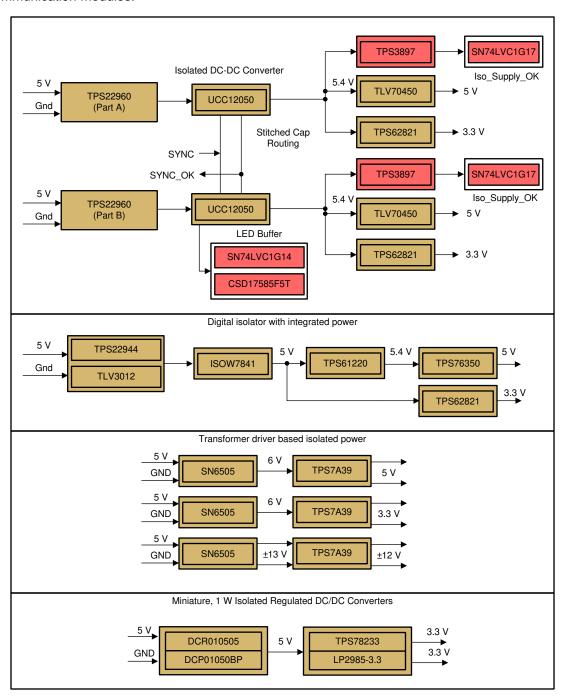

Figure 2 shows multiple approaches to generation of isolated power supply for analog input/output modules.

Figure 2. Wide Input Isolated Power Supply Architecture for Analog IO Modules

System Overview www.ti.com

#### 5.1.2.1 Generation of Isolated 5 V and ±15 V With Protection

This design has the following functionality:

- Generation of isolated split-rail supplies using DC/DC converter with integrated switch from 24-V input

- · Generation of isolated split-rail supplies using isolated power module from 5-V input

- · Input protection against overload using a load switch

- Input protection against transients using a flat clamp TVS

### 5.1.2.2 Generation of Regulated 3.3-V, ±5-V and ±12-V Supplies Using LDOs

This design has the following functionality:

- Generation of regulated split-rail supply using a dual LDO

- Generation of 5 V and 3.3 V using LDOs

#### 5.1.2.3 Generation of Stable Reference

This design has the following functionality:

- · Generation of stable reference using shunt reference with buffer

- · Generation of stable reference using series reference with buffer

## 5.1.3 Isolated Synchronous Communication With Split-Rail Fly-Buck™ Power

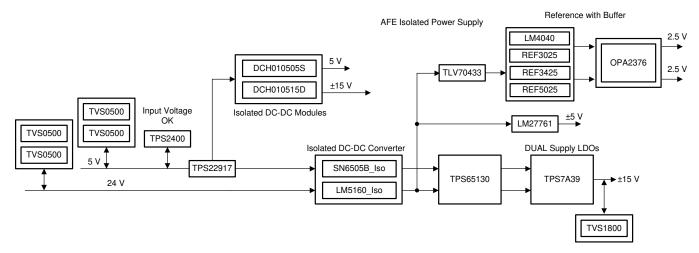

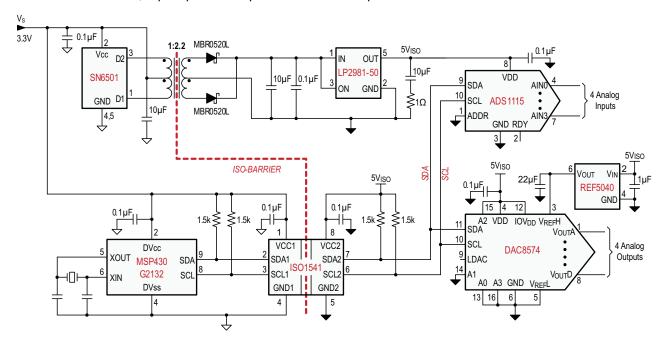

Figure 3 shows multiple approaches to the generation of isolated power supply for synchronous communication and analog IO modules with protection.

Figure 3. Isolated Synchronous Communication With Split-Rail Fly-Buck™ Power

www.ti.com System Overview

#### 5.1.3.1 Generation of 5 V and ±15 V from 24 V

This design showcases the following:

- · Generation of split-rail supply from 24-V input using a DC/DC converter

- · Generation of regulated split-rail supply using LDOs

- Input transient protection using a flat clamp TVS

## 5.1.3.2 Generation of 5 V and ±15 V from 5-V input

This design has the following functionality:

- Generation of split-rail supply from 5-V input using a DC/DC converter

- Generation of 5 V using LDO

- Input transient protection using flat clamp

## 5.1.3.3 Isolated Synchronous Interface

This design has the following functionality:

- · SPI using digital isolator

- · I2C interface using digital isolators

## 5.2 Highlighted Products

This section provides details of some of the focus TI products used in this reference design for generation of required power supplies for protection relay modules.

## 5.2.1 Isolated Power Supply for Communication Module

This section provides details of the devices used to generate the required isolated power supplies for the communication module:

## 5.2.1.1 Generation of Isolated 5-V, 5.4-V, 3.3-V, or 3.7-V Supply Using Isolated DC/DC With Protection and Diagnostics

This design has the following functionality:

- UCC12050, 500-mW, high-efficiency, 5-kVRMS isolated DC-DC converter

- TPS22960, 5.5-V, 0.5-A, 435-mΩ, 2-channel load switch with quick output discharge

- TLV74233, 200-mA small-size low-dropout (LDO) linear voltage regulator

- TLV70450, 24-V input voltage, 150-mA, ultra-low I<sub>O</sub> low-dropout (LDO) regulators

- TLV713, 150-mA low-dropout (LDO) regulator with fold-back current limit for portable devices

- TPS3897, single-channel ultra-small adjustable supervisory circuit with active-high, open-drain output

- SN74LVC1G14, single Schmitt-trigger inverter

- SN74LVC1G17, single Schmitt-trigger buffer

- CSD17571Q2, 30-V N-channel NexFET™ power MOSFETs

#### 5.2.1.2 Isolated 5-V and 3.3-V Supply Generation Using Power Module

This design has the following functionality:

- DCR010505P, miniature, 1-W isolated unregulated DC/DC converters

- DCP010505BP, miniature, 1-W isolated unregulated DC/DC converters in a PDIP package

- LP2985AIM5-3.3, 150-mA low-noise low-dropout regulator with shutdown

- TPS78233, 3.3-V, 150-mA, ultra-low quiescent current (500 nA) low-dropout linear regulator

System Overview www.ti.com

## 5.2.1.3 Isolated 5-V, 3.3-V and ±12-V Supply Generation Using Transformer Driver

This design has the following functionality:

- SN6505B, low-noise 1-A, 420-kHz transformer driver for isolated power supplies

- SN6501, low-noise, 350-mA, 410-kHz transformer driver for isolated power supplies

- $\bullet~$  TPS70933, 3.3-V, 150-mA 30-V ultra-low  $I_{\rm Q}$  wide-input low-dropout (LDO) regulator with reverse current protection

- TPS76050, 5-V output, 16-V, 50-mA, low I<sub>Q</sub>, low-dropout linear regulator

- TPS7A3901, dual, 150-mA, wide-V<sub>IN</sub>, positive and negative low-dropout (LDO) voltage regulator

www.ti.com System Overview

## 5.2.1.4 Isolated 5.4-V, 5-V, and 3.3-V Supply Using Digital Isolator With Integrated Power

This design has the following functionality:

- TPS22944, 5.5-V, 0.2-A, 500-mΩ, 100-mA current-limit load switch

- ISOW7841, high-efficiency, low-emissions, reinforced digital isolator with integrated power

- TPS61220, low input voltage, 0.7-V boost converter with 5.5-μA quiescent current

- TPS76350, low I<sub>o</sub>, 150-mA, low-dropout linear regulators

- TPS62821, 1-A step-down converter with 1% accuracy

## 5.2.2 Wide Input Isolated Power Supply for Analog IO Modules

This section provides details of the devices and configurations used to generate the required isolated power supplies for an analog IO module.

#### 5.2.2.1 Generation of Isolated 5-V and ±15-V With Protection

This design has the following functionality:

- LM5160, wide input 65-V, 2-A synchronous buck or Fly-Buck converter

- TPS22917, ultra-low leakage, 5.5-V, 2-A, 80-mΩ on-resistance load switch

- SN6505B, low-noise 1-A, 420-kHz transformer driver for isolated power supplies

- TPS2400, 5.5-V overvoltage protection controller with 100-V input transient protection

- DCH010515D, miniature, 1-W, 3-kV DC isolated DC/DC converters with dual output

- DCH010505S, miniature, 1-W, 3-kV DC isolated DC/DC converters

- TPS65130, split-rail converter with dual, positive and negative outputs (300 mA typ)

- TPS65130, split-rail converter with dual, positive and negative outputs (300 mA typ)

- TVS0500, 5-V flat-clamp surge protection device

## 5.2.2.2 Generation of Regulated 3.3-V, ±5-V and ±12-V Supplies Using LDOs

This design has the following functionality:

- TPS7A3901, dual, 150-mA, wide-V<sub>in</sub>, positive and negative low-dropout (LDO) voltage regulator

- LM27762, low-noise positive- and negative-output charge pump with integrated LDO

- TLV70433, 24-V input voltage, 150-mA, ultra-low Io low-dropout (LDO) regulators

- TVS1400, 14-V flat-clamp surge protection device

System Overview www.ti.com

#### 5.2.2.3 Generation of Stable Reference

This design has the following functionality:

- REF5025, 3-μVpp/V, noise, 3 ppm/°C drift precision series voltage reference

- REF3025, 2.5-V, 50-ppm/°C, 50-µA in SOT23-3 series (Bandgap) voltage reference

- REF3425, 2.5-V, low-drift low-power small-footprint series voltage reference

- LM4040AIM3-2.5, precision micropower shunt voltage reference

- OPA2376, precision, low noise, low quiescent current operational amplifier

## 5.2.3 Isolated Synchronous Communication With Split-Rail Fly-Buck™ Power

This section provides details of the devices used to generate the required isolated power supplies for analog IO module and digital isolators used for isolated synchronous communication.

#### 5.2.3.1 Generation of 5 V and ±15 V from 24-V input

This design has the following functionality:

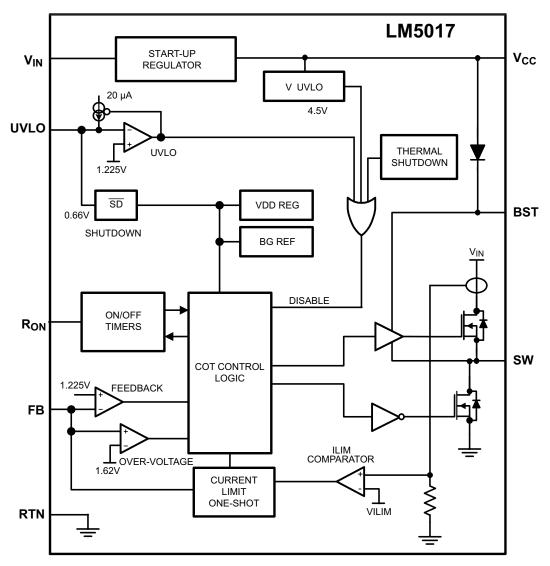

- LM5017, 7.5 V-100 V wide V<sub>IN</sub>, 600-mA constant on-time synchronous buck

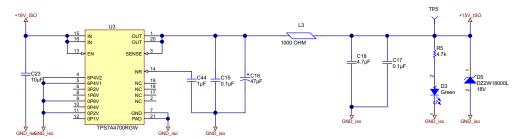

- TPS7A4700, 36-V, 1-A, 4.17-μV<sub>RMS</sub>, RF low-dropout (LDO) voltage regulator

- TPS7A3001, V<sub>IN</sub>, -3 V to -36 V, -200 mA, ultra-low noise, high-PSRR, low-dropout (LDO) linear regulator

- TPS7A1650, 60-V, 5-µA I<sub>O</sub>, 100-mA, low-dropout (LDO) voltage regulator with enable and power good

- TPS70933, 150-mA 30-V ultra-low I<sub>Q</sub> wide-input low-dropout (LDO) regulator with reverse current protection

- TVS3300, 33-V flat-clamp surge protection device

#### 5.2.3.2 Generation of 5 V and ±15 V from 5-V input

This design showcases the following functionality:

- TPS55010, 2.95-V to 6-V input, 2-W, isolated DC/DC converter with integrated FETS

- LP2985-50, 150-mA low-noise low-dropout regulator with shutdown

- TVS0500, 5-V flat-clamp surge protection device

## 5.2.3.3 Isolated Synchronous Interface

This design has the following functionality:

- ISO7741, high-speed, low-power, robust EMC quad-channel digital isolator

- ISO7141, 4242-V<sub>PK</sub> small-footprint and low-power 3/1 quad-channel digital isolator with noise filter

- ISO1541D, 2.5-kV<sub>RMS</sub> isolated unidirectional clock, bidirectional I2C isolators

## 5.2.4 System Design

The design is split into multiple boards as described in this section:

- 1. Isolated power supply for communication module

- 2. Wide input isolated power supply for analog IO modules

- 3. Isolated synchronous communication with split-rail Fly-Buck power

## 5.2.4.1 Isolated Power Supply for Communication Module

This section provides details of the devices used to generate the required power supplies for isolated communication module.

www.ti.com System Overview

## 5.2.4.1.1 Isolated 5-V and 3.3-V Supply Generation Using Power Module

This design features the following functionality and is configured as detailed in the following section:

- DCR010505P, 5-V output configuration loaded for 100 mA and connected to LDO

- DCP010505BP, 5-V output configuration loaded for 100 mA in PDIP package and connected to LDO

- LP2985AIM5-3.3, generation of fixed and regulated 3.3-V output loaded to 50 mA

## 5.2.4.1.2 Isolated 5-V, 3.3-V, and ±12-V Supply Generation Using Transformer Driver

This design features the following functionality and is configured as detailed in the following section:

- SN6505B, 6-V output loaded to 200 mA and connected to LDO

- SN6501, 6-V output loaded to 100 mA and connected to LDO

- TPS70933, generation of fixed and regulated 3.3-V output loaded to 50 mA

- TPS70950, generation of fixed and regulated 5-V output loaded to 50 mA

- TPS7A3901, configured to generate regulated dual ±12-V output loaded to 100 mA for each output

### 5.2.4.1.3 Isolated 5.4-V, 5-V, and 3.3-V Supply Using Digital Isolator With Integrated Power

This design showcases the following functionality and is configured as detailed in the following section:

- TPS22944, for overload protection of 5-V input to ISOW7841

- ISOW7841, configured for 5-V output loaded to 100 mA

- TPS76350, generation of fixed and regulated 5-V output loaded to 50 mA

- TPS62821, 5-V to 3.3-V conversion output loaded to 100 mA

## 5.2.4.1.4 Generation of Regulated DC Supplies With Protection and Diagnostics

This design showcases the following functionality and is configured as detailed in the following section:

- UCC12050, can be configured (using resistor) to generate 5.4-V, 5-V, 3.7-V or 3.3-V

- TPS22960, for overload protection of input voltage

- TLV74233, generation of fixed and regulated 3.3-V output loaded to 50 mA

- TLV70450, generation of fixed and regulated 5-V output loaded to 50 mA

- TPS3897, for monitoring of 5.4-V output voltage

- SN74LVC1G14, single Schmitt-trigger inverter for status indication

- SN74LVC1G17, single Schmitt-trigger buffer for status indication

- CSD17571Q2, 30-V N-channel NexFET power MOSFETs for driving the LEDs

The UCC12050 is a high isolation voltage DC/DC converter designed to provide efficient isolated power to isolated circuits that require well-regulated supply voltages. The UCC12050 integrates a transformer and DC/DC controller with a proprietary architecture to achieve high efficiency with very low emissions. The UCC12050 provides 500 mW (typical) of isolated output power at high efficiency. Requiring a minimum of external components and including on-chip device protection, the UCC12050 provides extra features such as an enable pin, synchronization of switching frequency among multiple devices, and selection of isolated output voltages.

#### 5.2.4.2 Wide Input Isolated Power Supply for Analog IO Modules

This section provides details of the devices used and configurations to generate required isolated power supplies for analog IO module.

#### 5.2.4.2.1 Generation of Isolated 5 V and ±15 V With Protection

This design showcases the following functionality and is configured as detailed in the following section:

- LM5160, configured for generating of isolated 5-V output loaded to 250 mA

- TPS22917, overload protection of 5-V input to SN6505B

System Overview www.ti.com

- SN6505B, configured for generation of isolated 5-V output from 5-V input

- TPS2400, used for diagnostics to indicate 5-V input voltage status

- DCH010515D, generation of isolated split-rail supply ±15 V loaded to 25 mA

- DCH010505S, generation of isolated split-rail supply 5 V loaded to 100 mA

- TPS65130, generation of isolated split-rail supply ±15 V loaded to 100 mA

- TVS3300, protection of LM5160 with 24-V input against

- TVS0500, protection of TPS22917 with 5-V input against transients

## 5.2.4.2.2 Generation of Regulated 3.3-V, ±5-V, and ±12-V Supplies Using LDOs

This design showcases the following functionality and is configured as detailed in the following section:

- TPS7A3901, generation of regulated split-rail supply ±12 V loaded to 100 mA

- LM27762, generation of regulated split-rail supply ±5 V loaded to 100 mA

- TLV70433, generation of fixed and regulated 3.3 V for generation of reference

- TVS1400, protection of split-rail supply voltage against transients

#### 5.2.4.2.3 Generation of Stable Reference

This design showcases the following functionality and is configured as detailed in the following section:

- REF5025, generation of 2.5-V reference from 3.3-V input

- REF3025, generation of 2.5-V reference from 3.3-V input

- REF3425, generation of 2.5-V reference from 3.3-V input

- LM4040AIM3-2.5, generation of 2.5-V reference from 3.3-V input

- OPA2376, for buffering the reference output

#### 5.2.4.3 Isolated Synchronous Communication With Split-Rail Fly-Buck™ Power

This section provides details of the devices used and configuration to generate the required isolated power supplies for analog IO module and digital isolators used for synchronous communication.

## 5.2.4.3.1 Generation of 5 V and ±15 V From 24-V input

This design showcases the following functionality and is configured as detailed in the following section:

- LM5017, generation of isolated split-rail ±17-V power supply

- TPS7A4700, generation of regulated 15 V loaded to 100 mA

- TPS7A3001, generation of regulated –15 V loaded to 100 mA

- TPS7A1650, generation of regulated 5 V loaded to 100 mA

- TPS70933, generation of fixed and regulated 3.3 V loaded to 50 mA

- TVS3300, protection of LM5017 DC/DC with 24-V input against transients

## 5.2.4.3.2 Generation of 5 V and ±15 V From 5-V input

This design showcases the following functionality and is configured as detailed in the following section:

- TPS55010, generation of isolated split-rail ±15-V power supply

- LP2985-50, generation of fixed and regulated 5 V loaded to 50 mA

- TVS0500, protection of TPS55010 DC/DC with 5-V input against transients

#### 5.2.4.3.3 Isolated Synchronous Interface

This design showcases the following functionality and is configured as detailed in the following section:

- ISO7741, implementing SPI from host

- ISO7141, implementing SPI from host

www.ti.com System Overview

• ISO1541D, implementing I2C interface from host

#### 5.2.4.4 Enhancements

There are multiple approaches to the generation of isolated split-rail power supplies based on load current and EMI performance for analog IO modules. These are summarized in Table 6.

Table 6. Isolated Split-Rail Supply Generation

| OPTIONS | ANALOG SUPPLY<br>RANGE | SWITCHER, DC/DC               | LDO                     | COMMENTS                                  |

|---------|------------------------|-------------------------------|-------------------------|-------------------------------------------|

| 1       | ±5 V (100 mA)          | NA                            | LM27762                 | No additional inductor or diodes required |

| 2       | ±5 V (50 mA)           | TPS60403                      | LP2951, LM337           | No additional inductor or diodes required |

| 3       | ±5 V (25 mA)           | TPS61040                      | LP2951, LM337           | Need inductor, diodes                     |

| 4       | ±10 V (25 mA)          | TPS61040                      | LP2951, LM337           | Need inductor, diodes                     |

| 5       | ±10 V (50–100 mA)      | SN6505 or SN6501              | TPS7A3901               | Need transformer, diodes                  |

| 6       | ±10 V (50–100 mA)      | SN6505 or SN6501              | TPS7A4901,<br>TPS7A3001 | Need transformer, diodes                  |

| 7       | ±10 V (20 ma)          | Power module (isolated DC/DC) | TPS7A4901,<br>TPS7A3001 | No additional inductor or diodes required |

| 8       | ±10 V (150 mA)         | TPS65131                      | TPS7A3901               | Need inductor, diodes                     |

| 9       | ±10 V (150 mA)         | TPS65131                      | TPS7A4901,<br>TPS7A3001 | Need inductor, diodes                     |

| 10      | ±10 V (150 mA)         | LM5017                        | TPS7A4901,<br>TPS7A3001 | Need transformer, diodes                  |

| 11      | ±10 V (60 mA)          | LM5002                        | NA                      | Need transformer, inductors, diodes       |

| 12      | ±15 V (100 mA)         | TPS55010                      | NA                      | Need transformer, diodes                  |

## 5.2.5 Design Guidelines

This section provides generic guidelines for designing the isolated power supply modules.

- Refer to the product data sheet for layout guidelines for the devices used in this reference design.

- Refer to the product data sheet and the EVMs for configuring the required outputs.

- The selection of the transformer plays an important role in providing the required isolation and output current.

## 6 Design Details for Isolated Synchronous Communication With Split-Rail Fly-Buck™ Power-Supply Board

This section provides implementation details for Isolated synchronous communication with split-rail Fly-Buck power supply board.

## 6.1 Power Supply

## 6.1.1 DC/DC Converter for Generation of Output Voltages

In industrial systems, signals are transmitted from a variety of sensors to a central controller for processing and analysis. To maintain safe voltages at the user interface, and to prevent transients from being transmitted from the sources, galvanic isolation is required. Isolation also avoids ground loop. The LM5017 is a synchronous buck regulator with integrated MOSFET.

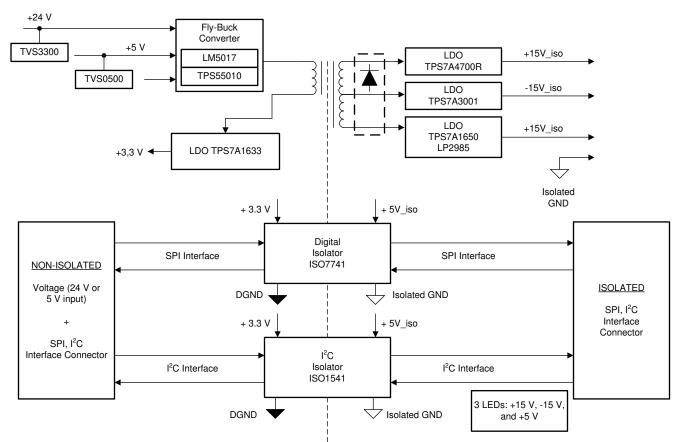

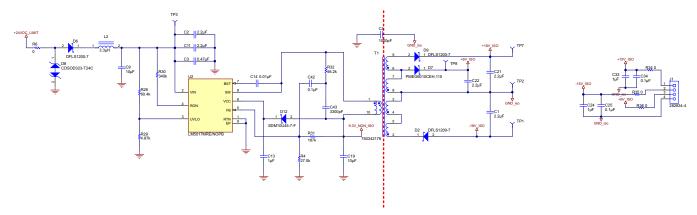

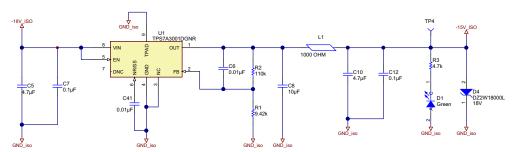

This design uses the LM5017 configured in Fly-Buck mode for converting the 24-V DC input to the required output voltage. The Fly-Buck converter generates the following voltages:

- Isolated voltages: 18 V, –18 V, and 7 V

- · Non-isolated voltages: 9 V (ratio of input voltage)

NOTE: The output voltages are unregulated outputs and may vary with the input voltage.

## 6.1.2 Isolated Output Voltage Regulator

Isolated voltages are used for

- · I2C and SPI isolators

- Interfaced to the connectors for powering external devices like ADC, DAC, and I2C expanders

The unregulated isolated voltage outputs of the Fly-Buck converter are regulated using the LDO. The following regulators are used in this design:

- 15 V → LDO TPS7A4700

- -15 V → Linear Regulator TPS7A3001

- 5 V → Linear Regulator TPS7A1650

#### 6.1.3 Non-isolated Output Voltage Regulator

Non-isolated voltages are used for I2C and SPI isolators. This supply can be used to power low-power microcontrollers based on the application.

The following non-isolated supply is generated in design:

3.3 V at 25 mA → Linear Regulator TPS70933

The isolated voltages are protected against overvoltage with Zener diodes . These Zener diodes provide additional protection for ESD .

## 6.2 Signal Isolation

## **CAUTION**

Although these devices provide galvanic isolation of up to 5000  $V_{\text{RMS}}$ , this reference design is not recommended for isolation voltage testing. The reference design is designed for the evaluation of device operating parameters only and may be damaged if a voltage exceeding 32-V DC is applied anywhere in the circuit.

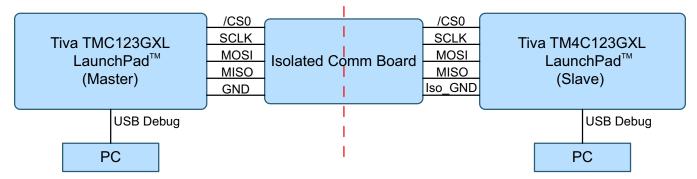

## 6.2.1 Serial Peripheral Interface (SPI)

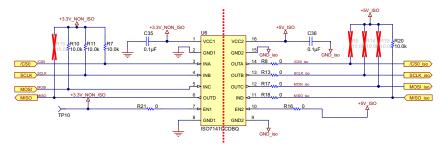

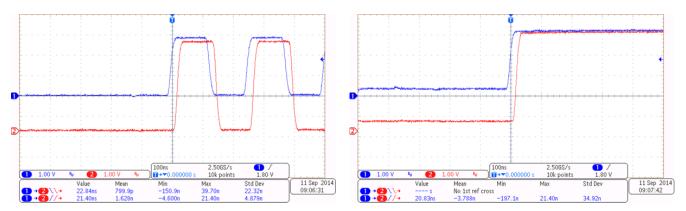

ISO7141CC (or ISO7741), a low-power 3/1 quad-channel digital isolator with noise filter, is used to isolate SPI signals. This design is tested up to 4Mbps.

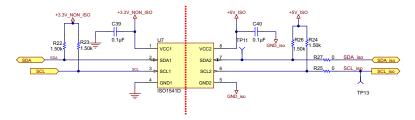

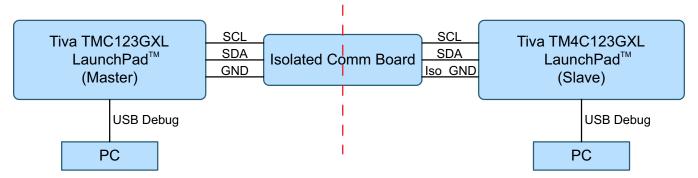

#### 6.2.2 I2C Interface

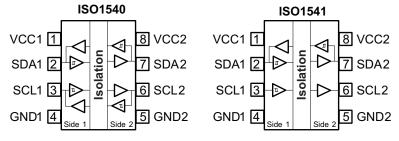

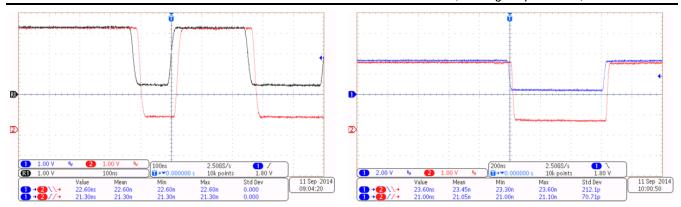

ISO1541, a low-power, bidirectional I2C isolator, is used to isolate I2C signals.

The I2C is open-drain topology, requiring two lines, serial data (SDA), and serial clock (SCL), to be connected to VDD by pullup resistors. To have logic Zero online, pull the line to ground (an operating MOSFET). To have logic One, let the line float (a not-operating MOSFET) to make it High due to the pullup resistor.

Pullup resistors are selected based on recommended drain currents. This design uses 1.5-k $\Omega$  pullup resistors and is tested at 100 Kbps.

#### 6.3 LED Indicators

LED indications for 15-V, -15-V, and 5-V isolated power supplies are provided in this design.

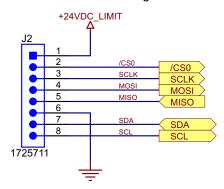

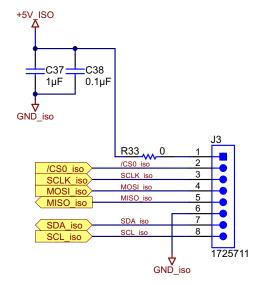

## 6.4 Input and Output Connectors

Input connector:

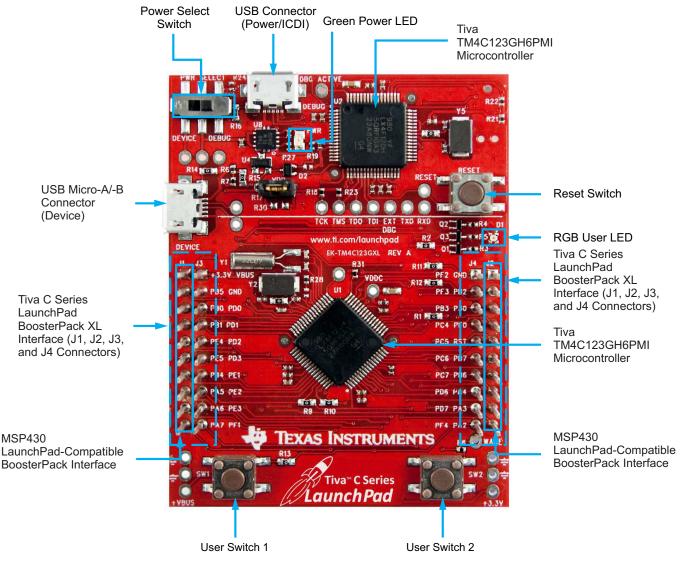

8-pin screw type terminal blocks for interfacing non-isolated SPI, I2C, and input power

Output connectors:

- 8-pin screw type terminal block for interfacing isolated SPI and I2C

- 4-pin screw type terminal block for isolated voltage outputs

## 7 Circuit Design for Isolated Synchronous Communication With Split Rail Fly-Buck™ Power-Supply Board

## 7.1 Power Supply

## 7.1.1 DC/DC Converter for Generation of Output Voltages

The Fly-Buck converter is evolved from a synchronous buck converter by adding coupled windings to the inductor to have flyback-like isolated outputs. The isolated outputs can be multiple by adding more secondary windings to the transformer.

Figure 4. Fly-Buck™ Topology Basics

The Fly-Buck is capable of generating multiple isolated and negative outputs. Fly-Buck topology has better regulation, better efficiency, and lower cost compared to flyback topology.

Figure 5. LM5017 Functional Block Diagram

The LM5017 is configured in Fly-Buck topology to generate non-isolated 3.3 V and isolated 5, 15, and -15 V from 24-V DC. An isolated Fly-Buck converter uses a coupled inductor windings to generate isolated outputs. Flyback topology does not need for an optocoupler or auxiliary winding as the secondary output closely tracks the primary output voltage, resulting in a cost effective and smaller-sized solution.

**Table 7. Power-Supply Specifications**

| INPUT — DC NOMINAL | OUTPUTS ISOLATED — DC |        | OUTPUT NON-ISOLATED — DC |       |

|--------------------|-----------------------|--------|--------------------------|-------|

| INFOT — DC NOMINAL | VOLTAGE               | LOAD   | VOLTAGE                  | LOAD  |

|                    | 15 V                  | 50 mA  |                          | 25 mA |

| 24 V               | –15 V                 | 50 mA  | 3.3 V                    |       |

|                    | 5 V                   | 100 mA |                          |       |

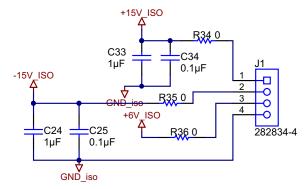

Figure 6. Fly-Buck™ Power-Supply Schematic

Table 8. LM5017 Fly-Buck™ Calculation

|            | SPECIFICATIONS |      | NOTE                         |

|------------|----------------|------|------------------------------|

| NAME       | (V)            | (A)  | NOTE                         |

| Vin_min    | 17             |      |                              |

| Vin_max    | 32             |      |                              |

| Vopri      | 7.9            | 0    |                              |

| Vosec1     | 5              | 0.1  |                              |

| Vosec2     | 5              | 0.1  |                              |

| Vosec3     | 15             | 0.05 |                              |

| Vosec4     | 15             | 0.05 |                              |

| η          | 0.85           |      | Assumed efficiency           |

| fsw        | 270            | kHz  |                              |

| Ron        | 344.23         | kΩ   |                              |

| Dmax       | 0.55           |      |                              |

| Dmin       | 0.29           |      |                              |

| Toff_min   | 1.68           | μs   | Toff_min > 0.144 μs          |

| Vdiode     | 0.3            | V    | Rectifier diode voltage drop |

| Nsec1/Npri | 0.67           |      |                              |

| Nsec2/Npri | 0.67           |      |                              |

| Nsec3/Npri | 1.94           |      |                              |

| Nsec4/Npri | 1.94           |      |                              |

## Table 9. Peak Current

| NAME     | VALUE | UNIT | NOTE            |

|----------|-------|------|-----------------|

| IL (avg) | 0.328 | A    |                 |

| Lpri     | 50    | μH   |                 |

| ΔIL      | 0.441 | A    |                 |

| IL_peak  | 0.548 | A    | IL_peak < 0.7 A |

## **Table 10. Transformer Design**

| NAME                    | VALUE                | DESCRIPTION                                                                     |  |

|-------------------------|----------------------|---------------------------------------------------------------------------------|--|

| CORE SELECTION          |                      |                                                                                 |  |

| Pout_total              | 2.5 W                |                                                                                 |  |

| Ae                      | 19.5 mm <sup>2</sup> | Effective core area                                                             |  |

| le                      | 24.2 mm              | Effective core length                                                           |  |

| Ve                      | 472 mm <sup>3</sup>  | Effective core volume                                                           |  |

| NUMBER OF TURNS         |                      |                                                                                 |  |

| Bmax                    | 250 mT               | Assumed max flux density in steady state                                        |  |

| Npri_min                | 6                    | Min prim. turns based on Bmax and peak currents                                 |  |

| Npri                    | 15                   | Actual prim. turns (Npri > Npri_min)                                            |  |

| Nsec1                   | 10                   |                                                                                 |  |

| Nsec1                   | 10                   |                                                                                 |  |

| Nsec1                   | 29                   |                                                                                 |  |

| Nsec1                   | 29                   |                                                                                 |  |

| FLUX DENSITY CHECK      |                      |                                                                                 |  |

| Ilim_max                | 1.3 A                | Max current limit                                                               |  |

| Bsat                    | 350 mT               | Saturation flux density                                                         |  |

| Bmat_sc                 | 222 mT               | Max flux density in short circuit Check Bmax_sc < Bsat, otherwise increase Npri |  |

| AIR GAP ESTIMATION (FOR | SMALL GAP)           |                                                                                 |  |

| μ0                      | 1.257E-06 H/m        | Vacuum permeability                                                             |  |

| μe                      | 219                  | Effective permeability                                                          |  |

| le/µe                   | 0.110 mm             |                                                                                 |  |

| ROUND CENTER POLE (LIKE | E CORE)              |                                                                                 |  |

| Dcp                     | 4.5 mm               | Center pole diameter                                                            |  |

| lg                      | 0.116 mm             | Air gap length                                                                  |  |

| RECTANGULAR CENTER PO   | LE (LIKE E CORE)     |                                                                                 |  |

| а                       | 3 mm                 | Center pole width                                                               |  |

| b                       | 4 mm                 | Center pole length                                                              |  |

| lg                      | 0.118 mm             | Air gap length                                                                  |  |

| CORE LOSS               |                      |                                                                                 |  |

| fsw                     | 270.00 kHz           |                                                                                 |  |

| ΔΒ                      | 38 mT                |                                                                                 |  |

| Pv                      | 50 kW/m <sup>3</sup> | Look up Pv in core material chart based on fsw and $\Delta B$                   |  |

| Pcore                   | 24 mW                | Core loss                                                                       |  |

## 7.1.2 UV Protection

The undervoltage lockout (UVLO) circuit allows the input undervoltage threshold and hysteresis to be independently programmed.

$$V_{IN} \text{ (UVLO,rising)} = 1.225 \times \left(\frac{R28}{R29} + 1\right)$$

where

• R28 =

$$60.4 \text{ k}\Omega$$

•

$$R29 = 4.87 \text{ k}\Omega$$

(1)

Then,  $V_{IN}$  (UVLO, rising) = 16.46 V.

$$V_{IN}$$

(HYS) =  $I_{HYS} \times R28$

where

•

$$I_{HYS} = 0.02 \text{ mA}$$

(2)

Then,  $V_{IN}$  (HYS) = 1.208 V.

## 7.1.3 Isolated Output Voltage Regulators

#### 7.1.3.1 Isolated 15 V

The TPS7A4700 is designed with bipolar technology primarily for high-accuracy, high-precision instrumentation applications where clean voltage rails are critical to maximize system performance. This feature is a must for powering operational amplifiers, ADCs, DACs, and other high-performance analog circuitry in critical applications such as medical, radio frequency (RF), and test-and-measurement.

In addition, the TPS7A4700 is ideal for post DC/DC converter regulation. By filtering out the output voltage ripple inherent to DC/DC switching conversions, maximum system performance is ensured in sensitive instrumentation, test-and-measurement, audio, and RF applications.

Output voltages are user-programmable (up to 20.5 V) using a printed circuit board (PCB) layout without the need of external resistors or feed-forward capacitors, thus reducing overall component count.

Figure 7. TPS7A4700 15-V Regulator

Table 11. TPS7A4700 Critical Parameters

PARAMETER

| PARAMETER                  | TPS7A4700           |

|----------------------------|---------------------|

| Output options             | Programmable output |

| V <sub>IN</sub> (Min) (V)  | 3                   |

| V <sub>IN</sub> (Max) (V)  | 36                  |

| V <sub>OUT</sub> (Min) (V) | 1.4                 |

| V <sub>OUT</sub> (Max) (V) | 20.5                |

| Iq (Typ) (mA)              | 0.58                |

| Vdo (Typ) (mV)             | 216                 |

| Accuracy (%)               | 2.5                 |

| Noise (μV <sub>RMS</sub> ) | 4                   |

| PSRR at 100 kHz (dB)       | 68                  |

#### 7.1.3.2 Isolated -15 V

The TPS7A3001 is a negative, high-voltage (-36 V), ultra low-noise ( $15.1 \, \mu V_{RMS}$ , 72 dB PSRR) linear regulator. TPS7A3001 includes a CMOS logic-level-compatible enable pin and capacitor-programmable soft-start function that allows for customized power-management schemes. Other features available include built-in current limit and thermal shutdown protection to safeguard the device and system during fault conditions.

The TPS7A3001 is designed using bipolar technology and is ideal for high-accuracy, high-precision instrumentation applications where clean voltage rails are critical to maximize system performance. This design is an excellent choice to power operational amplifiers, ADCs, DACs, and other high-performance analog circuitry.

In addition, the TPS7A3001 linear regulator is suitable for post DC/DC converter regulation. By filtering out the output voltage ripple inherent to DC/DC switching conversion, maximum system performance is provided in sensitive instrumentation, test and measurement, audio, and RF applications.

Figure 8. TPS7A3001 -15-V Regulator

| PARAMETER                  | TPS7A3001                            |

|----------------------------|--------------------------------------|

| Output options             | Adjustable output<br>Negative output |

| V <sub>IN</sub> (Min) (V)  | -36                                  |

| V <sub>IN</sub> (Max) (V)  | -3                                   |

| V <sub>OUT</sub> (Min) (V) | -33                                  |

| V <sub>OUT</sub> (Max) (V) | -1.2                                 |

| Iq (Typ) (mA)              | 0.05                                 |

| Vdo (Typ) (mV)             | 216                                  |

| Accuracy (%)               | 2.5                                  |

| Noise (µV <sub>RMS</sub> ) | 15                                   |

|                            |                                      |

Table 12. TPS7A3001 Critical Parameters

PSRR at 100 kHz (dB)

55

#### 7.1.3.3 Isolated 5 V

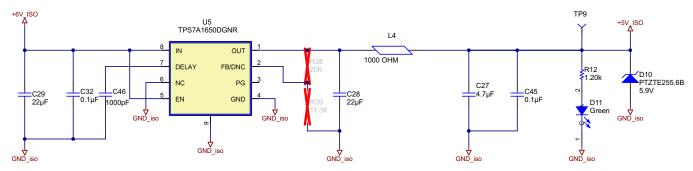

An isolated 5 V is generated using TPS7A1650 linear regulator.

The TPS7A1650 is ultra-low power, low-dropout (LDO) voltage regulator, which offers the benefits of ultra-low quiescent current, high input voltage and miniaturized, high thermal-performance packaging.

The TPS7A1650 is designed for continuous or sporadic (power backup) battery-powered applications where ultra-low quiescent current is critical to extending system battery life.

The TPS7A1650 offers an enable pin (EN) compatible with standard CMOS logic and an integrated open drain active-high power good output (PG) with a user-programmable delay. These pins are intended for use in microcontroller-based, battery-powered applications where power rail sequencing is required.

Figure 9. TPS7A1650 5-V Regulator

| PARAMETER                  | TPS7A1650    |

|----------------------------|--------------|

| Output options             | Fixed output |

| V <sub>IN</sub> (Min) (V)  | 3            |

| V <sub>IN</sub> (Max) (V)  | 60           |

| Fixed Output Options (V)   | 5            |

| V <sub>OUT</sub> (Min) (V) | 5            |

| V <sub>OUT</sub> (Max) (V) | 5            |

| I <sub>Q</sub> (Typ) (mA)  | 0.005        |

| Vdo (Typ) (mV)             | 60           |

| Accuracy (%)               | 2            |

| PSRR at 100 kHz (dB)       | 26           |

Table 13. TPS7A1650 Critical Parameters

The isolated SPI and I2C are interfaced with external devices. These external devices can operate on 3.3 V or 5 V. Currently, the levels are configured for external devices operating at 5 V. When the slave devices are operating at 3.3 V, change the following to configure the interface signals to 3.3 V:

- 1. Change U5: Use TPS7A1501 instead of TPS1650.

- 2. Populate R38 and R39 with values shown in the schematic and BOM. Currently, R38 and R39 are shown as do not populate.

The Fly-Buck design can generate –5 V. There is no requirement for –5 V in the designs this module is targeted to interface with; therefore, the design does not have the –5-V output regulator.

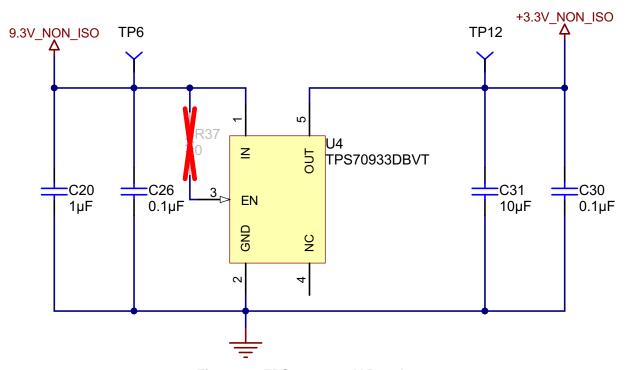

## 7.1.4 3.3-V Non-isolated Output Voltage

VCC\_NON\_ISO is applied to TPS70933 linear regulator that generates 3.3 V\_NON\_ISO. The 3.3 V\_NON\_ISO is used to power-up SPI and I2C digital isolators.

The TPS70933 linear regulator is an ultra-low, quiescent current device designed for power-sensitive applications. A precision band-gap and error amplifier provides 2% accuracy over temperature. Quiescent current of only 1  $\mu$ A makes TPS70933 ideal solutions for battery-powered, always-on systems that require very little idle-state power dissipation. TPS70933 have thermal-shutdown, current-limit, and reverse-current protections for added safety.

This regulator can be put into shutdown mode by pulling the EN pin low. The shutdown current in this mode goes down to 150 nA, typically.

Figure 10. TPS70933 3.3-V Regulator

Table 14. TPS70933 Critical Parameters

| PARAMETER                  | TPS70933     |

|----------------------------|--------------|

| Output options             | Fixed output |

| V <sub>IN</sub> (Min) (V)  | 2.7          |

| V <sub>IN</sub> (Max) (V)  | 30           |

| Fixed Output Options (V)   | 3.3          |

| V <sub>OUT</sub> (Min) (V) | 3.3          |

| V <sub>OUT</sub> (Max) (V) | 3.3          |

| Iq (Typ) (mA)              | 0.001        |

| Vdo (Typ) (mV)             | 300          |

| Accuracy (%)               | 2            |

| PSRR at 100kHz (dB)        | 26           |

## 7.1.5 Power-Supply Performance

Table 15. Current Consumption for SPI and I2C Isolators

| DEVICE | NON-ISOLATED SIDE — CURRENT AT 3.3 V | ISOLATED SIDE — CURRENT<br>AT 5 V |

|--------|--------------------------------------|-----------------------------------|

| SPI    | 3.5 mA                               | 9.6 mA                            |

| I2C    | 3.5 mA                               | 3.5 mA                            |

**Table 16. Maximum Power on Output Voltages**

| OUTPUT VOLTAGE | POWER  |

|----------------|--------|

| 15 V           | 0.8 W  |

| –15 V          | 0.8 W  |

| 5 V            | 0.55 W |

| 3.3 V          | 0.1 W  |

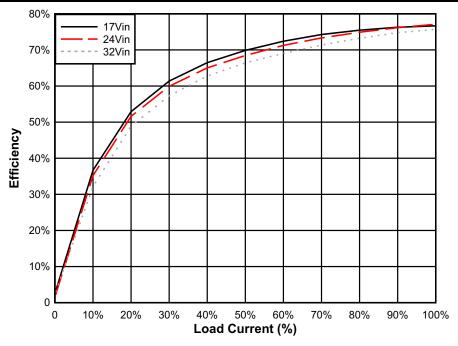

**Table 17. Efficiency Calculation**

| NAME         | VALUE  |

|--------------|--------|

| Output power | 2.25 W |

| Input power  | 3.1 W  |

| Efficiency   | >72%   |

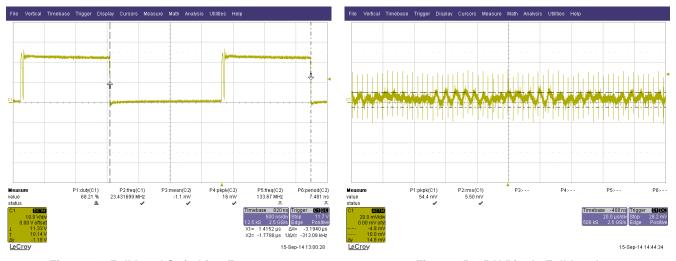

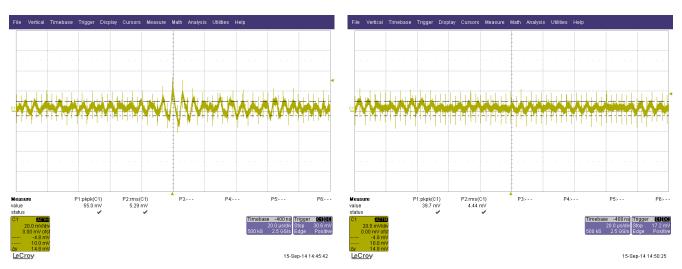

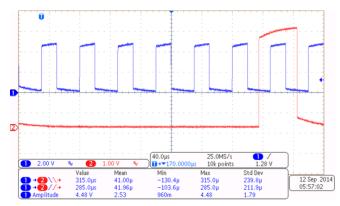

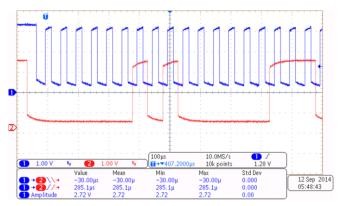

Figure 11. Efficiency Plot

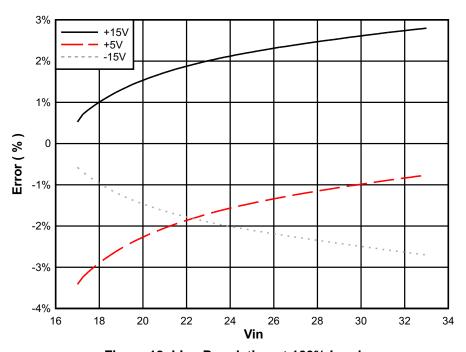

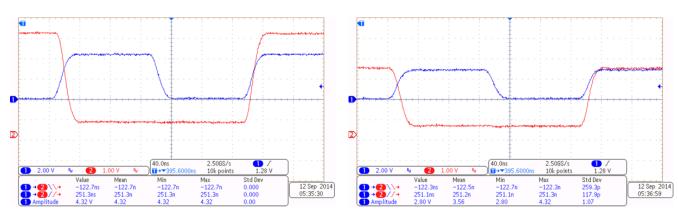

Figure 12. Line Regulation at 100% Load

## 7.1.6 Recommendations for Power Supply

- 1. Power supply must be on before SPI or I2C communication is initiated.

- 2. Do not hot swap the input and output power.

- 3. Do not apply overvoltage >30 V at the input.

## 7.2 Signal Isolation

## 7.2.1 Serial Peripheral Interface (SPI)

Figure 13. Pin Configuration for ISO7141CC (Top View)

Table 18. Output — High and Low Levels for ISO7141CC

|                 | PARAMETER                 | TEST CONDITIONS          | MIN                   | TYP | MAX | UNIT |

|-----------------|---------------------------|--------------------------|-----------------------|-----|-----|------|

| W               | High-level output voltage | $I_{OH} = -4 \text{ mA}$ | $V_{CCx}^{(1)} - 0.5$ | 4.8 |     | V    |

| V <sub>OH</sub> | High-level output voltage | I <sub>OH</sub> = -20 μA | $V_{CCx}^{(1)} - 0.1$ | 5   |     | V    |

| \/              | Low lovel output voltage  | I <sub>OL</sub> = 4 mA   |                       | 0.2 | 0.4 | V    |

| V <sub>OL</sub> | Low-level output voltage  | I <sub>OL</sub> = 20 μA  |                       | 0   | 0.1 | v    |

$<sup>^{(1)}</sup>$   $V_{CCx}$  is the supply voltage,  $V_{CC1}$  or  $V_{CC2}$ , for the output channel that is being measured.

Table 19. Input Levels for ISO7141CC

|                 | PARAMETER                                           | MIN | TYP | MAX             | UNIT |

|-----------------|-----------------------------------------------------|-----|-----|-----------------|------|

|                 | High-level output current (V <sub>CC</sub> ≥ 3.0 V) | -4  |     |                 | mA   |

| IOH             | High-level output current (V <sub>CC</sub> < 3.0 V) | -2  |     |                 | mA   |

| I <sub>OL</sub> | Low-level output current                            |     |     | 4               | mA   |

| V <sub>IH</sub> | High-level input voltage                            | 2   |     | V <sub>CC</sub> | V    |

| V <sub>IL</sub> | Low-level input voltage                             | 0   |     | 0.8             | V    |

This design is tested for the application requirement speed up to 4 Mbps.

ISO7141CC provide galvanic isolation up to 2500  $V_{RMS}$  for one minute per UL and 4242  $V_{PK}$  per VDE. ISO7141 is quad-channel isolator with three forward and one reverse-direction channels. ISO7141CC is capable of a 50-Mbps maximum data rate with a 5-V supply and a 40-Mbps maximum data rate with a 3.3-V or 2.7-V supply, with integrated filters on the inputs for noise-prone applications. The default output state is high as required for SPI.

Each isolation channel has a logic input and output buffer separated by a silicon dioxide (SiO2) insulation barrier. Used in conjunction with isolated power supplies, this device prevents noise currents on a data bus or other circuits from entering the local ground and interfering with or damaging sensitive circuitry. The device has TTL input thresholds and can operate from 2.7-V, 3.3-V, and 5-V supplies. All inputs are 5-V tolerant when supplied from a 2.7-V or 3.3-V supply.

Figure 14. ISO7141CC — SPI Isolator Section

Table 20. ISO7141CC Critical Parameters

| PARAMETER                                                      | ISO7141CC   |

|----------------------------------------------------------------|-------------|

| UL 1577 isolation voltage (single) (kV <sub>RMS</sub> )        | 2500        |

| VDE DIN EN 60747-5-5 basic transient overvoltage rating (kVpk) | 4200        |

| VDE DIN EN 60747-5-5 basic surge voltage rating (kVpk)         | 4000        |

| VDE DIN EN 60747-5-5 basic working voltage rating (kVpk)       | 566         |

| Number of channels                                             | 4           |

| Forward/reverse channels                                       | 3/1         |

| Supply voltages (V)                                            | 2.7, 3.3, 5 |

| Default output                                                 | High        |

| CSA 60950-1 basic working (V <sub>RMS</sub> )                  | 370         |

| CSA 60950-1 reinforced working (V <sub>RMS</sub> )             | 185         |

| CSA 61010-1 basic working (V <sub>RMS</sub> )                  | 300         |

| CSA 61010-1 reinforced working (V <sub>RMS</sub> )             | 150         |

| CSA Isolation Rating (V <sub>RMS</sub> )                       | 3000        |

| TTL/CMOS input threshold                                       | TTL, CMOS   |

| Propagation delay (ns)                                         | 23          |

**NOTE:** Alternatively, use a ISO7741 digital isolator. The ISO7741 device has low power consumption, typical 1.5-mA per channel at 1Mbps, and low propagation delay: 10.7 ns typical at 5 V. Other advantages include robust electromagnetic compatibility (EMC) including system-level ESD, EFT, and surge immunity and low emissions.

#### 7.2.2 I2C Interface

Figure 15. Pin Configuration for ISO1540 and ISO1541

|              | PARAMETER                        | MIN        | NOM MAX    | UNIT |

|--------------|----------------------------------|------------|------------|------|

| VCC1, VCC2   | Supply voltage                   | 3          | 5.5        |      |

| VSDA1, VSCL1 | I/O signal voltages, side 1      | 0          | VCC1       |      |

| VSDA2, VSCL2 | I/O signal voltages, side 2      | 0          | VCC2       |      |

| VIL1         | Low-level input voltage, side 1  | 0          | 0.5        | V    |

| VIH1         | High-level input voltage, side 1 | 0.7 x VCC1 | VCC1       |      |

| VIL2         | Low-level input voltage, side 2  | 0          | 0.3 × VCC2 |      |

| VIH2         | High-level input voltage, side 2 | 0.7 × VCC2 | VCC2       | 1    |

Table 21. Input and Output Levels for ISO1541

The ISO1541 is a low-power, bidirectional isolator that is compatible with I2C interfaces. This device has logic input and output buffers separated by TI's capacitive isolation technology using a SiO2 barrier. When used in conjunction with isolated power supplies, this device blocks high voltages, isolates grounds, and prevents noise currents from entering the local ground and interfering with or damaging sensitive circuitry.

This isolation technology provides for function, performance, size, and power consumption advantages when compared to optocouplers. The ISO1541 enable a complete isolated I2C interface to be implemented within a small form factor.

The ISO1541 has a bidirectional data and a unidirectional clock channel. The ISO1541 is useful in applications that have a single master while the ISO1540 is ideally fit for multi-master applications.

Isolated bidirectional communications is accomplished within ISO1541 by offsetting the side one low-level output voltage to a value greater than the side one high-level input voltage thus preventing an internal logic latch that otherwise would occur with standard digital isolators.

Figure 16. ISO1541 — I2C Isolator

Table 22. ISO1541 Critical Parameters

| ISO1541        |

|----------------|

| 2.5            |

| 4.3            |

| 4              |

| 0.0566         |

| 2.8            |

| 390            |

| 300            |

| 150            |

| 1              |

| 2              |

| Unidirectional |

| Bidirectional  |

|                |

| Table 23. Pullup Recommendations for I2C Interface(1) | Table 23. P | Pullup Recommendations | for | 12C | Interface <sup>(1)</sup> |