TI Designs: TIDA-01168

# Bidirectional DC-DC Converter Reference Design for 12-V/48-V Automotive Systems

### Description

The TIDA-01168 reference design is a four-phase. bidirectional DC-DC converter development platform for 12-V/48-V automotive systems. The system uses two LM5170-Q1 current controllers and a C2000™ TMS320F28027F microcontroller (MCU) for the power stage control. LM5170-Q1 subsystems provide current control using an innovative average current control scheme whereas the C2000™ microcontroller provides voltage feedback to the system. Such a control scheme eliminates an additional phase-currentbalancing circuitry, which is typical for multiphase converters. A system based on LM5170-Q1 allows a high level of integration, which reduces printed-circuit board (PCB) area, simplifies design, and speeds up development. The TIDA-01168 reference design fulfills the typical operating voltage requirements for 12-V/48-V automotive systems.

### Resources

TIDA-01168 Design Folder LM5170-Q1 Product Folder TMS320F28027F Product Folder LM5010A-Q1 Product Folder TPS560200-Q1 Product Folder TMP102-Q1 Product Folder TPS3306-Q1 Product Folder MC33063A-Q1 Product Folder TLC2272-Q1 Product Folder

# TI E2E™ Community

ASK Our E2E Experts

### **Features**

- 12-V Input Voltage Range: 6 V to 18 V

- 48-V Input Voltage Range: 24 V to 54 V

- Reverse Polarity, Overcurrent, Overvoltage, and Overtemperature Protections

- Multiphase Scalable Option

- Highly Integrated Solution Using Automotive Qualified Components

### **Applications**

- In-Vehicle Power Distribution in 12-V/48-V Automotive Systems

- Supercapacitor or Battery Backup Power Converters

System Description www.ti.com

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

### 1 System Description

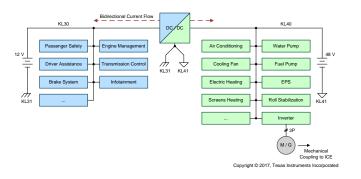

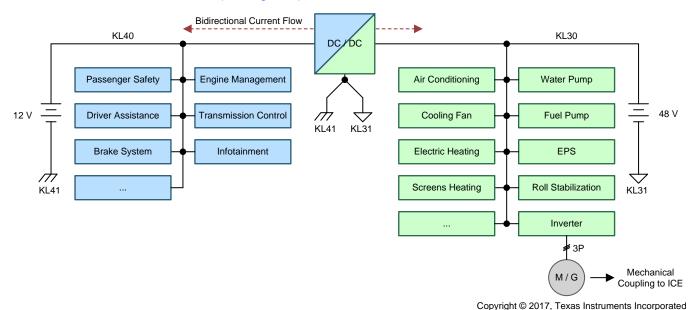

A bidirectional DC-DC converter applies in efficient electrical energy transfer and storage applications. A typical system uses two batteries, battery and motor-generator, or a combination of both (see Figure 1). Lithium-lon (Li-lon) or Lithium-Polymer (Li-Pol) technology provides the best performance. Alternatively, lead-acid batteries (Pb) are used for high-capacity and low-cost energy storage.

Figure 1. Dual Battery System Combined With Motor Generator

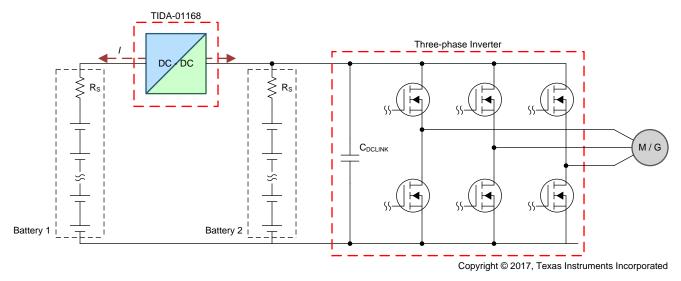

Modern Li-Ion and Li-Pol batteries have very-low series resistance and flat discharging curve. Figure 2 shows a typical discharge curve for a Li-Pol cell. The blue and red line represent different discharge currents with reference to the nominal cell capacity C. Note that cell voltage does not change significantly with the charge level from 0% to 80%.

Figure 2. Li-Pol Cell Typical Discharge Curve

For this reason, operating voltage on the power rails does not significantly change. The charge and discharge process of the cells affects slow voltage changes whereas the internal series resistance,  $R_i$ , causes short voltage transients. Consequently, the current control loop performance is more important than the voltage loop.

The TIDA-01168 uses the LM5170-Q1, which is a bidirectional, switched-mode current controller. In this case, the DC-DC converter operates more as an ideal current source with variable direction. This configuration allows energy transfer between two voltage domains. The microcontroller-based voltage feedback only maintains output voltage within the acceptable operating range and eventually allows a custom charging profile for the battery pack. See the key system specifications in Section 1.1.

www.ti.com System Description

# 1.1 Key System Specifications

**Table 1. Key System Specifications**

| PARAMETER                             | SPECIFICATIONS            |

|---------------------------------------|---------------------------|

| AD conversion resolution              | 12 b                      |

| Voltage reference                     | 2.495 V                   |

| Control loop resolution               | 10 b                      |

| Switching frequency                   | 100 kHz                   |

| MCU system clock                      | 50 MHz                    |

| Digital loop update rate              | 48.828125 kHz             |

| Number of phases                      | Four                      |

| Output power (BUCK mode)              | < 2 kW                    |

| Output power (BOOST mode)             | < 2 kW                    |

| 12-V terminal input operating voltage | 6 V to 18 V; nominal 12 V |

| 48-V terminal input operating voltage | 24 V to 54; nominal 48 V  |

| Efficiency (BUCK mode)                | < 97 %                    |

| Efficiency (BOOST mode)               | < 97 %                    |

| Maximum output current (BUCK mode)    | < 166 A                   |

| Maximum output current (BOOST mode)   | < 42 A                    |

System Overview www.ti.com

# 2 System Overview

The TIDA-01168 reference design is intended to serve as a development basis for a bidirectional DC-DC converter for 12-V/48-V automotive systems, not a complete solution. Advanced features such as CAN communication or safety solutions to meet any Automotive Safety Integrity Level (ASIL) are not a part of the design.

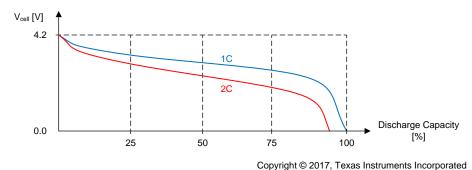

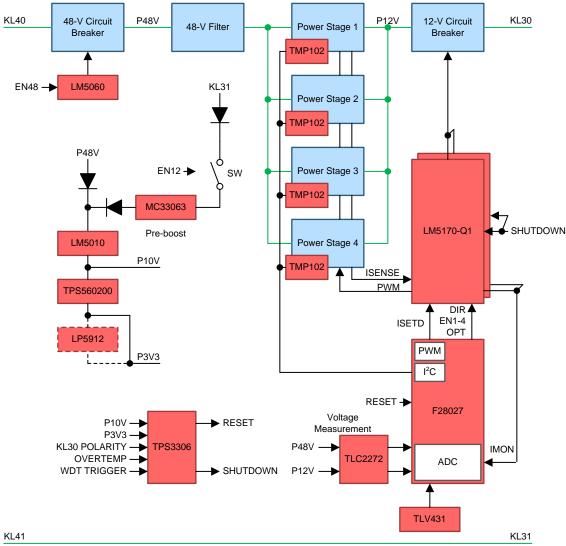

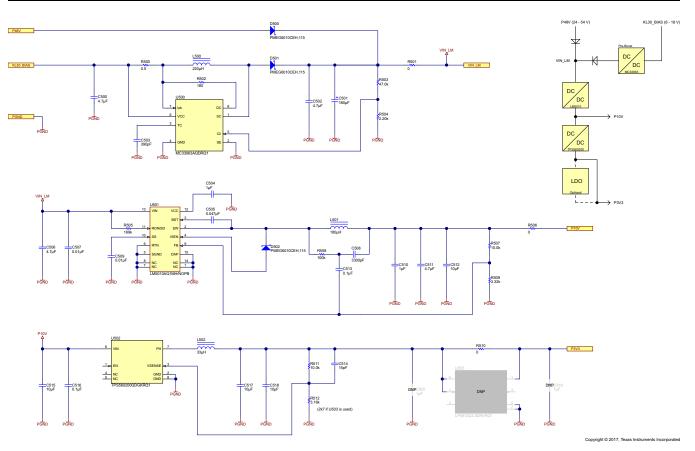

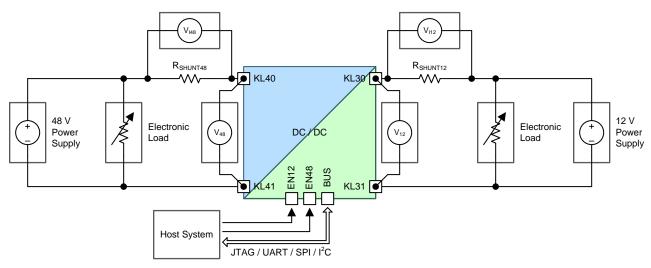

### 2.1 Block Diagram

Copyright © 2017, Texas Instruments Incorporated

Figure 3. TIDA-01168 Block Diagram

www.ti.com System Overview

# 2.2 Introduction to 48-V Systems

Reducing the environmental burden caused by excess emissions is an increasingly growing trend throughout the world and across all industries, including automotive. Carbon dioxide  $(CO_2)$ , while not regulated as an air pollutant, is the transportation sector's primary contribution to climate change [1]. In 2009 the European Commission set a target for 2015 fleet average of  $CO_2$  emissions to 130 grams per kilometer. Manufacturers are allowed to form a transparent pool for up to five years to achieve this target. In 2016 the average emissions level of a new car sold was 118.1 g/km. At the time of this writing, the European Commission has recently introduced a new regulation for  $CO_2$  emission limits. An even stricter regulation with 95 g  $CO_2$  / km limit is to begin in 2020 for the fleet average of each manufacturer [2].

Violation of these regulations results in an excess emissions premium to be paid by the car manufacturer. Car manufacturers apply various strategies to fulfill these emissions requirements. Increasing the invehicle power voltage is one of these strategies. The European automotive industry encourages 48-V technology as the next evolution step in onboard vehicle power. 48-V technology better optimizes power distribution in a vehicle, allows weight reduction, and allows for mild-hybrid operation while keeping costs reasonable. This technology altogether helps to reduce CO2 emissions. Five European OEM car manufacturers contribute to 48-V systems standardization. System requirements are specified in the VDO320 and LV148 norms (see Figure 4).

Figure 4. Split In-Vehicle Power in Typical 12-V and 48-V System

Figure 4 shows the typical structure of a split in-vehicle power network. The strategy is to move all power hungry components to the 48-V side with a Li-Ion battery, Li-Fe battery, or supercapacitor energy storage. This measure reduces input current by a factor of four for the same output power.

One trend also shows integration of the starter and generator into a single device:

- Integrated starter-generator (commercially referred to as ISG, ISA, ISAD, CAS, CSA, CISG, and so forth)

- Belt starter-generator (commercially referred to as BAS, BSG, BISG, BSA, eAssist, and so forth) These inverter-controlled synchronous (permanent-magnet synchronous motor (PMSM)) or asynchronous machines are able to start the internal combustion engine (ICE), help with acceleration (torque assist), and recuperate energy during braking (regenerative braking). The 12-V power rail provides backward compatibility with current automotive systems such as infotainment or engine management. A traditional lead-acid battery also has better capacity-to-cost ratio, better performance at low temperatures, and lower self-discharge in comparison with supercapacitors. A bidirectional DC-DC converter is required for energy transfer between both sides. Step-down (buck) mode applies during normal operation when the ISG or BSG on the 48 V operates as a generator, such as in a conventional vehicle. Step-up (boost) mode applies during the ICE start when energy in the 48-V battery may not be sufficient. However, final implementation is different for different concepts.

System Overview www.ti.com

### 2.2.1 48-V Systems Properties

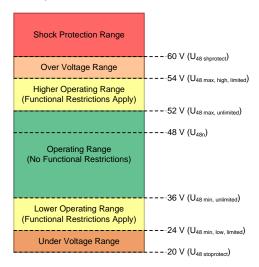

Figure 5 shows the voltage levels specified in VDA320 and Table 2 describes them.

Figure 5. Voltage Levels Defined by VDA320

Table 2. Voltage Levels Defined by VDA320

| ABBREVIATION                         | NOTATION                                                                                                                                        |      |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|

| U <sub>(48 sh protect)</sub>         | Shock protection voltage to fulfill the requirement to not exceed the limit for DC voltages in terms of shock protection according to ECE-R 100 |      |

| U <sub>(48r)</sub>                   | 2-V contingency reserve to the shock protection voltage                                                                                         | 58 V |

| U <sub>(48 max, high, limited)</sub> | Maximum voltage of the upper operating range with functional degradation                                                                        |      |

| U <sub>(48 max, unlimited)</sub>     | Minimum voltage of the upper operating range with functional degradation                                                                        |      |

| U <sub>(48n)</sub>                   | BN48 nominal voltage (the nominal voltage is based on DIN IEC 60038)                                                                            |      |

| U <sub>(48 min, unlimited)</sub>     | Minimum voltage of the operating range without functional degradation                                                                           |      |

| U <sub>(48 min, low, limited)</sub>  | Minimum voltage of the lower operating range with functional degradation                                                                        |      |

| U <sub>(48 stoprotect)</sub>         | Accumulator protection voltage                                                                                                                  |      |

The following lists the general assumptions and requirements from VDA320 [11]:

- Static direct voltages ≤ 60 V occur with a maximum ripple of 10% RMS in the onboard supply voltage.

- A single error in the wiring harness must not cause the 48-V supply to short circuit to the 12-V/24-V system.

- There is a common ground for the 12-V/24-V system and the 48-V system, which are connected through physically-separated grounding bolts or connections.

- All the voltage and current information refers to the component (terminal voltage).

- The polarity of the 48-V supply is prevented from reversing by appropriate measures in the vehicle.

- Jump starting with the 48-V power supply is prevented by appropriate measures applied in the vehicle.

- A single error must not cause a short circuit between the 48-V supply and the 12-V/24-V supply.

- Components simultaneously supplied at 48 V and 12 V/24 V, and interfaces based on 12 V/24 V, require their own ground connections for both supply voltages. These ground connections must be physically separated from one another.

- If a 48-V component loses its ground (terminal 31, terminal 41, or both), this must not disrupt or destroy communication networks or the electrical networks.

- Overcurrent tests should be detailed in the component specifications.

- No component may cause the voltage to enter the dynamic overvoltage range (for example, through a load dump or resonance peaks).

www.ti.com System Overview

If the voltage enters the overvoltage range up to  $U_{(48r)}$ , countermeasures should be taken through the component that is feeding energy back in or causing entry into the overvoltage range, so that the voltage exits the overvoltage range at the lower boundary.

• If the voltage enters the lower limited function range, countermeasures should be taken so that the voltage returns to the unlimited operation range.

### 2.2.2 48-V DC-DC Converter

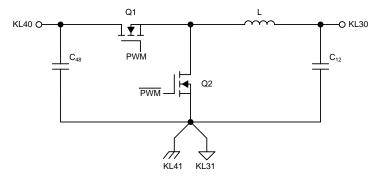

Non-isolated synchronous step-down converter topology is the most common topology used. Synchronous switches allow bidirectional current flow in the boost mode. The topology is a synchronous step-down converter when looking from the 48-V side and the topology is a synchronous step-up converter when looking from the 12-V side, as Figure 6 shows.

Figure 6. Non-Isolated Synchronous Step-Down Converter

A non-isolated DC-DC converter effectively creates a system star-point where common grounds for 12-V and 48-V voltage rails meet. This fact must be considered when designing the vehicle grounding concept. Equipment utilizing both power rails may require functional galvanic isolation to avoid ground loops that cause interference. Minimum standby current is achieved using a circuit breaker on the either side of the converter. The circuit breaker on the 12-V side also protects the converter against reverse polarity condition. Such a protection is not required on the 48-V side, which is intrinsically protected by appropriate measures in the vehicle.

The converter communicates with the host system over the system bus (CAN, FlexRay™).

### 2.3 High-Level Design Description

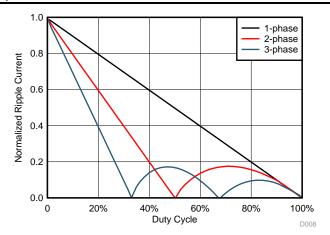

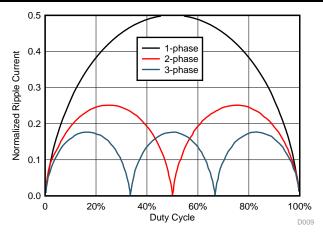

The TIDA-01168 is a multiphase DC-DC converter based on four buck power stages operating in parallel. A multiphase converter is an obvious choice for high-power applications. The typical benefits of a multiphase interleaved DC-DC converter are lower output ripple, which allows for smaller capacitors, faster transient response in comparison with a single-phase converter, smaller inductor size, and even power dissipation distribution over the board. Figure 7 and Figure 8 show how the root mean square (RMS) current is reduced based on the number of phases and duty cycle. The ideal case shows that the total ripple current for the given duty cycle, 25% for buck and 75% for boost mode, is reduced to the minimum. This reduced total ripple current helps to lower input and output capacitance to a minimum.

System Overview www.ti.com

Figure 7. Buck Output RMS Current, Boost Input RMS Current

Figure 8. Buck Input RMS Current, Boost Output RMS Current

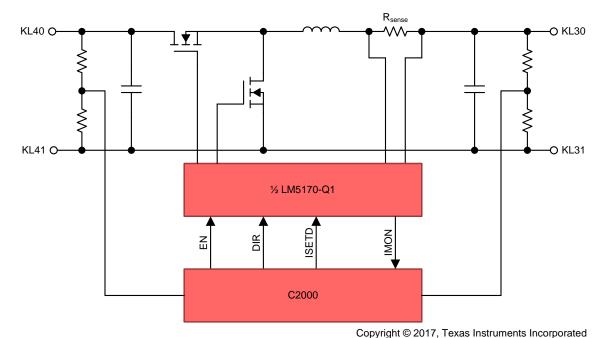

A pair of LM5170-Q1 devices control all four power stages. The LM5170-Q1 multiphase bidirectional current controller provides a complete control including gate drivers and current sensing. The device does not have any voltage feedback loop and acts as a switched mode current source driven by a pulse width modulation (PWM) or analog signal. The amount of current flowing to the load is given by the duty cycle on the ISETD signal. The direction (buck or boost) is set by the DIR signal.

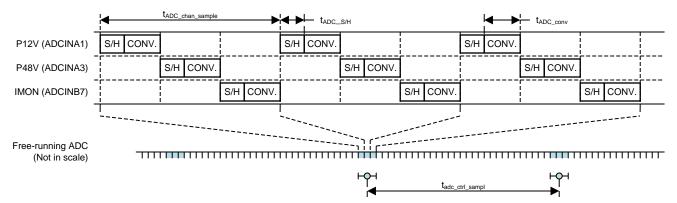

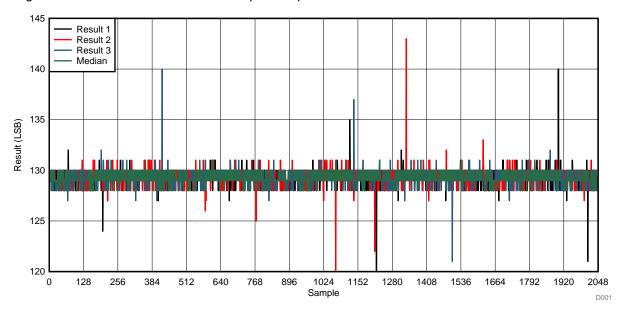

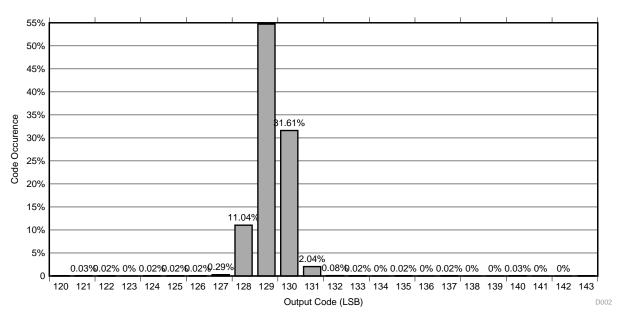

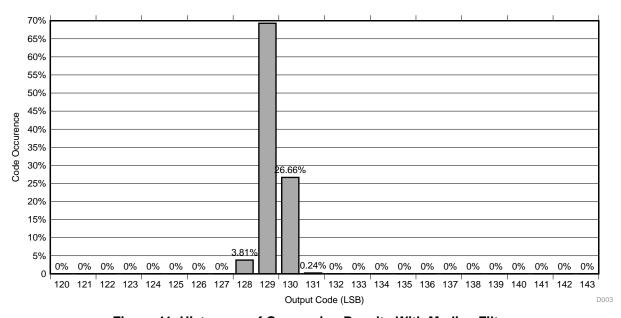

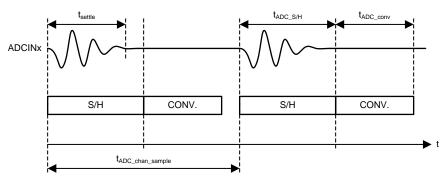

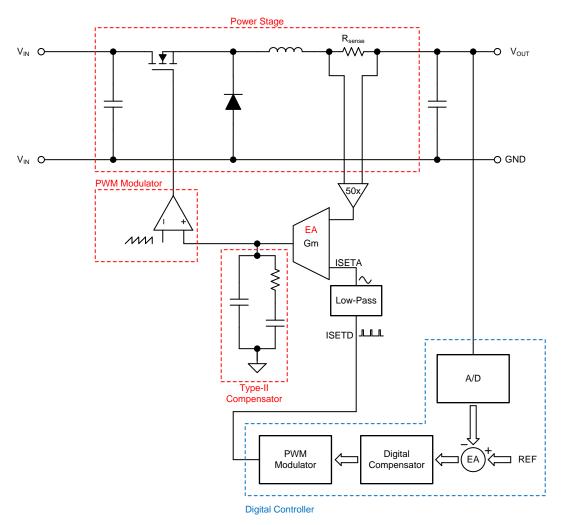

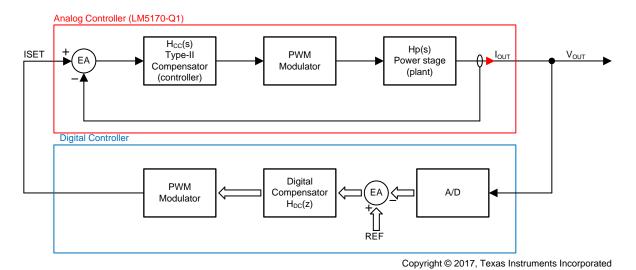

The system uses a digital voltage feedback loop based on the TMS320F28027 C2000™ Piccolo 32-b MCU running at 50 MHz. Figure 9 shows a simplified block diagram for a single phase. The 12-b analog-to-digital converter (ADC) in the MCU periodically reads output voltage every 20.48 µs. The current (set by the ISETD signal) through a load corresponds to the output voltage. The digital error amplifier compares the value from the ADC with the preset value (reference). The digital control loop with a digital compensator then calculates the error and sets a new duty cycle for the ISETD pin. The MCU optionally monitors voltage on the IMON pin, which corresponds to the current through the inductor. This information is not used for the control loop.

Figure 9. Simplified Block Diagram for Voltage and Current Feedback Loop

An L-C filter on the 48-V side helps to reduce output ripple in the boost mode. Output ripple in the boost mode is higher because, during t<sub>on</sub>, the load is energized only from the output capacitors.

www.ti.com System Overview

Each side of the converter can be disconnected from the respective power rail by a circuit breaker based on back-to-back N-MOSFETs configuration. The circuit breaker on the 12-V side is fully controlled by the LM5170-Q1 device, which protects against reverse polarity conditions and allows very low standby current (I<sub>O</sub>) when the system is off. The circuit breaker is shut off when the LM5170-Q1 device detects a failure. This condition is reported by the nFAULT pin. The LM5060-Q1 high-side protection controller controls the 48-V side circuit breaker. Although reverse polarity protection is usually not required for the 48-V rail, a back-to-back N-MOSFETs configuration is used to prevent any current flow when the system is off. The LM5060-Q1 device can trigger on undervoltage, overvoltage, and overcurrent events.

The system can be turned on from either a 12-V or 48-V power rail. A pre-boost DC-DC converter based on the MC33063A-Q1 device is used in the case of a turnon from the 12-V side triggered by the EN12 signal. Input for this pre-boost circuit bypasses the high-current 12-V circuit breaker. Output of the pre-boost DC-DC converter is set to approximately 28 V to provide enough gate voltage for the 12-V circuit breaker. The pre-boost DC-DC uses a hysteretic-based control scheme and therefore automatically stops switching when the 48-V is present. Standby current consumption can be further reduced by setting the EN12 signal low when the P48V voltage is present.

Two additional DC-DC converters are required for a bias power supply. The LM5010-Q1 is a high  $V_{\text{IN}}$  step-down converter with a 10-V output for biasing LM5170-Q1 devices. The TPS560200-Q1 device is used for energizing the rest of the circuitry. The 3.3-V output matches the digital-logic operating-voltage level. An optional linear post-regulator LP5912-Q1 can be used in case the switching noise influences the analog circuitry.

A simple diagnostics block is available in the design. Four configurable TMP102-Q1 temperature sensors communicating over the I²C bus monitor the temperature for each power stage. The ALERT output signals of these temperature sensors are connected to the shutdown signal, which switches off all the power stages after reaching the overtemperature threshold. The TPS3306-Q1 voltage supervisor and watchdog monitors the MCU and voltage rails. The programmable function input (PFI) detects polarity on KL30. Such a feature is required to restrict the 12-V circuit breaker opening during reverse polarity on the KL30. Without this restriction, high current flows through the inductor and body diode of the bottom MOSFET in all power stages, which results in permanent damage.

System Overview www.ti.com

### 2.4 Mechanical Construction

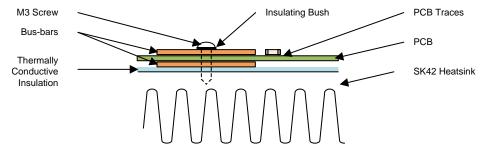

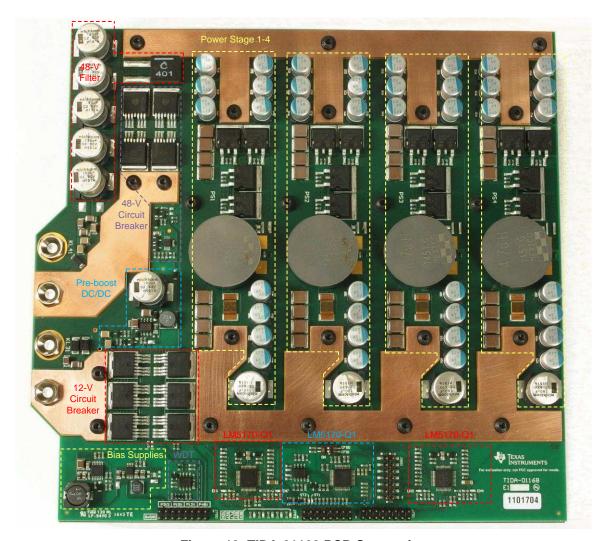

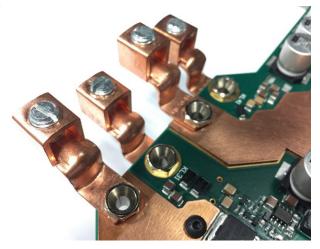

The mechanical construction of TIDA-01168 has been optimized for easy debugging and affordable manufacturing costs using commercially available technologies. Figure 10 shows the sandwich-like construction of the TIDA-01168 design.

Figure 10. Sandwich Construction of TIDA-01168

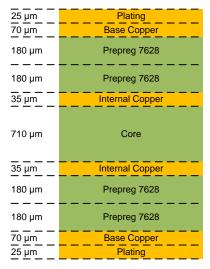

The PCB has four layers with single-side component placement. Figure 11 shows the FR-4 PCB layer stack. The current-carrying capability for high-current paths is further boosted by external, custom-built 1.5-mm thick copper bus bars. The bus bars are mounted on the top and bottom of the PCB on the exposed PCB traces. Bus bars are lacquered on visible sides with polyurethane transparent paint to prevent oxidation. Bus bars on the top layer carry positive voltages whereas the bus bar on the bottom is the common ground (negative terminal KL31, KL41).

Figure 11. PCB Layer Stack for TIDA-01168

Thermally conductive insulator (AMEC THERMASOL: SFT80-0.15-T1) provides electrical isolation between the PCB with the bus bar on the bottom side and the heat sink. This isolation prevents the heat sink from carrying current, which is important for maintaining a defined current return path. Areas without the bottom bus bar have a 1.5-mm gap between the PCB and the heat sink. This gap is filled by "gap-filler" (T GLOBAL: L373-150-2.0A) for better heat transfer from the PCB to the heat sink. This filler is important for the power stages especially underneath of the inductor and MOSFETs.

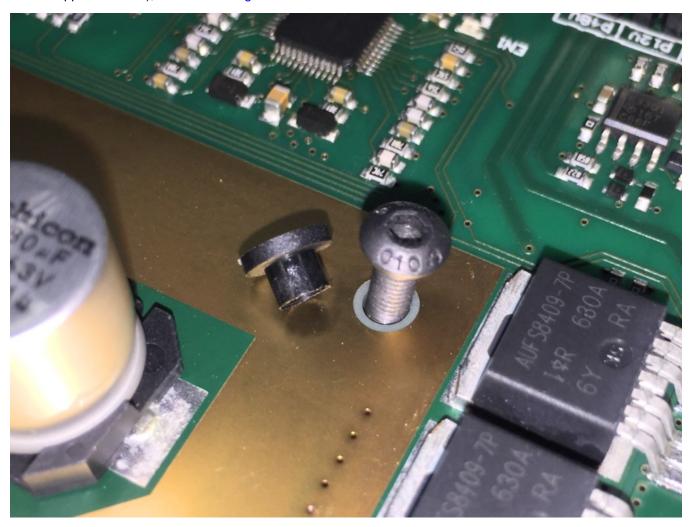

The extruded 200×200-mm heat sink used in this design is made by Fischer Elektronik GmbH & Co. KG. The assembly is held together using M3x10 machine screws. Screws are isolated from all active conductors by isolation bushings similar to those shown in Figure 12, which are typically used to isolate TO220 packages. A drilling plan for the heat sink as well as copper bus bar drawings are available as a part of the documentation.

www.ti.com System Overview

Figure 12. TIDA-01168 Assembled Prototype

Figure 13. TIDA-01168 PCB Structuring

System Overview www.ti.com

Table 3. TIDA-01168 PCB Layout—Selected Design Rules

| SEGMENT                          | DIMENSIONS                     |

|----------------------------------|--------------------------------|

| General traces (analog, digital) | 8 mil minimum, 10 mil typical  |

| Power traces – low current < 1 A | 30 mil typical                 |

| Gate driver traces               | 30 mil typical                 |

| Via size                         | 28 mil/12 mil (diameter/drill) |

| Clearance for power nets         | 20 mil                         |

| Clearance for other traces       | 6 mil minimum, 10 mil typical  |

| Components placement             | Top side only                  |

| Passive components package size  | 0603 (preferred) or larger     |

# 2.5 Highlighted Products

### 2.5.1 LM5170-Q1

The LM5170-Q1 controller provides the essential high voltage and precision elements of a dual-channel bidirectional converter for automotive 48-V and 12-V dual battery systems. The controller regulates the average current flowing between the high-voltage- and low-voltage ports in the direction designated by the DIR input signal. The current regulation level is programmed through analog or digital PWM inputs. Dualchannel differential current sense amplifiers and dedicated channel current monitors achieve typical current accuracy of 1%. Robust 5-A half-bridge gate drivers are capable of driving parallel MOSFET switches delivering 500 W or more per channel. The diode emulation mode of the synchronous rectifiers prevents negative currents but also enables discontinuous mode operation for improved efficiency with light loads. Versatile protection features include cycle-by-cycle current limiting, overvoltage protection at both HV and LV ports, MOSFET failure detection, and overtemperature protection. An innovative average current mode control scheme maintains constant loop gain allowing a single R-C network to compensate both buck and boost conversion. The oscillator is adjustable up to 500 kHz and can synchronize to an external clock. Multiphase parallel operation is achieved by connecting two LM5170-Q1 controllers for three or four-phase operation, or by synchronizing multiple controllers to phase-shifted clocks for a higher number of phases. A low state on the undervoltage lockout (UVLO) pin disables the LM5170-Q1 in a lowcurrent shutdown mode.

### 2.5.2 TMS320F28027

The F2802x Piccolo™ family of microcontrollers provides the power of the C28x core coupled with highly-integrated control peripherals in low pin-count devices. This family is code-compatible with previous C28x-based code and also provides a high level of analog integration. An internal voltage regulator allows for single-rail operation. Enhancements have been made to the HRPWM to allow for dual-edge control (frequency modulation). Analog comparators with internal 10-bit references have been added and can be routed directly to control the PWM outputs. The ADC converts from 0-V to 3.3-V fixed full-scale range and supports ratio-metric VREFHI/VREFLO references. The ADC interface has been optimized for low overhead and latency.

### 2.5.3 LM5010A-Q1

The LM5010Ax step-down switching regulator is an enhanced version of the LM5010 with the input operating range extended to a 6-V minimum. The LM5010Ax features all the functions required to implement a low-cost, efficient, buck regulator capable of supplying in excess of 1-A load current. This high-voltage regulator integrates an N-channel buck switch and is available in thermally-enhanced 10-pin WSON and 14-pin HTSSOP packages. The constant ON-time regulation scheme requires no loop compensation resulting in fast load transient response and simplified circuit implementation. The operating frequency remains constant with line and load variations due to the inverse relationship between the input voltage and the ON-time. The valley current limit detection is set at 1.25 A. Additional features include: VCC undervoltage lockout, thermal shutdown, gate drive undervoltage lockout, and maximum duty cycle limiter.

www.ti.com System Overview

### 2.5.4 TPS560200-Q1

The TPS560200-Q1 is a 17-V, 500-mA, low- $I_Q$ , adaptive ON-time D-CAP2 mode synchronous monolithic buck converter with integrated MOSFETs in an easy-to-use 8-pin MSOP package. The TPS560200-Q1 enables system designers to complete the suite of various end-equipment power bus regulators with a cost-effective, low component count, and low standby current solution. The main control loop for the device uses the D-CAP2 mode control that provides a fast transient response with no external compensation components. The adaptive ON-time control supports seamless transition between PWM mode at higher load conditions and advanced Eco-mode<sup>TM</sup>light load efficiency at light loads. The TPS560200-Q1 also has a proprietary circuit that enables the device to adopt to both low equivalent series resistance (ESR) output capacitors, such as POSCAP or SP-CAP, and ultra-low ESR ceramic capacitors. The device operates from a 4.5-V to 17-V  $V_{\rm IN}$  input. The output voltage can be programmed between 0.8 V and 6.5 V. The device also features a fixed 2-ms soft-start time. The device is available in the 8-pin MSOP package.

### 2.5.5 TMP102-Q1

The TMP102-Q1 device is a digital temperature sensor ideal for NTC/PTC thermistor replacement where high accuracy is required. The device offers an accuracy of  $\pm 0.5^{\circ}$ C without requiring calibration or external component signal conditioning. Integrated circuit temperature sensors are highly linear and do not require complex calculations or look-up tables to derive the temperature. The on-chip 12-bit ADC offers resolutions down to  $0.0625^{\circ}$ C. The 1.6-mm  $\times 1.6$ -mm SOT563 package has a 68% smaller footprint than an SOT23 package. The TMP102-Q1 device features SMBus<sup>TM</sup>, which is compatible with two-wire and I<sup>2</sup>C interface and allows up to four devices on one bus. The device also features an SMBus alert function. The device is specified to operate over supply voltages from 1.4 V to 3.6 V with the maximum quiescent current of 10  $\mu$ A over the full operating range. The TMP102-Q1 device is ideal for extended temperature measurement in a variety of communication, computer, consumer, environmental, industrial, and instrumentation applications. The device is specified for operation over a temperature range of  $-40^{\circ}$ C to 125°C. The TMP102-Q1 production units are 100% tested against sensors that are NIST-traceable and are verified with equipment that are NIST-traceable through ISO/IEC 17025 accredited calibrations.

### 2.5.6 TPS3306-Q1

The TPS3306 family is a series of supervisory circuits designed for circuit initialization that requires two supply voltages, primarily in digital signal processing (DSP) and processor-based systems. The product spectrum of the TPS3306-xx is designed for monitoring two independent supply voltages of 3.3 V/1.5 V, 3.3 V/1.8 V, 3.3 V/2 V, 3.3 V/2.5 V, or 3.3 V/5 V. During power up, RESET is asserted when the supply voltage VDD becomes higher than 1.1 V. Thereafter, the supervisory circuits monitor the SENSEn inputs and keep RESET active as long as SENSEn remains below the threshold voltage VIT. An internal timer delays the return of the RESET output to the inactive state (high) to ensure proper system reset. The delay time, td(typ) = 100 ms, starts after the SENSE1 and SENSE2 inputs have risen above the threshold voltage VIT. When the voltage at SENSE1 or SENSE2 input drops below the threshold voltage VIT, the output becomes active (low) again. The integrated power-fail (PFI) comparator with separate open-drain (PFO) output can be used for low-battery detection, power-fail warning, or for monitoring a power supply other than the main supply. The TPS3306-xx devices integrate a watchdog timer that is periodically triggered by a positive or negative transition of WDI. When the supervising system fails to retrigger the watchdog circuit within the time-out interval, tt(out) = 0.50 s, the RESET becomes active for the time period td. This event also reinitializes the watchdog timer. Leaving WDI unconnected disables the watchdog. The TPS3306-xx devices are available in standard 8-pin SO packages. The TPS3306-xxQ family is characterized for operation over a temperature range of -40°C to 125°C.

# 2.5.7 MC33063A-Q1

The MC33063A-Q1 device is an easy-to-use integrated circuit containing all the primary circuitry required for building simple DC-DC converters. The device primarily consists of an internal temperature-compensated reference, a comparator, an oscillator, a PWM controller with active current limiting, a driver, and a high-current output switch. Thus, the device requires minimal external components to build converters in the boost, buck, and inverting topologies.

System Overview www.ti.com

### 2.5.8 TLC2272-Q1

The TLC2272-Q1 and TLC2274-Q1 devices are dual and quadruple operational amplifiers from Texas Instruments. Both devices exhibit rail-to-rail output performance for increased dynamic range in single- or split-supply applications. The TLC227x-Q1 family offers 2 MHz of bandwidth and 3 V/µs of slew rate for higher-speed applications. These devices offer comparable AC performance while having better noise, input offset voltage, and power dissipation than existing CMOS operational amplifiers. The TLC227x-Q1 has a noise voltage of 9 nV/ $\sqrt{\text{Hz}}$ , which is two times lower than competitive solutions. The TLC227x-Q1, exhibiting high input impedance and low noise, is excellent for small-signal conditioning for high-impedance sources, such as piezoelectric transducers. In addition, the rail-to-rail output feature, with single- or split-supplies, makes this family a great choice when interfacing with analog-to-digital converters (ADCs). For precision applications, the TLC227xA-Q1 family is available with a maximum input offset voltage of 950 µV. This family is fully characterized at 5 V and  $\pm$ 5 V. The devices offer increased output dynamic range, lower noise voltage, and lower input offset voltage. This enhanced feature set allows the devices to be used in a wider range of applications. For applications that require higher output drive and wider input voltage range, see the TLV2432-Q1 and TLV2442-Q1 devices. All of the parameters of the TLC227x-Q1 family enables the device to be applicable in most automotive applications.

### 3 Hardware Design

**NOTE:** This text does not cover the fundamental theory of operation.

### 48-V Circuit Breaker

### 3.1.1 Description

The 48-V circuit breaker allows the DC-DC to completely disconnect from the 48-V battery rail using fieldeffect transistors (FETs). The block also protects the DC-DC against overvoltage and overcurrent. See Table 4 for a system interface overview.

Table 4. System Interface for 48-V Circuit Breaker

| SIGNAL | DIRECTION | DESCRIPTION                                                                                                       |

|--------|-----------|-------------------------------------------------------------------------------------------------------------------|

| KL40   | In/Out    | 48-V car battery system terminal (positive)                                                                       |

| KL41   | In/Out    | 48-V car battery system terminal (negative)                                                                       |

| P48V   | In/Out    | Protected 48-V rail (positive)                                                                                    |

| PGND   | In/Out    | Protected 48-V rail (negative)                                                                                    |

| KL40_M | Out       | 48-V battery four-wire voltage measurement terminal (positive)                                                    |

| KL41_M | Out       | 48-V battery four-wire voltage measurement terminal (negative)                                                    |

| EN48   | In        | Enable signal.; voltage greater than 2.0 V enables the circuit breaker; voltage on this pin shall not exceed 65 V |

### 3.1.2 Considerations

The 48-V circuit breaker conducts and disconnects current up to 50 A in both directions for voltages up to 70 V. The limit of 70 V for 40 ms is given by the E48-02 Transient Overvoltage test defined in VDA320. The ability to disconnect current flow in both directions is generally required; therefore, a back-to-back MOSFETs configuration is used. This requirement is also beneficial; for example, pre-charging the 48-V side capacitors to the KL40 voltage reduces the inrush current during turnon. Selected MOSFETs have a very low R<sub>DS(ON)</sub> and are rated up to 100 V. MOSFETs are in parallel to further reduce I<sup>2</sup>R losses caused by R<sub>DS(ON)</sub>. Gate charge is not important as long as the LM5060-Q1 device is able to turn them ON and OFF fast enough. Give careful consideration to the safety operating area (SOA).

The protected side of the 48-V circuit breaker is used as a reference point for the voltage measurement circuitry.

NOTE: The absolute maximum input and gate voltage for LM5060-Q1 is 75 V at 25°C. Contact a TI representative for 100-V capable solutions.

### 3.1.3 HW Implementation

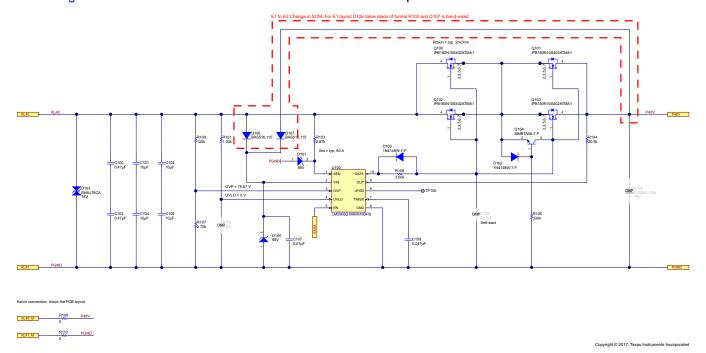

Figure 14 shows a schematic of the 48-V circuit breaker implementation.

Figure 14. 48-V Circuit Breaker Schematic

A transient voltage suppression (TVS) diode D103 and a group of capacitors C100 through C105 comprise the basic board-level input transient protection. The TVS diode is bidirectional to allow the input to withstand the reverse polarity condition. Capacitors in series reduce the probability of a short circuit in case of single capacitor failure. The minimum breakdown voltage for the diode must be over 70 V under any circumstances (tolerance, temperature drift) to avoid conducting during the E48-02 test. Capacitors are rated for 50 V. The series configuration for the capacitors increases the voltage rating by an approximate factor of 1.5 to 75 V considering the tolerance and manufacturing span.

**NOTE:** The component values have been chosen to protect the system in a laboratory environment only. Component selection for the automotive environment depends on the mechanical construction, cable length, and required criteria.

The U100 controls the Q100 through Q103 MOSFETs using an internal charge pump. Diodes D106 and D107 protect the VIN pin of the U100 in the event of reverse polarity. "OR" configuration of the diodes allow U100 operation either from the protected P48V or unprotected KL40 rail. This measure is important for the DC-DC converter turnon. Diode D106 conducts during start-up in BUCK mode from the KL40 rail. Diode D107 conducts during start-up in BOOST mode from the KL30 rail when the voltage on the KL40 rail is not present. C107 is a 100-V rated bypass capacitor. Diodes D101 and D105 are optional transient suppressors. Two resistor dividers R100, R107 and R101, R108 set the overvoltage and undervoltage threshold for U100. Undervoltage detection is not used. Transistor Q104, diode D102, and resistor R106 protect the transistor pair Q101 and Q103 from exceeding the maximum  $V_{\rm GS}$  during a reverse polarity event. If the voltage on the drains of any of the Q100, Q102 or Q101, Q103 pairs is below ground (KL41, KL31) then the transistor Q104 starts conducting, which reduces V<sub>GS</sub> to nearly zero. Resistor R106 sets the bias current through the base of Q104. Diode D102 protects the base-emitter junction of Q104 against reverse polarity during normal operation, which results in a small standby current through R106. The resistor R105 protects the GATE pin from reverse current exceeding 25 mA in the reverse polarity situation. R105 also affects the turnon and turnoff times for the Q100-Q103 pairs. For this reason, the diode D100 is used to reduce the turnoff time to the minimum. Capacitor C106 is the optional soft-start. Capacitor C108 is the timing capacitor, which sets the V<sub>DS</sub> fault detection time for U100.

Resistors R109 and R110 allow disconnecting the voltage measurement circuitry from the measurement points during development and testing.

The PCB layout that Figure 15 shows does not require any special considerations. All components are placed on the top side. Board-level input transient protection is close to the KL41 and KL40 terminals. Series-connected capacitors are 90° relative to one another. This technique is frequently used in the automotive industry to reduce the probability of simultaneous electrode cracking under mechanical stress. This technique is important because in most cases a cracked electrode of a ceramic capacitor shorts the capacitor. A hazardous situation and permanent damage of the board may occur if only a single capacitor is used or an electrode crack happens for both capacitors in series. Alternatively, capacitors with flexible SMD termination may be used. This general rule applies to all ceramic capacitors without any current-limiting element connected to the vehicle power rail.

Figure 15. 48-V Circuit Breaker PCB Layout

### 3.1.4 Test Data

See Section 6.1 for the test data.

### 3.1.5 Further Reading

See the following resources for more information:

- 1. Texas Instruments, *Automotive 12- and 24-V Battery Input Protection Reference Design*, TIDA-01167 Reference Design (TIDUC41)

- 2. Texas Instruments, Complete Front End Automotive Reverse Polarity and Series Fault Protection Reference Design, PMP10748 Reference Design (TIDUAW9)

### 3.2 48-V Filter

### 3.2.1 Description

The L-C filter on the P48V voltage rail mainly helps to reduce output ripple in the boost mode. See Table 5 for the system interface overview.

| SIGNAL  | DIRECTION | DESCRIPTION                                 |

|---------|-----------|---------------------------------------------|

| P48V    | In/Out    | Protected 48-V rail (positive - filtered)   |

| PGND    | In/Out    | Protected 48-V rail (negative)              |

| P48V NF | In/Out    | Protected 48-V rail (positive - unfiltered) |

Table 5. System Interface for 48-V Filter

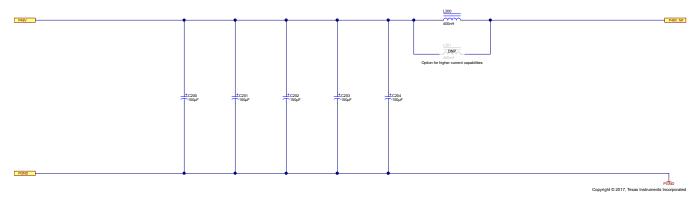

### 3.2.2 Considerations

In contrast with a typical DC-DC converter application, a battery is connected to the output of a DC-DC converter in 12-V/48-V automotive systems. This battery effectively helps to reduce output voltage ripple, especially within a low frequency range. Adding an L-C filter on the output of a boost converter helps to reduce output voltage ripple even further. Consider the following measures:

- The highest output voltage ripple occurs in single-phase operation.

- Output voltage ripple increases with a higher load.

- Capacitors must be dimensioned for the given ripple current.

- An L-C filter affects the compensation (stability) for both BUCK and BOOST mode.

- The saturation current of the inductor must be higher than the average DC current.

- Increasing the inductance for the same cutoff frequency results in a higher Q-factor and an additional dumping network may be necessary to prevent oscillations and ringing.

**NOTE:** The SPICE circuit simulator helps with identifying initial component values. Use models containing equivalent series inductance (ESL) and equivalent series resistance (ESR) for capacitors and DC resistance (DCR) for inductors. A designer can replace the power stage with an ideal current source that simulates the power inductor ripple current in continuous mode.

### 3.2.3 HW Implementation

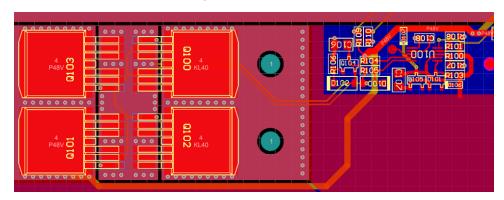

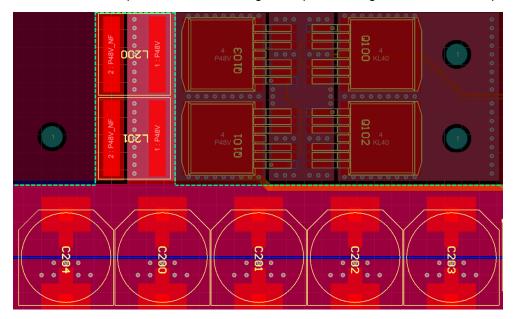

Figure 16 shows a schematic of the 48-V filter implementation.

Figure 16. 48-V Filter Schematic

The L-C filter consists of five aluminum capacitors C200 through C204 and two inductors L200 and L201. High-performance UCZ series capacitors from Nichicon are rated up to 80 V with a capacitance of 150  $\mu$ F. The ESR for these capacitors is typically 280 m $\Omega$  and a ripple current of 700 mA. Power inductors L200 and L201 are from the XAL1060 series from Coilcraft. The type of power inductors used has an 82-A saturation current and a typical DCR of 0.80 m $\Omega$ . Inductors L200 and L201 are in parallel to reduce power dissipation and provide flexibility for further optimization during development.

**NOTE:** Components used in the design are selected and optimized for a DC-DC converter operating with a resistive load in laboratory environment.

The PCB layout of the 48-V filter block in Figure 17 does not require any special attention. However, the designer should note the importance of connecting the capacitors to ground with a low impedance path.

Figure 17. 48-V Filter PCB Layout

### 3.2.4 **Test Data**

Test data for the 48-V block is not available and is a subject for future update.

### 3.2.5 **Further Reading**

See the following resources for more information:

- 1. Texas Instruments, AN-2162 Simple Success With Conducted EMI From DC-DC Converters, AN-2162 Application Report (SNVA489)

- 2. Texas Instruments, Input Filter Design for Switching Power Supplies, Application Note (SNVA489)

### 3.3 **Power Stages**

### 3.3.1 Description

As previously described, the power stages use the synchronous buck converter topology as shown in the previous Figure 6. All four power stages are identical including the PCB layout. See Table 6 for the system interface overview of a single-phase power stage.

**SIGNAL DIRECTION DESCRIPTION** In/Out P48V\_NF\_PSn (1) 48-V car battery system terminal (positive) PGND Pn (1) In/Out Power ground (negative) SW PSn (1) Out Switch node HO\_PSn (1) In High-side transistor gate LO\_PSn (1) In Low-side transistor gate CSA\_PSn (1) Out Shunt resistor current sensing - node A CSB\_PSn (1) Out Shunt resistor current sensing - node B P12V PSn (1)

Table 6. System Interface for Power Stage

Protected 12-V rail (positive)

In/Out

Where n = 1, 2, 3, 4 represents each individual phase.

### 3.3.2 Considerations

Input and output capacitor selection is affected by the bidirectional functionality. Capacitors swap their function based on the operation mode. Increasing the output capacitance reduces output voltage ripple and output voltage overshoot during a load disconnect event. However, increased output capacitance also has a negative effect on transient response time and system costs. The selection of capacitors starts with choosing the right capacitance and a sufficient ESR to fulfil the design requirements. The selection process is then followed by choosing the other important parameters such as maximum ripple current, temperature range, and voltage rating.

NOTE: Calculating current sharing (for ripple current analysis) between capacitors with different ESR and capacitance in parallel is not trivial. The SPICE circuit simulator is the most convenient tool for the circuit analysis. The same capacitors in parallel can be replaced by a single one. The total output capacitance is directly proportional and ESR is inversely proportional to the number of the same capacitors in parallel.

Finding a proper inductor for energy storage is challenging. The DC current rating must correspond to the maximum output current (BUCK) with some extra margin for the inductor ripple current. The inductor must never saturate. Inductance is selected based on the switching frequency. Smaller inductance inductors in the same package have a typically higher current rating due to a lower DCR, which results in a lower DC power loss. However, lower inductance increases ripple current and output ripple.

MOSFET transistor selection varies based on the system requirements. MOSFET transistors in the power stage negatively contribute to the total power dissipation, thus affecting the total system efficiency. The power dissipation results from conduction and switching losses. High-current MOSFET transistors with a low R<sub>DS(ON)</sub> minimize conduction losses (I<sup>2</sup>R), but typically have greater switching losses due to higher gate charges and parasitics [1]. In an ideal case, the MOSFETs are selected in such a way that the sum of conduction and switching losses is at the minimum. Various methods are available that detail how to select the optimal MOSFETs for a DC-DC converter. See The J/K Method: A Technique to Select the Optimal MOSFET for an example using the J-K method.

A snubber circuit may be necessary for damping the parasitic inductances and capacitances on the switch node during switching transitions.

A shunt resistor for current measurement must be rated to withstand the maximum ripple current through the inductor. Note the importance of using a shunt that has very low parasitic inductance and good stability over the whole temperature range. See the section titled Compensating for the Non-Ideal Current Sense Resistor in the LM5170-Q1 Multiphase Bidirectional Current Controller data sheet [2] to determine how to compensate the parasitic inductance of the shunt resistor.

### 3.3.3 **HW Implementation**

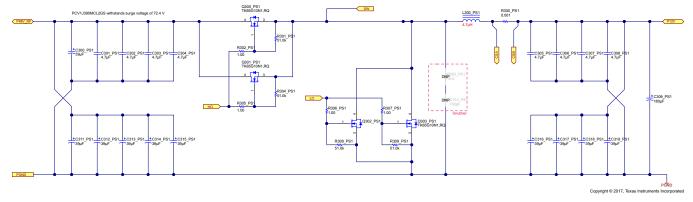

Figure 18 shows a schematic of the power stage (single phase shown).

Figure 18. Power Stage Schematic (One Phase)

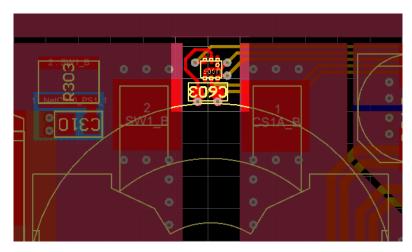

The group of small-value ceramic capacitors C301 through C304 on the 48-V side is as close to the switching node as possible. These ceramic capacitors cover small energy but very fast transients. Aluminum capacitors C300 and C311 through C315 handle low-frequency ripple and major output load changes. Capacitor groups C305 through C308, C316 through C319, and C309 serve the same purpose but on the 12-V side. All capacitors are carefully chosen to fulfill the voltage rating, ripple current rating, and temperature range. The group of 39-uF capacitors on the 48-V side are rated only to 63 V; nevertheless, their surge voltage is specified to 72.4 V for one minute, which sufficiently covers short term overvoltage cases. Power MOSFET transistors Q300 through Q303 are identical for both high side and low side. Each switch uses two 100-V rated N-FET transistors with  $R_{DS(ON)} = 3.8 \text{ m}\Omega$  (typical) in parallel. Every individual transistor gate has a separate gate resistor R302, R305, R306, or R307. This setup reflects a good engineering practice to mitigate a potential oscillation on the gate caused by a tank circuit formed from stray gate and drain inductances and gate-to-drain (Miller's) capacitance. Gate-to-source resistors R301, R304, R308, and R309 keep the respective transistor closed in case of high-impedance failure on HO and LO gate signals. L300 is a 4.7-µH inductor IHTH-1125KZ-5A (Vishay) with a specified saturation current of 52-A DC. The SER2915L-472KL from Coilcraft or the 7443640470 from Würth Elektronik can alternatively be placed on the board. The automotive-grade current sense resistor R300 is selected for a low inductance < 3 nH and a rated power up to 4 W. The optional snubber circuit R303 and C310 is not used.

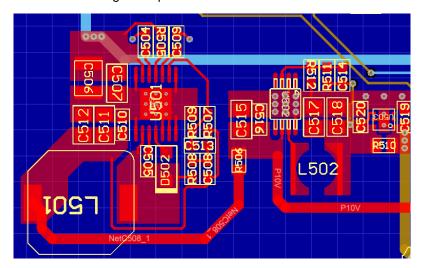

Figure 19. Power Stage (One Phase) PCB Layout

Various online articles describe PCB layout techniques for a synchronous step-down converter. This PCB layout is a trade-off between performance and single-side component placement for a relatively complex design. The desire is to keep high di/dt current paths as short as possible to reduce electromagnetic interference (EMI). Small capacitors are always the part of the shortest current return path, close to the switch node.

Routing the gate driver signals and current sensing signals to the optimal length is not possible due to the single-side component placement. Gate driver signals use 30-mil wide traces and current sense signals use 10-mil wide traces. These signals are routed differentially to reduce stray inductance as much as possible. An I<sup>2</sup>C temperature sensor for each power stage is located in close proximity to the inductor with the digital ground routed separately. High current traces are supported by copper bus bars on the top and bottom side of the PCB.

### 3.3.4 Test Data

See Section 6.2 for the test data.

### 3.3.5 Further Reading

See the following resources for more information:

- 1. Texas Instruments, *Understanding Buck Power Stages in Switchmode Power Supplies*, Application Report (SLVA057)

- 2. Texas Instruments, *Understanding Boost Power Stages in Switchmode Power Supplies*, Application Report (SLVA061)

- 3. Lynch, Brian T.; *Under the Hood of a DC/DC Boost Converter*, Seminar Topic 3 (http://www.ti.com/download/trng/docs/seminar/Topic\_3\_Lynch.pdf)

- 4. Lynch, Brian T.; Hesse, Kurt; Under the Hood of Low-Voltage DC/DC converters, Seminar

(http://application-notes.digchip.com/001/1-2958.pdf)

Powerelectronics.com, Miller, James; The J/K Method: A Technique to Select the Optimal MOSFET, Power Electronics Online Article (http://www.powerelectronics.com/dc-dc-converters/jk-method-technique-select-optimal-mosfet)

6. Texas Instruments, Taylor, Robert; Manack, Ryan; Controlling switch-node ringing in synchronous buck converters, Power Management Technical Brief (SLYT465)

### 3.4 12-V Circuit Breaker

### 3.4.1 Description

The 12-V circuit breaker protects the DC-DC converter against reverse polarity and allows disconnecting the circuitry from the 12-V battery in case of a failure or to prevent current consumption when the system is switched off. The functionality is the same as the 48-V circuit breaker except the 12-V circuit breaker has a reverse polarity protection requirement. See Table 7 for a system interface overview.

| SIGNAL    | DIRECTION | DESCRIPTION                                                                                                   |

|-----------|-----------|---------------------------------------------------------------------------------------------------------------|

| KL30_BIAS | Out       | Bias voltage rail for pre-boost circuitry                                                                     |

| KL30_POL  | Out       | Polarity detection for the 12-V battery                                                                       |

| P12V      | In/Out    | Protected 12-V rail (positive)                                                                                |

| PGND      | In/Out    | Protected 12-V rail (negative)                                                                                |

| EN12      | In        | Enable signal; voltage greater than 2.0 V enables the circuit breaker; optimized for 3.3-V/ 5-V logic signals |

| BRKG      | In        | Gate signal for the circuit breaker MOSFETs                                                                   |

| BRKS      | In        | Source signal for the circuit breaker MOSFETs                                                                 |

| KL30      | In/Out    | 12-V car battery system terminal (positive)                                                                   |

| KL31      | In/Out    | 12-V car battery system terminal (negative)                                                                   |

| KL30_M    | Out       | 12-V battery four-wire voltage measurement terminal (positive)                                                |

| KL31_M    | Out       | 12-V battery four-wire voltage measurement terminal (negative)                                                |

Table 7. System Interface for 12-V Circuit Breaker

### 3.4.2 Considerations

The DC-DC converter is disconnected from both power rails when the system is off. This setup ultimately requires an external impulse to the system to initiate device start-up. This impulse can either be the EN12 or EN48 signal. The circuit breaker on the 12-V side is controlled by the LM5170-Q1 controllers. The controllers do not contain any internal charge pump for the circuit breaker MOSFET transistors. Voltage on the HV-port must be at least 10-V higher than on the LV-port (KL30) to allow these N-MOSFET transistors to operate in the linear (ohmic) region as a switch. A back-to-back configuration of very low  $R_{DS(ON)}$  MOSFET transistors must be used similarly to the 48-V circuit breaker. A simple pre-boost circuit is connected to the 12-V battery terminal (KL31) to bypass the 12-V circuit breaker and enable DC-DC start-up from the 12-V side.

Per industry expectations, the 12-V battery in a vehicle is user accessible. For this reason, a reverse polarity condition may occur. The system must detect this condition and force the 12-V circuit breaker off in case this situation arises. Opening the 12-V circuit breaker during a reverse polarity condition results in excessive current flowing through the substrate diode of the low MOSFET and the inductor in the power stage, which causes immediate damage of the system.

The protected side of the 12-V circuit breaker is used as a reference point for the voltage measurement circuitry.

# 3.4.3 HW Implementation

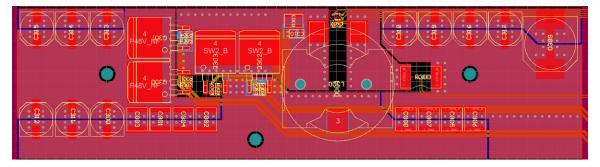

Figure 20 shows a schematic of the 12-V circuit breaker.

Figure 20. 12-V Circuit Breaker Schematic

The circuit breaker uses back-to-back configuration of N-MOSFET transistors Q402 through Q406 in parallel. Resistor R404 prevents opening transistors in the case of high impedance on the BRKG and BRKS signals. C404 is an optional soft-start capacitor. Capacitors C400 through C403 and TVS diodes D402 and D403 form a basic input transient protection. RV400 is a placeholder for an optional metal oxide varistor (MOV), which is used for further transient suppression.

A P-MOSFET transistor Q400 is used for bypassing the 12-V circuit breaker for the pre-boost circuit. Current for the pre-boost circuit is relatively low, so a cheap P-MOSFET transistor is sufficient. Resistor R400 helps to close Q400. Diode D401 protects the gate-source junction of Q400 against excessive  $V_{\rm GS}$  voltage. Resistors R402 and R403 set bias for a transistor-based inverter Q401. Resistor R401 limits current when the Zener diode D401 starts opening due to short term overvoltage. Diode D400 is a reverse polarity protection for the pre-boost circuitry. Voltage drop on D400 is negligible and only applies when the pre-boost operates during system start-up from the 12-V battery. The node between D400 and Q400 is used by the diagnostic block for reverse polarity detection on the 12-V side.

Resistors R109 and R110 allow disconnecting the voltage measurement circuitry from the measurement points during development and testing.

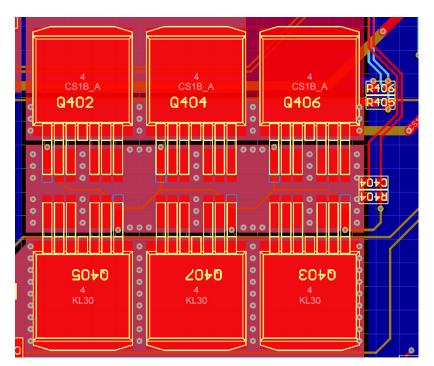

Figure 21 shows a PCB layout of the 12-V circuit breaker. The input transient protection PCB layout is similar to that of the 48-V circuit breaker. The bypass circuitry is in close proximity to the pre-boost converter. High current traces are supported by copper bus bars on the top side and bottom side of the PCB.

Figure 21. 12-V Circuit Breaker PCB Layout

### 3.4.4 **Test Data**

See Section 6.3 for test data.

### 3.5 LM5170-Q1 Subsystem

### 3.5.1 **Description**

The system uses two LM5170-Q1 subsystems for a current feedback loop: subsystem A or \_LM1, subsystem B or \_LM2. See the LM5170-Q1 data sheet [2] for a detailed theory of operation of the LM5170-Q1. Table 8 shows the system interface for both LM5170-Q1 subsystems.

NOTE: The PCB layout and the netlist for both LM5170-Q1 subsystems are identical. Signals SYNCIN and SYNCOUT are used for synchronization.

Table 8. System Interface for LM5170-Q1 Subsystem

| SIGNAL           | DIRECTION | DESCRIPTION                                                     |

|------------------|-----------|-----------------------------------------------------------------|

| P10V_LMn         | In        | +10-V bias supply for LM5170-Q1                                 |

| AGND_LM <i>n</i> | _         | Common analog ground                                            |

| SYNCOUT_LMn      | Out       | Clock synchronization (output)                                  |

| ISETD_LMn        | In        | Current programming (PWM with variable duty cycle: 3.3-V logic) |

| VIN_LMn          | In        | HV-port (P48V) voltage (positive)                               |

| UVLO_LM <i>n</i> | In        | Master enable                                                   |

| EN1_LMn          | In        | Channel 1 enable                                                |

| DIR_LMn          | In        | Direction command (buck/boost)                                  |

| SYNCIN_LMn       | In        | Clock synchronization (input)                                   |

| OPT_LM <i>n</i>  | In        | Multiphase configuration (sets phase lag of the SYNCOUT)        |

Table 8. System Interface for LM5170-Q1 Subsystem (continued)

| SIGNAL                                               | DIRECTION | DESCRIPTION                            |

|------------------------------------------------------|-----------|----------------------------------------|

| EN2_LMn                                              | In        | Channel 2 enable                       |

| NFAULT_LMn                                           | In/Out    | Fault flag (internal pullup to 5 V)    |

| IOUT1_LMn                                            | Out       | Channel 1 current monitor output       |

| IOUT2_LMn                                            | Out       | Channel 2 current monitor output       |

| BRKS_LMn                                             | Out       | 12-V circuit breaker common SOURCE pin |

| BRKG_LMn                                             | Out       | 12-V circuit breaker common GATE pin   |

| CS1A_LMn                                             | In        | Current sensing channel 1 – node A     |

| CS1B_LMn                                             | In        | Current sensing channel 1 – node B     |

| SW1_LMn                                              | In        | Switch node channel 1                  |

| SW2_LMn                                              | In        | Switch node channel 2                  |

| CS2A_LMn                                             | In        | Current sensing channel 2 – node A     |

| CS2B_LMn                                             | In        | Current sensing channel 2 – node B     |

| HO1_LMn                                              | Out       | High-side transistor gate – channel 1  |

| LO1_LMn                                              | Out       | Low-side transistor gate – channel 1   |

| HO2_LMn                                              | Out       | High-side transistor gate – channel 2  |

| LO2_LMn                                              | Out       | Low-side transistor gate – channel 2   |

| where $n = 1,2$ represents each individual subsystem |           |                                        |

### 3.5.2 Considerations

Consider the following when selecting a controller for a 12-V/48-V automotive bidirectional DC-DC converter:

- Isolated or non-isolated topology

- Bidirectional operation

- Multiphase operation and synchronization

- Current sharing between phases

- Design scalability

- · Digital, analog, or hybrid control loop

- · Interfacing with the host microcontroller or system

- · Protection mechanisms

- · Level of integration and automotive qualification

The LM5170-Q1 is the most straightforward and highly-integrated solution for the 12-V/48-V non-isolated bidirectional DC-DC converter.

# 3.5.3 HW Implementation

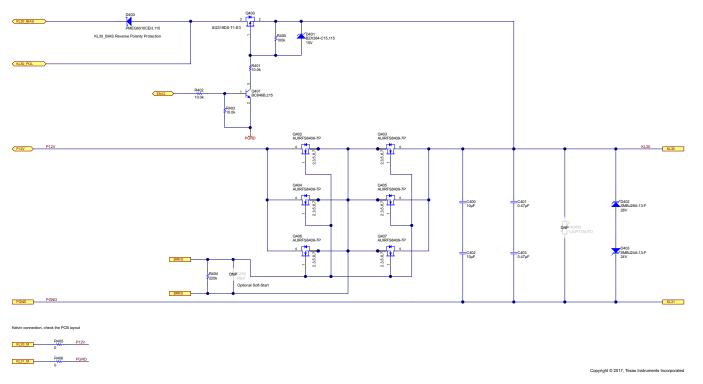

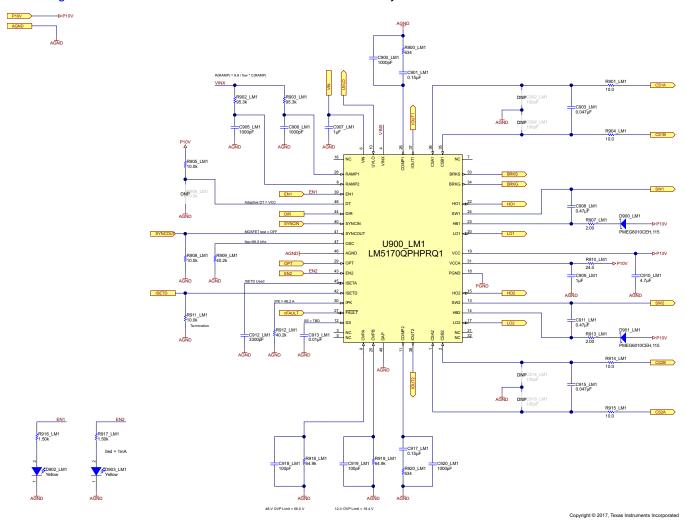

Figure 22 shows a schematic of the first LM5170-Q1 subsystem.

Figure 22. LM5170-Q1 Subsystem Schematic (Subsystem 1)

RC circuits R902, R903 and C905, and C906 are a part of the ramp generator. C907 is a bypass capacitor for the HV-input pin, which is rated up to 100 V. C910 is a bypass capacitor for the bias supply. The analog bias supply 10 V is decoupled by the RC filter R910, C909. Component groups C900, C901, R900 and C917, C920, and R920 are current-loop compensation networks for each channel, respectively. Resistors R918 and R918 set the overvoltage protection voltage threshold for the OVPA and OVPB pins. Small 100-pF capacitors C918 and C919 reduce the noise on the pins. A 10-k pulldown resistor R908 on the SYNCOUT pin disables the internal MOSFET fault check circuitry.

**NOTE:** The MOSFET fault check is disabled due to high capacitance on P48V and P12V. Enabling this functionality may cause false fault reporting during LM5170-Q1 start-up.

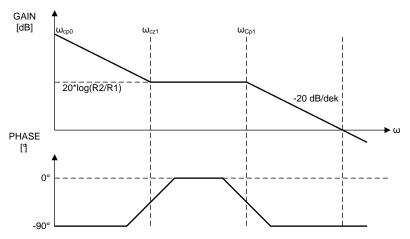

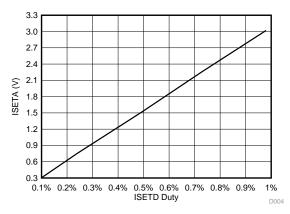

Resistor R909 sets the switching frequency to approximately 100 kHz. The ISETD pin is used for current regulation. Pulldown resistor R911 defines the ISETD logic level when the output pins of the MCU are in a high-z state (reset). Capacitor C912 on the ISETA pin forms a low-pass filter, which converts the PWM signal from the ISETD pin to an analog voltage proportional to the duty cycle. Proper selection of this capacitor depends on the PWM for the ISETD pin and is critical for voltage loop stability. A higher capacitance adds delay to the control loop. A smaller capacitance increases voltage ripple on the ISETA pin due to a higher cutoff frequency of the RC filter.

A 10-k pullup resistor R905 sets the internal adaptive dead-time control between the high-side and low-side driver. Resistor R906 is a placeholder for the fixed dead-time settings. Resistor R912 programs the threshold for the cycle-by-cycle current limit comparator. Capacitor C913 defines soft-start time.

Component groups R901, R904, C903, C902, C904 and R914, R915, C915, C914, and C916 compensate parasitic inductance of the sense resistor. Components C908, R907, D900 and R911, R913, and R901 are bootstrap circuits for high-side MOSFET drivers.

Channel activity is visualized by LEDs D902 and D903 connected to EN1 and EN2 signals. Resistors R916 and R917 set the current through the LEDs to approximately 1 mA.

**NOTE:** Always refer to the latest revision of a data sheet for proper component selection. The LM5170-Q1 data sheet contains detailed design procedure beginning in the section titled *Design Requirements* [2].

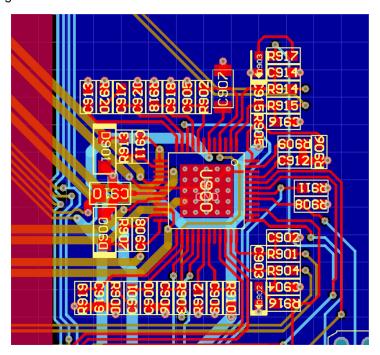

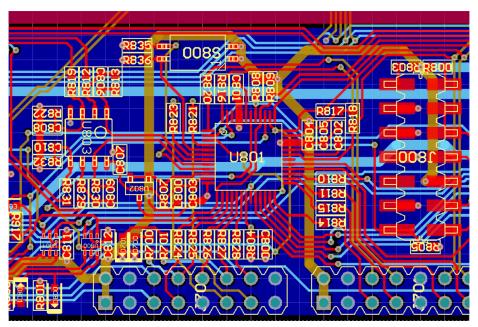

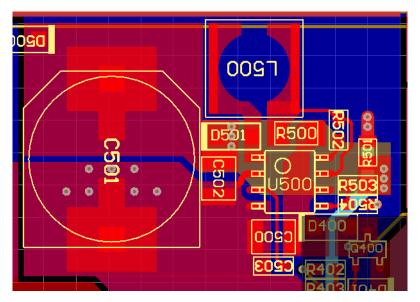

Figure 23 shows a PCB layout of the LM5170-Q1 subsystem. All components are placed in close proximity to the LM5170-Q1 on the top side of the PCB. The thermal pad is a reference point where analog and power ground meet.

Figure 23. LM5170-Q1 Subsystem PCB Layout

### 3.5.4 Test Data

See Section 6.4 for the test data.

### 3.5.5 Further Reading

See the following resources for more information:

- Texas Instruments, Interconnecting automotive 48V and 12V rails in dual-battery systems,

TI E2E™ Online Community Forum Behind the Wheel; March 2017

(https://e2e.ti.com/blogs\_/b/behind\_the\_wheel/archive/2017/03/20/how-to-connect-dual-automotive-battery-systems-)

- Texas Instruments, Selecting a bidirectional converter control scheme,

TI E2E™ Online Community Forum Power House; March 2017

(https://e2e.ti.com/blogs\_/b/powerhouse/archive/2017/03/20/select-a-bidirectional-converter-control-scheme)

# 3.6 C2000™ MCU

# 3.6.1 Description

The C2000 MCU block, based on TMS320F28027F, is responsible for the outer voltage feedback loop, interfacing with LM5170-Q1 devices, and communication with the host system when applicable. See Table 9 for a system interface overview of the C2000 MCU block.

Table 9. System Interface for C2000™ Control MCU

| SIGNAL   | DIRECTION | DESCRIPTION                                                          |

|----------|-----------|----------------------------------------------------------------------|

| P3V3     | In        | +3.3-V bias supply                                                   |

| KL30_M   | In        | 12-V battery four-wire voltage measurement terminal (positive)       |

| KL31_M   | In        | 12-V battery four-wire voltage measurement terminal (negative)       |

| KL41_M   | In        | 48-V battery four-wire voltage measurement terminal (positive)       |

| KL40_M   | In        | 48-V battery four-wire voltage measurement terminal (negative)       |

| ADCINA6  | In/Out    | General purpose analog input or digital input/output                 |

| ADCINA7  | In/Out    | General purpose analog input                                         |

| ADCINB1  | In/Out    | General purpose analog input                                         |

| ADCINB2  | In/Out    | General purpose analog input or digital input/output                 |

| ADCINB3  | In/Out    | General purpose analog input                                         |

| ADCINB4  | In/Out    | General purpose analog input or digital input/output                 |

| ADCINB6  | In/Out    | General purpose analog input or digital input/output                 |

| SIMO     | In/Out    | SPI slave in, master out (unused)                                    |

| SOMI     | In/Out    | SPI slave in, master out (unused)                                    |

| CLK      | In/Out    | SPI clock (unused)                                                   |

| STEA     | In/Out    | SPI chip select (unused)                                             |

| TXD      | Out       | Serial Communications Interface (SCI) transmit                       |

| RXD      | In        | Serial Communications Interface (SCI) receive                        |

| EN1_A    | Out       | Power Stage 1 Enable (LM5170-Q1 subsystem A, EN1)                    |

| EN2_A    | Out       | Power Stage 2 Enable (LM5170-Q1 subsystem A, EN2)                    |

| EN1_B    | Out       | Power Stage 3 Enable (LM5170-Q1 subsystem B, EN1)                    |

| EN2_B    | Out       | Power Stage 4 Enable (LM5170-Q1 subsystem B, EN2)                    |

| OPT      | Out       | Multiphase configuration (sets phase lag of the SYNCOUT)             |

| DIR      | Out       | Direction command (buck/boost)                                       |

| ISETD    | Out       | Current programming (PWM with variable duty cycle: 3.3-V logic)      |

| IMON     | ln        | Sum of phase-current monitor currents from both LM5170-Q1 subsystems |

| nFAULT   | In        | LM5170-Q1 subsystem fault detection monitor                          |

| SDA      | In/Out    | I <sup>2</sup> C bus data                                            |

| SCL      | Out       | I <sup>2</sup> C bus clock                                           |

| nRST     | In        | Microcontroller reset                                                |

| UVLO     | In/Out    | UVLO monitoring and open-collector output                            |

| WDT_TRIG | Out       | External watchdog timer trigger                                      |

| GND      | _         | Common ground                                                        |

### 3.6.2 Considerations

MCU selection for this hybrid DC-DC converter, which combines the analog circuitry of LM5170-Q1 and the digital control for the outer voltage feedback loop, depends on several factors. In general, the batteries on 12-V and 48-V rails represent large energy storage with low internal resistance. These battery qualities free the external voltage loop from the requirement to handle ultra-fast transients known from other multiphase converters (processor power, for example). This configuration reduces the demand on MCU computing and peripherals performance. In theory, the lowest-cost MCU with a PWM for the ISETD pin and ADC periphery for voltage measurements can be used for a digital voltage feedback loop as long as the transient response is sufficient for the given system requirements. The transient response of the system corresponds to the refresh-rate of the PWM for the ISETD pin. During this period the MCU must sample voltages on the ADC pins and calculate the new PWM duty cycle.

A difference amplifier is used for four-wire voltage measurements. This solution improves load regulation. The operational amplifier must be capable of input and output rail-to-rail operation resulting from sensing close to ground, single-supply, and interfacing with the unipolar-input ADC. The voltage control loop does not require any current measurement. Current monitoring in TIDA-01168 is used only for approximate indication. An operational amplifier configured as a current-to-voltage converter is recommended whenever more precise current measurements are required.

### 3.6.3 HW Implementation

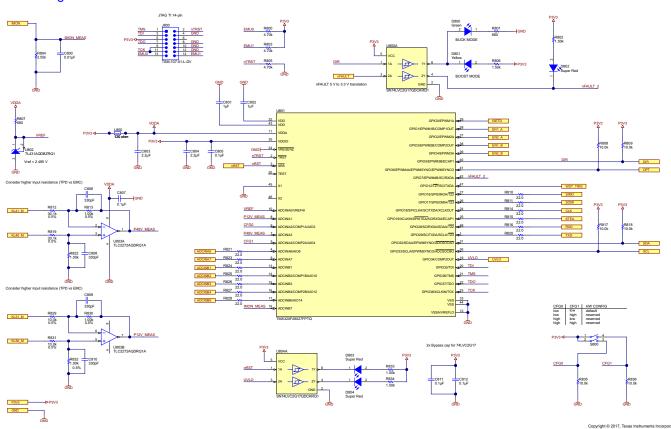

Figure 24 shows a schematic of the C2000™ Control MCU.

Figure 24. C2000™ Control MCU Schematic

The LM5170-Q1 current monitors have a current source output proportional to the current through the inductor of each respective channel. All monitor outputs are conceded together, thus the IMON signal represents the sum of currents through all phases. Resistor R804 in parallel with capacitor C800 is a simple current-to-voltage converter with a low-pass filter. The output is connected directly to the ADC. Voltage measurement is based on a dual operational amplifier U803. The operational amplifier is configured as a difference amplifier. Resistors R812, R813, R819, R822 and R829, R830, R831, and

R832 set the gain for each channel. Resistors R812 and R819 must be rated up to 100 V in this application, which requires sensing up to 70 V. Capacitors C806 and C808 through C8010 set the cutoff frequency of the low-pass filter. Using the same capacitance of these capacitors is important. Any asymmetry affects the common-mode rejection ratio. Output of the operational amplifier goes directly to the ADC.

NOTE: TI recommends to place an RC circuit between the output of the operational amplifier and the input of the ADC. This circuit improves the load response of the operational amplifier. The recommenced values are a 1- $\Omega$  to 20- $\Omega$  resistor and 10-100 pF capacitor.

The TL431-Q1 shunt regulator U802 and biasing resistor R807 provide a stable reference voltage for the ADC. Lossy ferrite bead L800 and the capacitor C803 isolate the analog power supply from the digital power supply rail. Capacitors C801 through C805 are bypassing capacitors for digital power pins and internal voltage regulators of the MCU.

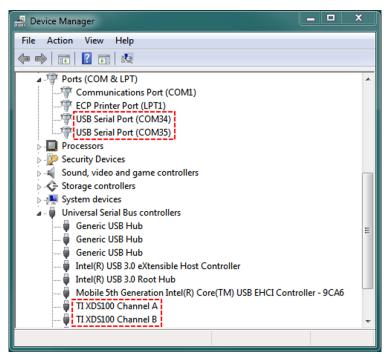

The TMS320F28027F MCU is the smallest member from the C2000 real-time control MCU family. The microcontroller uses the internal 10-MHz oscillator as a clock source.

The 14-pin header connector J800 and resistors R800, R803, and R805 are required for the XDS100compatible Joint Test Action Group (JTAG) interface. Logic gates U800 and U804 with bypass capacitors C811 and C812 drive LEDs D800 through D804. U800A does logic-level translation for the NFAULT signal from the LM5170-Q1. Resistors R801, R802, R806, R833, and R834 set the current through the LEDs to approximately 1 mA. The group of 22-Ω resistors is for the MCU interface. One common habit is to place a 22-Ω series termination for signals interfaced outside the PCB board. Resistors R808 and R809 are DIR and OPT signal pullup resistors for the LM5170-Q1. Resistors R817 and R818 are pullup resistors for the I<sup>2</sup>C bus. The exact value of I<sup>2</sup>C pullup resistors depends on the clock speed, number of devices connected on the bus (parasitic capacitance), and bus length. I<sup>2</sup>C temperature sensors are located in the power stage areas. High currents resulting in strong magnetic fields couple a lot of impulse noise to I<sup>2</sup>C signals. When debugging I<sup>2</sup>C communication, this noise must be taken into account and active operation when all four phases are enabled is recommended.

Switch S800 and resistors R835 and R36 are reserved for firmware configuration. The current firmware v1.0 does not support this feature.

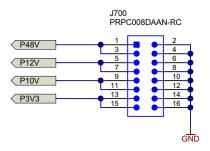

The PCB layout of the C2000 control MCU block does not have any special requirements except for the analog circuitry. See Figure 25 for the PCB layout.

Figure 25. C2000™ Control MCU PCB Layout

### 3.6.4 Test Data

See Section 6.4 for the test data.

### 3.6.5 Further Reading

See the following resources for more information:

Texas Instruments, C2000™ Real-Time Microcontrollers, C2000 MCU Brochure (SPRB176AD)

# 3.7 Diagnostics

### 3.7.1 Description

The diagnostic block in TIDA-01168 monitors phase temperatures, MCU activity, reverse polarity condition on the 12-V rail, and bias voltages for the MCU and LM5170-Q1 subsystems. See Table 10 for a system interface overview of the diagnostic block.

| SIGNAL   | DIRECTION  | DESCRIPTION                             |

|----------|------------|-----------------------------------------|

|          | BIRLEGIION |                                         |

| P3V3     | In         | +3.3-V bias supply                      |

| GND      | _          | Common ground                           |

| SDA      | In/Out     | I <sup>2</sup> C bus data               |

| SCL      | In         | I <sup>2</sup> C bus clock              |

| KL30_POL | In         | Polarity detection for the 12-V battery |

| nRST     | Out        | MCU reset                               |

| nSHDN    | Out        | Emergency shutdown for LM5170-Q1s       |

| WDT_TRIG | In         | External watchdog timer trigger         |

Table 10. System Interface for Diagnostic Block

### 3.7.2 Considerations

A basic set of diagnostic features and bias supply failure detection are beneficial even in a design intended for laboratory use. Temperature sensors monitor each power phase and react to overtemperature events independently of the control MCU. External reset circuitry with a watchdog timer is often used in systems controlled by an MCU. In the event that the MCU does not react (locks up), for example, due to a software bug or a control flow error, the watchdog timer shuts down the complete system and keeps it in a safe state. An integrated watchdog timer in the MCU can also be used if the provided level of robustness is sufficient. External watchdog circuit ICs are usually combined with voltage supervisor functionality, which make them a very robust solution. Systems with ASIL requirements often use a system basis chip (SBC). The SBC integrates even more functionality in a single chip, for example low-dropout regulators (LDOs), voltage supervisors, CAN and LIN interfaces, or wake-up signals.

Monitoring bias voltages for the MCU and LM5170-Q1 subsystems is important to ensure that all integrated circuits operate only within the specified operating voltage range. Operating within the specified operating range is important, especially during system start-up when all devices should be kept in reset or standby mode until the bias voltages reach the preset value.

### 3.7.3 HW Implementation

Figure 26 shows a schematic of the diagnostics.

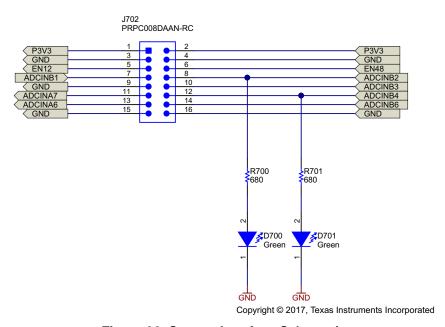

Figure 26. Diagnostics Schematic

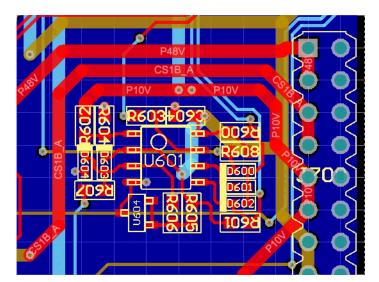

U600, U602, U603, and U605 are TMP102-Q1 temperature sensors interfaced over an I<sup>2</sup>C bus. The biggest benefit of these senors is the ALERT open-collector output. The temperature sensor allows the designer to set a custom overtemperature threshold in the way that the ALERT output is set low when temperature reaches the threshold. All ALERT outputs are connected together to the OVERTEMP signal. Resistor R608 is a pullup resistor and does not have a critical value. Capacitors C600 through C603 are bypass capacitors for TMP102-Q1 temperature sensors. The external watchdog and voltage supervisor U601 is TPS3306-33, which monitors 3.3-V and 10-V power supplies for the MCU and LM5170-Q1 devices (see Figure 27). Resistor dividers R602 and R604 set the undervoltage threshold for the 10-V power rail. Capacitor C604 is a bypass capacitor.

A special circuitry checks the reverse polarity condition on the 12-V battery terminal (KL31). Shunt regulator U604 along with resistor R605 provide a stable nominal voltage of 2.495 V. Resistors R606 and R607 are a resistor divider. The power fail input (PFI) of U601 senses the output of the divider. If the voltage on KL30\_POL is slightly negative, the voltage on the PFI is below the threshold and the power fail output (PFO) signal is low. The PFO signal, overtemperature, and reset signal are logically connected together by diodes D600 through D602. Diodes D603 and D604 protect the PFI input. If any of the signals are low, the emergency shutdown signal nSHDN switches off the LM5170-Q1 devices. The emergency shutdown also immediately disconnects the 12-V circuit breaker or prevents turning it on during a reverse polarity condition in the 12-V battery terminal. Removing the resistor R603 allows disabling the watchdog timer during development and MCU programming.

The PCB layout of the diag block is fairly simple. The I<sup>2</sup>C temperature sensors are located in the power section. Wiring separate power for the sensors is important. Do not ground the sensors locally to the power ground. See Figure 28 for further details.

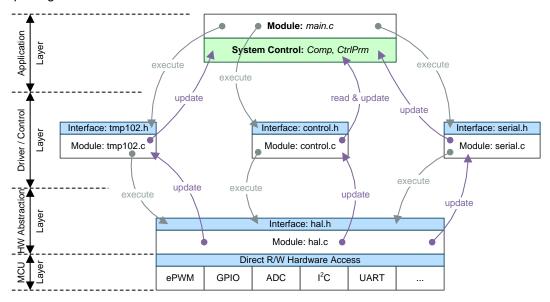

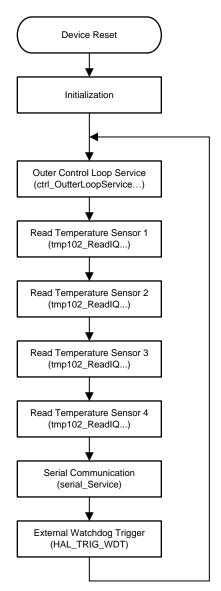

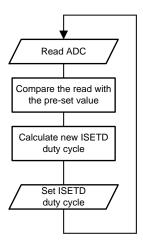

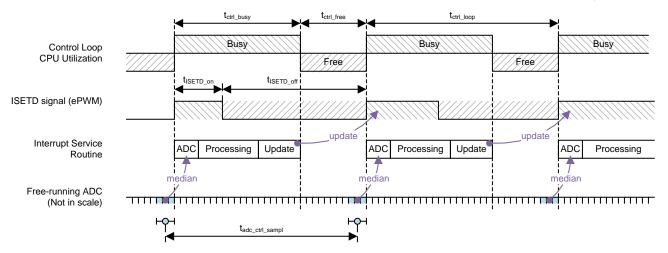

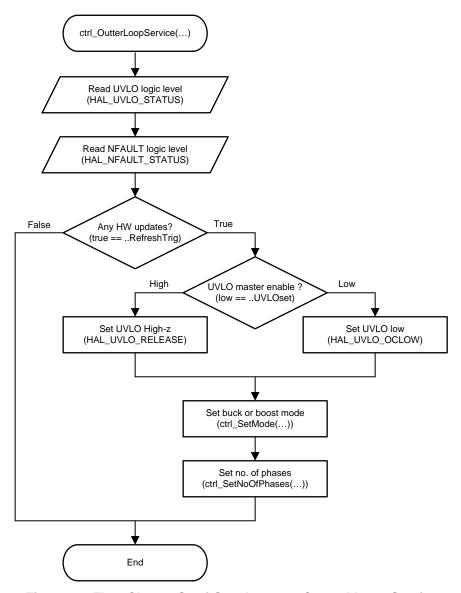

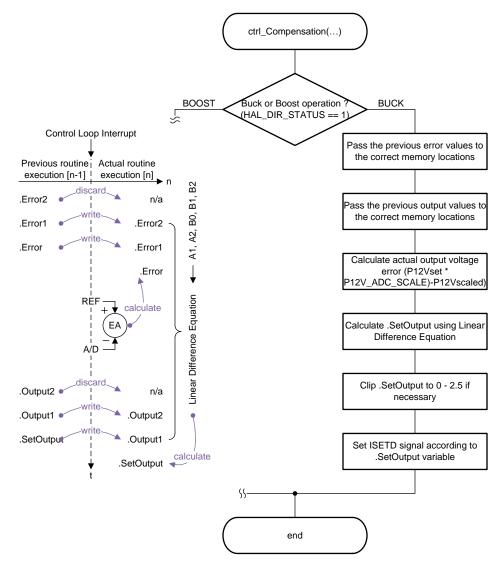

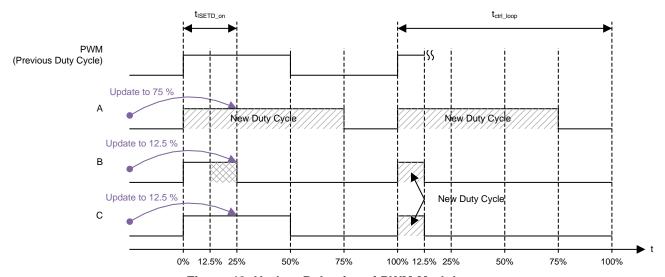

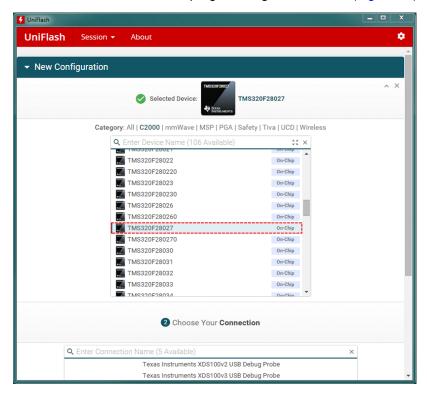

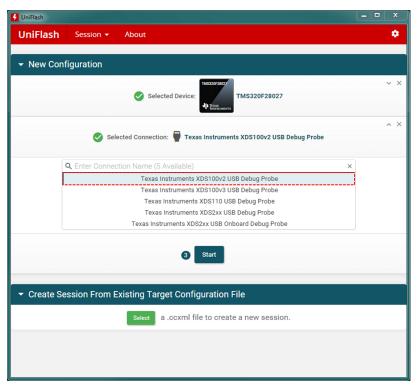

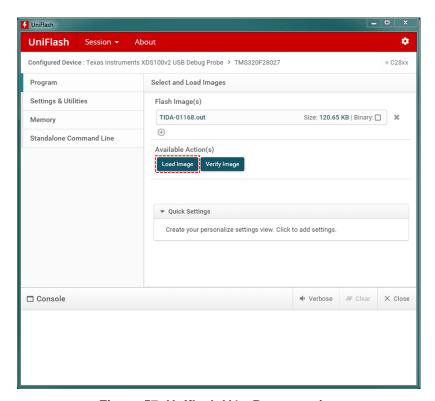

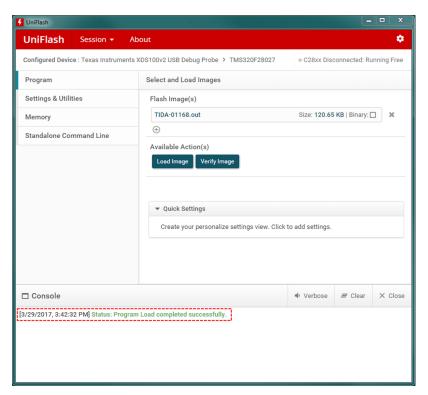

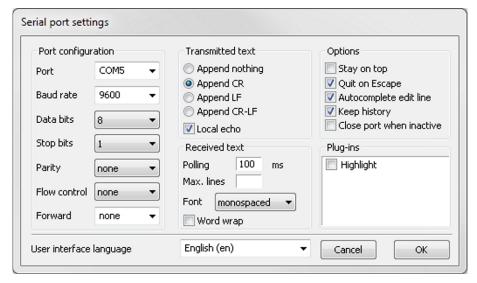

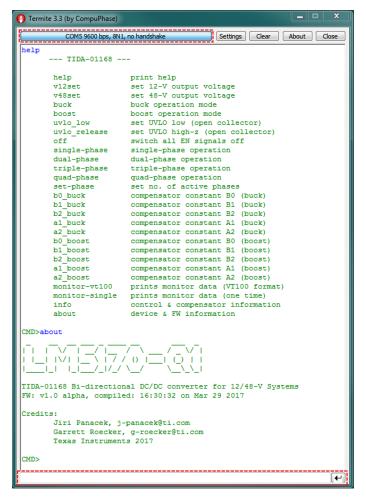

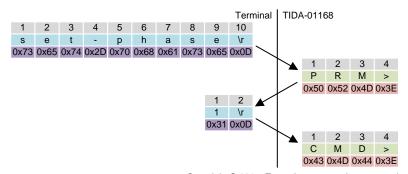

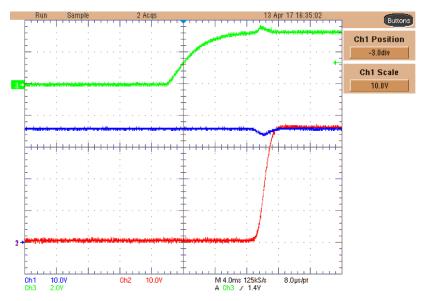

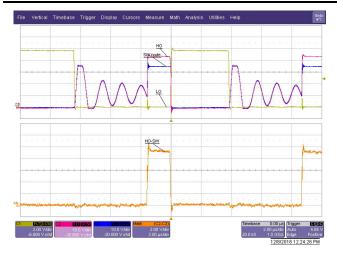

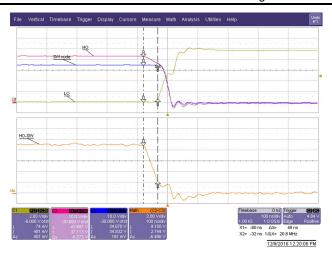

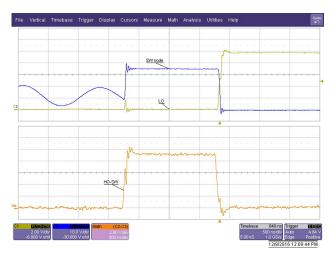

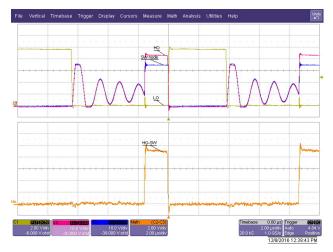

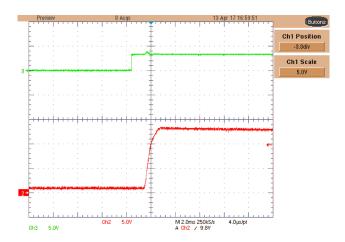

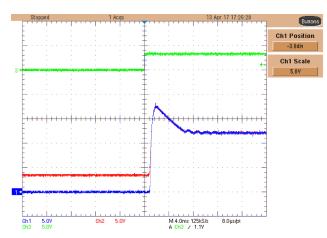

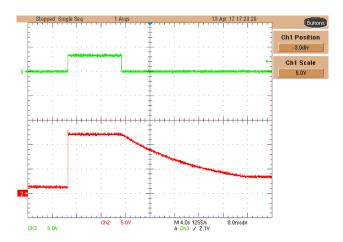

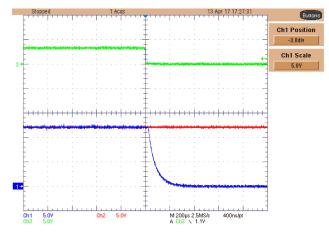

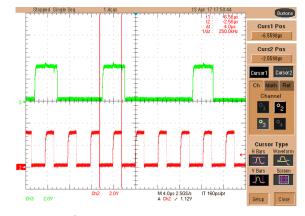

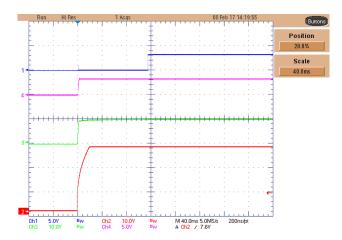

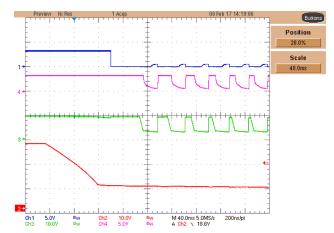

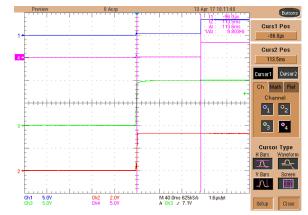

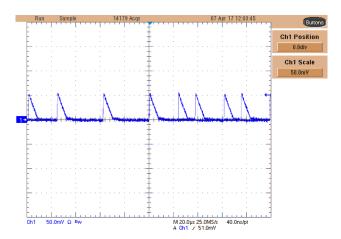

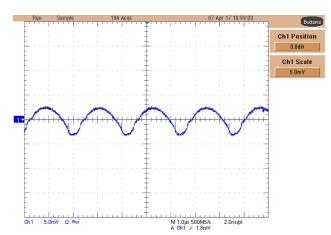

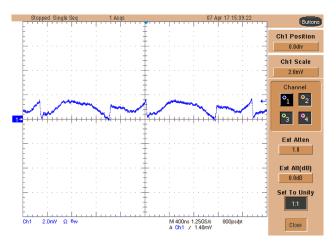

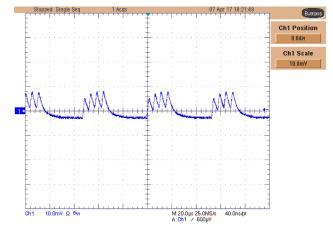

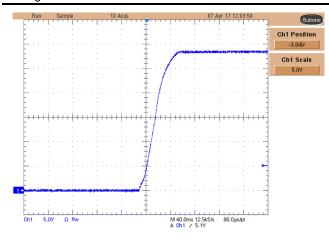

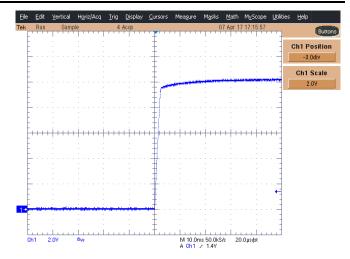

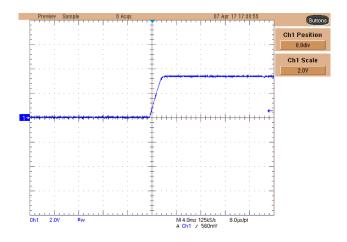

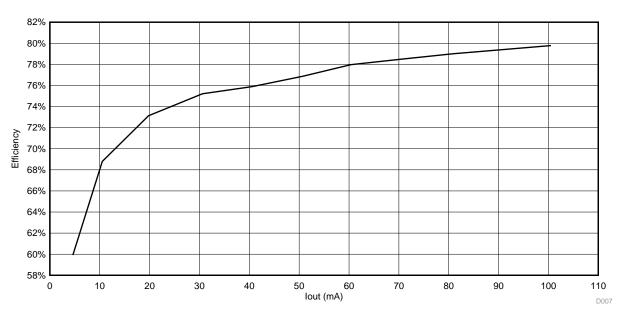

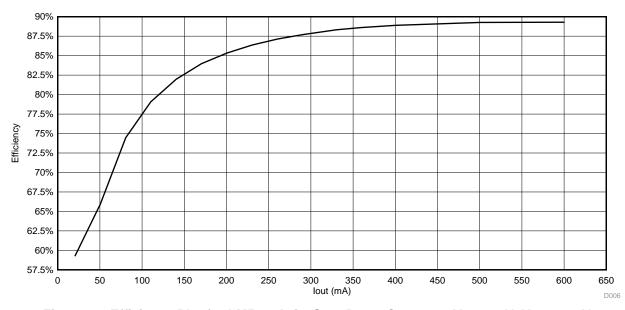

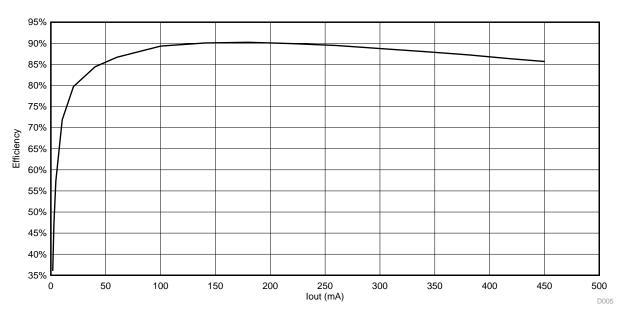

Figure 27. Diag PCB Layout—External Watchdog and Voltage Supervisor