# Design Guide: TIDA-010054 Bidirectional, Dual Active Bridge Reference Design for Level 3 Electric Vehicle Charging Stations

# Description

This reference design provides an overview on the implementation of a single-phase Dual Active Bridge (DAB) DC/DC converter. DAB topology offers advantages like soft-switching commutations, a decreased number of devices and high efficiency. The design is beneficial where power density, cost, weight, galvanic isolation, high-voltage conversion ratio, and reliability are critical factors, making this design an excellent choice for EV charging stations and energy storage applications. Modularity and symmetrical structure in the DAB allow for stacking converters to achieve high power throughput and facilitate a bidirectional mode of operation to support battery charging and discharging applications.

#### Resources

| TIDA-010054                    | Design Folder  |

|--------------------------------|----------------|

| UCC21710, UCC14141-Q1, AMC1311 | Product Folder |

| AMC1306M05, AMC1336, AMC1302   | Product Folder |

| TPS2640, TLVM13620, TMCS1133   | Product Folder |

| TPS7A20, TLV760                | Product Folder |

| TMS320F280039                  | Product Folder |

Ask our TI E2E<sup>™</sup> support experts

# Features

- Bidirectional dual-active-bridge with Single- (SPS) and Extended-phase-shift (EPS) control

- Smart Gate driver UCC21710 providing integrated protection for SiC MOSFETs

- TMS320F280039 controller for implementation of digital control

- Isolated voltage and current sensing

- Maximum power output of 10 kW

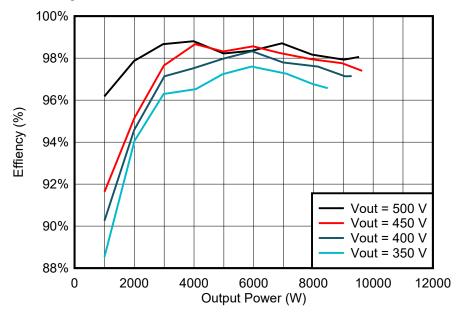

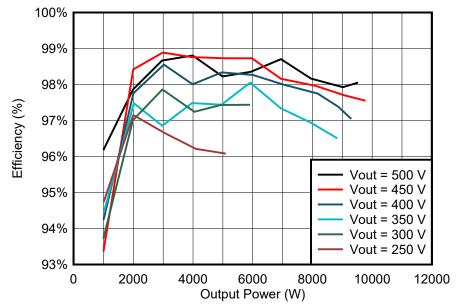

- Achieves peak efficiency 98.7%, full load efficiency – 98%

- Primary voltage of 700V–800V DC, secondary voltage of 350V – 500 V DC (SPS) 250V–500V (EPS)

- PWM switching frequency of 100 kHz and reduced transformer size enabled by planar magnetics

- Soft switching without auxiliary components

# Applications

- DC fast charging station

- DC fast charging power module

- Power conversion system (PCS)

- Hybrid, electric and powertrain systems

1

# **1 System Description**

The electric vehicle charging standards governed by the Combined Charging System and CHAdeMO<sup>®</sup> are constantly changing and are pushing for faster battery charging rates requiring typically less than 30 minutes spent at a charging station for one full charge of an electric vehicle. The DC charging station is typically a Level 3 charger which can cater to a very high power level between 120–240 kW. These DC charging stations are standalone units which house AC/DC and DC/DC power conversion stages. A number of power conversion modules are stacked together inside of a charging station to increase the power levels and enable fast charging. DC fast-charging stations provide a high power DC current to an electric vehicle's battery without passing through any onboard AC/DC converter, which means the current is connected directly to the battery. Most cars on the road today can handle only up to 50 kW. Newer cars have the ability to charge at greater rates of power. As EVs come with higher range and batteries get bigger, DC charging solutions are being developed to support long-range EV batteries through fast charging stations up to 250 kW or more.

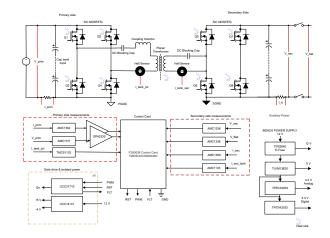

The DC/DC converter in a charging station must be capable of interfacing with the rectified bus voltage (700–800 V) from a three-phase Vienna rectifier at the input and connect with the battery of an electric vehicle at the output, delivering rated power. The DC/DC converter finds important application in a number of end equipment. Figure 1-1 shows the use in charging stations, solar photovoltaic systems, energy storage systems, and electric vehicle traction applications.

Figure 1-1. Role of DC/DC Converter

The DC/DC converter must be capable of handling high power levels. In addition to this, the converter must be modular, which enables single power stage converter units to be paralleled, whereby the output power throughput can be scaled to higher levels as required by DC charging station standards. Current trends in the charging station are moving toward converters that can handle bidirectional power flow. New practices, such as Vehicle-to-Grid (V2G), involve power transfer between the battery of an electric vehicle and the AC grid. Bidirectional DC/DC converters enable charging of the battery in the forward mode of operation and facilitate flow of power back to the grid from the battery during reverse mode of operation, which can be used to stabilize the grid during peak load periods.

Power density and system efficiency are two important requirements of a converter in a DC charging station. Operating at high switching frequencies enables reduced size of magnetics. By moving to higher bus voltage to facilitate fast charging, more power can be transferred at the same current level. This helps to reduce the amount of copper, thereby improving power density of the converter. The converter must also be highly efficient

2

as it results in significant cost savings and reduced thermal solution. This reduced thermal solution directly translates into reduced and compact heat sink size, which in turn increases the power density of the converter. The converter must also be capable of inherent soft switching like ZVS (Zero Voltage Switching) and ZCS (Zero Current Switching) without the addition any bulky passive components which might hamper power density.

The DC/DC converter must be capable of interfacing seamlessly with Lithium ion or a lead acid battery, which are predominantly used in EV charging stations. The DC/DC converter must also be capable of providing the required voltage conversion between the high-voltage and low-voltage side and provide galvanic isolation between them.

Traditional switching devices have a limit on how quickly the device can switch high voltages, or more appropriately, the dV/dt ability of the device. This slow ramping process increases switching loss because the device spends more time in switching transition. This increased switch time also increases the amount of dead time required in the control system to prevent shoot-through and shorts. The solution to this was developed in newer switching semiconductor technology such as SiC and GaN devices with high electron mobility. This reference design uses SiC MOSFETs alongside TI's SiC gate driver technology to demonstrate the potential benefits it translates when it comes to efficiency and power density.

The following four popular topologies were considered for analysis.

- LLC resonant converter

- Phase-shifted, full bridge

- Single-phase, dual-active bridge

- Dual-active bridge in CLLC mode

Based on this study, the dual-active bridge was chosen for implementation in this reference design, owing to the ease of bidirectional operation, modular structure, competitive efficiency, and power density numbers with respect to other competing topologies. This reference design focuses on addressing the challenges when designing a high-power, dual-active-bridge DC/DC converter for the EV charging station.

# **1.1 Key System Specifications**

Table 1-1 lists some of the critical design specifications of the dual-active-bridge (DAB) DC/DC converter. The system has a full load efficiency of 97.6% at an output power of 10 kW.

| PARAMETER               | SPECIFICATIONS                                  | DETAILS         |

|-------------------------|-------------------------------------------------|-----------------|

| Input voltage range     | 700–800-V DC                                    | Section 3.1     |

| Output voltage range    | 250–500-V DC                                    | Section 3.1     |

| Output power rating     | 10-kW maximum                                   | Section 2.3.5   |

| Output current          | 26-A maximum                                    | Section 2.3.5   |

| Efficiency              | Peak 98.8% (at 4 kW) full load 98.0% (at 10 kW) | Section 4.5     |

| PWM switching frequency | 100 kHz                                         | Section 2.3.4.6 |

| Power density           | > 2 kW/L                                        | Section 4.5     |

| Voltage ripple          | < 5 %                                           | Section 2.3.4.5 |

#### Table 1-1. Key System Specifications

Table 1-1 shows that the input voltage range is between 700 V and 800 V. This range was considered because the DC/DC converter must interface with the front-end Vienna rectifier and the three-phase power factor correction (PFC), which has an output that is within this range. This converter can also be used in conjunction with single-phase PFC systems with an output that is in the range of 400 V, which must interface with 48- and 72-V batteries.

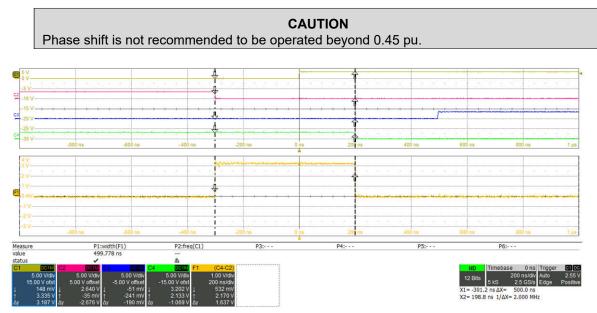

CAUTION

Do not leave the design powered when unattended.

#### WARNING

**High voltage!** Accessible high voltages are present on the board. Electric shock is possible. The board operates at voltages and currents that can cause shock, fire, or injury if not properly handled. Use the equipment with necessary caution and appropriate safeguards to avoid injuring yourself or damaging property. For safety, use of isolated test equipment with overvoltage and overcurrent protection is highly recommended.

TI considers it the responsibility of the user to confirm that the voltages and isolation requirements are identified and understood before energizing the board or simulation. *When energized, do not touch the design or components connected to the design.*

#### WARNING

Hot surface! Contact can cause burns. Do not touch!

Some components can reach high temperatures >  $55^{\circ}$ C when the board is powered on. Do not touch the board at any point during operation or immediately after operating, as high temperatures can be present.

#### WARNING

design as a finitering of the second second

TI intends this reference design to be operated in a *lab environment only and does not consider the design as a finished product* for general consumer use. The design is intended to be run at ambient room temperature and is not tested for operation under other ambient temperatures.

TI intends this reference design to be used only by *qualified engineers and technicians* familiar with risks associated with handling high-voltage electrical and mechanical components, systems, and subsystems.

There are *accessible high voltages present on the board*. The board operates at voltages and currents that can cause shock, fire, or injury if not properly handled or applied. Use the equipment with necessary caution and appropriate safeguards to avoid injuring yourself or damaging property.

6

# 2 System Overview

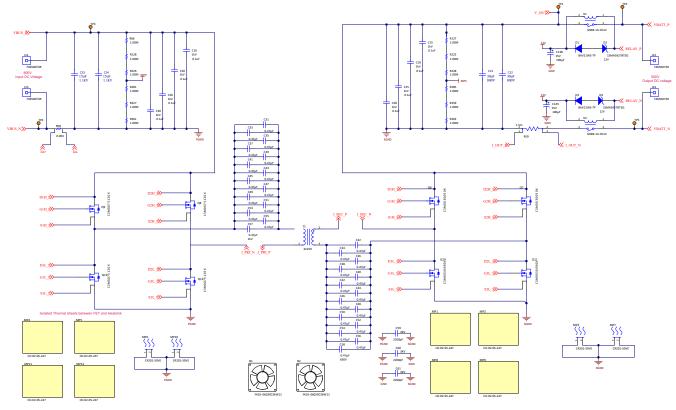

This section shows the block diagram of the dual-active-bridge DC/DC converter.

# 2.1 Block Diagram

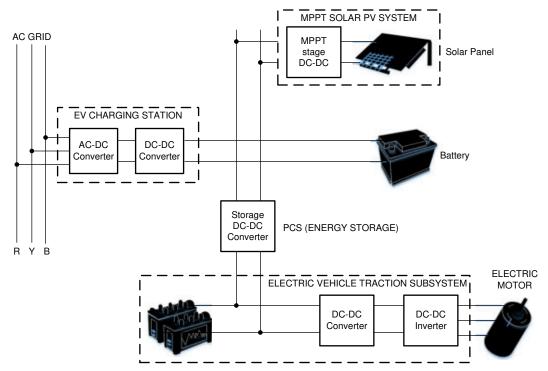

Figure 2-1. TIDA-010054 Block Diagram

This reference design consists of four main sections that intercommunicate:

- A power board comprising the power stage SiC MOSFETs, a high-frequency transformer, current sensing ٠ electronics, gate drivers, voltage and current sensing, and the system power tree

- A TMDSCNCD280039C control card to support digital control

# 2.2 Highlighted Products

This section highlights the critical components of the design which include the gate driver, F280049 controller, isolated amplifiers for current and voltage sensing, and generating voltage references.

# 2.2.1 UCC21710

The UCC21710 is a galvanically isolated single-channel gate driver designed to drive up to 1700-V SiC MOSFETs and IGBTs. The device features advanced integrated protection, best-in-class dynamic performance, and robustness. UCC21710 has up to ±10-A peak source and sink current. The input side is isolated from the output side with SiO2 capacitive isolation technology, supporting up to 1.5-kV<sub>RMS</sub> working voltage with longer than 40 years isolation barrier life, 12.8-kV<sub>PK</sub> surge immunity, as well as providing low part-to-part skew , and >150 V/ns common mode noise immunity (CMTI). The UCC21710 includes the state-of-art protection features, such as fast overcurrent and short circuit detection, shunt current sensing support, fault reporting, active Miller clamp, and input and output side power supply UVLO to optimize SiC and IGBT switching behavior and robustness. The isolated analog to PWM sensor can be utilized for easier temperature or voltage sensing, further increasing the versatility of the drivers and simplifying the system design effort, size and cost.

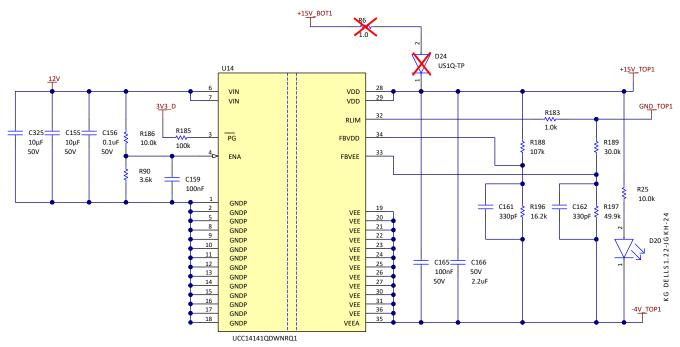

#### 2.2.2 UCC14141-Q1

UCC14141-Q1 is an automotive qualified high-isolation voltage DC/DC power module designed to provide power to IGBT or SiC gate drivers. The UCC14141-Q1 integrates a transformer and DC/DC controller with a proprietary architecture to achieve high density with very low emissions. The high-accuracy output voltages provide better channel enhancement for higher system efficiency without over-stressing the power device gate. The input voltage of UCC14141-Q1 supports both wide LiFePO4 battery voltage of electric vehicle (8 V–18 V) and regulated 12-V rail (10.8 V–13.2 V), with different output power. The fully-integrated module with on-chip device protection requires a minimum of external components, and provides extra features such as input undervoltage lockout, overvoltage lockout, output voltage power-good comparators, overtemperature shutdown, soft-start time-out, adjustable isolated positive and negative output voltage, an enable pin, and an open-drain output power-good pin.

#### 2.2.3 AMC1311

The AMC1311 is used for DC voltage sensing at the input and output terminals. The device is a precision, isolated amplifier with an output separated from the input circuitry by an isolation barrier that is highly resistant to magnetic interference. This barrier is certified to provide reinforced galvanic isolation of up to 7-kV peak according to VDE V 0884-1 and UL1577. The high-impedance input of the AMC1311 is optimized for connection to high-voltage resistive dividers or other voltage signal sources with high output resistance. The excellent performance of the device supports accurate, low temperature drift voltage or temperature sensing and control in closed-loop systems.

For more details on this device, see the AMC1311 product page.

#### 2.2.4 AMC1302

The AMC1302 is a precision, isolated amplifier with an output separated from the input circuitry by an isolation barrier that is highly resistant to magnetic interference. This barrier is certified to provide reinforced galvanic isolation of up to 5 kV<sub>RMS</sub> according to VDE V 0884-11 and UL1577, and supports a working voltage of up to 1.5 kV<sub>RMS</sub>. The isolation barrier separates parts of the system that operate on different common-mode voltage levels and protects the low-voltage side from hazardous voltages and damage. The input of the AMC1302 is optimized for direct connection to a low-impedance shunt resistor or other low-impedance voltage source with low signal levels. The excellent DC accuracy and low temperature drift supports accurate current control in PFC stages, DC/DC converters, AC-motor and servo drives over the extended industrial temperature range from  $-40^{\circ}$ C to +125°C. The integrated missing-shunt and missing high-side supply detection features simplify system-level design and diagnostics.

7

# 2.2.5 OPA320

The OPA320 (single) and OPA2320 (dual) are a new generation of precision, low-voltage CMOS operational amplifiers optimized for very low noise and wide bandwidth while operating on a low quiescent current of only 1.45 mA. The OPA320 series is an excellent choice for low-power, single-supply applications. Low-noise (7  $nV/\sqrt{Hz}$ ) and high-speed operation also make them well-suited for driving sampling analog-to-digital converters (ADCs). Other applications include signal conditioning and sensor amplification. The OPA320 features a linear input stage with zero-crossover distortion that delivers excellent common-mode rejection ratio (CMRR) of typically 114 dB over the full input range.

For more details on this device, see the OPA320 product page.

#### 2.2.6 AMC1306M05

The AMC1306 is a precision, delta-sigma ( $\Delta\Sigma$ ) modulator with the output separated from the input circuitry by a capacitive double isolation barrier that is highly resistant to magnetic interference. This barrier is certified to provide reinforced isolation of up to 7000 V<sub>PEAK</sub> according to the DIN VDE V 0884-11 and UL1577 standards. Used in conjunction with isolated power supplies, this isolated modulator separates parts of the system that operate on different common mode voltage levels and protects lower-voltage parts from damage. The input of the AMC1306 is optimized for direct connection to shunt resistors or other low voltage level signal sources. The unique low input voltage range of the ±50-mV device allows significant reduction of the AMC1306 is Manchester coded (AMC1306Ex) or uncoded (AMC1306Mx), depending on the derivate. By using an integrated digital filter (such as those in the TMS320F2807x or TMS320F2837x microcontroller families) to decimate the bitstream, the device can achieve 16 bits of resolution with a dynamic range of 85 dB at a data rate of 78 kSPS. The bitstream output of the Manchester coded AMC1306Ex versions support single-wire data and clock transfer without having to consider the setup and hold time requirements of the receiving device.

#### 2.2.7 AMC1336

The AMC1336 is a precision, delta-sigma ( $\Delta\Sigma$ ) modulator with the output separated from the input circuitry by a capacitive double isolation barrier that is highly resistant to magnetic interference. This barrier is certified to provide reinforced isolation of up to 8000 V<sub>PEAK</sub> according to the DIN VDE V 0884-11 and UL1577 standards. Used in conjunction with isolated power supplies, this isolated modulator separates parts of the system that operate on different common mode voltage levels and protects lower-voltage parts from damage. The unique wide, bipolar. ±1-V input voltage range of the AMC1336 and the high input resistance support direct connection of the device to resistive dividers in high-voltage applications. When used with a digital filter to decimate the output bitstream, the device can achieve 16 bits of resolution with a dynamic range of 87 dB at a data rate of 82 kSPS. On the high side, the AMC1336 is supplied by a 3.3-V or 5-V power supply. The isolated digital interface operates from a 3.0-V, 3.3-V, or 5-V power supply. The AMC1336 performance is specified over the extended industrial temperature range of  $-40^{\circ}$ C to +125°C.

# 2.2.8 TMCS1133

The TMCS1133 is a galvanically isolated Hall-effect current sensor with industry-leading isolation and accuracy. An output voltage proportional to the input current is provided with excellent linearity and low drift at all sensitivity options. Precision signal conditioning circuitry with built-in drift compensation is capable of less than 2.5% maximum total error over temperature and lifetime with no system level calibration, or less than 1.5% maximum total error with a one-time room temperature calibration (including both lifetime and temperature drift). AC or DC input current flows through an internal conductor generating a magnetic field measured by integrated on-chip Hall-effect sensors. Coreless construction eliminates the need for magnetic concentrators. Differential Hall sensors reject interference from stray external magnetic fields. Low conductor resistance increases measurable current ranges up to  $\pm$ 96 A while minimizing power loss and easing thermal dissipation requirements. Insulation capable of withstanding 5000 V<sub>RMS</sub>, coupled with minimum 8.1-mm creepage and clearance provide up to 1100 V<sub>DC</sub> reliable lifetime reinforced working voltage. Integrated shielding enables excellent common-mode rejection and transient immunity. Fixed sensitivity allows the TMCS1133 to operate from a single 3-V to 5.5-V power supply, eliminates ratiometry errors, and improves supply noise rejection.

#### 2.2.9 TMS320F280039C

The TMS320F28003x (F28003x) is a member of the C2000<sup>™</sup> real-time microcontroller family of scalable, ultralow latency devices designed for efficiency in power electronics, including but not limited to: high power density, high switching frequencies, and supporting the use of GaN and SiC technologies.

These include such applications as:

- Motor drives

- Appliances

- Hybrid, electric and powertrain systems

- Solar and EV charging

- Digital power

- Body electronics and lighting

- Test and measurement

The real-time control subsystem is based on TI's 32-bit C28x DSP core, which provides 120 MHz of signal processing performance for floating- or fixed-point code running from either on-chip flash or SRAM. The C28x CPU is further boosted by the Floating-Point Unit (FPU), Trigonometric Math Unit (TMU), and VCRC (Cyclical Redundancy Check) extended instruction sets, speeding up common algorithms key to real-time control systems.

The CLA allows significant offloading of common tasks from the main C28x CPU. The CLA is an independent 32-bit floating-point math accelerator that executes in parallel with the CPU. Additionally, the CLA has a dedicated memory resource and can directly access the key peripherals that are required in a typical control system. Support of a subset of ANSI C is standard, as are key features like hardware breakpoints and hardware task-switching.

The F28003x supports up to 384KB (192KW) of flash memory divided into three 128KB (64KW) banks, which enable programming and execution in parallel. Up to 69KB (34.5KW) of on-chip SRAM is also available to supplement the flash memory.

The Live Firmware Update hardware enhancements on F28003x allow fast context switching from the old firmware to the new firmware to minimize application downtime when updating the device firmware.

High-performance analog blocks are integrated on the F28003x real-time microcontroller (MCU) and are closely coupled with the processing and PWM units to provide excellent real-time signal chain performance. Sixteen PWM channels, all supporting frequency-independent resolution modes, enable control of various power stages from a 3-phase inverter to power factor correction and advanced multilevel power topologies.

The inclusion of the Configurable Logic Block (CLB) allows the user to add custom logic and potentially integrate FPGA-like functions into the C2000 real-time MCU.

Interfacing is supported through various industry-standard communication ports (such as SPI, SCI, I2C, PMBus, LIN, CAN and CAN FD) and offers multiple pin-MUXing options for the best signal placement. The Fast Serial Interface (FSI) enables up to 200Mbps of robust communications across an isolation boundary.

New to the C2000 platform is the Host Interface Controller (HIC), a high-throughput interface that allows an external host to access the resources of the TMS320F28003x directly.

Want to learn more about features that make C2000 Real-Time MCUs the right choice for your real-time control system? See *The Essential Guide for Developing With C2000™ Real-Time Microcontrollers* application note and visit the *C2000™ real-time MCUs* page.

The *Getting Started With C2000™ Real-Time Control Microcontrollers (MCUs)* getting started guide covers all aspects of development with C2000 devices from hardware to support resources. In addition to key reference documents, each section provides relevant links and resources to further expand on the information covered.

To get started, see the TMDSCNCD280039C evaluation board and download C2000Ware.

9

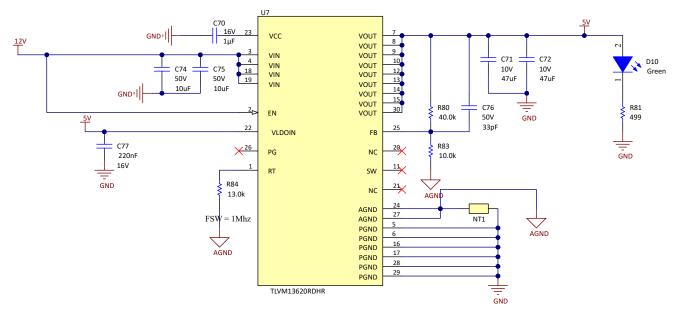

# 2.2.10 TLVM13620

The TLVM13620 synchronous buck power module is a highly integrated 36-V, 2-A DC/DC design that combines power MOSFETs, a shielded inductor, and passives in an Enhanced HotRod<sup>™</sup> QFN package. The module has pins for VIN and VOUT located at the corners of the package for optimized input and output capacitor layout placement. Four larger thermal pads beneath the module enable a simple layout and easy handling in manufacturing. With an output voltage range from 1 V to 6 V, the TLVM13620 is designed to quickly and easily implement a low-EMI design in a small PCB footprint. The total design requires as few as four external components and eliminates the magnetics and compensation part selection from the design process. Although designed for small size and simplicity in space-constrained applications, the TLVM13620 module offers many features for robust performance: precision enable with hysteresis for adjustable input voltage UVLO, integrated VCC, bootstrap and input capacitors for increased reliability and higher density, constant switching frequency over the full load current range for enhanced load transient performance, negative output voltage monitoring.

### 2.2.11 ISOW1044

The ISOW1044 device is a galvanically-isolated controller area network (CAN) transceiver with a built-in isolated DC-DC converter that eliminates the need for a separate isolated power supply in space-constrained isolated designs. The low-emissions, isolated DC-DC meets CISPR 32 radiated emissions Class B standard with just two ferrite beads on a simple two-layer PCB. Additional 20-mA output current can be used to power other circuits on the board. An integrated 10Mbps GPIO channel is available and can help remove an additional digital isolator or optocoupler for diagnostics, LED indication, or supply monitoring.

#### 2.2.12 TPS2640

The TPS26400 devices are compact, feature rich high-voltage eFuses with a full suite of protection features. The wide supply input range of 4.2 V to 42 V allows control of many popular DC bus voltages. The device can withstand and protect the loads from positive and negative supply voltages up to ±42 V. Integrated back-to-back FETs provide a reverse current blocking feature making the device suitable for systems with output voltage holdup requirements during power fail and brownout conditions. Load, source, and device protection are provided with many adjustable features including overcurrent, output slew rate and overvoltage, undervoltage thresholds. The internal robust protection control blocks along with the high-voltage rating of the TPS26400 helps to simplify the system designs for Surge protection. A shutdown pin provides external control for enabling and disabling the internal FETs as well as placing the device in a low-current shutdown mode. For system status monitoring and downstream load control, the device provides fault and precise current monitor output. The MODE pin allows flexibility to configure the device between the three current-limiting fault responses (circuit breaker, latch off, and Auto-retry modes).

# 2.3 System Design Theory

The following sections give an extensive overview of the operating principles of the dual-active bridge.

#### 2.3.1 Dual Active Bridge Analogy With Power Systems

Power transfer between the two bridges in a dual active bridge is analogous to the power flow between two voltage buses in a power system. Consider two voltage sources connected by a line reactance as shown in Figure 2-2.

Figure 2-2. Power Transfer Between Voltage Bus

Figure 2-2 shows that the voltage source on the right is lagging with respect to the voltage source on the left. Hence, the power transfer takes place from the left towards the right as per Equation 1.

$$P = \frac{V_1 V_2 \sin(\phi)}{\omega L} \tag{1}$$

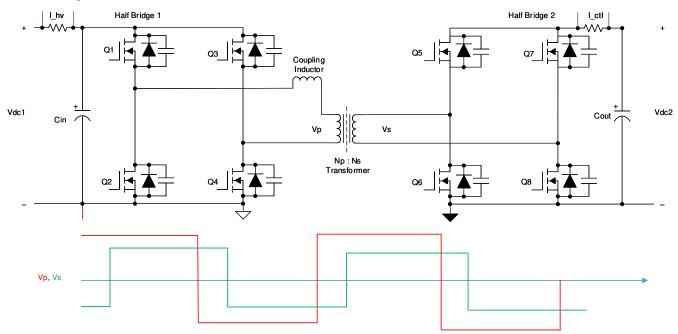

Similarly, power transfer happens in a dual-active bridge where two high-frequency square waves are created in the primary and secondary side of the transformer by the switching action of MOSFETs. These high-frequency square waves are phase shifted with respect to each other. Power transfer takes place from the leading bridge to the lagging bridge, and this power flow direction can be easily changed by reversing the phase shift between the two bridges. Hence, it is possible to obtain bidirectional power transfer with ease in a dual-active bridge as shown in Figure 2-3.

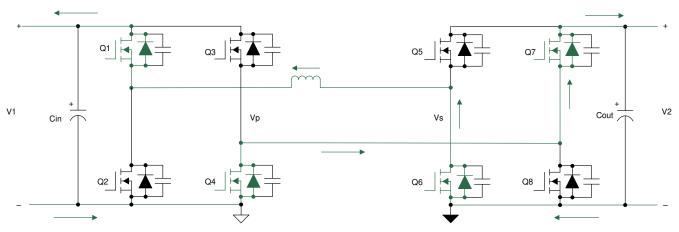

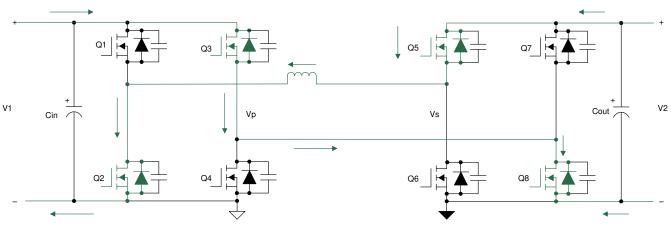

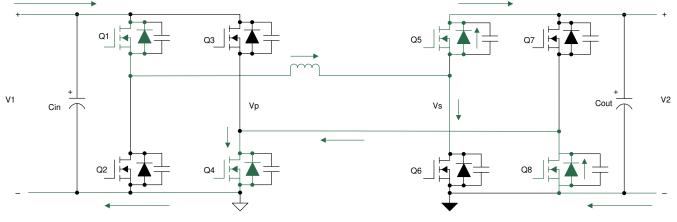

Figure 2-3. Dual-Active Bridge

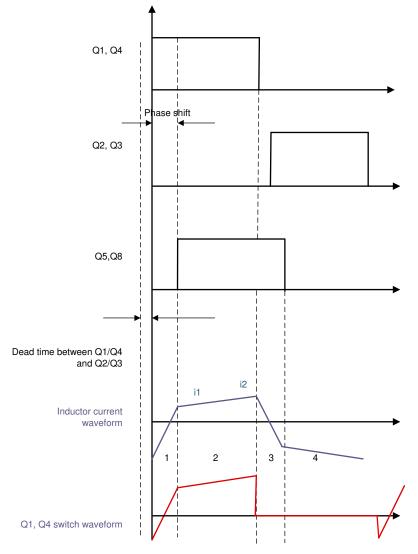

#### 2.3.2 Dual-Active Bridge – Switching Sequence

In a single-phase, dual-active bridge, primary and secondary bridges are controlled simultaneously. All switches operate at 50% duty ratio. The diagonal switches turn on and turn off together so that the output of each bridge is a square wave. The switching sequence of the converter is elaborated in detail in this section. For simplification the transformer is assumed with a windings ratio n = 1:1 and can be removed, for the description of the switching sequence.

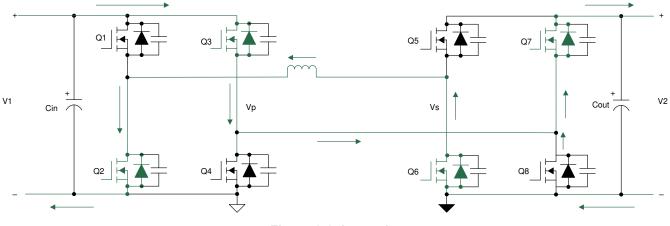

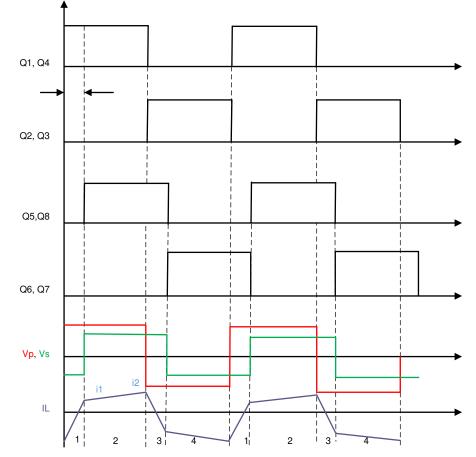

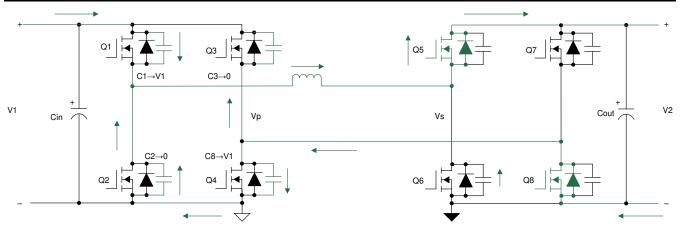

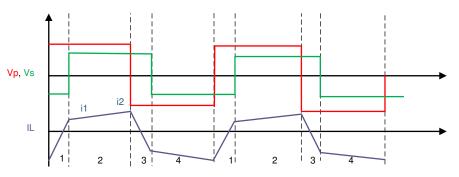

The switching sequence is divided into four intervals based on the inductor current waveform and phase shift between the voltages at the primary and secondary of the transformer. The voltage and the current waveforms are depicted in Figure 2-10. During interval one, the inductor current waveform is both positive and negative, and hence, the current commutation follows the scheme shown in Figure 2-4 and Figure 2-5. During this interval, switches Q1 and Q4 in the primary and switches Q6 and Q7 in the secondary conduct current.

Figure 2-4. Interval 1: Negative Inductor Current

Figure 2-5. Interval 1: Positive Inductor Current

During this interval, the voltage across the primary, Vp, is equal to V1, and the voltage across the secondary, Vs, is equal to V2. The difference between these voltages appears across the leakage inductor, and the slope of the current during this interval can be approximated by Equation 2.

$$\frac{di}{dt} = \frac{V1 + V2}{L}$$

(2)

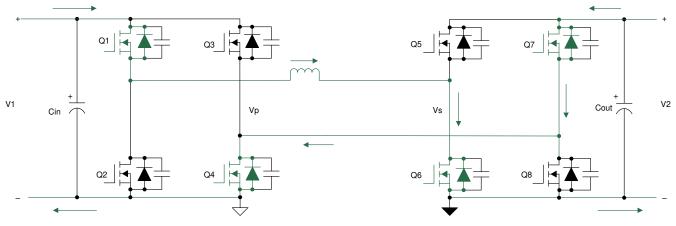

During interval two, the inductor current is positive. The voltage across the transformer primary is positive and is equal to V1, and the voltage across the secondary winding is positive and is equal to V2. Hence, the difference of these two voltages appears across the leakage inductor, and the slope of the rising current during this interval can be calculated by Equation 3.

$$\frac{di}{dt} = \frac{V1 - V2}{L}$$

(3)

During this interval, switches Q1 and Q4 remain turned on, but as the voltage across the secondary is now V2 with the inductor current positive, switches Q5 and Q8 turn on to conduct current. There is a small dead time period between the turn off of Q6 and Q7 and the turn on of Q5 and Q8. During this dead time, the phenomenon of zero voltage switching (ZVS) occurs, which is explained in detail in the following section. The commutation sequence for the second interval is shown in Figure 2-6.

Figure 2-6. Interval 2

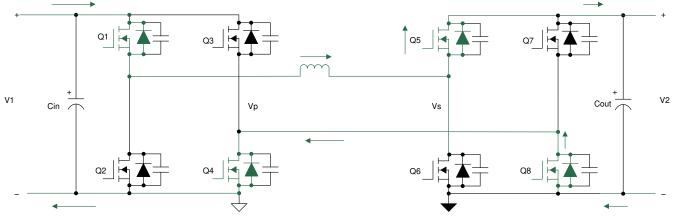

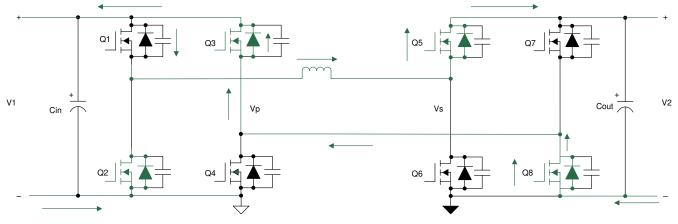

During interval three, the inductor current starts ramping down from the positive peak to a negative value as shown in Figure 2-10. In this interval, the voltage across the primary is –V1, and the voltage across the secondary is V2. The difference of these voltages, which is (-V1-V2), appears across the inductor. Hence, the current ramps down with a negative slope as shown in Equation 4.

$$\frac{di}{dt} = -\frac{V1 + V2}{L} \tag{4}$$

During this interval, switches Q5 and Q8 continue to remain turned on, but as the voltage across the primary is now -V1, switches Q2 and Q3 turn on to conduct current. The conduction for both directions of inductor current IL > 0 and IL < 0 is shown in Figure 2-7 and Figure 2-8, respectively.

Figure 2-7. Interval 3: Positive Inductor Current

14

Figure 2-8. Interval 3: Negative Inductor Current

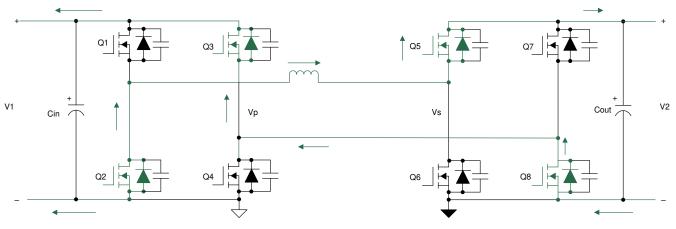

During interval four, the inductor current continues to be negative. During this interval, the voltage across the primary is -V1 and, and the voltage across the secondary is -V2. The difference in these voltages, which is (-V1+V2), appears across the inductor. Hence, the current ramps down with a negative slope as shown in Equation 5.

$$\frac{di}{dt} = -\frac{V1 - V2}{L}$$

(5)

During this interval, switches Q2 and Q3 continue to remain turned on, but as the voltage across the secondary are now -V2, switches Q6 and Q7 turn on to conduct current as shown in Figure 2-9.

Figure 2-9. Interval 4

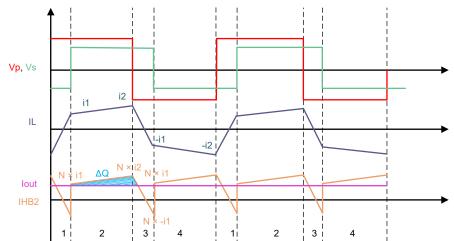

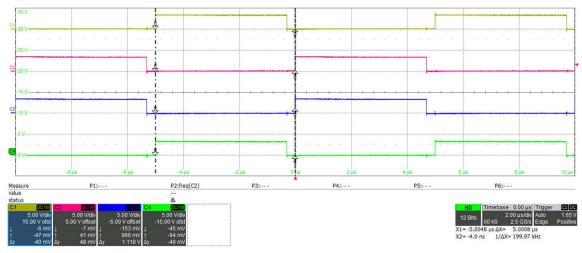

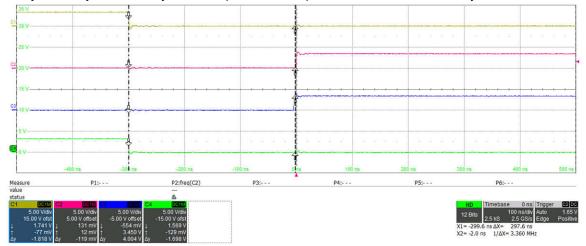

Figure 2-10 shows the gating pulses of the switches on the primary and secondary side. The variable Ø represents the phase shift between the PWM pulses of the primary and secondary side. Vp and Vs represent the voltage on the primary and secondary winding of the transformer. IL represents the transformer current.

Figure 2-10. Gate Signals, Transformer Primary and Secondary Voltages, and Inductor Current

# 2.3.3 Dual-Active Bridge – Zero Voltage Switching (ZVS)

Between turn-off of one MOSFET and turn-on of the other MOSFET of a branch there is dead time. During this dead time the energy stored in the inductor discharges the output capacitances of the MOSFETs and holds them close to zero voltage before they are turned on. This phenomenon, where the voltage across the MOSFET is close to zero at turn on, is referred to as zero voltage switching (ZVS). This is a major advantage with this topology, where due to the natural lagging current in one of the bridges, the inductive stored energy causes ZVS of all of the lagging bridge switches and some of the switches of the leading bridge. This depends on the stored inductive energy ( $E_L = 0.5LI^2$ ) available to charge and discharge the output capacitances of MOSFETs ( $E_C = 0.5CV^2$ ), which again depends on the load of the converter and the input to output voltage ratio. A more detailed look on the boundaries of ZVS is documented in Section 2.3.4.2. Here the principal of ZVS is explained with the transition from interval one to interval two. Similar analysis can be done for all turn-on events.

When transition happens from interval one to two, the primary side switches  $Q_1$  and  $Q_5$  continue conduction, whereas in the secondary,  $Q_6$  and  $Q_7$  turn off and  $Q_5$  and  $Q_8$  turn on. Initially the voltage across  $Q_6$  and  $Q_7$  is zero when conducting, and  $Q_5$  and  $Q_8$  block the entire secondary voltage. During dead time, when all of the switches in the secondary are off, the inductor-stored energy circulates current which discharges the capacitor across MOSFETs  $Q_5$  and  $Q_8$  to zero and charges the capacitor across MOSFETs  $Q_6$  and  $Q_7$  to the full secondary voltage. The current commutation is shown in Figure 2-11.

Figure 2-11. ZVS Transition in Secondary Side - Capacitor

Once the capacitors have been charged and discharged, the current must continue to flow. The current flows through the diodes  $D_5$  and  $D_8$ , thereby clamping the voltage across MOSFETs  $Q_5$  and  $Q_8$  to zero as shown in Figure 2-12. During the next interval, MOSFETs  $Q_5$  and  $Q_8$  are turned on at zero voltage, thereby reducing turn on losses completely. The arrow close to the diode indicates that the diode is conducting and the MOSFET is off.

Figure 2-12. ZVS Transition in Secondary Side - Diode

Similarly, zero voltage switching across the switches of the primary during the transition from interval 2 to 3 is explained in the following section. When transition happens from interval two to three, the secondary side switches  $Q_5$  and  $Q_8$  continue conduction, whereas in the primary,  $Q_1$  and  $Q_4$  turn off and  $Q_2$  and  $Q_3$  turn on. Initially, the voltage across  $Q_1$  and  $Q_4$  is zero when conducting, and  $Q_2$  and  $Q_3$  block the entire secondary voltage. During dead time when all of the switches in the primary are off, the inductor stored energy circulates current, which discharges the capacitor across MOSFETs  $Q_2$  and  $Q_3$  to zero and charges the capacitor across MOSFETs  $Q_1$  and  $Q_4$  to the full primary voltage. The current commutation is shown in Figure 2-13.

Figure 2-13. ZVS Transition in Primary Side - Capacitor

Once the capacitors have been charged and discharged, the current must continue to flow. The current flows through diodes  $D_2$  and  $D_3$ , thereby clamping the voltage across MOSFETs  $Q_2$  and  $Q_3$  to zero as shown in Figure 2-14. During the next interval, MOSFETs  $Q_2$  and  $Q_3$  are turned on at zero voltage, thereby reducing turn on losses completely. The arrow close to the diode indicates that the diode is conducting and the MOSFET is off.

Figure 2-14. ZVS Transition in Primary Side - Diode

#### 2.3.4 Dual-Active Bridge - Design Considerations

A number of factors are critical in the design of the power stage of a dual-active bridge. The most important factors are the selection of leakage inductor, desired phase shift of operation, output capacitor rating, switching frequency of operation, selection of SiC MOSFETs, transformer, and intended ZVS range of operation. Many of these design parameters are interrelated, and selection of any one of them has a direct impact on the others. For example, the selection of leakage inductor has a direct effect on the maximum power transferred, which in turn affects the phase shift of operation of the converter at the intended power level. Each of these factors are discussed in detail in the following sections.

#### 2.3.4.1 Leakage Inductor

The primary specifications for designing a power converter system are input voltage  $V_1$ , output voltage  $V_2$ , and the maximum required power transfer. The power transfer relation of the dual-active bridge is given by Equation 6. The best value for N is  $V_{1,nom}/V_{2,nom}$ , which is 1.6 for this designs specifications.

$$P = \frac{NV_1 V_2 \varphi(\pi - |\varphi|)}{2\pi^2 F_s L}$$

where

• V<sub>1</sub> is the primary-side voltage

- V<sub>2</sub> is the secondary-side voltage

- N is the primary to secondary turns ratio

- φ is the phase shift in radians

- F<sub>s</sub> is the switching frequency

- L is the leakage or coupling inductance

Equation 6 shows that the power transfer can be controlled with the phase shift  $\varphi$ , where the maximum power transfer occurs for  $\varphi = \pi / 2$ .

With V<sub>1</sub> and V<sub>2</sub> fixed, there are two variables left to design for the required output power. These are the switching frequency  $F_s$  and the leakage inductance L. With  $F_s$ set to 100 kHz, L is selected as 35 µH. This allows a theoretical maximum power transfer of 22.85 kW. This leaves some headroom above the target power of 10 kW, which is required for lower output voltages.

The selection of the inductor defines the maximum current stress in the switch node of the converter.

Figure 2-15 shows the inductor current waveform. The currents at points  $i_1$  and  $i_2$  can be derived from this waveform.

$$i_1 = 0.5 \times (2 \times \varphi - (1 - d) \times \pi) \times I_{base}$$

<sup>(7)</sup>

$$i_2 = 0.5 \times (2 \times d \times \phi + (1 - d) \times \pi) \times I_{base}$$

#### where

- d is the voltage transfer ratio of the converter given in Equation 9

- Ibase is the nominal base current of the converter given in Equation 10

$$d = N \times \frac{V_2}{V_1}$$

(9)

$$I_{\text{base}} = \frac{V_1}{\omega L} \tag{10}$$

#### 2.3.4.2 Soft Switching Range

As explained in Section 2.3.2 the zero voltage switching is dependent on the inductor current  $I_L$ . To enable a ZVS transition between interval one and interval two,  $I_L$  needs to be positive when  $Q_5$  and  $Q_8$  is turned on. The current at this point is defined as  $i_1$  (see Equation 9). For ZVS transition between interval two and three,  $I_L$  needs to be positive as well. This current point is defined as  $i_2$  (see Equation 10). For ZVS transition between interval three interval four and interval four and interval one,  $I_L$  needs to be negative. Since the current waveform is symmetric, the currents at these points are equal to  $-i_1$  and  $-i_2$ .

Neglecting output capacitance of the MOSFETs, the ZVS range can derived by setting equations Equation 9 and Equation 10 to zero and solving for  $\varphi$ . This gives the minimum required phase shift for ZVS depending on input and output voltage ratio d. This leads to Equation 11 and Equation 12.

$$\varphi_{\text{ZVS, pri}} > \frac{\left(1 - \frac{1}{d}\right) \times \pi}{2}$$

(11)

(8)

(12)

$$\varphi_{\text{ZVS, sec}} > \frac{(1-d) \times \pi}{2}$$

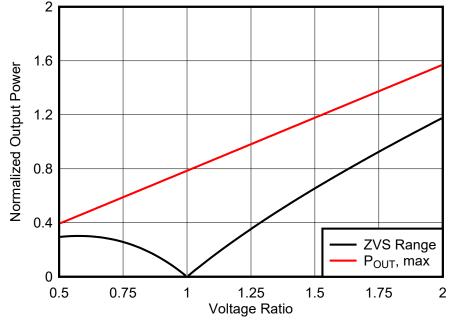

Since the phase shift is proportional to the output power, the ZVS range can be plotted on a output power over voltage ratio graph as shown in Figure 2-16. The power is normed to P<sub>base</sub>.

Figure 2-16. ZVS Range and Maximum Output Power Over Voltage Ratio

$$P_{\text{base}} = \frac{V_1^2}{\omega L} \tag{13}$$

The red line in Figure 2-16 shows the maximum possible output power  $P_{out,max}$  for a certain voltage ratio. For light loads (output power below ZVS boundary plotted in black) and a voltage ratio d < 1, the secondary side experiences hard switching, while for d > 1 and low load the primary side experiences hard switching. For voltage ratios d close to one ZVS can be achieved down to very low loads. The ZVS range can be increased by applying different control schemes like extended-, dual- or triple-phase shift control.

Extended-phase shift control is implemented and available in software. For detailed information see Section 6.

#### 2.3.4.3 Effect of Inductance on Current

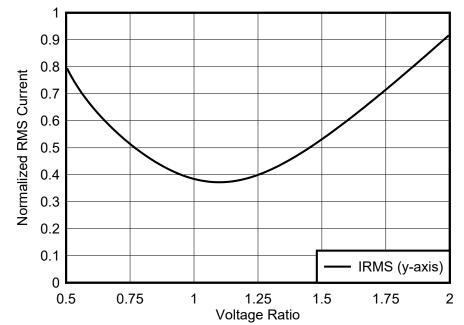

The selection of leakage inductance also determines the currents in the converter. Equation 14 and Equation 15 show the RMS currents across the primary winding and secondary winding of the transformer. It is important not only to calculate currents in the nominal operating point where d = 1, since for other voltage ratios RMS currents can increase for the same power transferred as shown in Figure 2-17. The RMS current is normalized to  $I_{base}$  (see Equation 10).

$$I_{P_{RMS}} = \sqrt{\frac{1}{3} \times \left(i_1^2 + i_2^2 + \left(1 - \frac{2\phi}{\pi}\right) \times i_2 \times i_1\right)}$$

(14)

$$I_{S_RMS} = N \times I_{P_RMS}$$

(15)

Figure 2-17. RMS Currents in Leakage Inductor for Equal Output Power Over Different Voltage Ratio

#### 2.3.4.4 Phase Shift

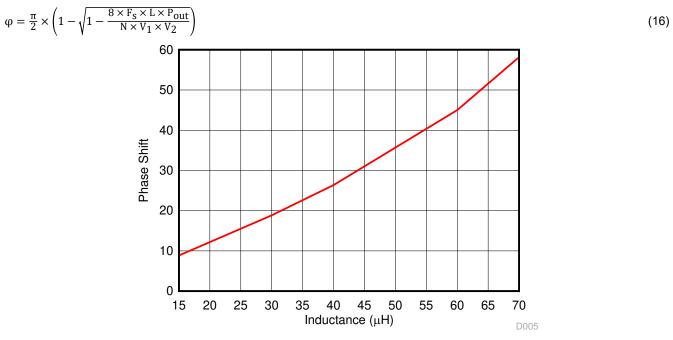

The phase shift of the converter is dependent on the value leakage inductor. The phase shift for required power transfer is given by Equation 16.

Figure 2-18. Variation of Phase Shift With Leakage Inductance

Figure 2-18 shows the required phase shift in degrees over leakage inductance for  $V_1 = 800$  V,  $V_2 = 500$  V, N = 1.6,  $F_S = 100$  kHz, and  $P_{out} = 10$  kW. The graph illustrates that for a small value of inductance, a maximum power transfer at a small value of phase shift is obtained. To have fine control over power transferred, fine high-resolution steps in which the phase can be varied must be obtained. Alternatively, a larger inductor can obtain maximum power transfer at a high value of phase shift for better control. For the selected L = 35  $\mu$ H, a phase shift of 23 degrees or 0.4 radians is required.

# 2.3.4.5 Capacitor Selection

The output capacitor in the dual-active bridge must be designed to handle the ripple. Figure 2-19 illustrates that the capacitor current is the difference between the current  $I_{HB2}$  and the output current  $I_{Load}$ , also called  $I_{out}$  as shown in Equation 17. The waveforms are also shown in Figure 2-20.  $I_{HB2}$  is the rectified and scaled inductor current. The best output current  $I_{out}$  is obtained by  $P_{out} / V_2$ . From the difference between  $I_{out}$  and  $I_{HB2}$  the charge  $\Delta Q$  (marked in blue) can be obtained. Afterwards, the required capacitance can be calculated using Equation 18 for a maximum allowed ripple voltage.

$$I_{cap} = I_{HB2} - I_{out}$$

(17)

$$C_{out} = \frac{\Delta Q}{V_{ripple}}$$

(18)

Since the current waveforms depend on input-to-output voltage ratio and phase shift, this analysis needs to be done for all corner cases.

A MATLAB® script is used to obtain  $\Delta Q$  for different input-to-output voltage ratios. The script first interpolates the ideal capacitor current waveform shown in Figure 2-20 and subtracts  $I_{out}$ . The resulting waveform is the capacitor current  $I_{C,out}$ . Next, the integral of  $I_{C,out}$  is calculated. Subtracting min( $\int I_{C,out}$ ) of max( $\int I_{C,out}$ ) provides  $\Delta Q$ . This results in  $\Delta Q$  of 12 µC for 10-kW output power and nominal input and output voltages. For lower output voltages,  $\Delta Q$  increases to 50 µC. Using Equation 18 and a voltage ripple of 5 V leads to a required output capacitance of 10 µF. These are the best values assuming no parasitics in the capacitors. In the current design Aluminum Electrolytic Capacitors with relatively high ESR are used. Therefore 470 µF of output capacitance is necessary to reduce the ripple to 5%. In the next design revision, the design is changed to film-capacitors, with much lower ESR which allows a significant reduction in output capacitance.

Figure 2-19. Output Current in Dual-Active Bridge

Figure 2-20. Output Capacitor Current

The capacitor also needs to be able to handle the RMS current, which is calculated with Equation 19.

$$I_{C, RMS} = \sqrt{\frac{\phi}{2 \times \pi} \times \frac{1}{3} \times \left(i_{C2}^2 + i_{C2} \times i_{C3} + i_{C3}^2\right) + \left(1 - \frac{\phi}{2 \times \pi}\right) \times \frac{1}{3} \times \left(i_{C1}^2 + i_{C1} \times i_{C2} + i_{C2}^2\right)}$$

(19)

where

$i_{C1} = (i_1 \times N) - I_{out}$

$i_{C2} = (i_2 \times N) - I_{out}$

$i_{C3} = (-i_1 \times N) - I_{out}$

#### 2.3.4.5.1 DC-Blocking Capacitors

DC Blocking capacitors are introduced in the power stage to avoid saturation of the transformer in case of unbalanced currents, which can be caused by mismatched PWM signals, mismatched propagation delays in gate drivers or other asymmetries in the system. Especially during start-up and load transients unbalanced currents can occur. The DC blocking capacitors must be designed to handle the RMS currents on the transformer, be able to withstand the full-voltage and provide enough capacitance to not influence the switch-node voltage waveforms in a significant manner.

$$C_{\text{DCBlock, min}} = \frac{100}{4 \times \pi^2 \times F_{\text{S}}^2 \times L} = 7.2 \ \mu\text{F}$$

(20)

# 2.3.4.6 Switching Frequency

Switching frequency is an important design parameter which affects the efficiency and power density of the power converter. The input and output voltage levels primarily determine the type of switches used in the power stage. Usage of SiC MOSFETs in the power stage enables high switching frequencies. Operating at higher switching frequencies enables a reduced size of magnetics which improves thermal conditions, thereby improving the power density of the converter. Therefore, selection of switching frequency is primarily a tradeoff between the allowable heat sink design and the transformer size for a given efficiency target. Secondly, if the output capacitance (Ecoss) of MOSFET is very high, selection of switching frequency leads to high switching losses at light load and hampers efficiency. Selection of switching frequency also affects the control-loop bandwidth implementation. Considering all of these parameters, 100 kHz was used as the switching frequency for this application.

#### 2.3.4.7 Transformer Selection

In a power supply design, transformers and inductors are major contributors to size. Increasing the operating frequency reduces the size, but increasing the switching frequency beyond a particular value affects the

efficiency of the power module. This is because the skin effect becomes very high at that frequency where the current flows through the surface of the conductor. Similar to the skin effect, there is a proximity effect, which causes current to only flow on surfaces closest to each other. Furthermore, from a proximity standpoint in high-frequency designs, conductor size and the number of layers must be optimized. With a planar transformer, more interleaving to reduce the proximity effect can be achieved. This interleaving can be tailored to produce a specific amount of leakage so as to aid in power transfer and to contribute to ZVS.

Planar transformers offer the following advantages over conventional transformers and hence were used in this reference design:

- Planar magnetics have very high power density. They are more compact and consume less space when compared to a conventional transformer of the same power rating.

- They have the ability to do more interleaving to reduce AC conductor losses.

- They have consistent spacing between turns and layers which translate into consistent parasitics. Both leakage inductance and intra-winding capacitances can be maintained to very predictable and tight values.

- Tight control over the leakage inductance is possible with planar magnetics.

- The compact size of the transformer can support integration of the additional shim inductor with the transformer itself without the need for a separate component on board.

The leakage inductor alone cannot provide soft switching up to light loads. As seen previously, increasing the soft switching range by increasing inductor value increases the RMS currents. In practice, a leakage inductor is chosen to provide soft switching only up to  $\frac{1}{2}$  or  $\frac{1}{3}$  of rated load. To increase the soft switching range, multiphase-shift controls can be applied. In some applications increased switching losses because of hard switching are acceptable for low loads since conduction losses decrease for low loads.

#### 2.3.4.8 SiC MOSFET Selection

As shown in Figure 2-1, the main power stage switching devices of the primary and secondary must block the full input and output DC voltages. SiC switches were chosen for the following reasons:

- The switching speed of the SiC MOSFET is faster than a traditional Si device, thereby reducing switching losses.

- The reverse recovery charge is significantly smaller in the SiC MOSFET for the DAB application, resulting in reduced voltage and current overshoot.

- Lower state resistance significantly reduces conduction losses during on time of the device.

- The switches have the ability to block higher voltages without breaking down.

For this design, 1200-V Cree<sup>®</sup> devices with on-state resistance of 75 m $\Omega$  were used on the primary side, and a 900 V, voltage-blocking Cree device with on-state resistance of 30 m $\Omega$  was used in the secondary. Both are four-pin devices with a Kelvin connection for better switching performance. The actual conduction and switching loss calculations are shown in the following sections.

#### 2.3.5 Loss Analysis

This section reviews the theoretical efficiency numbers obtained in the dual-active bridge. To arrive at the losses in different elements, the average and the RMS currents across the primary and secondary side are calculated. Details on the actual derivation of equations are out of scope for this design. The maximum power transfer in a dual-active bridge occurs at a phase shift of 90°. However, a high phase shift requires a high leakage inductance for power transfer. Using a high inductor leads to increased RMS currents in the primary and secondary side, which affects the efficiency of the converter.

Figure 2-18 shows the relationship between phase shift and the required inductance obtained from MATLAB simulations. The system specifications are tabulated in Table 2-1.

| Table 2-1. DC/DC Converter Electrical Parameters |                        |

|--------------------------------------------------|------------------------|

| PARAMETER                                        | SPECIFICATIONS         |

| Phase shift                                      | –0.44 < φ < 0.44 (rad) |

| Total Leakage Inductance                         | 35 µH                  |

| Turns Ratio                                      | 1: 0.625               |

| Load resistance                                  | 25 Ω                   |

# Table 2-1 DC/DC Converter Electrical Parameters

# Table 2-1. DC/DC Converter Electrical Parameters (continued)

| (continuou)    |                |  |

|----------------|----------------|--|

| PARAMETER      | SPECIFICATIONS |  |

| Input Voltage  | 800 V          |  |

| Output voltage | 500 V          |  |

| Input current  | 12.5 A         |  |

| Output current | 20 A           |  |

| Output Power   | 10 kW          |  |

#### 2.3.5.1 SiC MOSFET and Diode Losses

As SiC is used in the power stage, the body diodes conduct only during the dead time, causing ZVS. In all other instances, the channel of SiC is turned on to conduct current. The peak current in the primary is calculated using Equation 7 and Equation 8. For the nominal operating conditions:

- V<sub>1</sub> = 800 V

- V<sub>2</sub> = 500 V

- F<sub>s</sub>= 100 kHz

- T<sub>s</sub>=10 µs

- N = 1.6

- φ = 0.4 rad

- P = 10 kW

- L = 35 µH

Calculating  $i_1$  and  $i_2$  for these inputs leads to  $i_1 = i_2 = 14.3$  A.  $i_1 = i_2$  is only true for the nominal output voltage V<sub>2</sub> = V<sub>1</sub> / N.

Figure 2-21 shows the current waveform of the switches on the primary side. The RMS value can be calculated from equation Equation 21. Inserting the values mentioned above leads to 9.67 A of RMS current for primary side switches.

$$I_{\text{switch, prim, rms}} = \sqrt{\frac{1}{6} \times \left(i_1^2 + i_2^2 + \left(1 - \frac{2\phi}{\pi}\right) \times i_2 \times i_1\right)} = 9.67 \text{ A}$$

(21)

The diode conducts for only a small fraction of time during the switching period, as in the dead time causing ZVS. The dead time chosen for this application is 200 ns.

$$I_{\text{diode, prim}} = i_2 \times \frac{t_{\text{dead}}}{T_{\text{S}}} = 0.286 \text{ A}$$

(22)

The value of drain-source resistance corresponding to the applied gate voltage waveform is obtained from the SiC MOSFETs data sheet. This value is 75 m $\Omega$ . The forward voltage drop across the body diode is 5.5 V. The conduction losses across the four primary side FETs is calculated using Equation 23:

$$P_{\text{cond, prim}} = 4 \times \left( I_{\text{switch, prim, rms}}^2 \times R_{\text{ds, on}} + I_{\text{diode, prim}} \times V_{\text{fd, prim}} \right) = 34.34 \text{ W}$$

(23)

Similarly, the conduction losses are calculated across the secondary side FETs by scaling the primary side RMS currents with transformer turns ratio using Equation 24 and Equation 25. The on state resistance of the secondary side MOSFET is 30 m $\Omega$ . The forward voltage drop across the body diode is 5.5 V

$$I_{switch, sec, rms} = N \times I_{switch, prim, rms} = 15.47 A$$

(24)

$$I_{diode, sec} = N \times I_{diode, prim} = 0.458 A$$

(25)

$$P_{\text{cond, sec}} = 4 \times \left( I_{\text{switch, sec, rms}}^2 \times R_{\text{ds, on}} + I_{\text{diode, sec}} \times V_{\text{fd, sec}} \right) = 37.88 \text{ W}$$

(26)

Figure 2-21. Switch Current Waveforms for Calculating RMS Value of Current

The switching loss curves from the manufacturer are used to calculate switching losses.

Because the FETs turn on at zero voltage, only the turn-off loss coefficients are used for calculating the switching losses. Using the C3M0030090K data sheet information, a turn-off energy of 60  $\mu$ J is estimated for this operating condition. The values of switching loss per device is obtained using the information in Equation 27. This leads to 24 W of switching losses for the secondary side.

$$P_{sw, tunroff, sec} = F_s \times E_{off} = 6 W$$

For the primary side switch C3M0075120K the turn-off energy is estimated at 75  $\mu$ J. Which leads to 30 W of switching losses on the primary side.

$$P_{sw, tunroff, prim} = F_s \times E_{off} = 7.5 W$$

Total turn off switching losses in the primary and secondary side across all eight switches comes to 54 W.

These calculations are done for the nominal operating conditions. For different operating points these calculations need to be adjusted. For non-nominal output voltages, the zero-voltage-switching can be lost and the turn-on losses must be taken into account.

#### 2.3.5.2 Transformer Losses

For this reference design a planar transformer was selected and was designed with the specifications shown in Table 2-2. The estimated power losses under normal operating conditions are 50 W.

| Table 2-2. Transformer Specifications |                                                           |  |

|---------------------------------------|-----------------------------------------------------------|--|

| FUNCTIONAL SPECIFICATIONS             | RATINGS                                                   |  |

| Total output power                    | 10 kW (500 V/20 Adc)                                      |  |

| Operating frequency                   | 100–200 kHz                                               |  |

| Input voltage of transformer          | 800 V (V <sub>OUT</sub> = 500 V), Bipolar Square waveform |  |

| Volt-second product                   | 8000 V μs – for V <sub>OUT</sub> = 500 V, 100 kHz         |  |

| Primary-to-secondary ratio            | 24:15                                                     |  |

| Primary current maximum               | 13.5 Arms (20 A peak) – for V <sub>OUT</sub> = 500 V      |  |

| Secondary current maximum             | 20 Arms (30 A peak) – for V <sub>OUT</sub> = 500 V        |  |

| Estimated power losses                | 50 W – for V <sub>OUT</sub> = 500 V, 100 kHz;             |  |

| Primary winding DC resistance         | 43 mΩ                                                     |  |

| Secondary winding DC resistance       | 16 mΩ                                                     |  |

| Leakage inductance                    | 34 µH                                                     |  |

| Magnetizing inductance                | 720 µH                                                    |  |

| Table 2-2. | Transformer | Specifications |

|------------|-------------|----------------|

|------------|-------------|----------------|

More details of this transformer are available from Payton.

#### 2.3.5.3 Inductor Losses

The inductor used for this design is a custom inductor, which is integrated in the Payton planar transformer. The total leakage inductance is 34  $\mu$ H and the total estimated power loss provided by the manufacturer is 15 W (for V<sub>OUT</sub> = 500 V, F<sub>s</sub>=100 kHz).

(27)

(28)

### 2.3.5.4 Gate Driver Losses

The power loss in the gate driver circuit includes the losses in the UCC21530 and losses in the peripheral circuitry like the gate resistors. The power losses consist of the static power loss, which includes quiescent power loss on the driver as well as driver self-power consumption when operating with a certain switching frequency. Values of the quiescent current flowing into the  $V_{cc}$  pin ( $I_{VCCQ}$ ) and  $V_{DD}$  pin ( $I_{VDDQ}$ ) are extracted from the data sheet.

$$P_{O} = (V_{CC} \times I_{VCCO}) + (V_{DD} \times I_{VDDO}) = (3.3 V \times 3 mA) + (15 V \times 4 mA) = 70 mW$$

(29)

By substituting the values from the data sheet in Equation 29, the result is  $P_Q$  losses of the gate driver around 70 mW. The other component of gate driver loss is the switching operation loss. Which result in a total of 560 mW for eight gate drivers.

$$P_{sw} = 2 \times (V_{DD} - V_{EE}) \times Q_G \times F_s = 0.2 W$$

(30)

By substituting the value of  $V_{DD}$  = 15 V,  $V_{EE}$  = -4 V,  $F_{SW}$  = 100 kHz,  $Q_G$  = 53 nC in Equation 30, the switching loss comes to 0.2 W per FET on primary. The gate charge for C3M0075120K (primary side MOSFET) is extracted from the data sheet. Similarly, for the secondary side, the switching losses are calculated to be approximately 0.33 W. Gate charge,  $Q_G$ , for the C3M0030090K MOSFET is 87 nC and is obtained from the data sheet. Also during turn on and turn off of the MOSFETs, losses occur in the gate resistors. The turn on and turn off gate resistors are 2  $\Omega$ . These resistors are chosen to dampen out the oscillations at the gate. The gate driver IC can sink and source 10-A peak current during the switching process. Taking an average value of this current pulse over a switching cycle, the turn on and turn off losses occurring in the gate resistors is given by Equation 31.

$$P_{\text{cond}} = \frac{Q_{\text{G}} \times (V_{\text{DD}} - V_{\text{EE}}) \times F_{\text{s}}}{2} \times \left(\frac{R_{\text{on}}}{R_{\text{Gin}}} + \frac{R_{\text{off}}}{R_{\text{Gin}}}\right) = 18 \text{ mW}$$

(31)

This value comes to 18 mW for each switch on primary side and 30 mW per switch on secondary side, summing up to 192 mW in total. Thus, the total losses occurring in all gate drivers is approximately 3 W.

#### 2.3.5.5 Efficiency

Table 2-3 summarizes the loss numbers from the previous sections and computes the theoretical efficiency at 10 kW.

| TYPE OF LOSS                                      | LOSS (WATTS) |

|---------------------------------------------------|--------------|

| SiC conduction loss in primary and secondary side | 72           |

| SiC turn off switching loss                       | 54           |

| Transformer loss                                  | 50           |

| Gate driver loss + shunt resistor losses          | 3            |

| Inductor loss                                     | 15           |

| Efficiency                                        | 98%          |

#### Table 2-3. Loss Analysis

#### 2.3.5.6 Thermal Considerations

Heat sinks are used to cool CR201-50VE. Two FETs are mounted per heat sink: therefore, insulation must be used between the exposed drain of the FETs and the heat sink. CD-02-05-247 insulation sheets are used. Additionally two 12-V (CFM-6015V-154-362) fans are mounted to provide sufficient airflow. The heat sink data sheet provides a thermal resistance of 0.5 C / W (R<sub>th,HS</sub>). The insulation sheet adds another 0.1 C / W (R<sub>th,iso</sub>) of thermal resistance. The primary side FET C3M0075120K has a thermal resistance R<sub>th,JC</sub> of 1.1 C / W and a maximum operating temperature of 150°C, while the secondary sided FET (C3M0030090K) has a thermal resistance R<sub>th,JC</sub> of 0.48 C / W and also a maximum junction temperature of 150°C. With this information, the maximum allowable power dissipation per FET can be calculated with Equation 32. This assumes 2 FETs are connected to one heat sink like in the reference design.

$P_{max} = \frac{T_{J, max} - T_A}{2 \times R_{th, HS} + R_{th, iso} + R_{th, JC}}$

This leads to a maximum of 50 W of losses per FET on primary side and 69 W per FET on secondary side assuming an ambient temperature  $T_A$  of 40°C.

# 3 Circuit Description

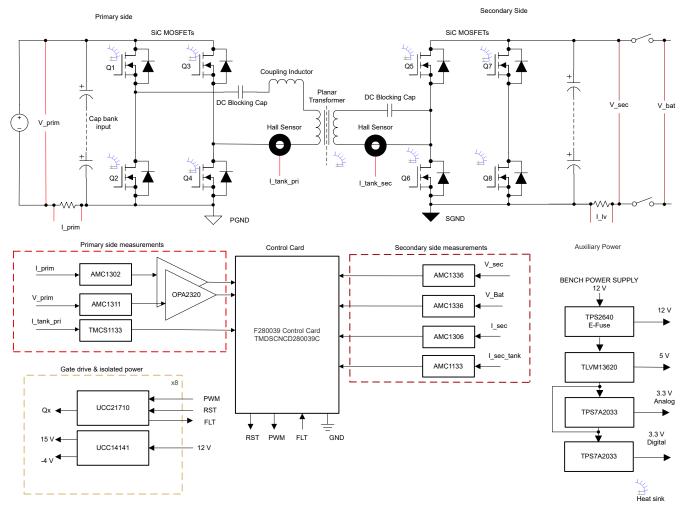

# 3.1 Power Stage

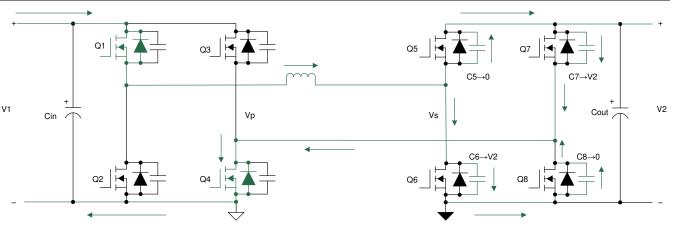

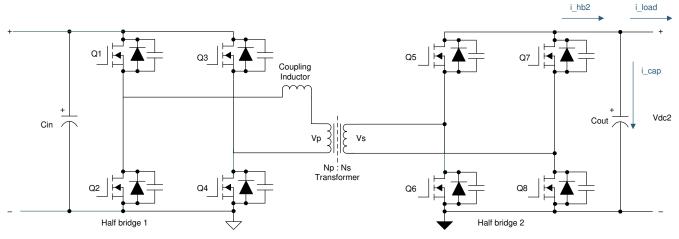

Figure 3-1 shows the power stage of a single-phase, dual-active bridge. The primary side consists of 1200-V, 75-m $\Omega$  silicon carbide FETs C3M0075120K to block a DC voltage of 800 V, and the secondary side consists of 900-V, 30-m $\Omega$  silicon carbide FETs C3M0030090K to block DC voltage of 500 V. The full bridges are connected with a high-frequency switching transformer (T1). Four CR201-50VE heat sinks in combination with two fans are used to cool the FETs. CD-02-05-247 insulation sheets are used between the FETs and the heat sinks to provide necessary insulation and a good thermal interface.

Figure 3-1. Power Stage

(32)

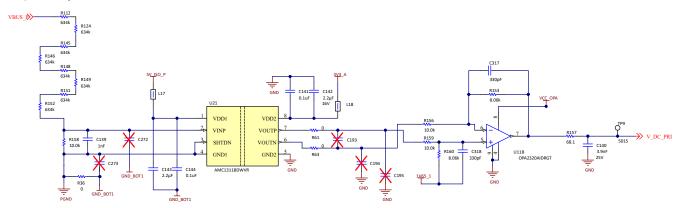

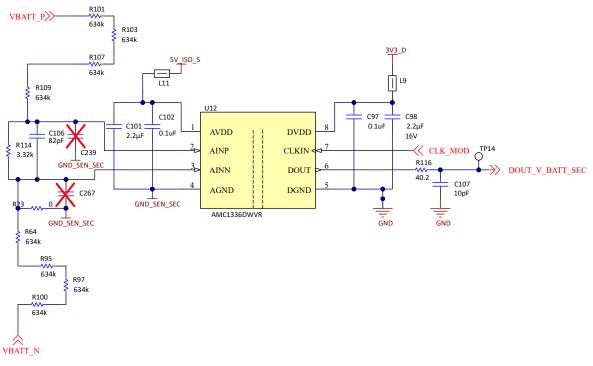

# 3.2 DC Voltage Sensing

#### 3.2.1 Primary DC Voltage Sensing

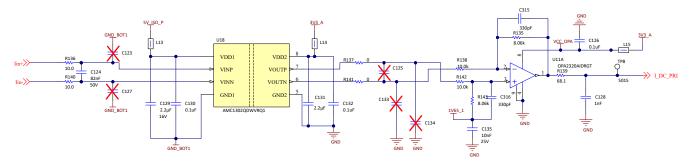

Figure 3-2 shows the primary voltage sensing circuit. The maximum primary input voltage to be sensed is 800 V and is scaled down by a resistor divider network to 1.57 V, which is compatible to the 2-V input of the AMC1311. Figure 3-2 shows eight 634-k $\Omega$  resistors and one 10-k $\Omega$  resistor used to drop the primary voltage signal. The signal is then processed by one channel of the OPA2320, which converts it in the range of 0 V to 3.3 V as required by the ADC.

Figure 3-2. Primary Side DC Voltage Sensing

Figure 3-2 shows the isolated power supply circuit for powering the AMC1311. An isolated 3.3-V supply is needed to power the primary side of the AMC1311. The isolated power supply is shared with a low-side gate driver bias supply, generated by a UCC1414-Q1. The 15-V output voltage of the UCC14141-Q1 is used but a TLV760 is necessary to generate the 5 V for the AMC1311. This isolated supply is also used for the isolated current sensing on the primary side.

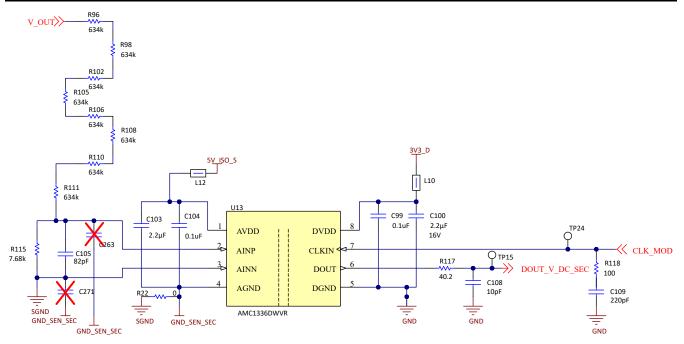

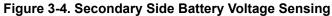

#### 3.2.2 Secondary DC Voltage Sensing

On the secondary side an isolated modulator is used for voltage sensing. A digital interface is preferred here, since the secondary side sensing is much further away from the controller. A digital interface is not as vulnerable to noise and therefore a better fit for long traces inside a power conversion system. The necessary clock is generated by a spare PWM module of the microcontroller. The output bit stream is fed into the SDFM Module of the C2000. Using the configurable decimation filters within the SDFM module allows for accurate measurements and fast protection. The 500 V is scaled down to 0.76 V which fits the ±1-V input of the AMC1336.

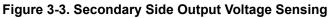

#### 3.2.2.1 Secondary Side Battery Voltage Sensing

In addition to the DC voltage sensing, a battery voltage sensing is implemented inside the relays, which allows for active pre-charging from the primary side. This modulator uses the same clock as the DC voltage sensing inside the relays. The output is connected to another SDFM channel. For the resistor divider there are two scenarios. If the relay is open GND\_SEN\_SEC is floating with regards to VBATT\_N. In the case the full resistor divider is active, scaling down the 500 V to 0.33 V. IN case the relay is closed VBATT\_N is shorted with GND\_SEN\_SEC; therefore, only the upper part of the resistor divider is active. In this configuration 500 V is scaled down to 0.65 V.

# 3.3 Current Sensing

Current sensing is important for sensing overcurrent and getting a closed loop system to work accurately. In this design, current sensing is done at multiple locations with different sensing methods. The first is on the input and output side DC terminals using current sense resistors. The isolated amplifier AMC1302 is used on the primary side and has a input voltage of 50 mV. Therefore, a  $3-m\Omega$  shunt resistor is used, converting the maximum input current of 12.5 A to 37.5 mV.

Figure 3-5. Primary Side Input Current Sensing

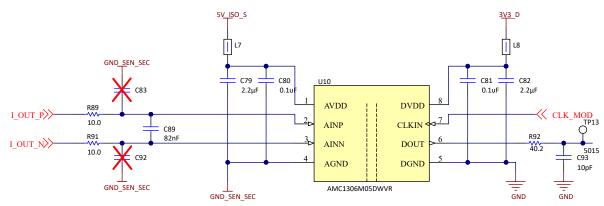

The isolated modulator AMC1306M05 is used on the secondary side. Here a 1.5-m $\Omega$  shunt converts the maximum output current of 20 A to 30 mV, which fits the 50-mV input of the AMC1306M05. Now for lower output voltages, higher output currents can be achieved, which can need a smaller shunt to measure the full current range.

Figure 3-6. Secondary Side Output Current Sensing

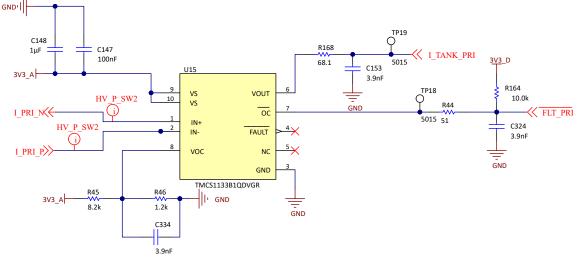

The Hall sensor TMCS1133 is used to measure the transformer current on the primary and secondary side. Here a Hall sensor is preferred because of the lower propagation delay which is needed to implement an overcurrent protection at the switch nodes. TMCS1133 offers 1 MHz of bandwidth, which is necessary to measure an accurate current waveform at 100 kHz switching frequency. TMCS1133 also offers a built-in overcurrent protection which is set to 45 A on the primary side and to 70 A on secondary side by the resistor divider on the VOC pin. The fault output indicates this overcurrent scenario. This pin is connected to a GPIO of the C2000 MCU, which is configured to trip the PWM signal in case of overcurrent.

Figure 3-7. Transformer Current Sensing

# **3.4 Power Architecture**

The power tree of this reference design consists of multiple ICs providing the necessary system voltages:

- An external 12-V power supply is necessary to operate the board. This 12-V rail directly powers the fans, relays, and UCC14141 isolated bias supplies

- 5 V to the Control Card and 3.3-V LDOs

- Two LDOs are used to generate 3.3-V digital and 3.3-V analog supplies for the Cs

- Isolated bias supply provides +15 V and 4 V for gate drivers

- An LDO is used on the high side to generate isolated 5 V to power the high sides of the isolated sensing circuits

#### 3.4.1 Auxiliary Power Supply

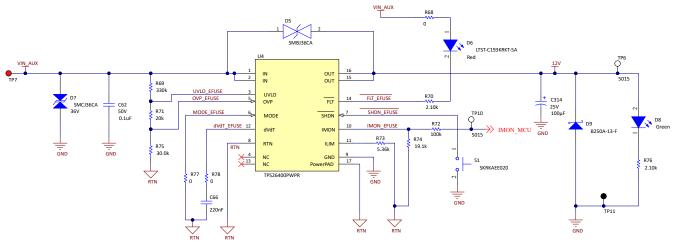

The external power is directly used to power fans, relays and isolated bias supplies. Therefore, the eFuse TPS2640 is used to protect the system. Overvoltage protection is set to 15 V, undervoltage lockout is set to 9 V and a current limit is set to 2.2 A. A detailed design procedure is found in the device data sheet. Two LEDs are used to indicate the status. The green LED D8 indicates normal status, while the red LED D6 indicates a fault state. Use the S1 push-button to reset the device.

Figure 3-8. eFuse Circuitry

The power module TLVM13620 is used to generate a 5-V rail from the input. LED D10 indicates the 5-V output. A module with integrated inductor is used for the design simplicity and small footprint.

Figure 3-9. 5-V Power Module

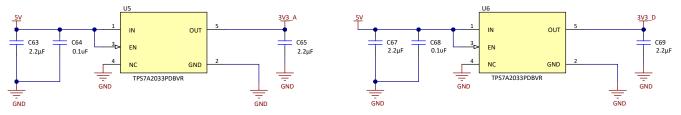

Two LDOs are used to generate a 3.3-V analog and a 3.3-V digital rail.

Figure 3-10. LDOs for Analog and Digital 3.3-V Rails

# 3.4.2 Gate Driver Bias Power Supply

The UCC14141 device is selected as an isolated bias supply. This is a isolated bias module with an integrated transformer, offering the smallest footprint and height. The output is configured in a dual rail configuration to +15 V and -4 V. The maximum power drawn per device is calculated using the UCC14141-Q1 calculator tool available on the product folder. With this the value of the current-limiting resistor (RLim) (RLIM in Figure 3-11). Here 1 k $\Omega$  is selected for the devices only supplying one gate driver and 600  $\Omega$  is selected for the devices supplying one gate driver and the high side of the isolated sensing. Each output is connected to an LED indicating that isolated power is present. There are precautions on the board to share the isolated bias supply between the two low-side FETs on each side. For this jumper the resistors need to be placed and RLim needs to be adjusted. This is not tested yet. Additionally there is the option to populate a bootstrap supply for the high-side FETS, which is also not yet tested.

Figure 3-11. Gate Driver Bias Supply Circuit

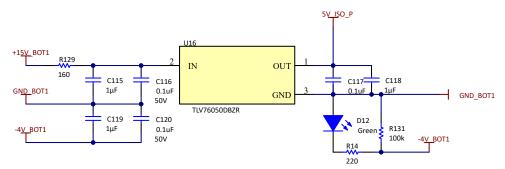

# 3.4.3 Isolated Power Supply for Sense Circuits

To generate the isolated supply for the isolated amplifiers and modulators the low-side gate driver bias supply is reused. The 15-V isolated rail is converted down to a 5-V rail using a TLV760 with fixed 5-V output. A series resistor is used at the input to reduce the power dissipated in the LDO.

Figure 3-12. Supply for Voltage and Current Sense Derived From Gate Driver Bias Supplies

# 3.5 Gate Driver Circuit

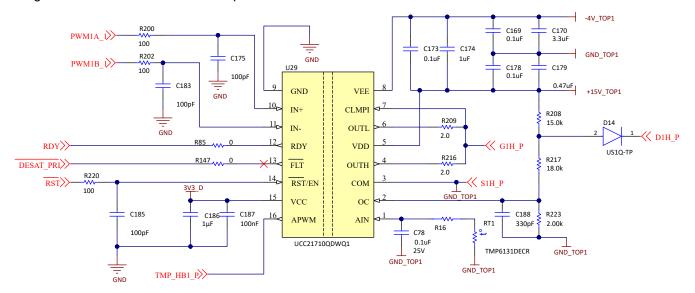

The UCC21710 is used as a gate driver. This device was selected for the integrated features for SiC, like DESAT protection, internal active Miller clamp and soft turn-off. The PWM interlock makes sure that at no time both complimentary PWMs of on H-Bridge are turned on. The analog-to-PWM channel, can be used for isolated temperature sensing on the high side. The DESAT voltage was configured to 6.4 V with a blanking time of 1 µs using the UCC217xx XL Calculator Tool available in the device product folder. The undervoltage lockout function of UCC21710 is used to check if both the isolated power (VCC ) and the non isolated power (VCC) are in a valid range which is indicated on the RDY pin.

Figure 3-13. UCC21710 Gate Drive Circuit

# **3.6 Additional Circuitry**

The isolated CAN transceiver ISOW1044 is used to enable CAN communication. The device is connected to the MCU through the D-Sub 9 pin connector. CAN Communication is not implemented in the current state of this design.

The TMUX1204 is used to interface the outputs of UCC21710 APWM channels to the control card connector. SN74LVC126A buffers are used to redrive the PWM signals.

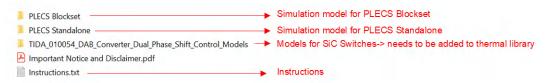

#### 3.7 Simulation

To support evaluation of this reference design, a PLECS simulation deck is provided in the product folder. This simulation can be used to evaluate both single-phase shift and extended- phase shift modulation, in regards to efficiency and thermal behavior. The simulation is available for PLECS standalone and PLECS Blockset in combination with MATLAB and Simulink.

#### Note

PLECS is a third party tool. The tool is available as PLECS Blockset (MATLAB Simulink extension) or standalone. For more information, see plexim.com.

### 3.7.1 Setup

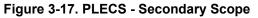

Figure 3-14 shows the folder structure of the downloadable file.

Figure 3-14. PLECS Simulation - Folder Overview

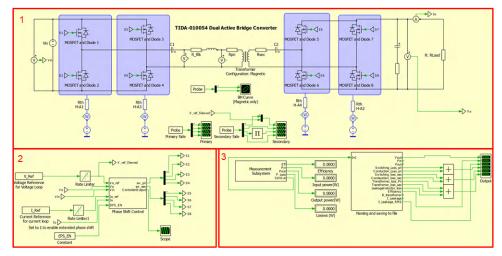

Figure 3-15. PLECS Simulation Deck

The PLECS simulation deck consists of three major parts:

- 1. Power converter:

- a. Contains power converter, with manufacturer silicon carbide field-effect transistor (SiC-FET) models

- b. Heat sinks, the setup is similar to TIDA-010054 for thermal analysis

- c. Primary scope for analyzing switch node waveforms

- d. Secondary scope to analyze output voltage, current, and power

- e. BH Curve to analyze magnetic behavior of the transformer

- 2. Phase shift control:

- a. Contains controller for voltage and current loop. Allows to switch between voltage and current loop by opening Phase Shift Control block and changing the configuration of the controller.

- b. Extended phase shift modulation can be enabled by setting EPS\_EN = 1 in the initialization script.

- 3. Measurement subsystem:

- a. Measures and adds up losses in the system, to calculate efficiency

- b. Displays to see input power. Output power efficiency and losses while simulation is running

- c. Naming and saving to a file block, to name signals from the measurement subsystem and enabling to save to Microsoft<sup>®</sup> Excel<sup>®</sup> file (only for the standalone version)

# 3.7.2 Running Simulations

This section contains instructions for PLECS using the Blockset and standalone setup.

#### Instructions PLECS Blockset:

- 1. Open both TIDA\_010054\_DAB\_Converter\_Parameters.m and TIDA\_010054\_DAB\_Converter\_Simulation.slx files in MATLAB

- 2. Open the PLECS circuit in TIDA\_010054\_DAB\_Converter\_Simulation.slx

- 3. Add the TIDA\_010054\_DAB\_Converter\_Models folder to the thermal library (File  $\rightarrow$  PLECS Preferences  $\rightarrow$  Thermal  $\rightarrow$  (Press the plus sign))

- Run TIDA\_010054\_DAB\_Converter\_Parameters.m to populate parameters in the MATLAB workspace. These can be modified to simulate different operation points or to enable and disable extended-phase-shift control (EPS\_EN = 1 or EPS\_EN = 0)

- 5. Run simulation either by pressing Run in TIDA\_010054\_DAB\_Converter\_Simulation.slx or by pressing Simulation → Run in the PLECS Simulation Deck

- 6. Simulation can be observed in scopes and displays within the PLECS circuit

### Instructions PLECS Standalone:

- 1. Open the TIDA\_010054\_DAB\_standalone.plecs file in PLECS

- 2. Add the TIDA\_010054\_DAB\_Converter\_Models folder to the thermal library (File  $\rightarrow$  PLECS Preferences  $\rightarrow$  Thermal  $\rightarrow$  (Press the plus sign))

- Initialization is found under Simulation → Simulation parameters → Initialization. These can be modified to simulate different operation points or to enable and disable extended-phase-shift control (EPS\_EN = 1 or EPS\_EN = 0)

- 4. Run the simulation by pressing Simulation  $\rightarrow$  Run in the PLECS Simulation Deck

- 5. Simulation can be observed in scopes and displays within the PLECS circuit

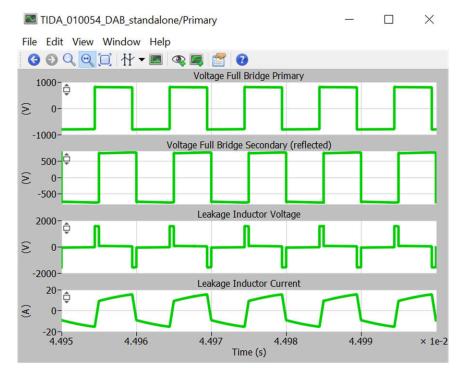

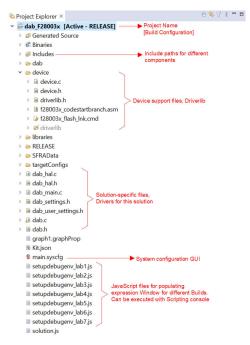

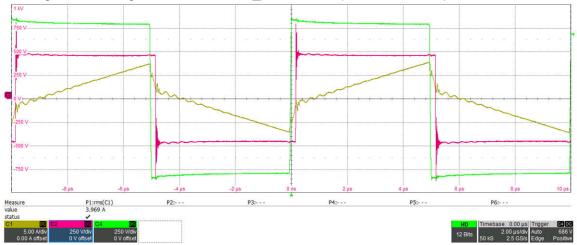

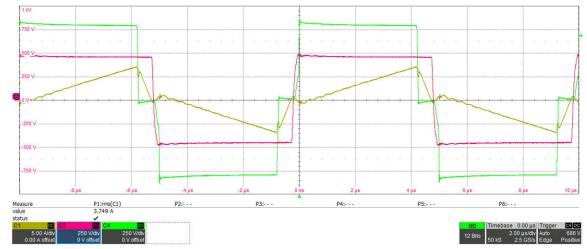

Figure 3-16 shows the primary scope. Use this scope to evaluate the switching waveforms.

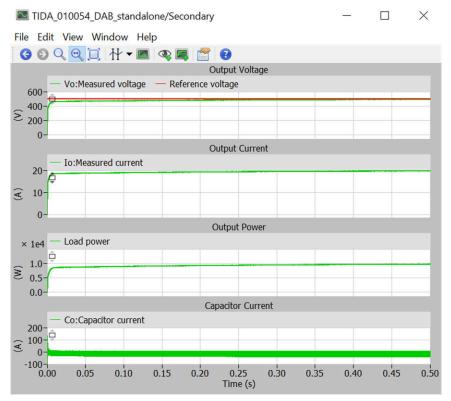

Figure 3-17 shows the secondary scope. Use this window to observe output voltage, current, and power, as well as the output voltage ripple and capacitor current.

Figure 3-16. PLECS - Primary Scope

#### Note

This simulation deck is for system level evaluation. Not all parasitic effects can be simulated accurately. Simulation results can vary from measurement results.

For example, SiC-FET manufacturer models do not include output capacitances. Therefore, softswitching is achieved down to very light loads in simulation. Efficiencies under light load vary from actual measurements.

# 4 Hardware, Software, Testing Requirements, and Test Results

# 4.1 Required Hardware and Software

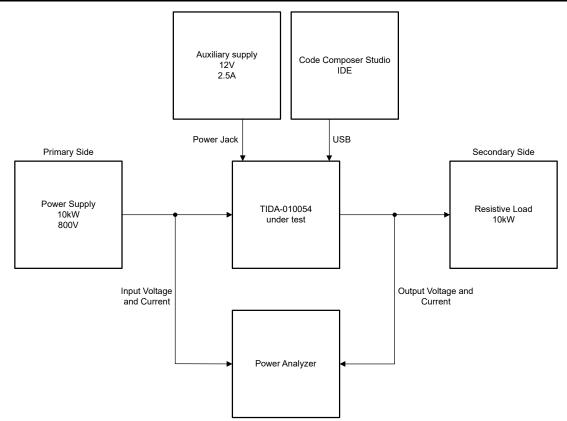

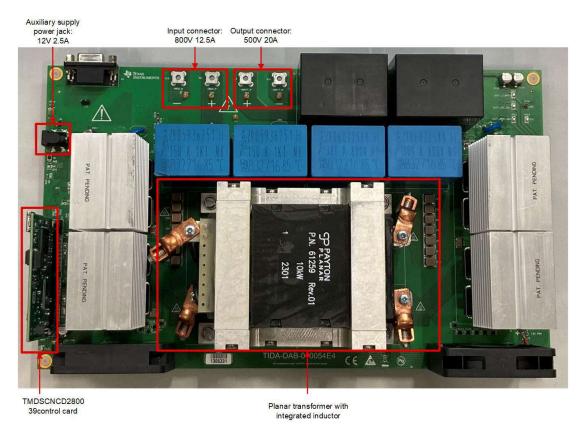

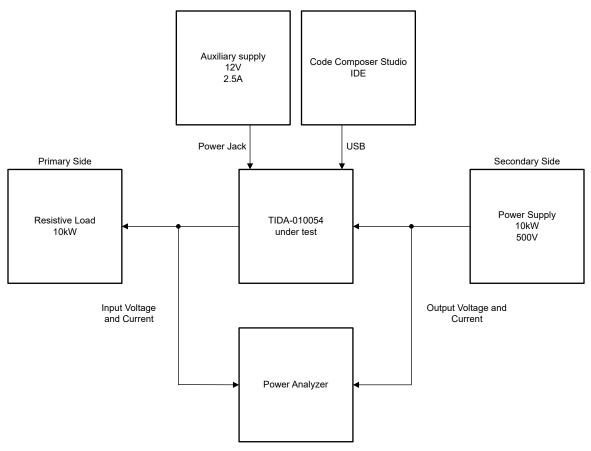

### 4.1.1 Hardware

The following hardware is required for this reference design:

- One TIDA-010054 power board

- One TMDSCNCD280039C control card

- USB Type-C<sup>®</sup> cable

- Laptop

The following test equipment is needed to power and evaluate the DUT:

- 10-kW DC source capable of delivering voltage between 700 V-800 V at required current

- 10-kW resistive load bank

- Power analyzer

- Auxiliary power supply with jack connector 12-V, 2.5-A rated

- Oscilloscope

- Isolated voltage probes and current probes

### 4.1.2 Software

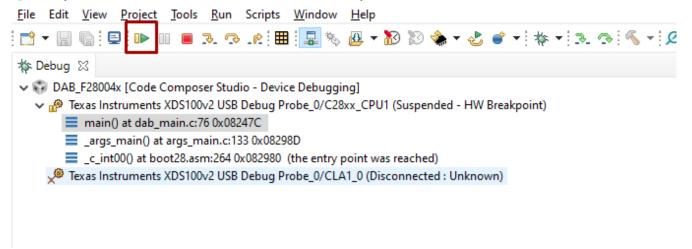

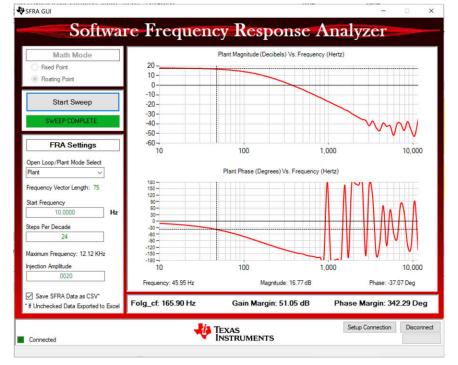

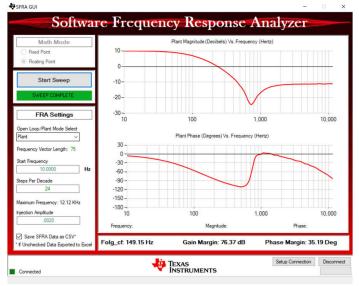

Code Composer Studio<sup>™</sup> with C2000 powerSUITE and C2000WARE-DIGITALPOWER-SDK used in this design.

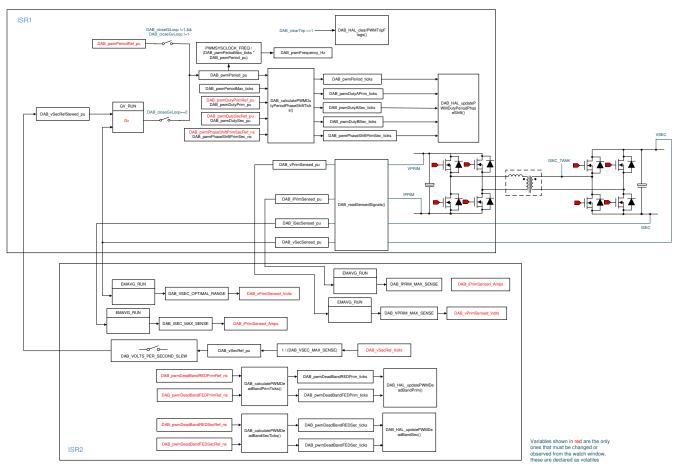

The general structure of the project follows C2000Ware-DigitalPower-SDK Structure. For this design, <solution> is "DAB". The solution name is also used as the module name for all the variables and defines used in the solution. Hence, all variables and function calls are prepended by the DAB name (for example, DAB\_vSecSensed\_pu). This naming convention lets the user combine different solutions while avoiding naming conflicts.

- 1. The "<solution>.c/h" are solution-specific and device-independent files that consist of the core algorithmic code.

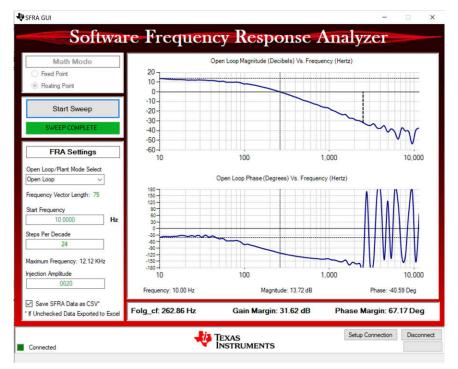

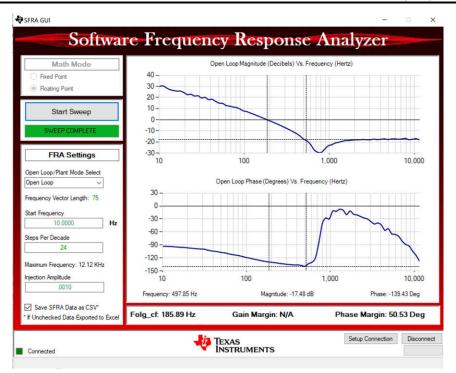

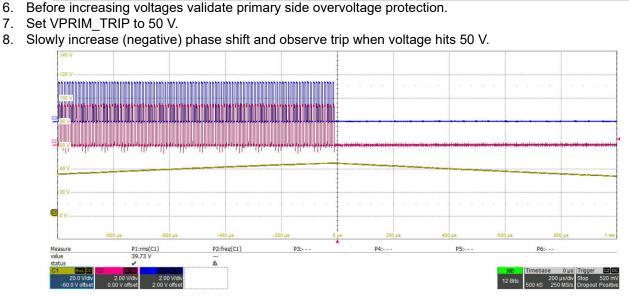

- 2. The "<solution>\_board.c/h" are board-specific and device-dependent. This file consists of device-specific drivers to run the solution. If the user wants to use a different modulation scheme or a different device, the user is required only to make changes to these files, besides changing the device support files in the project.