# Design Guide: TIDM-02013 7.4-kW EV or HEV Bidirectional Onboard Charger Reference Design With GaN

# Description

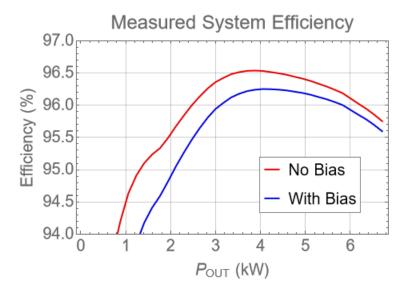

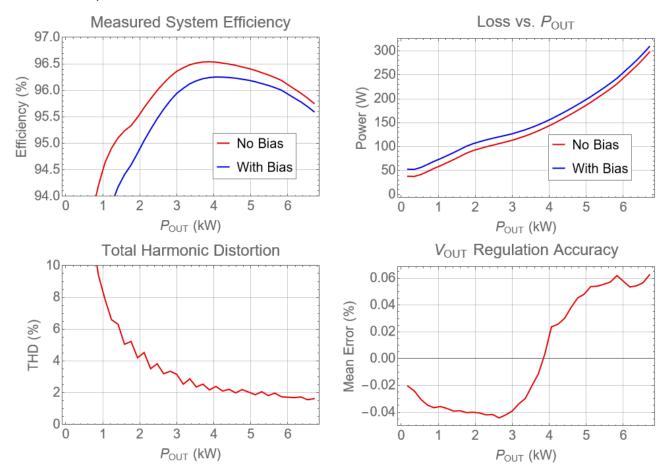

The PMP22650 reference design is a 7.4-kW, bidirectional, onboard charger. The design employs a two-phase totem pole PFC and a full-bridge CLLLC converter with active synchronous rectification. The CLLLC uses both frequency and phase modulation to regulate the output across a wide voltage range. This design uses a single TMS320F280039C microcontroller to control both the PFC and DCDC stages. This design is also supported with a TMS320F28P65x microcontroller. High density is achieved through the use of high-speed GaN switches (LMG3522-Q1). A peak system efficiency of 96.5% was achieved with an open-frame power density of 3.8 kW/L.

This design illustrates control of this power topology using a single C2000<sup>™</sup> MCU in closed voltage and closed current-loop mode. The hardware and software available with this design help accelerate your time to market.

## Resources

TIDM-02013, PMP22650 TMS320F280039C, TMS320F28P650DK AMC3330-Q1, AMC3302-Q1, UCC21222-Q1 C2000WARE-DIGITAL-POWERSDK TMDSCNCD280039C, TMDSCNCD28P65X Design Folder Product Folder Product Folder Software Folder Tool Folder

## Features

- Power Max: 7.4 kW, 96.5% peak efficiency

- VAC 90–264V AC: 240V AC TYP

- Vprim: 400 V DC nominal; Vsec: 250-450 V DC

- CLLLC resonant tank with 500-kHz nominal PWM switching (200 kHz–800 kHz range) enables higher power density

- Soft switching with Zero Voltage Switching (ZVS) on the primary; Zero Current Switching (ZCS) and ZVS on the secondary enable higher efficiency

- Active synchronous rectification scheme implementation using Rogowski coil sensor enables higher efficiency

- Software support for TMS320F28003x device with the Control Law Accelerator (CLA), which enables integrated OBC design with AC-DC and DC-DC controlled using a single C2000 MCU

- Software support for TMS320F28P65x device with one CPU (CPU1) controlling AC-DC and DC-DC stages is provided.

- Reduced CPU overhead with the new hardware oversampling feature of TMS320F28P65x

## Applications

- Hybrid, Electric, and Powertrain Systems

- DC Fast Charging Station

- Power Conversion System (PCS)

# 1 CLLLC System Description

Onboard chargers (OBCs) are an essential part of Electric Vehicles (EVs) and Hybrid Electric Vehicles (HEV). An OBC typically consists of an AC-DC [power factor correction (PFC) rectifier stage] and an isolated DC-DC converter, as shown in Figure 1-1. C2000 MCUs are designed to implement advanced digital power control that automotive applications demand; for more information, see C2000 Digital Power and C2000 EV.

Figure 1-1. Typical OBC Architecture

The ability to charge the battery fully overnight is highly desired for most EV Level 1 and Level 2 chargers. With battery capacity increasing, the OBCs need to be designed for even higher power. With the increasing power capacity of the OBC, specifications such as power density and efficiency are even more important, due to limited space and cooling capacity in the car.

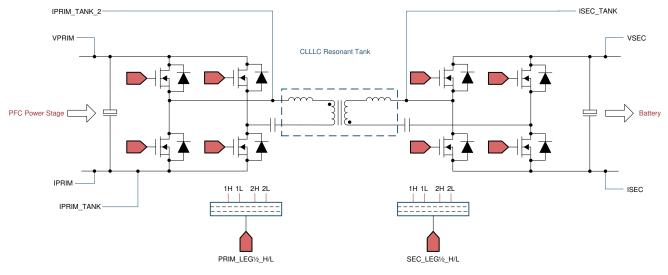

The CLLLC (Capacitor-Inductor-Inductor-Inductor-Capacitor)—with its symmetric tank, soft switching characteristics, and ability to switch at higher frequencies—is a good choice for these applications. In this design, control and implementation of a CLLLC topology, as shown in Figure 1-2, is illustrated.

Figure 1-2. CLLLC Topology for Isolated DC-DC Converter

The nomenclature for Figure 1-2 is as follows:

| VPRIM                    | Primary side voltage (typically comes from a PFC converter)                                                                                                                                                                                                                |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IPRIM                    | Return current of the primary side, can be used for protection and monitoring.                                                                                                                                                                                             |

| IPRIM_TANK, IPRIM_TANK_2 | Tank current on the primary side, two methods to sense using shunt current sense and<br>other is Rogowski's coil. Only one is needed, used to implement synchronous rectification<br>in the reverse direction for example, secondary to primary. Also used for protection. |

| VSEC                     | Secondary side voltage (typically, a battery)                                                                                                                                                                                                                              |

| ISEC                     | Return current of the secondary side, used to implement the battery current control loop.                                                                                                                                                                                  |

| ISEC_TANK                | Tank current on the secondary side, used to implement the synchronous rectification for<br>the forward direction power flow for example, primary to secondary.                                                                                                             |

| PRIM_LEG1/2_H/L          | PWMs for the primary side full bridge                                                                                                                                                                                                                                      |

| SEC_LEG1/2_H/L           | PWMs for the secondary side full bridge                                                                                                                                                                                                                                    |

|                          |                                                                                                                                                                                                                                                                            |

## 1.1 Key System Specifications

The CLLLC reference design power specifications are listed in Table 1-1.

| Table 1-1. Key System Specifications |                                         |  |

|--------------------------------------|-----------------------------------------|--|

| PARAMETER SPECIFICATIONS             |                                         |  |

| Prim Voltage (Vprim)                 | 400 V–450 V DC (average)                |  |

| Sec Voltage (Vsec)                   | 250 V–450 V DC<br>Max                   |  |

| Power Rating forward                 | 7.4 kW                                  |  |

| Output Current (I <sub>OUT</sub> )   | 20<br>A Max                             |  |

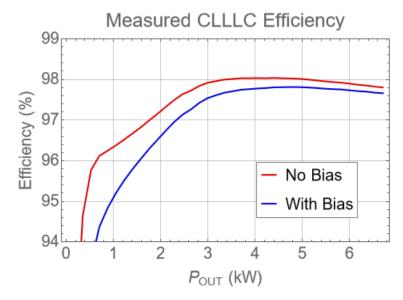

| Efficiency (CLLLC)                   | Peak 98%                                |  |

| PWM Switching Frequency              | 500 kHz Nominal (200 kHz–800 kHz Range) |  |

#### WARNING

TI intends this reference design to be used only by *qualified engineers and technicians* familiar with risks associated with handling high-voltage electrical and mechanical components, systems, and subsystems.

There are *accessible high voltages present on the board*. The board operates at voltages and currents that may cause shock, fire, or injury if not properly handled or applied. Use the equipment with necessary caution and appropriate safeguards to avoid injuring yourself or damaging property.

#### CAUTION

Do not leave the design powered when unattended.

#### WARNING

**High voltage!** There are accessible high voltages present on the board. Electric shock is possible. The board operates at voltages and currents that may cause shock, fire, or injury if not properly handled. Use the equipment with necessary caution and appropriate safeguards to avoid injuring yourself or damaging property. For safety, use of isolated test equipment with over-voltage and over-current protection is highly recommended.

TI considers it the user's responsibility to confirm that the voltages and isolation requirements are identified and understood before energizing the board or simulation. *When energized, do not touch the design or components connected to the design.*

#### WARNING

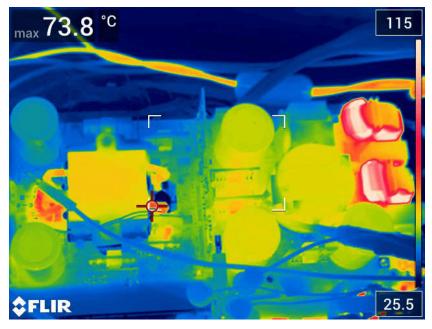

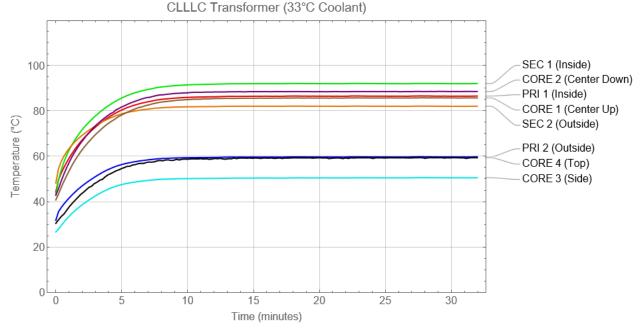

Hot surface! Contact may cause burns. Do not touch!

Some components may reach high temperatures >55°C when the board is powered on. The user must not touch the board at any point during operation or immediately after operating, as high temperatures may be present.

# 2 CLLLC System Overview

# 2.1 Block Diagram

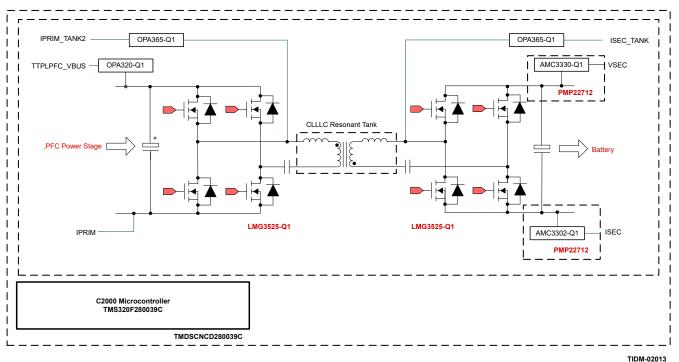

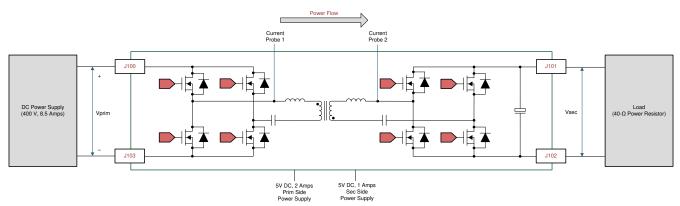

Figure 2-1 shows the block diagram of the CLLLC topology.

## Figure 2-1. CLLLC Block Diagram

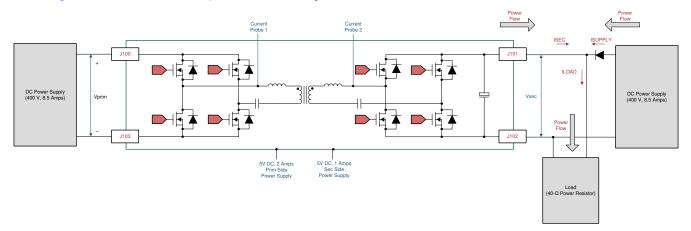

This reference design uses the following EVMs and PMP designs to achieve operation as documented in this guide:

- 1. OBC Base Board: PMP22650( with PMP22712 +PMP22773 Daughter cards)

- 2. F280039C controlCARD Evaluation Module: TMDSCNCD280039C

The following sections discuss details of the hardware, software, and system design.

## 2.2 Design Considerations and System Design Theory

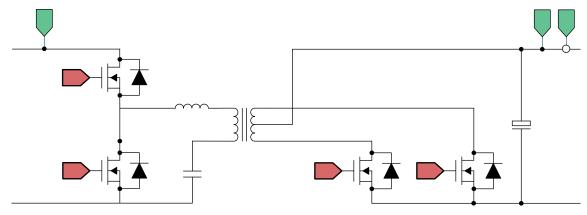

LLC converters are widely popular due to their ability to achieve ZVS at the primary side, and ZCS on the secondary side. A typical LLC Series Resonant Converter (SRC) is shown in Figure 2-2. The primary side of this converter is half bridge; thus, the transformer utilization from a Volt-sec perspective is half. In addition, the current rating for the switches is twice of what is needed, compared to when a full-bridge structure is used.

Figure 2-2. LLC Half-Bridge SRC

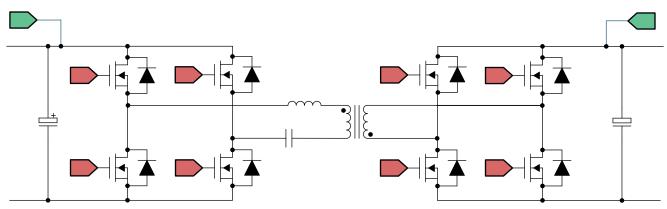

Although half-bridge LLC SRCs are attractive at lower power for cost reasons, for high-power and high-density applications, a full-bridge LLC SRC is desired for the following reasons:

- 1. A full-bridge LLC converter better utilizes the magnetic core of the transformer on both the secondary side and primary side; therefore, it is able to offer better power density.

- 2. A full-bridge LLC converter reduces current rating; and therefore, reduces the cost of copper in wires. The converter also enables higher power (compared to half-bridge SRCs) to be achieved with the same copper wires.

Figure 2-3. Full-Bridge LLC Converter

A full-bridge LLC converter, as shown in Figure 2-3, falls under the broad category of Dual Active Bridge (DAB) converters. Under DAB converters, the converter can be classified on the basis of model or operation:

- 1. A phase-shifted DAB converter is one of the most popular converters historically.

- 2. Resonant DAB converters have different variants on resonant tanks (LC, LLC, CLLC, CLLLC, and so forth).

Resonant DAB converters are of interest because high efficiency, high power, and high density are achievable with such converters. CLLLC, with its symmetric tank, is capable of bidirectional operation. The problem with using an LLC structure for bidirectional use is that the switching frequency, when operating in the reverse power flow mode, is governed by the transformer winding capacitance and the leakage inductance. This offers little or no control on the gain of the power stage and the switching frequency. Therefore, the CLLLC type of structure is preferred as it offers much better control on the switching frequency and an additional degree of freedom on the gain.

#### 2.2.1 Tank Design

In this section, the tank parameter selection for the CLLLC is discussed based on the voltage gain desired, soft switching characteristics, and an appropriate power profile is selected for the charger based on CLLLC.

For additional calculations and information, refer to the following files located inside the software install package at C2000Ware\_DigitalPower\_SDK\_<ver>/solution/tidm\_02013/hardware/

## 2.2.1.1 Voltage Gain

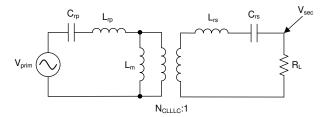

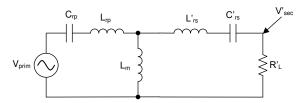

To understand tank design, first the gains for both battery-charging mode and reverse-power-flow mode must be analyzed with First Harmonic Analysis (FHA) using first harmonic approximation. The simplified diagram of the resonant tank is given in Figure 2-4.

Figure 2-4. FHA Model for CLLLC Resonant Tank During Battery Charging Mode (BCM)

where  $\mathsf{R}_{L\_dc}$  is the DC resistive load at the

## The nomenclature for Figure 2-4 is as follows:

| V <sub>prim</sub><br>(TTPLPFC_V <sub>BUS</sub> ) | Voltage input at primary side                        |

|--------------------------------------------------|------------------------------------------------------|

| L <sub>rp</sub>                                  | Primary side resonant inductor                       |

| C <sub>rp</sub>                                  | Primary side resonant capacitor                      |

| N <sub>CLLLC</sub>                               | Turns ratio of the transformer                       |

| L <sub>m</sub>                                   | Magnetizing inductor                                 |

| V <sub>sec</sub>                                 | Voltage output at secondary side                     |

| L <sub>rs</sub>                                  | Secondary side resonant inductor                     |

| C <sub>rs</sub>                                  | Secondary side resonant capacitor                    |

| R <sub>L</sub>                                   | Effective load seen with FHA on the secondary output |

$$\mathsf{R}_{\mathsf{L}} = \left(\frac{8}{\pi^2}\right) \mathsf{R}_{\mathsf{L}_{\mathsf{d}}\mathsf{d}}$$

Note here the effective  $R_L$  is accounted for as output.

Referring to secondary side quantities on the primary side,

- $L_{rs}$ ' is equal to  $L_{rs}$  \*  $N_{CLLLC}$  \*  $N_{CLLLC}$  $C_{rs}$ ' is equal to  $C_{rs}$  / ( $N_{CLLLC}$  \*  $N_{CLLLC}$ )  $R_{L}$ ' is equal to  $R_{L}$  \* ( $N_{CLLLC}$  \*  $N_{CLLLC}$ )  $V_{rs}$ ' is equal to  $V_{rs}$  \*  $N_{CLLLC}$

Figure 2-5. FHA CLLLC With Quantities Referred to Primary Side in BCM

Using KCL and KVL, the gain equation can be written as Equation 1.

$$\frac{V_{sec}}{V_{prim}} = \frac{\left[Z_m \mid\mid \left(Z_{rs}' + R_L'\right)\right]R_L'}{\left(Z_{rp} + \left[Z_m \mid\mid \left(Z_{rs}' + R_L'\right)\right]\right)\left(Z_{rs}' + R_L'\right)N_{CLLLC}}$$

(1)

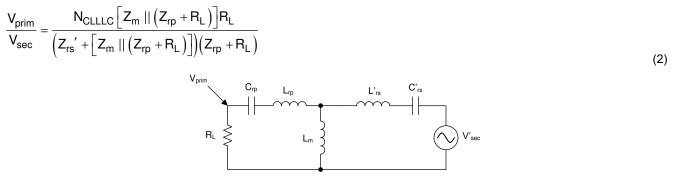

Similarly, for the reverse power flow, the circuit can be simplified as shown in Figure 2-6, and the gain can be written as Equation 2.

Figure 2-6. FHA Model for Gain Calculation in RCM

Equation 1 and Equation 2 are used in the following section to study the voltage gain based on the parameters selected for the design.

## 2.2.1.2 Transformer Gain Ratio Design (N<sub>CLLLC</sub>)

Resonant converters are typically most efficient when operating at or near the resonant frequency. Since this is a bidirectional battery charger, this design needs to cover a range of output voltages. This implies that *n* should be chosen such that the converter operates at as low a current as possible to help reduce  $I^2R$  losses. Following this design concept the highest output current will occur at the lowest output voltage at which you need to supply full power. We will set *n* at this point such that the converter operates as close to resonance as possible. In this design this works out to be a turns ratio of 1.1:1. This enables the lowest losses while still allowing for a wide output voltage range.

## 2.2.1.3 Magnetizing Inductance Selection (L<sub>m</sub>)

To ensure ZVS operation of the primary side FETs, we need to make sure the energy stored in the resonant tank is greater than the energy stored in the FET output capacitors. We can use Equation 3 to determine the needed  $L_m$  for full-bridge LLC SRCs.

$$L_{m} \leq \frac{Tt_{dead}}{16 * C_{oss}}$$

(3)

where the intended switching frequency for the converter is 500 kHz, hence T =  $1/(500 \times 10^3)$ , and based on the power device. Selected parameters such as  $t_{dead}$  and  $C_{oss}$  can also be identified from the power device data sheet. Typically, the effective  $C_{oss}$  must be calculated using curve fitting. On this design, based on the design parameters discussed,  $L_m$  must be less than 20 µH. In addition to what is accounted for in the above calculation, there is inter-winding capacitance in a real transformer that needs to be discharged by the resonant tank current. Therefore, using simulation, a value of 14 µH was selected to ensure ZVS across the operating range of the converter; this value is used in the subsequent selection processes.

## 2.2.1.4 Resonant Inductor and Capacitor Selection (L<sub>rp</sub> and C<sub>rp</sub>)

While selecting  $L_{rp}$ , the ratio of  $L_m$  to  $L_{rp}$  is widely used as a design parameter,

$$L_{n} = \frac{L_{m}}{L_{rp}}$$

(4)

The L<sub>n</sub> value is selected such that it ensures the voltage gain in the resonant tank is enough across the operating range of the converter. In this design, as the input voltage comes from a PFC stage and will have a estimated 10% ripple, a gain variation of at least 10% is needed. With this criteria in mind and the fact that L<sub>n</sub> should be kept higher to reduce the inductor value, and hence the losses, L<sub>n</sub> equal to 14 is selected for this design, based on the plot of the FHA with L<sub>n</sub> varying with load (see Figure 2-7).

Figure 2-7. CLLLC Tank Gain Variation With L<sub>n</sub> Varying

Now that the selection of  $L_n$  is made,  $L_{rp}$  can be calculated using Equation 4.  $L_{rp}$  and  $C_{rp}$  determine the series resonant frequency of the converter and they are related by Equation 5.

$$f_{res} = \frac{1}{2\pi \sqrt{L_{rp}C_{rp}}}$$

(5)

Equation 5 can then be used to calculate the  $C_{rp}$  needed on the design. However, due to component availability, the next closest value of  $C_{rp}$  is used on the design. With these component values, the BCM gain is shown in Figure 2-7.

In Figure 2-7, as the load increases (that is,  $R_{L_{dc}}$  goes lower), the gain curve becomes non-monotonic in the region below series resonant frequency. This can lead to the loss of ZVS on the primary FETs and, more critically, the loss of control. Therefore assuming maximum load at nominal Vout, the load is limited or clamped to  $R_{L_{dc}} = 30 \Omega$ , for which the gain is monotonic (see Figure 2-7).

Additionally Figure 2-7 shows that in BCM we have enough gain across our operating frequency of 200kHz to 800kHz to cover all operating conditions. Lastly, it is worth noting that if the PFC ripple can be reduced then the totally expected input range will also reduce. This causes the required gain range to reduce, and ultimately helping to reduce the frequency variation needed to support all load conditions.

## 2.2.2 Current and Voltage Sensing

In the following sections, the sensing scheme for different currents and voltages on the design are discussed. On the design, multiple schemes are implemented so that users can select the appropriate schemes for their application needs.

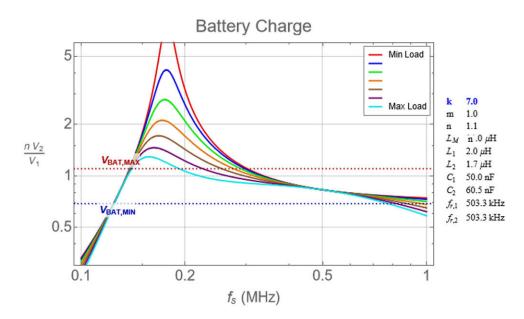

## 2.2.2.1 VPRIM Voltage Sensing

8

The C2000 MCU is biased on the primary side; hence, the primary voltage is sensed by a resistor divider to the ground of the board. As oversampling is used, an op amp in voltage follower arrangement is used to buffer the signal for the ADC as shown in Figure 2-8. The buffer helps reduce impedance as seen by the ADC, and hence, a faster sampling rate can be used. Otherwise, the sampling will be limited by the time constant of the resistor divider resistance, which is typically high, and hence, only slow sampling can be done.

7.4-kW EV or HEV Bidirectional Onboard Charger Reference Design With GaN

Figure 2-8. VPRIM Voltage Sensing Circuit

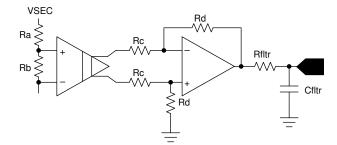

## 2.2.2.2 VSEC Voltage Sensing

The secondary side voltage is sensed in an isolated manner using the AMC3330-Q1, as shown in Figure 2-9.

Figure 2-9. VSEC Voltage Sensing Circuit

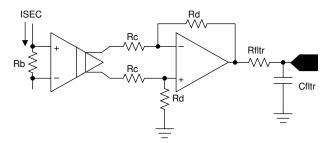

## 2.2.2.3 ISEC Current Sensing

The secondary side output current is also sensed in an isolated manner using the AMC3302-Q1, as shown in Figure 2-10.

Figure 2-10. ISEC Current Sensing Circuit

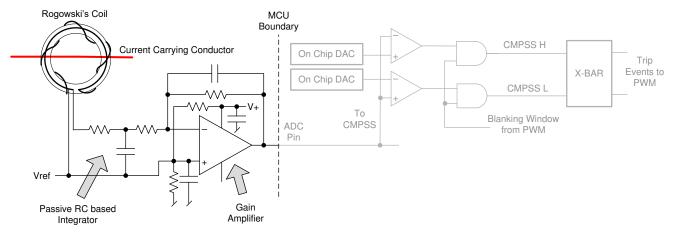

## 2.2.2.4 ISEC TANK and IPRIM TANK

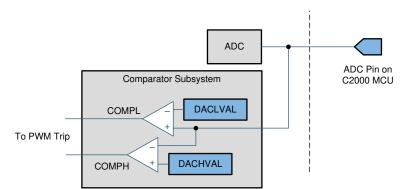

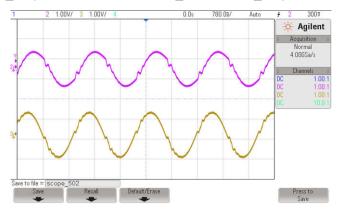

A Rogowski coil-based sensing mechanism is chosen to sense the high-frequency current in the tank on the primary side and the secondary side in an isolated manner, as shown in Figure 2-11. The ADC pin is internally connected to the Comparator Subsystem (CMPSS), which can generate the correct pulses that go through the X-Bar to the PWM to get the action required for synchronous rectification.

Figure 2-11. ISEC Tank Current Sensing Using Rogowski's Coil

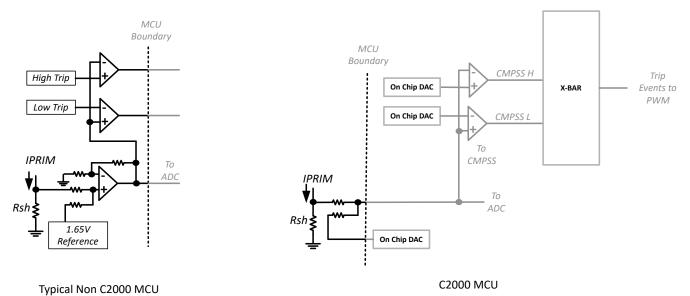

## 2.2.2.5 IPRIM Current Sensing

The primary side current, IPRIM, is sensed using LMV796-Q1.(see Figure 2-12).

#### Figure 2-12. IPRIM Current Sensing Circuit, Comparison With Typical MCU vs. C2000 MCU

#### 2.2.2.6 Protection (CMPSS and X-Bar)

Most power electronics converters need protection from overcurrent events. For this design, multiple comparators are needed, and references for the trip points need to be generated. Using C2000 MCUs—such as TMS320F280039, which has an on-chip windowed comparator as part of the Comparator Subsystem (CMPSS) along with 12-bit DACs for trip set points—that are internally connected to the PWM module enables fast tripping of the PWM without the need of external hardware. This saves board space and cost in the end application as extra components can be avoided by using on-chip resources such as DAC, comparators, and ADC. All of these resources can be used together and at the same time, without any extra external connections. Furthermore, the CMPSS-generated signals go to the X-Bar, where they can be combined in different and unique fashions to flag unique trip events from multiple sources.

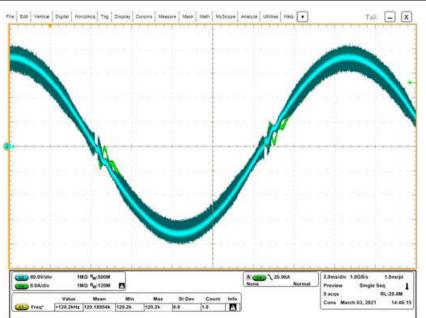

## 2.2.3 PWM Modulation

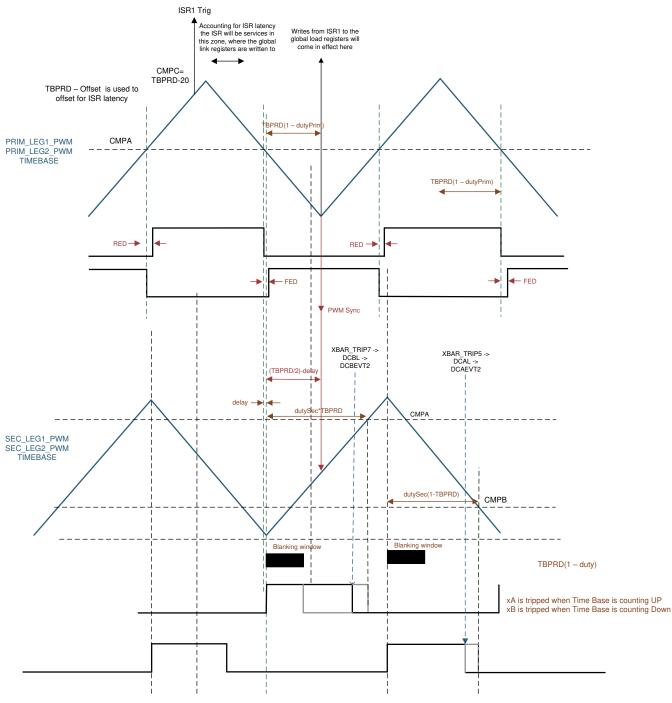

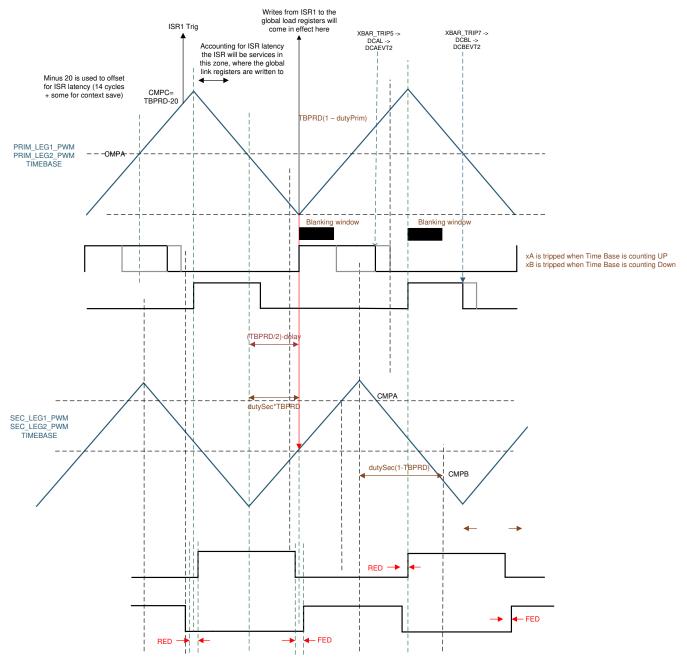

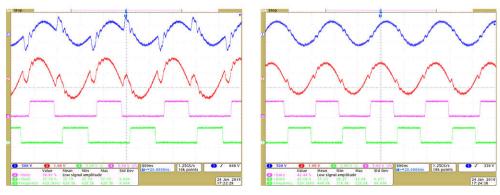

Figure 2-14 shows the PWM waveform configuration used on this design.

High-resolution PWM is used for the primary legs and the secondary legs. Up-down count mode is used to generate the PWMs. To use the high-resolution PWMs, the PRIM\_LEG1\_H PWM pulse is centered on the period event and the time base is configured to be up-down count. A complementary pulse with high-resolution dead time is then generated for the complementary switch. Between LEG1 and LEG2, there is a 180-degree phase shift for a full-bridge operation. This is achieved by using the feature on the PWM module to swap the xA and xB output. (Alternatively, a phase shift can also be implemented, but is not needed on this design.)

The PWM pulse to the secondary side goes through an isolator, which adds additional propagation delay. To account for this propagation delay, a small advance of the PWM is required. This is implemented in form of a phase-shift delay with respect to the primary active PWM pulse's falling edge. The phase shift of the secondary side is a combination of the period and the delay needed for the isolator, as shown in Figure 2-14. As active synchronous rectification scheme is used, the rising edge is controlled by the primary side PWM switch timing. As the switching event can be noisy, a blanking window is used. The current in the secondary tank can be discontinuous depending on the operating frequency and load. Hence, the falling edge is controlled by the trip action that is triggered as soon as the secondary current reaches zero. The trip is then latched until the next zero or period event to avoid any spurious turn on of the secondary side switches because of noise. The blanking pulse is generated by the PWM time base but the trip latch and the blanking actions happen as part of the CMPSS. Depending on whether it is the positive half or the negative half of the tank current, two different trip signals are generated and sent to the PWM module through the X-Bar. The Type-4 PWM on the C2000 MCU can uniquely use these events to trip the xA pulse during the up count and xB during the down count. For details, refer to the code in the function CLLLC\_HAL\_setupSynchronousRectificationAction(), which is the HAL file for the solution, see Section 5.1.2.

The global link mechanism on the Type-4 PWM is used to reduce the number of cycles needed to update the registers and enables high-frequency operation. For example, the following code in the CLLLC\_HAL\_setupPWM() function links the TBPRD registers for all the PWM Legs. Using this linkage, a single write to the PRIM\_LEG1 TBPRD register will write the value to PRIM\_LEF2, SEC\_LEG1, and SEC\_LEG2.

EPWM\_setupEPWMLinks(CLLLC\_PRIM\_LEG2\_PWM\_BASE, EPWM\_LINK\_WITH\_EPWM\_1, EPWM\_LINK\_TBPRD);

EPWM\_setupEPWMLinks(CLLLC\_SEC\_LEG1\_PWM\_BASE, EPWM\_LINK\_WITH\_EPWM\_1, EPWM\_LINK\_TBPRD);

High-resolution PWM relies on carrying forward remainder calculation from the previous cycle into the next; hence, a periodic sync should not be used between the primary and secondary side PWMs to maintain the phase relation. Whenever a frequency change or duty change is detected, a one-time sync is issued using a fast interrupt service routine (ISR1, see Section 5.1.2.2).

Figure 2-14. PWM Scheme Used on CLLLC Design With Active Synchronous Rectification with Power Flow Primary to Secondary

Similarly for the reverse power flow direction, the PWM configuration used is shown in Figure 2-15

Figure 2-15. PWM Scheme Used on CLLLC Design With Active Synchronous Rectification with Power Flow Secondary to Primary

# **3 Totem Pole PFC System Description**

Let surface! Contact may cause burns. Do not touch! Some components may reach high temperatures > 55°C when the board is powered on. The user must not touch the board at any point during operation or immediately after operating, as high temperatures may be present.

## 3.1 Benefits of Totem-Pole Bridgeless PFC

All plug-in hybrid electric vehicles (PHEVs) require an onboard charger (OBC) between the power grid and the high-voltage battery pack located inside the vehicle. Implementing a power factor correction (PFC) converter is mandatory to connect directly to the power grid for AC/DC power conversion and maximize the real power that flows to the downstream DC/DC converters.

Conventional PFC converters implement a passive diode bridge for rectification, which is now known as a passive PFC technique. The advantages of such a scheme are: simple design, reliability, slow-system control loop, and low cost. However, the disadvantages are also very obvious: the passive components are heavy with a low-power factor and generate significant power losses, which results in bulky heat sinks and a lot of heat dissipation. Further investigation into the matter shows that an input bridge consumes approximately 2% of the input power at the low line of a wide mains application. If the designer can suppress one of the series diodes, then they can save 1% of the input power, which allows the efficiency to rise from 94% to 95% (Turchi; Dalal; Wang; Lenck 2014). Due to previously-mentioned drawbacks, the power rating of bridged traditional PFCs is limited under hundreds of watts, especially in a hybrid-electric vehicle (HEV) or electric vehicle (EV) where reduced space and weight are the key design parameters.

As a result, the trend continues to move toward a bridgeless architecture with the elimination of the traditional diode bridge. The OBC is based on a silicon power device and has limitations such as low efficiency, low power density, and high weight. With the advantages of the SiC MOSFET, the designer can greatly improve these limitations by utilizing the superior performance of fast switching, low reverse recovery charge, and a low  $R_{DS(ON)}$ .

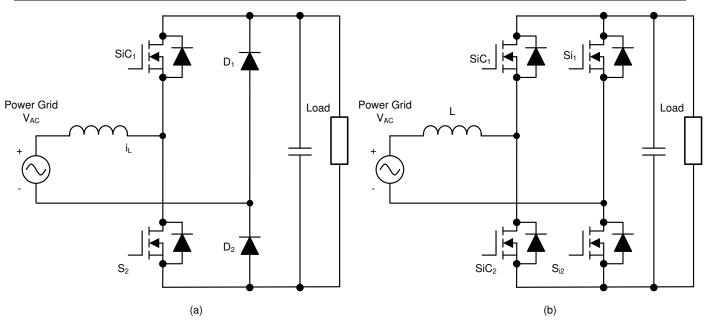

Figure 3-1 shows the basic structure of the totem-pole bridgeless PFC boost rectifier. The component consists of a boost inductor, two high-frequency boost GaN or SiC switches (Labeled SiC<sub>1</sub> and SiC<sub>2</sub> in the diagram below), and two components for conducting current at the line frequency. The line frequency components can be two slow diodes, as Figure 3-1 shows. Side (A) shows two silicon diodes (D<sub>1</sub> and D<sub>2</sub>). Side (B) shows that the use of Si<sub>1</sub> and Si<sub>2</sub> further increases the efficiency.

#### Figure 3-1. Totem-Pole Bridgeless PFC Boost Converter Topology: (A) Diode for Line Rectification (B) MOSFET for Line Rectification

The inherent issue in the totem-pole PFC is the operation mode transition at the AC voltage zero-crossing. When the AC input changes from the positive half line to the negative half line at the zero-crossing, the duty ratio of the low-side high-frequency switch SiC<sub>2</sub> changes from 100% to 0%, and the duty cycle of SiC<sub>1</sub> changes from 0% to 100%. Because of the slow reverse recovery of the high-side diode (or body diode of the MOSFET), the voltage at the cathode of D<sub>2</sub> cannot jump from ground to DC+ voltage instantly (this causes a large current spike). Because of this issue, the designer cannot use an Si MOSFET in a continuous-conduction mode (CCM) totem-pole PFC. Therefore SiC<sub>1</sub> and SiC<sub>2</sub> must be either gallium nitride (GaN) or SiC MOSFET field-effect transistors (FETs), which have a low reverse recovery, for TIDM-02013 we have chosen GaN FETs.

The biggest advantage of the totem-pole PFC is the reduced power losses in the conduction path. Table 3-1 shows the device comparison between a conventional PFC and a totem-pole PFC.

| PARAMETER                    | LOW-FREQUENCY<br>DIODES | HIGH-FREQUENCY<br>DIODES | HIGH-FREQUENCY<br>SWITCHES | CONDUCTION PATHS                                                                          |

|------------------------------|-------------------------|--------------------------|----------------------------|-------------------------------------------------------------------------------------------|

| Conventional bridged<br>PFC  | Four                    | One                      | One                        | Two low-speed diodes + one switch<br>or (two low-speed diodes + one high-<br>speed diode) |

| Totem-pole bridgeless<br>PFC | Two                     | Zero                     | Two                        | One high-speed GaN switch + one<br>low-speed Si (or SiC) MOSFET                           |

#### Table 3-1. Device Comparison of Conventional Bridged PFC and Totem-Pole Bridgeless PFC

The following list summarizes the benefits of the totem-pole PFC:

- Although the conventional PFC boost converter is the most popular topology, its efficiency suffers from the conduction losses of the front-end diode bridge rectifier and it is not bidirectional. A totem-pole PFC is inherently capable of bidirectional operation.

- Bridgeless PFC boost converters greatly reduce the number of diodes, increase the power density, and increase the efficiency.

- This PFC is superior in terms of: high efficiency, small common mode noise, small AC current ripple, small reverse recovery current, and fewer components.

- The low reverse recovery charge of the GaN body diode and the low turn on resistance of the GaN FET make the converter an efficient and cost-effective solution for bidirectional onboard chargers.

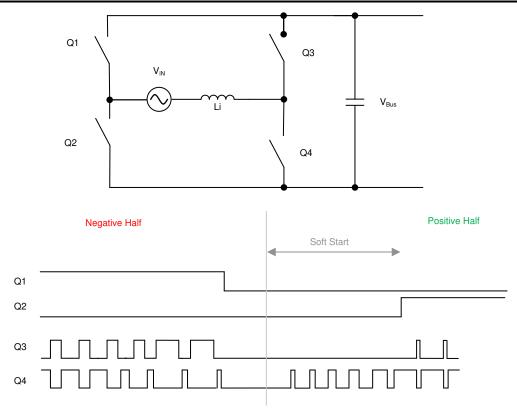

## 3.2 Totem-Pole Bridgeless PFC Operation

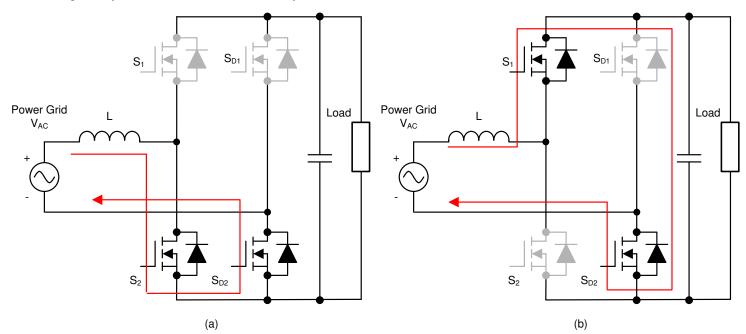

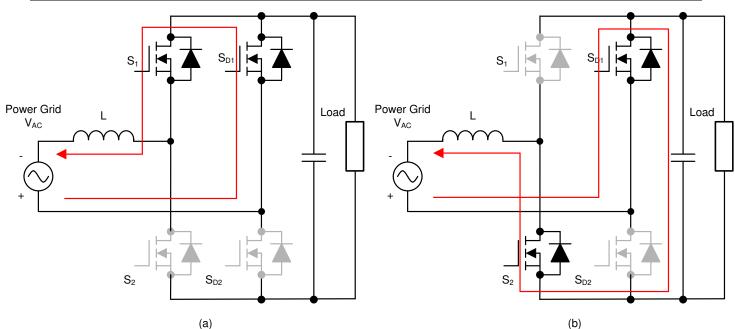

The totem-pole PFC operates in the positive and negative cycles of the AC mains input, respectively, and determines the current flow depending on how the high frequency GaN MOSFETs are switched (see Figure 3-2 and Figure 3-3, respectively).

The high-frequency GaN MOSFETs together with the inductor create a synchronous mode boost converter. During the positive half cycle,  $S_2$  is the boost switch which is driven with duty cycle D and  $S_1$  is driven with a complementary pulse-width modulation (PWM) signal (1-D). Figure 3-2 (A) shows the direction in which the current flows. Similarly, during the period when  $S_2$  is switched with 1-D,  $S_1$  is switched with D; Figure 3-2 (B) shows the direction in which the current flows. Note that, during this cycle,  $S_{D2}$  conducts continuously.

During the negative half cycle, the operation is similar except that the role of the high-side- and low-side, high-frequency switches are swapped. Figure 3-3 shows the direction in which the current flows. Note that, during this cycle,  $S_{D1}$  conducts continuously.

Figure 3-2. Totem-Pole Bridgeless PFC Operation During Positive Half Cycle: (A) While S<sub>2</sub> is Switched ON (B) While S<sub>2</sub> is Switched OFF

Figure 3-3. Totem-Pole Bridgeless PFC Operation During Negative Half Cycle: (A) While  $S_1$  is Switched ON (B) While  $S_1$  is Switched OFF

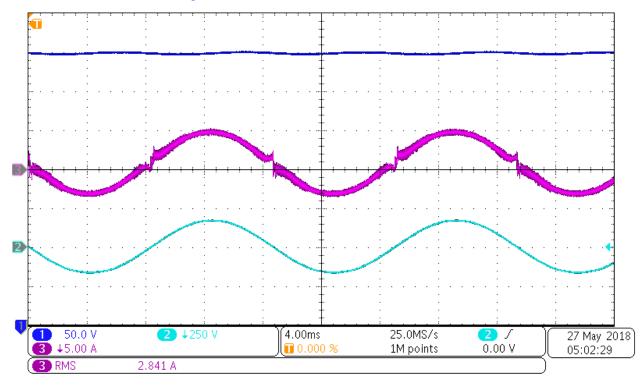

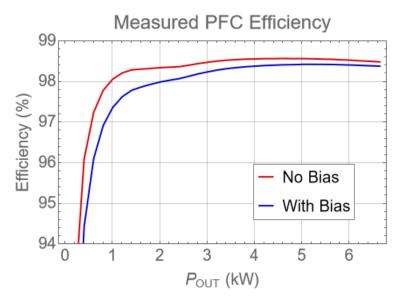

This reference design uses GaN FETs (LMG3522R030-Q1) and TI's C2000<sup>™</sup> Piccolo<sup>™</sup> (TMS320F280039C) high-performance MCU. The high-frequency GaN FETs operate at a 120-kHz switching frequency and the pair of Si MOSFETs operate at the line frequency (approximately 45 Hz to 60 Hz). Thus the conduction path includes one GaN switch and one low-frequency Si switch with significantly-reduced conduction losses. The use of two-channel interleaving to reduce conduction loss and input current ripple. Test results demonstrate a high efficiency above 98.5%.

## 3.3 Key System Specifications

Table 3-2 lists the key system specifications of this design.

| Table 3-2. TIDA-02013 PFC Key System Specifications |                                                                                                                                                                                                                                                                             |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PARAMETER                                           | SPECIFICATIONS                                                                                                                                                                                                                                                              |  |  |

| Input                                               | <ul> <li>Single phase</li> <li>Voltage: ≈ 90-V AC<sub>RMS</sub> to 264-V AC<sub>RMS</sub></li> <li>AC line frequency range: 50Hz to 60 Hz</li> <li>Input current: 32 A<sub>RMS_MAX</sub> at 240 V, 32 A<sub>RMS_MAX</sub> at 120 V</li> <li>Power factor: ≥ 0.99</li> </ul> |  |  |

| Output                                              | <ul> <li>PFC output: ≈ 400 V Typical</li> <li>Maximum output power: 7.4kW at ≈ 400 V</li> <li>Peak efficiency: 98.5%</li> </ul>                                                                                                                                             |  |  |

| Performance                                         | <ul> <li>PFC stage for high-voltage li-ion battery OBC</li> <li>Switching frequency: 120 kHz</li> <li>Isolation: Reinforced</li> <li>Input AC sensing</li> <li>PFC output voltage sensing</li> </ul>                                                                        |  |  |

| Protection                                          | <ul> <li>Overtemperature protection</li> <li>Short-circuit protection</li> <li>Overcurrent protection</li> <li>Undervoltage protection</li> <li>Overvoltage protection at</li> </ul>                                                                                        |  |  |

## Table 3-2. TIDA-02013 PFC Key System Specifications

# 3.4 System Overview

## 3.4.1 Block Diagram

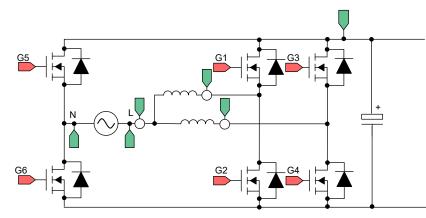

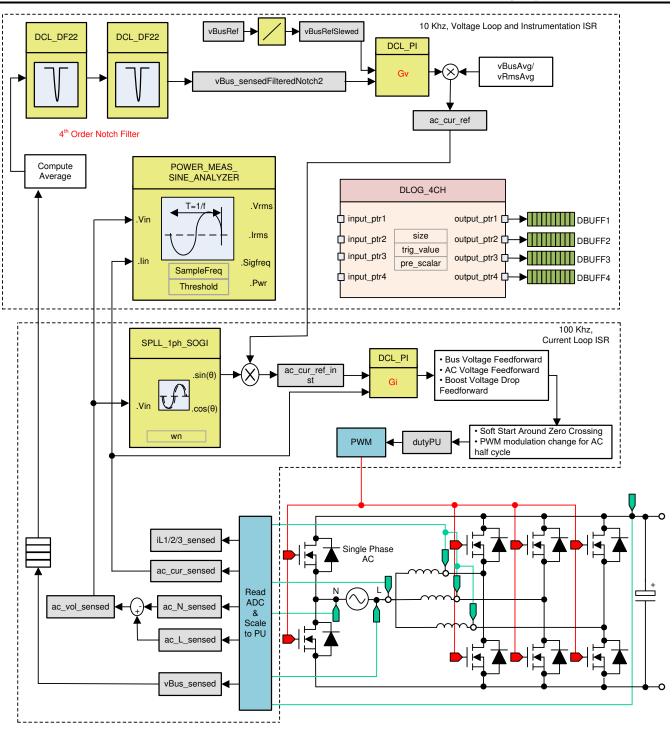

Figure 3-4 shows the system block diagram of the TIDM-02013 reference design, which includes the following elements.

- Power switches G1-G4 are high-frequency GaN MOSFETs, for which there is a 180° phase shift between each half bridge leg. G5 and G6 forms a low-frequency (40- to 60-Hz) synchronous rectifier bridge which virtually has no switching loss; a low conduction loss feature is desirable for these two devices.

- TMS320F280039C C2000 real-time microcontroller functions as the controller, which has all the voltage and current sensor inputs and generates the correct PWM signals for G1-G6. The controller also reads any fault signal from the gate driver boards and shuts down the system if a fault occurs. The reset function is used during start-up or when a fault clears.

- Hall sensors are used to sense the total input current and current for each channel. Voltage dividers are used to sense the input line and neutral voltages as well as output DC bus voltages.

Figure 3-4. TIDM-02013 PFC Block Diagram

## 3.5 System Design Theory

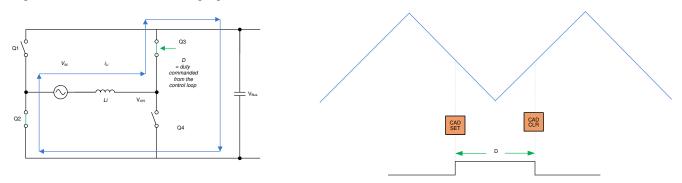

## 3.5.1 PWM

Figure 3-5 shows a simplified diagram of a single phase of the interleaved TTPL PFC topology. To control this rectifier, the duty cycle is controlled to regulate the voltage directly. This regulation is possible if the software variable Duty, or D, is set so that when it is equal to 1, Q3 is always ON, and the setting makes the voltage  $V_{xiN}$  equal to the  $V_{bus}$  voltage. When Duty is set to 0, Q3 never turns on, and Q4 is always connected to DC bus negative, which makes the voltage go to 0.

Figure 3-5. Single-Phase Diagram of TTPL PFC

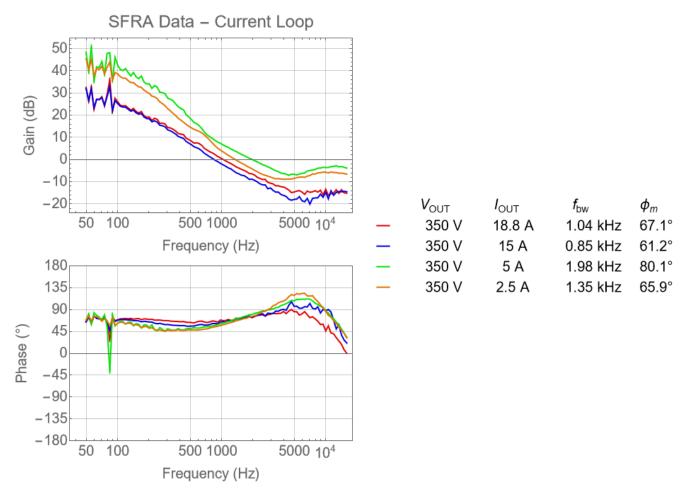

## 3.5.2 Current Loop Model

To understand the current loop model, first look at the inductor current closely. In Figure 3-5, the duty cycle (D) is provided to the PWM modulator, which is connected to the switch Q3 and Q4. From here, Equation 6 is written as:

(6)

(7)

#### $V_{xiN} = D \times V_{bus}$

#### Note

When D is set to 1, Q3 is on all of the time, and when D is 0, Q3 is off all of the time.

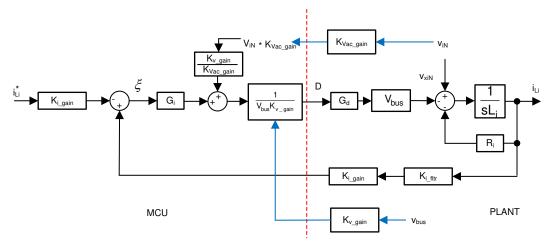

To modulate the current through the inductor, the voltage  $V_{xiN}$  is regulated using the duty cycle control of Q3 and Q4 switches. It is assumed that the direction of current is positive in the direction from the AC line into the rectifier and that the grid is fairly stiff when using the DC bus feedforward and the AC voltage feedforward. Figure 3-6 shows the simplified current loop, and the current loop plant model is written as Equation 7.

$$H_{p_i} = \frac{i_{Li}^*}{D} = \frac{1}{K_{v_gain}} \times K_{i_gain} \times G_d \times \frac{1}{Z_i}$$

where,

- $\kappa_{v_{gain}}$  is the inverse of maximum bus voltage sensed,  $V_{busMaxSense}$

- K<sub>i\_gain</sub> is the inverse of maximum AC current sensed, I<sub>AC\_MaxSense</sub>

- K<sub>i\_fltr</sub> is the response of the RC filter connected from the current sensor to the ADC pin

- G<sub>d</sub> is the digital delay associated with the PWM update and digital control is the current command

- iLi is the current command

Figure 3-6. Current Loop Control Model

#### Note

The negative sign on the reference is used because the current loop is thought to be regulating the voltage,  $V_{xiN}$ . To increase the current,  $V_{xiN}$  must be reduced—hence, the opposite sign for reference and feedback in Figure 3-6.

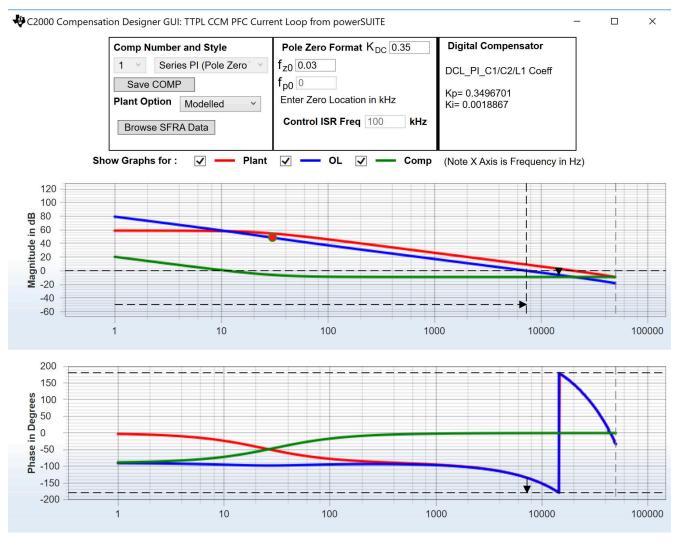

This current loop model is then used to design the current compensator. A simple proportional integral controller is used for the current loop.

In the case of two interleaved phases, the current is simply two times more as the same duty cycle is provided to each leg. Hence, the plant model is given as Equation 8.

$$H_{p_{-}i} = \frac{i_{Li}^{*}}{D} = 2 \times \frac{1}{K_{v_{-}gain}} \times K_{i_{-}gain} \times K_{i_{-}fltr} \times G_{d} \times \frac{1}{Z_{i}}$$

(8)

## 3.5.3 DC Bus Regulation Loop

The DC bus regulation loop is assumed to provide the power reference. The power reference is then divided by the square of the line voltage's RMS to provide the conductance, which is further multiplied by the line voltage giving the instantaneous current command.

EXAS

RUMENTS

www.ti.com

Small signal model of the DC bus regulation loop is developed by linearizing Equation 9 around the operating point.

$$i_{DC}v_{bus} = \eta V_{Nrms}i_{Nrms} \rightarrow \hat{i}_{DC} = \eta \frac{\overline{V}_{Nrms}}{\overline{V}_{bus}}i_{Li}$$

(9)

For a resistive load, the bus voltage and current are related as shown in Equation 10:

$$\hat{V}_{bus} = \frac{R_L}{1 + sR_LC_o} \hat{i}_{DC}$$

(10)

The DC voltage regulation loop control model can be drawn as shown in Figure 3-7. An additional  $V_{bus}$  feed forward is applied to make the control loop independent of the bus voltage. Therefore, the plant model for the bus control can be written as in Equation 11:

Figure 3-7. DC Voltage Loop Control Model

Using Figure 3-7, a proportional integrator (PI) compensator is designed for the voltage loop. The bandwidth of this loop is kept low as it is in conflict with the THD under steady state.

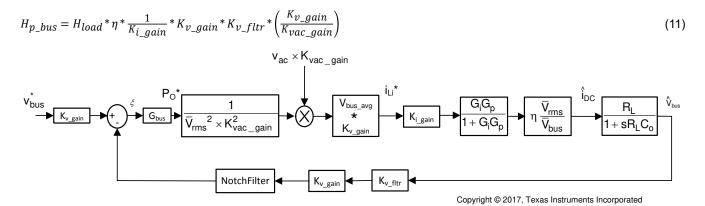

## 3.5.4 Soft Start Around Zero-Crossing for Eliminating or Reducing Current Spike

Zero-crossing current spikes present a challenging issue for TTPL PFC topologies. This issue is solved by implementing a soft-start scheme with a state machine to turn on and off switches in a particular sequence.

## Figure 3-8. PWM Sequence With Soft Starting to Reduce Current Spike at Zero-Crossing

Figure 3-8 shows the switching sequence when the AC wave goes from negative to positive. During the negative half, Q1 is ON, Q3 is the active FET, and Q4 is the sync FET. During this time, the voltage across Q2 is the DC bus voltage. When the AC cycle changes, Q2 must be on 100% or close to 100%. If Q2 is turned ON immediately, a substantial positive spike results. Therefore, a soft-start sequence is used to turn Q4 ON as shown in Figure 3-8. The tuning of this soft start depends on the inductance value and other power stage parameters such as device  $C_{oss}$ .

Another reason for a negative current spike around zero-crossing is the relatively low AC voltage around the zero-crossing. When Q3 is turned ON, though the duty cycle is low, a high-voltage difference is applied and can result in a high negative current spike. Therefore, a sufficient delay is applied before Q3 starts switching back again.

Similarly, Q2 is turned on after some delay after the soft start has started.

## 3.5.5 Current Calculation

Select the input fuse, filter current ratings based on the max input current, which Equation 12 calculates as:

$$I_{inrms} = \frac{P_{out\_max}}{\eta \cdot V_{inrms} \cdot PF} = 28.2 A$$

where,

- P<sub>OUT MAX</sub> is the maximum output power 6.6 kW

- η is the efficiency (assumed as 98.6%)

- V<sub>IN RMS</sub> is the input voltage RMS value (240 V)

- PF is the power factor (assumed as 0.99)

## 3.5.6 Inductor Calculation

The inductor plays important role in affecting system efficiency, current ripple, and overall size. It is always a balance between the efficiency and the power density. The inductance value is calculated based on the input voltage, output voltage, and worst case ripple.

(12)

The duty cycle is calculated as:

$$D = 1 - \frac{V_{in}}{V_{out}} \tag{13}$$

Calculation of the current ripple into inductor can be distinguished into three periods:

$$I_{ripple} = \left(\frac{V_{in}}{L} - 2 \times \frac{V_{out} - V_{in}}{L}\right) \times D \times T_s \quad \leftarrow For D \le 1/3$$

(14)

$$I_{ripple} = \left(\frac{2 \times V_{in}}{L} - \frac{V_{out} - V_{in}}{L}\right) \times \left(D - \frac{1}{3}\right) \times T_s \quad \leftarrow For \ 1/3 < D < 2/3 \tag{15}$$

$$I_{ripple} = \left(\frac{3 \times V_{in}}{L}\right) \times \left(D - \frac{2}{3}\right) \times T_s \quad \leftarrow For \ D \ge 2/3 \tag{16}$$

In the worst cases, the equation becomes:

$$I_{ripple} = \frac{V_{out} \times T_s}{12 \times L} \tag{17}$$

This design targets at achieving 10% current ripple at maximum input power and maximum AC current:

$$I_{ripple} < 10\% \times \frac{\sqrt{2} \times P_{out\_max}}{V_{in\_max} \times \eta}$$

(18)

where,

- Pout\_max is the maximum output power

- η is the efficiency

- V<sub>in\_max</sub> is the maximum input voltage

As a result, the inductance is calculated as 126  $\mu$ H at 12 A RMS current.

## 3.5.7 Output Capacitor Calculation

Due to the input double-line frequency ripple on the DC link capacitor, its capacitance is mainly determined by the output voltage ripple, as calculated in Equation 19:

$$C_{out(\min)} \ge \frac{P_{out}/V_{out}}{4 \cdot \pi \cdot f_{line\_\min} \cdot V_{ripple\_max}} = 860 \mu F$$

(19)

where,

- P<sub>OUT</sub> is the output power

- V<sub>OUT</sub> is the output voltage

- f<sub>LINE MIN</sub> is the minimum line frequency

- V<sub>RIPPLE</sub> is the output ripple

The actual capacitor used is 1410  $\mu$ F(3 x 470uF).

EXAS

**RUMENTS**

www.ti.com

## 3.5.8 Current and Voltage Sense

The Hall-effect sensor ACS733KLATR-40AB-T is used for the total input current sensing, as Figure 3-10 shows. The OPA320-based amplifier circuit tunes the low output voltage of the sensor to a higher level and sends this voltage to the controller ADC pin. The ACS733KLATR-40AB-T device senses each individual interleaved phase's current which allows phase current balancing.

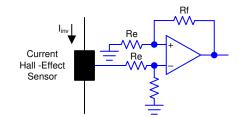

## Figure 3-9. Hall Effector Sensor Signal Conditioning Circuit

The output voltage from the signal conditioning circuit is scaled to match the ADC range using the circuit as shown in Figure 3-9. The voltage is calculated as:

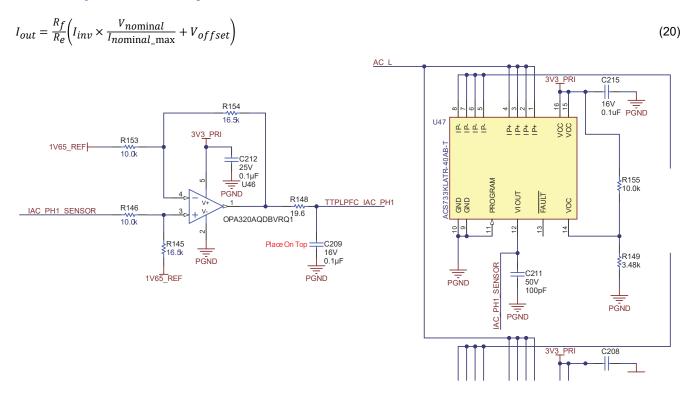

Figure 3-10. Schematic of Current Sensing

The input AC voltage is sensed differentially by sensing the line, and the neutral inputs refer to the control ground separately with two voltage dividers, as Figure 3-11 shows. The control ground is the DC link negative terminal; therefore, a single voltage divider can be used to sense the DC bus voltage. An RC filter filters the signals before connecting to the controller. A common RC filter is used for all the sensing signals on this design.

Figure 3-11. Schematic of Voltage Dividers for AC Input Voltage Sense

# 4 Highlighted Products 4.1 C2000 MCU TMS320F28003x

C2000<sup>™</sup> 32-bit microcontrollers are optimized for processing, sensing, and actuation to improve closed-loop performance in real-time control applications such as industrial motor drives; solar inverters and digital power; electrical vehicles and transportation; motor control; and sensing and signal processing.

The TMS320F28003x (F28003x) is a powerful 32-bit floating-point microcontroller unit (MCU) that lets designers incorporate crucial control peripherals, differentiated analog, and nonvolatile memory on a single device.

The CLA allows significant offloading of common tasks from the main C28x CPU. The CLA is an independent 32-bit floating-point math accelerator that executes in parallel with the CPU. Additionally, the CLA has its own dedicated memory resources and it can directly access the key peripherals that are required in a typical control system. Support of a subset of ANSI C is standard, as are key features like hardware breakpoints and hardware task-switching.

High-performance analog blocks are integrated on the F28003x MCU to further enable system consolidation. Three separate 12-bit ADCs provide precise and efficient management of multiple analog signals, which ultimately boosts system throughput. Four analog comparator modules provide continuous monitoring of input voltage levels for trip conditions.

The TMS320C2000<sup>™</sup> devices contain industry-leading control peripherals with frequency-independent Enhanced Pulse Width Modulator/High-Resolution Pulse Width Modulator (ePWM/HRPWM) and Enhanced Capture (eCAP) module allow for a best-in-class level of control to the system. The built-in Sigma-Delta Filter Module (SDFM) allows for seamless integration of an oversampling sigma-delta modulator across an isolation barrier.

Connectivity is supported through various industry-standard communication ports [such as Serial Peripheral Interface (SPI); Serial Communication Interface (SCI); Inter-integrated Circuit (I2C); and Controller Area Network (CAN)] and offers multiple multiplexing options for optimal signal placement in a variety of applications. New to the C2000<sup>™</sup> platform is the fully compliant Power-Management Bus (PMBus). Additionally, in an industry first, the Fast Serial Interface (FSI) enables high-speed, robust communication to complement the rich set of peripherals that are embedded in the device.

A specially enabled device variant, TMS320F28003xC, allows access to the Configurable Logic Block (CLB) for additional interfacing features. See the Device Comparison table in the TMS320F28003x microcontrollers data manual for more information.

The Embedded Real-Time Analysis and Diagnostic (ERAD) module enhances the debug and system analysis capabilities of the device by providing additional hardware breakpoints and counters for profiling.

Following is the subset of features of the C2000 MCU that are highlighted on this design to enable control of high-frequency CLLLC topology:

- 1. **High-resolution PWM**: With picosecond resolutions possible, the ePWM module on the C2000 MCU can generate high-frequency PWM with accuracy. With the Type-4 PWM high-resolution period control, high-resolution duty control, high-resolution dead-band control, along with high-resolution phase shift control, is possible. This enables generation of balanced pulses for the resonant tank excitation and is an enabling feature for high-frequency power converters.

- Comparator Subsystem (CMPSS) with ePWM for active synchronous rectification: Active synchronous rectification enables higher efficiency and for high-frequency resonant converters that operate both below and above the resonant point, it is a necessary feature for the topology. The C2000 MCUs' integrated CMPSS enables generation of the active synchronous rectification pulses by using the integrated comparators and the integrated Digital-to-Analog Converters (DACs). (See Section 2.2.2.4.)

- 3. **Blanking window**: Due to noise, which is unavoidable in switching converters, the blanking window feature is used to suppress the CMPSS output during noisy switching events. This blanking window is provided by the ePWM time base and can be applied at different times during the PWM cycle. (See Section 2.2.3.)

- 4. **X-Bar**: Multiple trip sources are possible in a power converter. The X-bar enables combining different trip actions from either different CMPSS or from GPIO to generate trip behavior desired in the ePWM without need of external logic.

- 5. **Control Law Accelerator (CLA)** enables integration of control of multiple topologies on a single controller. The software provided with this design provides the option to run the control loop on the CLA or the C28x.

6. **Global Link feature in PWM module** enables update to multiple PWMs through a single write, which reduces the CPU burden and enables higher-frequency converters to be controlled easily.

## 4.2 LMG352xR30-Q1

The LMG352xR030-Q1 is an automotive qualified 650-V  $30-m\Omega$  GaN FET with integrated driver, protection and temperature reporting. The integrated driver enables switching speed up to 150 V/ns. TI's integrated precision gate bias results in higher switching SOA compared to discrete external gate drivers. This integration, combined with a low-inductance package, delivers clean switching and minimal ringing in hard-switching power supply topologies. Other features, including adjustable gate drive strength for EMI control, overtemperature, and robust overcurrent protection with fault indication, provide optimized BOM cost, board size, and footprint. Advanced power management features include digital temperature reporting; the temperature of the GaN FET is reported through a variable duty cycle PWM output, which enables the system to optimally manage loading.

## 4.3 UCC21222-Q1

The UCC21222 device is an isolated dual channel gate driver with programmable dead time. It is designed with 4-A peak-source and 6-A peak-sink current to drive power MOSFET, IGBT, and GaN transistors.

The UCC21222 device can be configured as two low-side drivers, two high-side drivers, or a half-bridge driver. 5ns delay matching performance allows two outputs to be paralleled, doubling the drive strength for heavy load conditions without risk of internal shoot-through.

The input side is isolated from the two output drivers by a 3.0-kV<sub>RMS</sub> isolation barrier, with a minimum of 100-V/ns common-mode transient immunity (CMTI).

Resistor programmable dead time gives the capability to adjust dead time for system constraints to improve efficiency and prevent output overlap. Other protection features include: Disable feature to shut down both outputs simultaneously when DIS is set high, integrated deglitch filter that rejects input transients shorter than 5-ns, and negative voltage handling for up to -2-V spikes for 200-ns on input and output pins. All supplies have UVLO protection.

## 4.4 AMC3330-Q1

The AMC3330 is a precision, isolated amplifier with a fully integrated, isolated DC/DC converter that allows single-supply operation from the low-side of the device. The reinforced capacitive isolation barrier is certified according to VDE V 0884-11 and UL1577 and separates sections of the system that operate on different common-mode voltage levels and protects low-voltage domains from damage. The input of the AMC3330 is optimized for direct connection to high-impedance, voltage-signal sources such as a resistor-divider network to sense high-voltage signals. The integrated isolated DC/DC converter allows measurement of non-ground-referenced signals and makes the device a unique design for noisy, space-constrained applications.

## 4.5 AMC3302-Q1

The AMC3302 is a precision, isolated amplifier optimized for shunt-based current measurements. The fully integrated, isolated DC/DC converter allows single-supply operation from the low-side of the device, which makes the device a unique solution for space-constrained applications. The reinforced capacitive isolation barrier is certified according to VDE V 0884-11 and UL1577 and supports a working voltage of up to 1.2 kV<sub>RMS</sub>. The isolation barrier separates parts of the system that operate on different common-mode voltage levels and protects the low-voltage side from hazardous voltages and damage. The input of the AMC3302 is optimized for direct connection to a low-impedance shunt resistor or another low-impedance voltage source with low signal levels. The excellent DC accuracy and low temperature drift supports accurate current measurements over the extended industrial temperature range from  $-40^{\circ}$ C to  $+125^{\circ}$ C.

# 5 Hardware, Software, Testing Requirements, and Test Results

## 5.1 Required Hardware and Software

This section details the hardware and explains the different sections on the board and how to set them up for the experiments as outlined in this design guide.

## 5.1.1 Hardware Settings

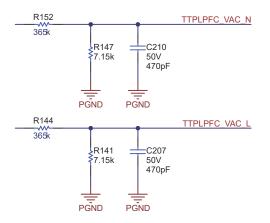

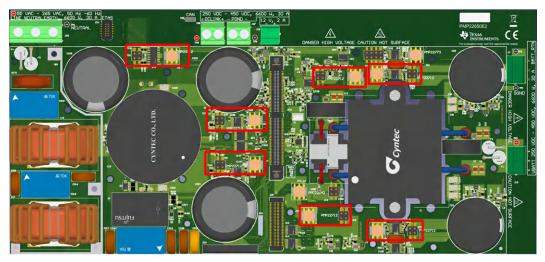

The design follows a High-Speed Edge Card (HSEC) control card concept, and any device for which a HSEC control card is available from the C2000 MCU product family can be potentially used on this design. The key resources used for controlling the power stage on the microcontroller are listed in Table 5-1. Figure 5-1 shows the key power stage and connectors on the reference design. Table 5-3 lists the key connectors and their functions.

- 1. Make sure no power source is connected to the board.

- 2. Insert the control card in the J25 slot.

- 3. Connect a power source (*but do not power up*) for the 12V bias supplies (+12 V, 2 A) at the J15 shown in Figure 5-1.

- 4. Now, switch the power source on for the bias supply. A green LED on the control card will light up. This indicates the C2000 MCU device is powered. Note: The bias for the microcontroller is separated from the power stage; this enables a safe bring up of the system in this set of instructions.

- 5. To connect JTAG, use a USB cable from the control card and connect it to a host computer.

- For operation of the TTPLPFC stage an AC input must be connected to J33 (90V 264V). For testing a >10kW supply has been used, however a clean and stable lower-rated supply can be used in the case where only low-power tests are being conducted.

- 7. For stand alone operation of the PFC stage a load may be connected to J37 and J38, alternatively the CLLLC can be used to load the PFC stage.

- 8. For stand alone operation of the CLLLC stage a DC power supply (400V) may be connected to VBUS at J15. If this is done the TTPLPFC should not be started in software and the AC source described in step 6 above should not be connected.

- 9. A load should be connected to the secondary side of the CLLLC converter when in use. J7 and J10 can be used to connect such a load.

- 10. When operating both the PFC and DCDC stages connect an AC supply as in Step 6 above and a load as in step 9 above. No connection to VBUS is needed however a current bleed resistor may be helpful to ensure excess voltage can be quickly bled off after execution of the OBC.

- 11. Current and voltage probes can be connected to observe the tank current at primary and secondary. Optionally, a power meter can be connected to measure the efficiency.

Hardware, Software, Testing Requirements, and Test Results

Figure 5-1. Board Overview

There are 7 bias supply daughter cards required shown in red

30

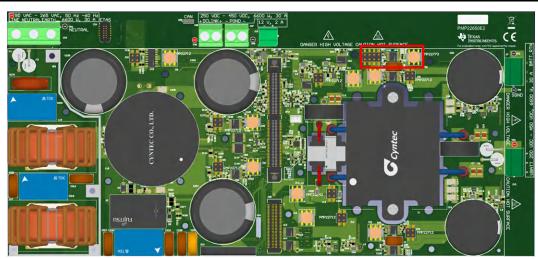

Figure 5-2. PMP22712 - bias supplies

There is one Feedback isolation daughter card PMP22773 required indicated in red

Figure 5-3. PMP22773 – Feedback Isolation Daughter Card

| Table 5-1. Key Digital Pin Assignments                         |        |                                           |  |  |

|----------------------------------------------------------------|--------|-------------------------------------------|--|--|

| Signal name         HSEC Pin Number         F28003x peripheral |        |                                           |  |  |

| SYSTEM ISR Trigger                                             | -      | ECAP1                                     |  |  |

| CLLLC_CONTROL_OUTPUT_DAC_PIN                                   | 14     | DACA                                      |  |  |

| CLLLC_PRIM_LEG1_H/L                                            | 49/ 51 | EPWM1 (A/B)                               |  |  |

| CLLLC_PRIM_LEG2_H/L                                            | 53/ 55 | EPWM2 (A/B)                               |  |  |

| CLLLC_SEC_LEG1_H/L                                             | 50/ 52 | EPWM3 (A/B)                               |  |  |

| CLLLC_SEC_LEG2_H/L                                             | 54/ 56 | EPWM4 (A/B)                               |  |  |

| CLLLC_FAULTn                                                   | 74     | $GPIO-23 \rightarrow INPUTXBAR2$          |  |  |

| CLLLC_LC_CHANGE                                                | 62     | GPIO-14                                   |  |  |

| CLLLC_SEC_SIDE_DIAG                                            | 80     | GPIO-30                                   |  |  |

| TTPLPFC_LOW_FREQ_H/L                                           | 57/ 59 | EPWM5 (A/B)                               |  |  |

| TTPLPFC_HIGH_FREQ_PH1_H/L                                      | 61/ 63 | EPWM6 (A/B)                               |  |  |

| TTPLPFC_HIGH_FREQ_PH2_H/L                                      | 58/ 60 | EPWM7 (A/B)                               |  |  |

| TTPLPFC_FAULTn                                                 | 72     | $GPIO-22 \rightarrow INPUTXBAR1$          |  |  |

| TTPLPFC_INRUSH_RELAY_CTRL                                      | 64     | GPIO-15                                   |  |  |

| ERRORSTSn                                                      | 102    | GPIO55                                    |  |  |

| SYSTEM WATCHDOG OUT                                            | 75     | GPIO24                                    |  |  |

| SYSTEM_WATCHDOG_DISABLE                                        | 77     | GPIO25(Resistor option)                   |  |  |

| SYSTEM_PMIC_SPI (resv)                                         | 79     | GPIO26(Resistor option)                   |  |  |

| SYSTEM_PMIC_SPI (resv)                                         | 81     | GPIO27(Resistor option)                   |  |  |

| SYSTEM_DISABLE_FET_SUPPLY                                      | 85     | GPIO32                                    |  |  |

| SYSTEM_TEMP_MUX_OUT1                                           | 91     | GPIO41 -> ECAP2 $\rightarrow$ INPUTXBAR3  |  |  |

| SYSTEM_TEMP_MUX_OUT2                                           | 96     | $GPIO60 \text{ -> } ECAP3 \to INPUTXBAR4$ |  |  |

| SYSTEM_TEMP_MUX_SEL_1-3                                        | 93     | GPIO47                                    |  |  |

|                                                                | 94     | GPIO58                                    |  |  |

|                                                                | 95     | GPIO59                                    |  |  |

| SYSTEM_PROFILING1-3                                            | 89     | GPIO40                                    |  |  |

|                                                                | 92     | GPIO44                                    |  |  |

|                                                                | 101    | GPIO49                                    |  |  |

| FSI_TX_D0                                                      | 101    | GPIO-49/FSITXA D0                         |  |  |

| FSI_TX_D1                                                      | 103    | GPIO-50/FSITXA_D1                         |  |  |

| FSI_TX_CLK                                                     | 105    | GPIO-51/FSITXA CLK                        |  |  |

## Table 5-1. Key Digital Pin Assignments

#### Table 5-1. Key Digital Pin Assignments (continued)

| Signal name | HSEC Pin Number | F28003x peripheral                  |

|-------------|-----------------|-------------------------------------|

| LED1        | 82              | $GPIO-31 \to LED1$                  |

| LED2        | 86              | $GPIO-34 \rightarrow LED2 \ (SFRA)$ |

This table describes the sampling scheme for the reference design. Across the top each column represents one independent ADC. Each ADC acts entirely independently from the others. Each signal is assigned one or more Start Of Conversions (SOCs). Each SOC represents one independent reading of that channel, for example TTPLPFC\_IAC\_PH1 is assigned SOC0 and SOC1 within ADCA. This means that this signal will be sampled twice every cycle, once triggered by ePWM6\_SOCA and once triggered by ePWM6\_SOCB. Since this trigger is running at 120kHz this signal is effectively oversampled by a factor of two times during each 120kHz sampling period. Similarly CLLLC\_ISEC is oversampled 11 times, and CLLLC\_IPRIM is not oversampled. The table also indicates several low-frequency sampled signals which can be seen that these signals use a different SOC signal. Finally since a round robin counter is used to process the SOCs in numeric order the table reads as a timeline from top to bottom in the order of sampling.

#### Table 5-2. Key Analog Signals

|                          | ADC-A                                      | ADC-B                         | ADC-C                       |

|--------------------------|--------------------------------------------|-------------------------------|-----------------------------|

| Highest Priority Signals | TTPLPFC_IAC_PH1 (A2, CMPSS1)               | TTPLPFC_IAC_PH2 (B12, CMPSS3) | TTPLPFC_VAC (C7)            |

| (120kHz)                 | $SOC0 \to ADC\_TRIGGER\_EPWM6\_SOCA$       | SOC0 →                        | SOC0 →                      |

|                          | $SOC1 \to ADC\_TRIGGER\_EPWM6\_SOCB$       | ADC_TRIGGER_EPWM6_SOCA        | ADC_TRIGGER_EPWM6_SOCA      |

|                          |                                            | SOC1 →                        | SOC1 →                      |

|                          |                                            | ADC_TRIGGER_EPWM6_SOCB        | ADC_TRIGGER_EPWM6_SOCB      |

|                          | CLLLC_ISEC (A5, CMPSS2)                    | TTPLPFC_VBUS / CLLLC_VBUS     | CLLLC_VSEC (C11, CMPSS2)    |

|                          | $SOC2 \to ADC\_TRIGGER\_EPWM6\_SOCA$       | (B4)                          | $SOC2 \rightarrow$          |

|                          | $SOC3 \to ADC\_TRIGGER\_EPWM6\_SOCA$       | $SOC2 \rightarrow$            | ADC_TRIGGER_EPWM6_SOCA      |

|                          | $SOC4 \to ADC\_TRIGGER\_EPWM6\_SOCA$       | ADC_TRIGGER_EPWM6_SOCA        | SOC3 →                      |

|                          | $SOC5 \to ADC\_TRIGGER\_EPWM6\_SOCA$       | SOC3 →                        | ADC_TRIGGER_EPWM6_SOCA      |

|                          | $SOC6 \to ADC\_TRIGGER\_EPWM6\_SOCA$       | ADC_TRIGGER_EPWM6_SOCB        | $SOC4 \rightarrow$          |

|                          | SOC7 →ADC_TRIGGER_EPWM6_SOCA               | $SOC4 \rightarrow$            | ADC_TRIGGER_EPWM6_SOCA      |

|                          | $SOC8 \to ADC\_TRIGGER\_EPWM6\_SOCB$       | ADC_TRIGGER_EPWM7_SOCA        | SOC5 →                      |

|                          | $SOC9 \to ADC\_TRIGGER\_EPWM6\_SOCB$       | SOC5 →                        | ADC_TRIGGER_EPWM6_SOCA      |

|                          | $SOC10 \to ADC\_TRIGGER\_EPWM6\_SOCB$      | ADC_TRIGGER_EPWM7_SOCB        | SOC6 →                      |

|                          | $SOC11 \to ADC\_TRIGGER\_EPWM6\_SOCB$      |                               | ADC_TRIGGER_EPWM6_SOCA      |

|                          | $SOC12 \to ADC\_TRIGGER\_EPWM6\_SOCB$      |                               | SOC7 →                      |

|                          |                                            |                               | ADC_TRIGGER_EPWM6_SOCA      |

|                          |                                            |                               | SOC8 →                      |

|                          |                                            |                               | ADC_TRIGGER_EPWM6_SOCA      |

|                          |                                            |                               | SOC9 →                      |

|                          |                                            |                               | ADC_TRIGGER_EPWM6_SOCA      |

|                          |                                            |                               | SOC10 →                     |

|                          |                                            |                               | ADC_TRIGGER_EPWM6_SOCA      |

|                          |                                            |                               | SOC11 →                     |

|                          |                                            |                               | ADC_TRIGGER_EPWM6_SOCA      |

|                          |                                            |                               | SOC12 →                     |

|                          |                                            |                               | ADC_TRIGGER_EPWM6_SOCA      |

|                          | CLLLC_IPRIM (A9, CMPSS2)                   |                               |                             |

|                          | SOC13→ADC_TRIGGER_EPWM1_SOCA               |                               |                             |

| Low-Frequency Sampling   | TTPLPFC_VAC_L (A4)                         | TTPLPFC_VAC_N (B2)            | TTPLPFC_VBUS2 (C10, CMPSS2) |

| Signals                  | SOC14 $\rightarrow$ ADC_TRIGGER_CPU1_TINT2 | SOC10 →                       | SOC14 →                     |

| (10kHz)                  |                                            | ADC_TRIGGER_CPU1_TINT2        | ADC_TRIGGER_CPU1_TINT2      |

|                          | SYSTEM_ TEMP_1 (A11)                       | SYSTEM_VREF_1_65 (B5)         | CLLLC_VSEC (C11, CMPSS2)    |

|                          | $SOC15 \to ADC\_TRIGGER\_CPU1\_TINT2$      | SOC11                         | $VSEC13 \rightarrow SOC15$  |

|                          |                                            | →ADC_TRIGGER_CPU1_TINT2       | →ADC_TRIGGER_CPU1_TINT2     |

#### Table 5-2. Key Analog Signals (continued)

|                         | ADC-A | ADC-B                                | ADC-C                        |

|-------------------------|-------|--------------------------------------|------------------------------|

| Not Sampled, CMPSS only |       | CLLLC_IPRIM_TANK (A12/C5,<br>CMPSS2) | CLLLC_ISEC_TANK (C1, CMPSS4) |

#### Table 5-3. Key Connectors and Their Function

| CONNECTOR<br>NAME | FUNCTION                                |  |

|-------------------|-----------------------------------------|--|

| J33               | AC input                                |  |

| J37/J38           | VBUS connection; PFC output, DCDC VPRIM |  |

| J7/J10            | DCDC output connection; DCDC VSEC       |  |

| J15               | 12 V 2 A power supply                   |  |

| J25/J26           | HSEC control card connector slot        |  |

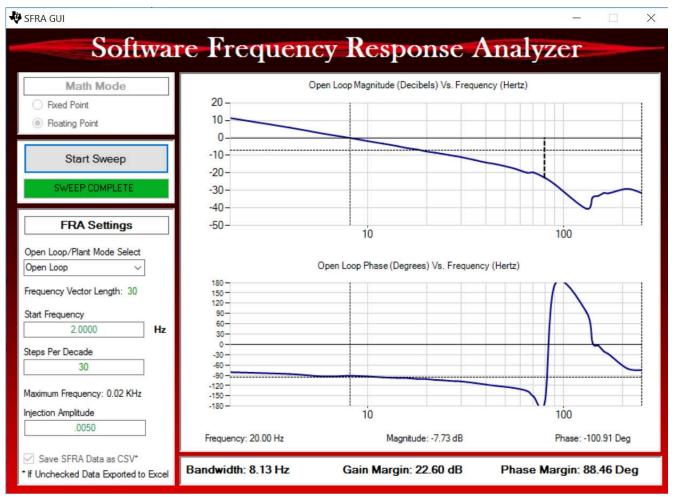

#### 5.1.1.1 Control Card Settings

Certain settings on the device control card are required to communicate over JTAG and use the isolated UART port. The user must also provide a correct ADC reference voltage. The following are the required settings for revision A of the F280039C control card. The user can also refer to the information sheet located inside C2000Ware at \c2000ware\boards\controlcards\TMDSCNCD280039C or alternatively get it from the *F280039 controlCARD Information Guide*.

- 1. S1:A on the control card must be set on both ends to the ON (Left) position to enable JTAG connection to the device and UART connection for the SFRA GUI. If this switch is set to OFF (Right), the user cannot use the isolated JTAG built-in on the control card nor can the SFRA GUI communicate to the device.

- 2. J1:A is the connector for the USB cable that is used to communicate to the device from a host PC on which Code Composer Studio<sup>™</sup> Integrated Development Environment (IDE) runs.

- 3. A 3.3-V reference is desired for the control-loop tuning on this design. Internal reference of the F28003x is used, and for this, the S3 switch must be moved to the top position(that is, pointing to INT).

- 4. A capacitor is connected between the isolated grounds on the control card, C7:A. It must be removed before connecting HV power.

For best performance RC filter caps are required to be added to several ADC channels. Each of the component designators are clearly marked in the silkscreen and assembly plots can be found in C2000Ware for TMDSCNCD280039C. \c2000ware\boards\controlcards\TMDSCNCD280039C

| SIGNAL          | CAPACITOR COMPONENT<br>DESIGNATOR | CAPACITOR VALUE |

|-----------------|-----------------------------------|-----------------|

| TTPLPFC_VBUS    | C46                               | 1 µF 0603       |

| CLLLC_VSEC      | C43                               | 1 µF 0603       |

| TTPLPFC_VAC     | C32                               | 1 µF 0603       |

| TTPLPFC_IAC_PH1 | C31                               | 1 µF 0603       |

| TTPLPFC_IAC_PH2 | C49                               | 1 µF 0603       |

| CLLLC_ISEC_TANK | C50                               | 560 pF 0603     |

| CLLLC_ISEC      | C34                               | 1 µF 0603       |

#### 5.1.2 Software

The software of this design is available in the DigitalPower Software Development Kit (SDK) for C2000 MCUs (C2000WARE-DIGITALPOWER-SDK).

#### 5.1.2.1 Opening the Project Inside Code Composer Studio

To start:

- 1. Install Code Composer Studio from the Code Composer Studio (CCS) Integrated Development Environment (IDE) tools folder. Version 12.0 or above is recommended.

- 2. Install C2000WARE-DIGITAL-POWER-SDK in one of two ways:

- Through the C2000Ware Digital Power SDK tools folder

- Go to CCS and under View → Resource Explorer. Under the TI Resource Explorer, go to C2000WARE-DIGITAL-POWER-SDK, and click on the install button.

- 3. When installation completes, close CCS, and open a new workspace. CCS automatically detects powerSUITE. A restart of CCS may be required for the change to be effective.

#### Note

powerSUITE is installed with the SDK by default.

The firmware project can now be imported as follows:

The user can also directly import the project, by going inside CCS to Click Project  $\rightarrow$  Import CCS Projects and browsing to the solution folder located at <SDK>/solutions/tidm\_02013/f28003x/ccs.

A project spec will appear, clicking on this will create a self-contained folder of the project with all the dependencies inside it.

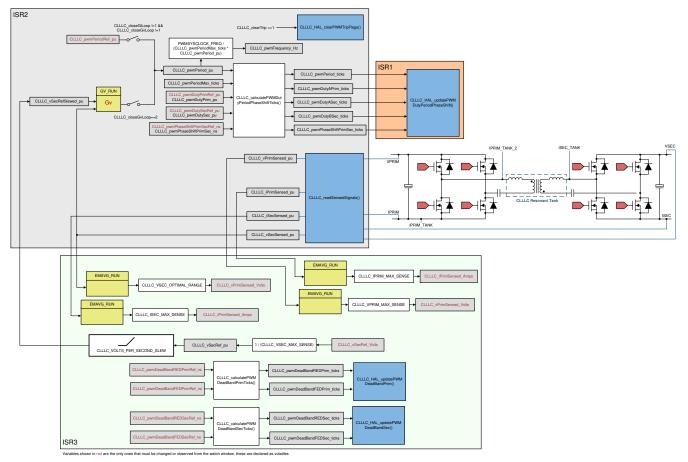

#### 5.1.2.2 Project Structure

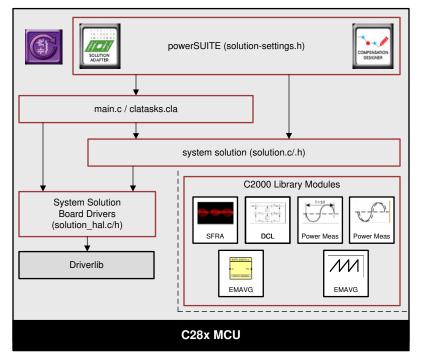

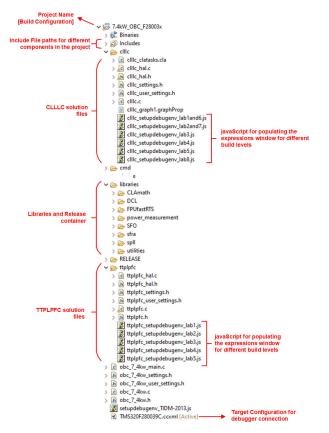

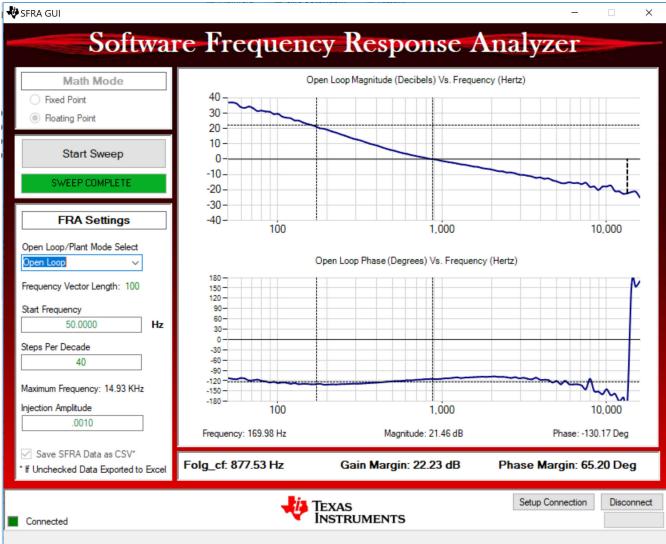

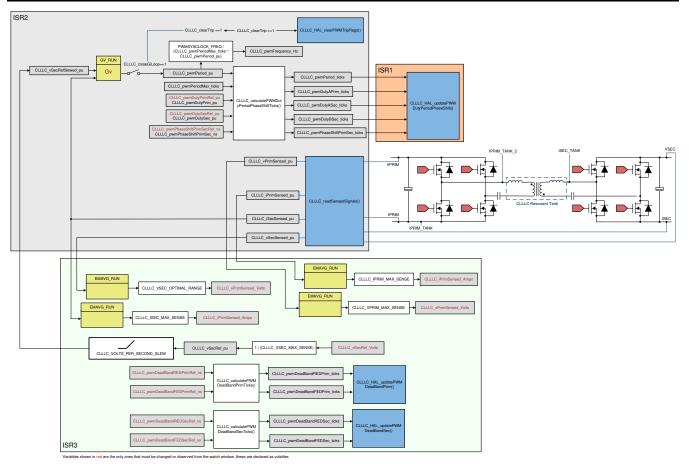

Figure 5-4. Project Structure Overview

The general structure of the project is shown in Figure 5-4. Once the project is imported, the Project Explorer will appear inside CCS as shown in Figure 5-5.

Solution-specific and device-independent files that consist of the core algorithmic code are in <*solution*>.*c/h*. For example *TTPLPFC.c* or *CLLLC.h*.

Board-specific and device-specific files are in *<solution>\_hal.c/h*. This file consists of device-specific drivers to run the solution. If the user wants to use a different modulation scheme or a different device, the user is required only to make changes to these files, besides changing the device support files in the project.

The *<solution>-main.c* file consists of the main framework of the project. This file consists of calls to the board and solution file that help in creating the system framework, along with the interrupt service routines (ISRs) and slow background tasks.

For this design, there are three <solution> monikers *obc\_7\_4kw*, *clllc*, and *ttplpfc*. Please note that to maintain maximum flexibility we have chosen to keep the CLLLC code base and the TTPLPFC code base as independent

as possible while the *obc\_7\_4kw* files were added where needed to contain settings independent to the TTPLPFC and CLLLC. This allows the end user to operate each stage independently and incorporate different topologies for either the PFC or DCDC stages easily in their final design if desired.

The *<solution>\_settings.h* file contains code configuration settings like which lab to build. While the *<solution>\_user\_settings.h* contains the board level configurations such as #defines for ADC mapping, GPIOs etc.

*solution.js* files contain a script file which can help populate relevant variables to observer during the execution of each lab. To use these scripts open the scripting console(View - Scripting Console). Paste the contents of the solution.js file into the scripting console and press enter. This will populate the expressions window for debug later.

The solution name is also used as the module name for all the variables and defines used in the solution. Hence, all variables and function calls are prepended by the CLLLC name (for example, CLLLC\_vSecSensed\_pu). This naming convention lets the user combine different solutions while avoiding naming conflicts.

Figure 5-5. Project Explorer View of the CLLLC Project

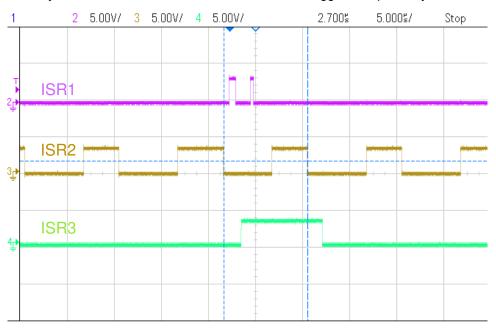

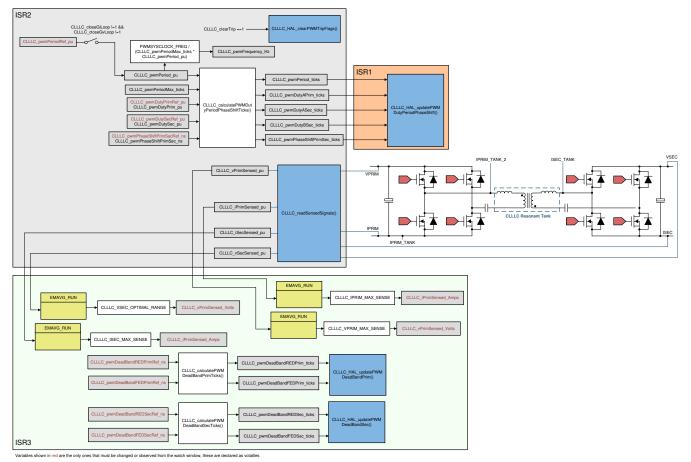

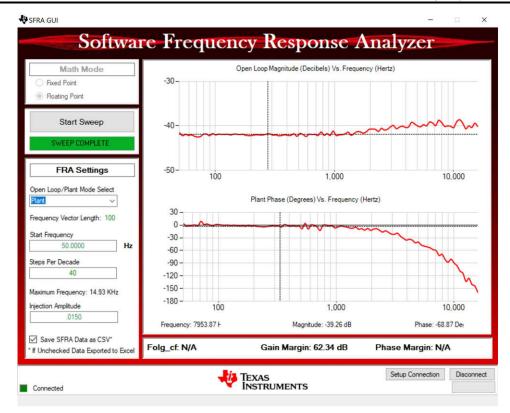

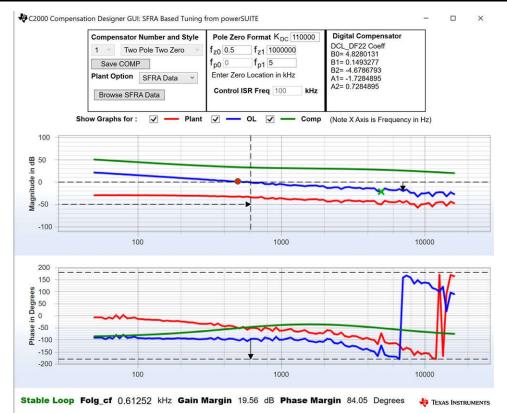

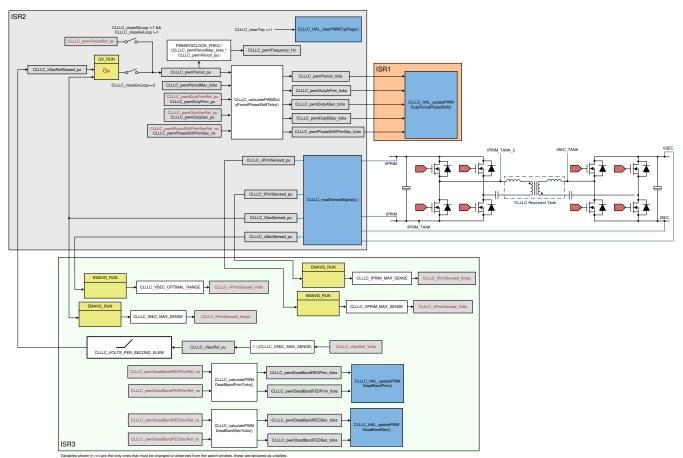

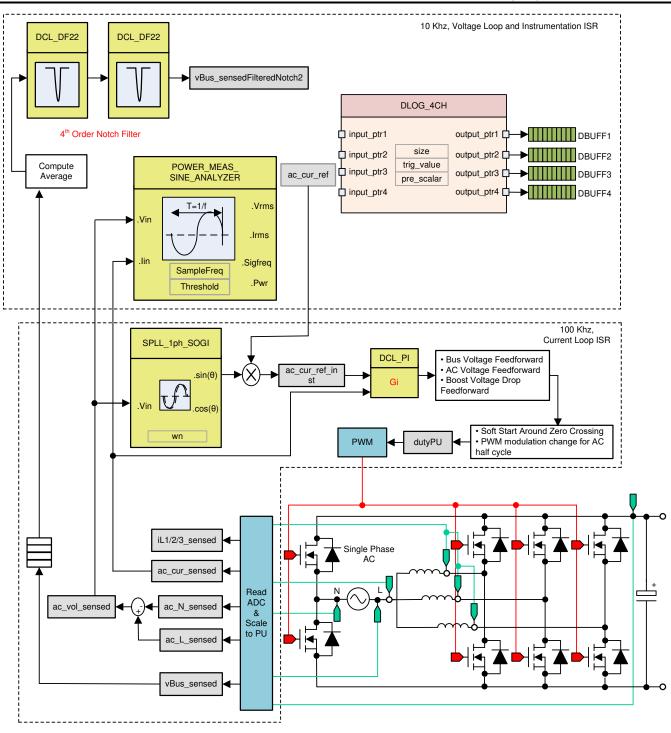

The OBC project consists of three ISRs (ISR1, ISR2, and ISR3) running on 2 cores, the C28x core and the CLA core. Using an ePWM for the ISR1 trigger, an eCAP for ISR2's trigger, and ADC for ISR3's trigger allows the ISR priority to be controlled entirely by hardware. Table 5-4 shows how each ISR is partitioned and its tasks.

| ISR           | Trigger source | C28x                                 | CLA                             |

|---------------|----------------|--------------------------------------|---------------------------------|

| ISR1 (120kHz) | ePWM           | N/A                                  | Update CLLLC PWM values         |

| ISR2 (120kHz) | eCAP           | PFC current loop                     | CLLLC control code, enable ISR1 |

| ISR3 (10kHz)  |                | PFC voltage loop,<br>instrumentation | N/A                             |

| Table 5-4. ISF | Partitions | and Tasks |

|----------------|------------|-----------|

|----------------|------------|-----------|

**ISR1** is the fastest and non-nestable ISR reserved for PWM updates and is ran entirely on CLA. ISR1 is triggered by the PRIM\_LEG1\_PWM\_BASE  $\rightarrow$  EPWM\_INT\_TBCTR\_U\_CMPC event. In general, this interrupt is disabled by writing a value to CMPC, which is greater than all possible TBPRD register values for PRIM\_LEG1\_PWM\_BASE. This is done through the CLLLC\_HAL\_setupISR1Trigger function. Following are the defines that are related to this ISR.

```

#define CLLLC_ISR1_PERIPHERAL_TRIG_BASE CLLLC_PRIM_LEG1_PWM_BASE

#define CLLLC_ISR1_TRIG INT_EPWM1

#define CLLLC_ISR1_PIE_GROUP INTERRUPT_ACK_GROUP3

```

```

#define CLLLC_ISR1_TRIG_CLA CLA_TRIGGER_EPWM1INT

```

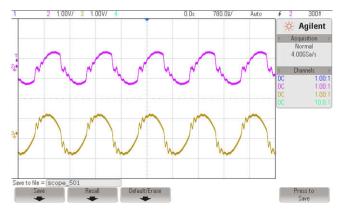

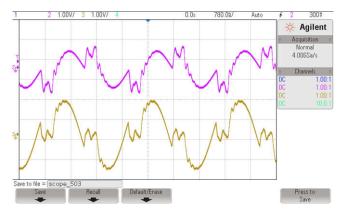

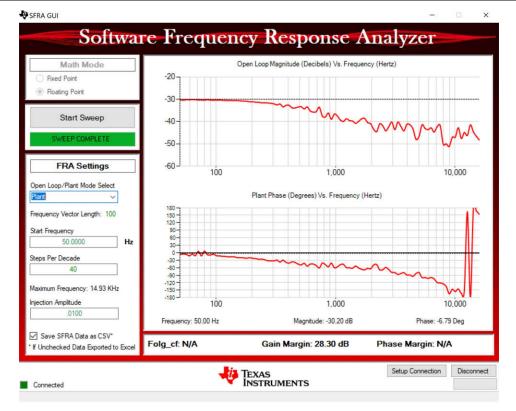

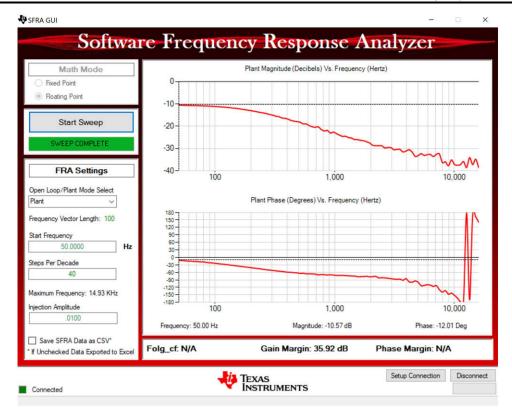

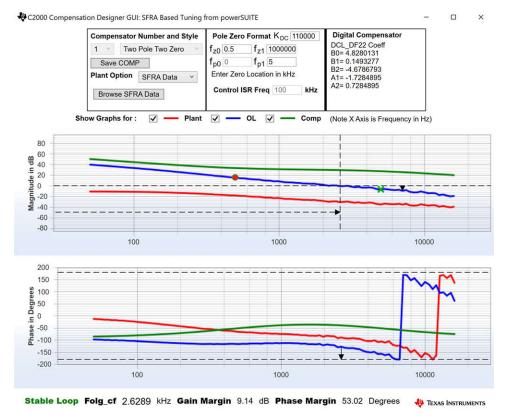

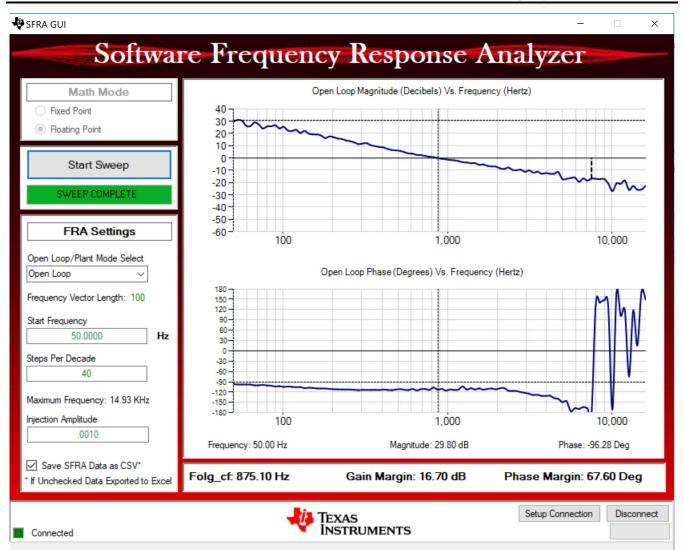

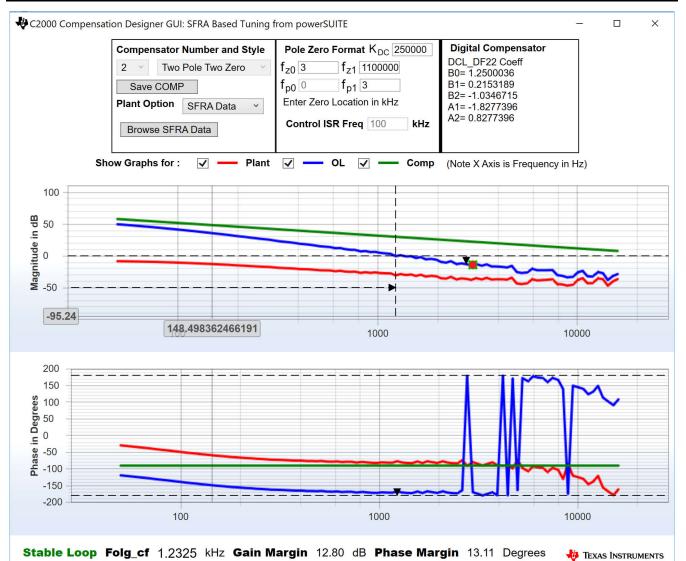

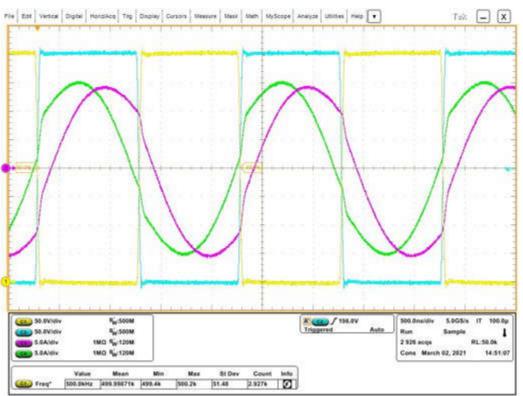

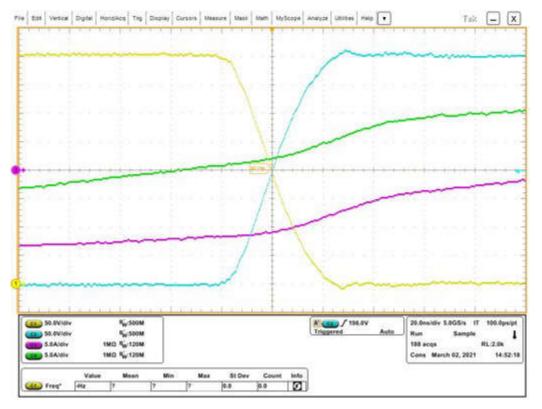

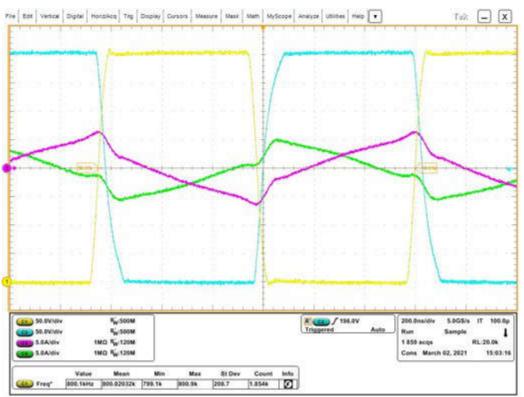

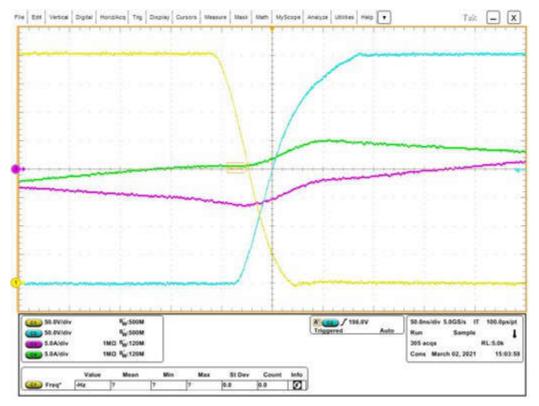

**ISR2** is split across both cores. This allows a simple modular code segregation for the TTPLPFC and CLLLC code. Both the ISR2 ran on the C28x and the ISR2 ran on the CLA are triggered by the same source and operate in tandem. The C28x core run task related to the TTPLPFC while the CLA core runs task related to the CLLLC's execution.