System-Level Crosstalk-Induced Efficiency Impact of DCDC Converter:

**Simulation to Measurement Correlation**

Joerg Goller, Jie Chen, and Rajen Murugan

APEC 2016 - March 20-24, 2016

SLYY087

### **Synopsis**

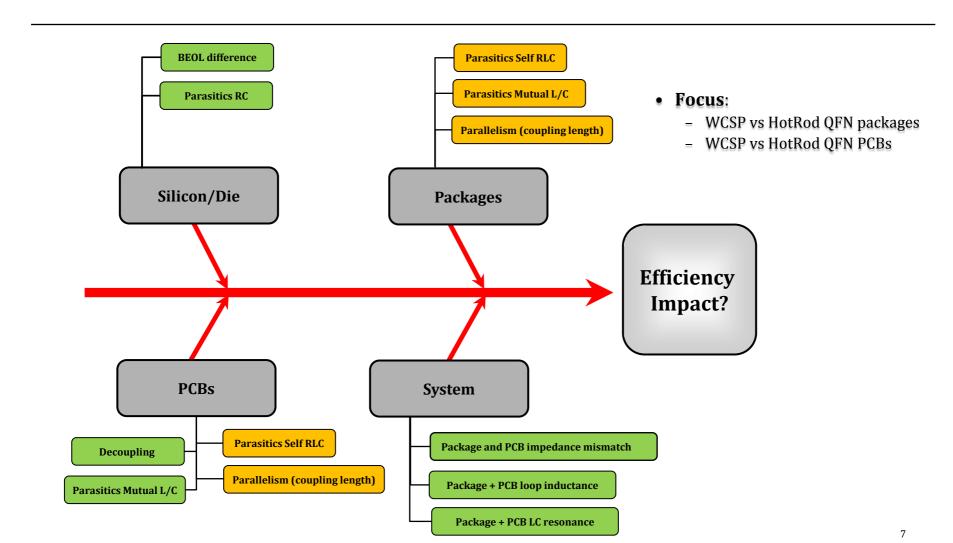

- Higher switching frequency,  $R_{DSON}$ , and gate charge  $(Q_g)$  are among some of the factors that contribute to efficiency impact.

- Additionally the system (i.e. package and PCB) electrical parasitics also contributes to efficiency performance degradation.

- In this work we show that 2<sup>nd</sup> order electromagnetic (EM) effects (viz. **mutual capacitive** and **inductive** parasitic coupling via crosstalk), beyond just self RLC, are becoming critical and can impact efficiency.

- Using co-design electrical modeling and simulation methodology, we demonstrate how crosstalk in the system impacted efficiency of the TPS63050<sup>TM</sup>, a TI's buck-boost converter.

- Good correlation between simulation and lab measurements was achieved.

- It is critical to assess performance impact of the system. It is recommended to integrate system-level co-verification modeling early in the design development phase.

# Background

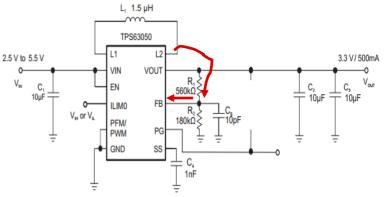

• TPS63050<sup>TM</sup> is a high efficiency, low quiescent-current buck-boost converter for consumer and industrial applications (0.5A, 2.5MHz).

• Support automatic PWM/PFM mode transition with fixed and adjustable output voltage versions.

• Packaged in:

WCSP (wafer-level chip scale)

• Size: 1.6 x 1.2mm, 12-pin, 0.4mm pitch)

HotRod<sup>TM</sup> QFN (quad-flat no leads)

• Size: 2.5 x 2.5mm, 12-pin, 0.5mm pitch)

2.5 V to 5.5 V  $V_{N}$   $C_{1}$   $V_{N}$   $C_{2}$   $V_{N}$   $V_{N}$

• Characterization of device packaged in HotRod<sup>TM</sup> yielded in approximately **identical DC** parameters (e.g. overall  $R_{DSON}$ ) vs.WCSP version.

• All **AC parameters are comparable** with the exception of **efficiency** - which was found to be considerably **lower** in the HotRod<sup>TM</sup> packaged device!

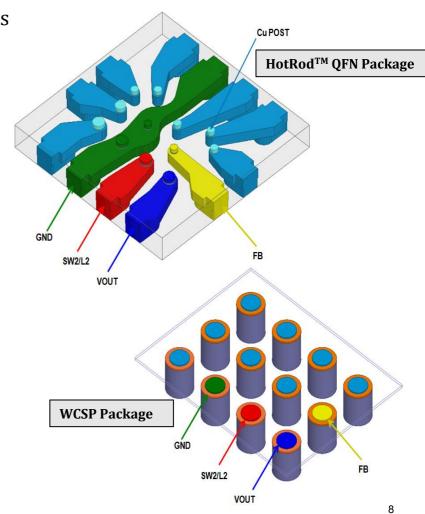

# **Packaging Technologies**

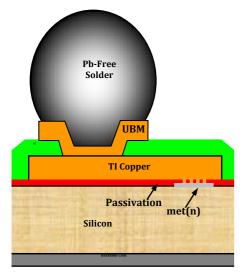

#### Wafer-level Chip Scale (WCS) Package [2]

- Designed for minimum size and footprint.

- Die-pkg ratio is 1:1.

- Wirebonds are eliminated/replaced by thick copper redistribution and solder bumps.

- Good current capabilities but limited in comparison to HotRod.

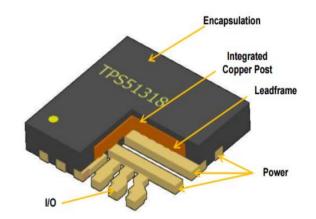

### HotRod<sup>TM</sup> QFN Package [3]

- Leadless packages specifically designed for power applications.

- Eliminates power device wire bonds by attaching the power device and/or die directly to the leadframe.

- Small foot-print, standard QFN pitch, low parasitics, and high-current capabilities.

- Connections to PCB via solder lands.

### Efficiency (η) Measurement

Lout

Iout

### **Additional Background Data**

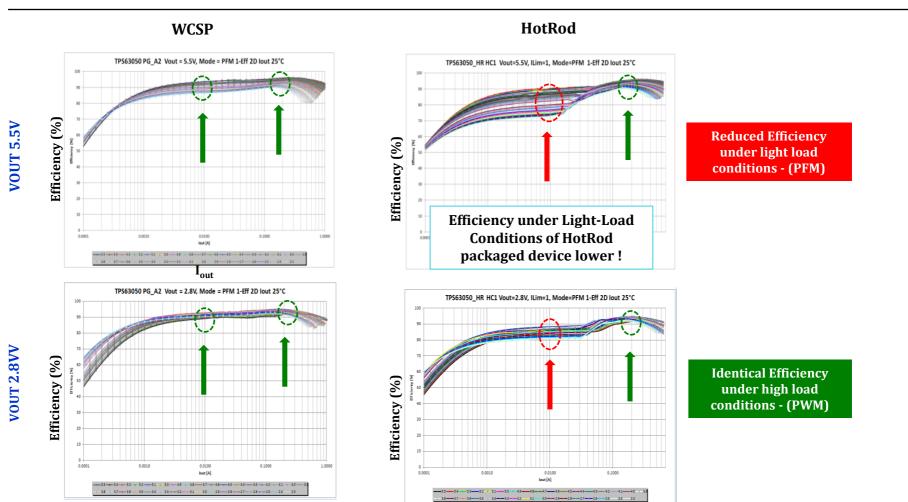

### Some observations:

- Under light load conditions only and when in PFM mode.

- For adjustable VOUT version only which utilize external feedback resistor divider network. Fix voltage version does not show degradation which utilize internal feedback divider network.

- Effect is temperature and VIN independent.

- Fix voltage version and adjustable devices have identical silicon.

- Baselayer are identical

- Different package technologies (WCSP vs. HR)

- Metal system differences:

- Top metal layers changed for HotRod package options

- While doing so, implemented some improvements for routing and shielding of critical signals such as FB (feedback)

- Minor routing differences in EVM/Board layout due to different package breakout /fan-out

## **Debug/Investigative Fishbone**

### Package Parasitics Comparison

- Performed with 3D Quasi-Static electromagnetic s

- Employ volumetric meshing to capture 3D effect.

- Extracted self (RLC) and mutual ( $C_M$  and  $L_M$ ).

#### — Comparative results:

| WCSP (@ 2.5MHz)   |          |          |        |          |         |  |  |  |

|-------------------|----------|----------|--------|----------|---------|--|--|--|

|                   | R (mOhm) | L (nH)   | C (fF) | Lm (nH)  | Cm (fF) |  |  |  |

| FB                | 0.72177  | 0.043981 | 22.029 |          |         |  |  |  |

| SW2/L2            | 0.72049  | 0.043946 | 22.04  | 0.0084   | 1.2027  |  |  |  |

| VOUT              | 0.72088  | 0.043924 | 20.278 | 0.011792 | 4.8096  |  |  |  |

| HotRod (@ 2.5MHz) |          |          |        |          |         |  |  |  |

|                   | R (mOhm) | L (nH)   | C (fF) | Lm (nH)  | Cm (fF) |  |  |  |

| FB                | 1.4394   | 0.22713  | 111.84 |          |         |  |  |  |

|                   |          |          |        |          |         |  |  |  |

| SW2/L2            | 0.75544  | 0.13111  | 117.38 | 0.0103   | 9.536   |  |  |  |

- $C_{MHR} > C_{MWCSP}$  (approximately 8X)

- $L_{MHR} > L_{MWCSP}$  (approximately 1.2X)

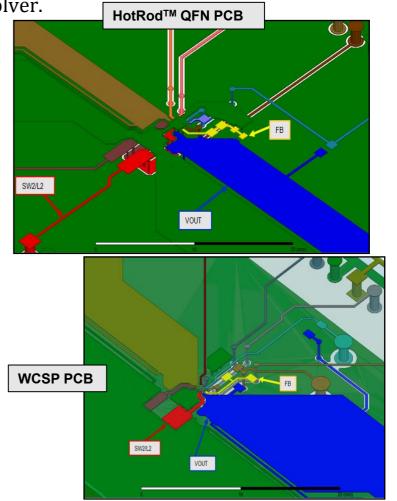

### **PCB Parasitics Comparison**

- Performed with 3D Quasi-Static electromagnetic solver.

- Employ volumetric meshing to capture 3D effect.

- Extracted self (RLC) and mutual ( $C_M$  and  $L_M$ ).

#### — Comparative results:

| WCSP (@ 2.5MHz)   |          |        |        |         |         |  |  |  |

|-------------------|----------|--------|--------|---------|---------|--|--|--|

|                   | R (mOhm) | L (nH) | C (pF) | Lm (nH) | Cm (pF) |  |  |  |

| FB                | 15.551   | 3.258  | 0.641  |         |         |  |  |  |

| SW2/L2            | 8.409    | 1.866  | 1.056  | 0.0678  | 0.012   |  |  |  |

| VOUT              | 7.394    | 8.663  | 13.348 | 0.4840  | 0.201   |  |  |  |

| HotRod (@ 2.5MHz) |          |        |        |         |         |  |  |  |

|                   | R (mOhm) | L (nH) | C (pF) | Lm (nH) | Cm (pF) |  |  |  |

| FB                | 6.561    | 1.268  | 0.753  |         |         |  |  |  |

| SW2/L2            | 6.164    | 2.637  | 2.823  | 0.0157  | 0.0031  |  |  |  |

| Vout              | 10.525   | 8.352  | 8.840  | 0.1490  | 0.174   |  |  |  |

- HotRod<sup>TM</sup> LC<sub>SELF</sub> > WCSP LC<sub>SELF</sub>

- $HotRod^{TM} L_M C_M < WCSP L_M C_M$

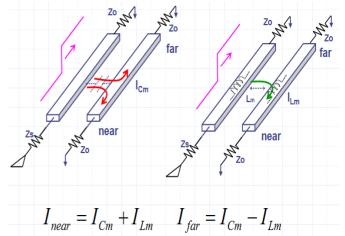

## **Crosstalk Coupling Mechanisms**

• Crosstalk (XTLK) is the electromagnetic coupling of energy from one line to another via:

- Mutual inductance (magnetic field)  $\rightarrow V_{Lm} = L_m \frac{dl}{dt}$

- Mutual capacitance (electric field)  $\rightarrow I_{Cm} = C_m \frac{dV}{dt}$

- Crosstalk generally depends on:

- Edge rate (slew rate)

- Voltage amplitude

- Parallelism (coupling length)

- Near-end (NEXT) and Far-end (FEXT)

- Root cause of noise coupling:

- SW pin coupled noise to FB pin.

- Parallelism higher in HotRod package

- NEXT (coupled to die EA/Comp)

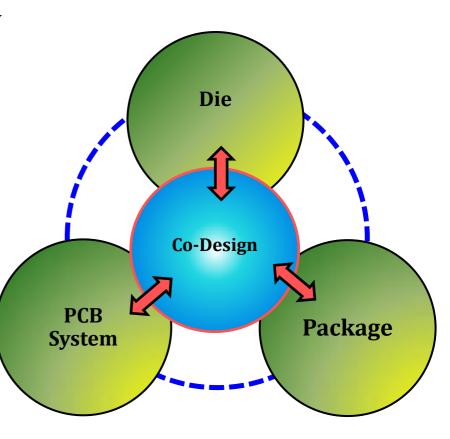

# **System-Level Modeling Methodology**

- Use co-analysis methodology previously developed and correlated to silicon measurements [4-5].

- Employ Cadence Virtuoso environment for system-level analysis.

- Packages and PCBs electrical parasitics models extracted via a 3D quasi-static solver.

- Models include both parasitic self and mutual parasitics.

- Full system-level analysis include DCDC converter transistor spice network, package, and PCB spice netlist.

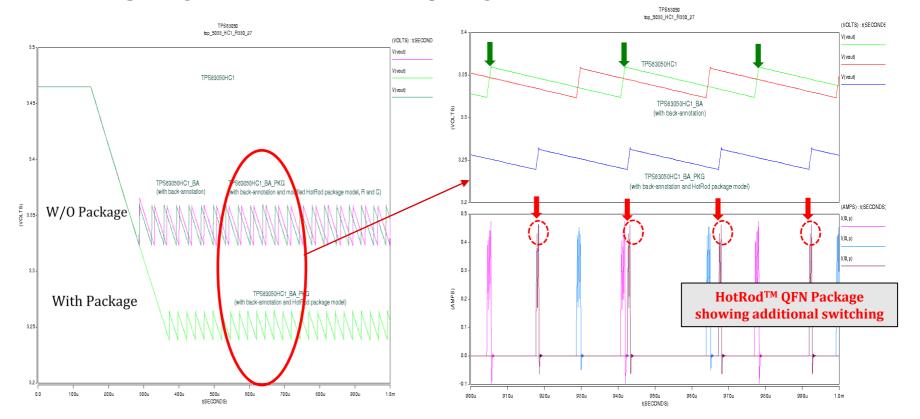

## **System-Level Modeling Results**

- Performed using system-level co-design modeling methodologies.

- Noise coupling causes EA/Comparator to assume false VOUT and in turn additional switching to regulate. Observed in device packaged in HotRod<sup>TM</sup> QFN.

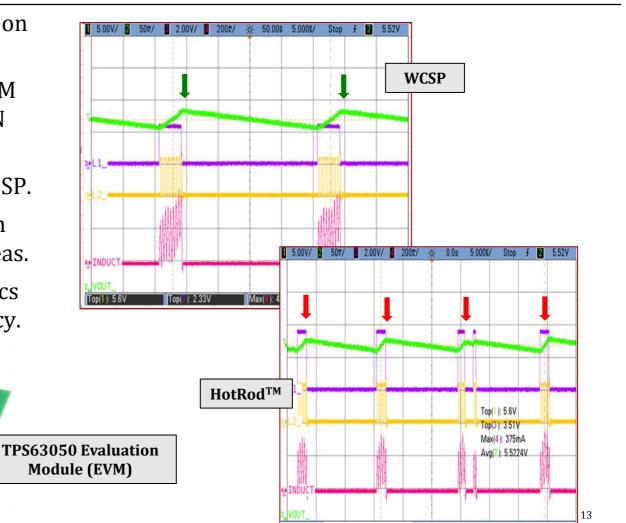

### Simulation to Meas. Correlation

- Measurement performed on EVM system.

- Higher activity during PFM mode with HotRod<sup>TM</sup> QFN package yielding:

- ➤ less efficiency vs WCSP.

- Good correlation between simulation and silicon meas.

- Package and PCB parasitics effect can impact efficiency.

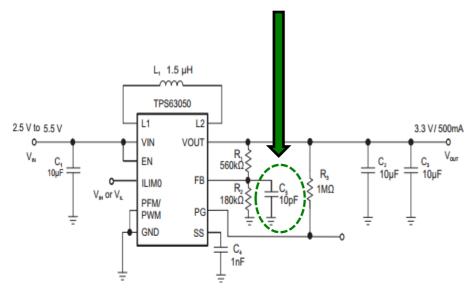

### The Work-Around

- Need to decouple/filter noise coupled to FB line on the HotRod QFN packaged device.

- Many external (i.e. on PCB) mitigation techniques were investigated.

- Optimal fix was to add an external decap (10pF) to FB pin on PCB (shown below)

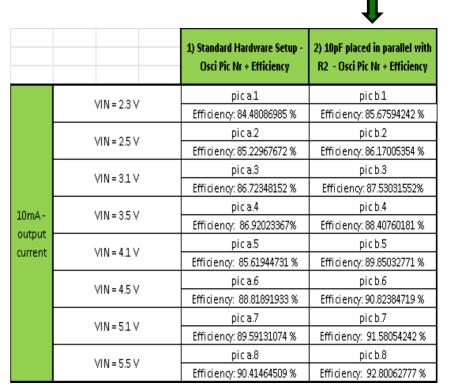

# Lab measurement shows efficiency Improvement with 10pF decap

### **Summary**

- Root cause of efficiency drop on TPS63050<sup>TM</sup> was primarily due to mutual capacitive (i.e. crosstalk) coupling on package.

- Coupling noise reduction achieved by decap filtering on PCB not a cost-effective option!

- Issue missed in verification as initial simulations (using first order effect only) with chip-level back-annotation showed no efficiency issue.

- Second and higher order electromagnetic effects are becoming critical.

- Use co-design modeling and analysis methodologies to assess system (package and PCB) parasitic impact early in the design phase.

- Co-verification is a **MUST** for first pass design success.

### References

- [1] TPS6305x Single Inductor Buck-Boost With 1-A Switches and Adjustable Soft Start specification sheet <a href="http://www.ti.com/product/tps63050">http://www.ti.com/product/tps63050</a>

- [2] AN-1112 DSBGA Wafer Level Chip Scale Package <a href="http://www.ti.com/lit/an/snva009af/">http://www.ti.com/lit/an/snva009af/</a>

- [3] HotRod QFN Package PCB Attachment <a href="http://www.ti.com/lit/an/slua715/">http://www.ti.com/lit/an/slua715/</a>

- [4] R. Murugan, S. Chakraborty, S. Mukherjee, D. Gope, and V. Jandhyala, "Building IC-package-PCB-system EMI/EMC verification and early design flows: Challenges and Methods", Proceedings of DESIGNCON conf., Santa Clara, February 2010.

- [5] J. Chen, R. DeMoor, M. Mi, and R. Murugan, "Using Co-Design Techniques to Minimize IC Package Cost Without Compromising Performance: Simulation and Measurement Validation", IEEE Symposium on Electromagnetic Compatibility & Signal Integrity, EMC&SI, April 28-30, 2015 – Best Industry Paper Award.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive **Amplifiers** amplifier.ti.com Communications and Telecom www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps DSP dsp.ti.com **Energy and Lighting** www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical Logic Security www.ti.com/security logic.ti.com

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors www.ti.com/omap TI E2E Community e2e.ti.com

Wireless Connectivity www.ti.com/wirelessconnectivity