# AFE10004-EP 4-Channel Power-Amplifier Precision Analog Front End With Integrated EEPROM and Gate Bias Switches

## 1 Features

- Specified for defense and aerospace applications

- Controlled baseline

- One assembly and test site

- One fabrication site

- Product traceability

- Extended product life cycle

- Local and remote diode temperature sensor

- $\pm 2.5^\circ\text{C}$  error, maximum

- 0.0625°C resolution

- Internal EEPROM for autonomous operation

- Storage for four independent transfer functions

- Device configuration storage

- Open space for user storage

- Qualified for 15-year retention

- Four analog outputs

- Four monotonic DACs: 1.22mV resolution

- Automatically configured output ranges:

- Positive output voltage: 5.5V, maximum

- Negative output voltage: -10V, minimum

- High current drive capability:

- Source up to 100mA

- Sink up to 20mA

- High capacitive load tolerant: up to 15 $\mu\text{F}$

- Gate bias on and off control switches

- Two programmable off voltages

- Two auxiliary DACs: 1.22mV resolution

- Fast switching time: 50ns, typical

- Low resistance: 3 $\Omega$ , maximum

- Built-in sequencing control

- Internal 2.5V reference

- SPI and I<sup>2</sup>C interfaces: 1.7V to 3.6V operation

- SPI: 4-wire Interface

- I<sup>2</sup>C: Eight selectable peripheral addresses

- Specified temperature range: -55°C to +125°C

## 2 Applications

- Radar

- Electronic warfare

- Communications payload

- Defense radio

## 3 Description

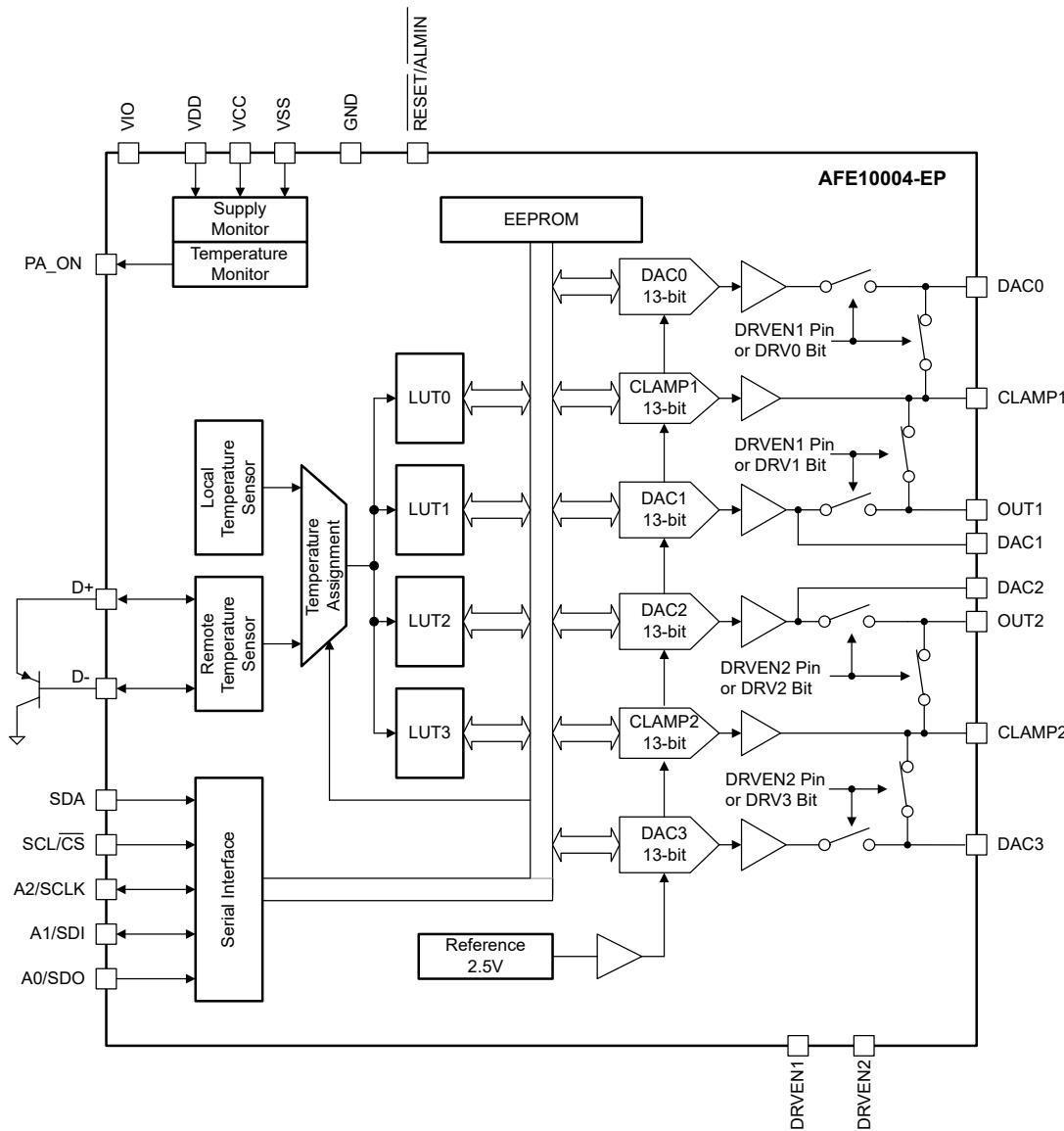

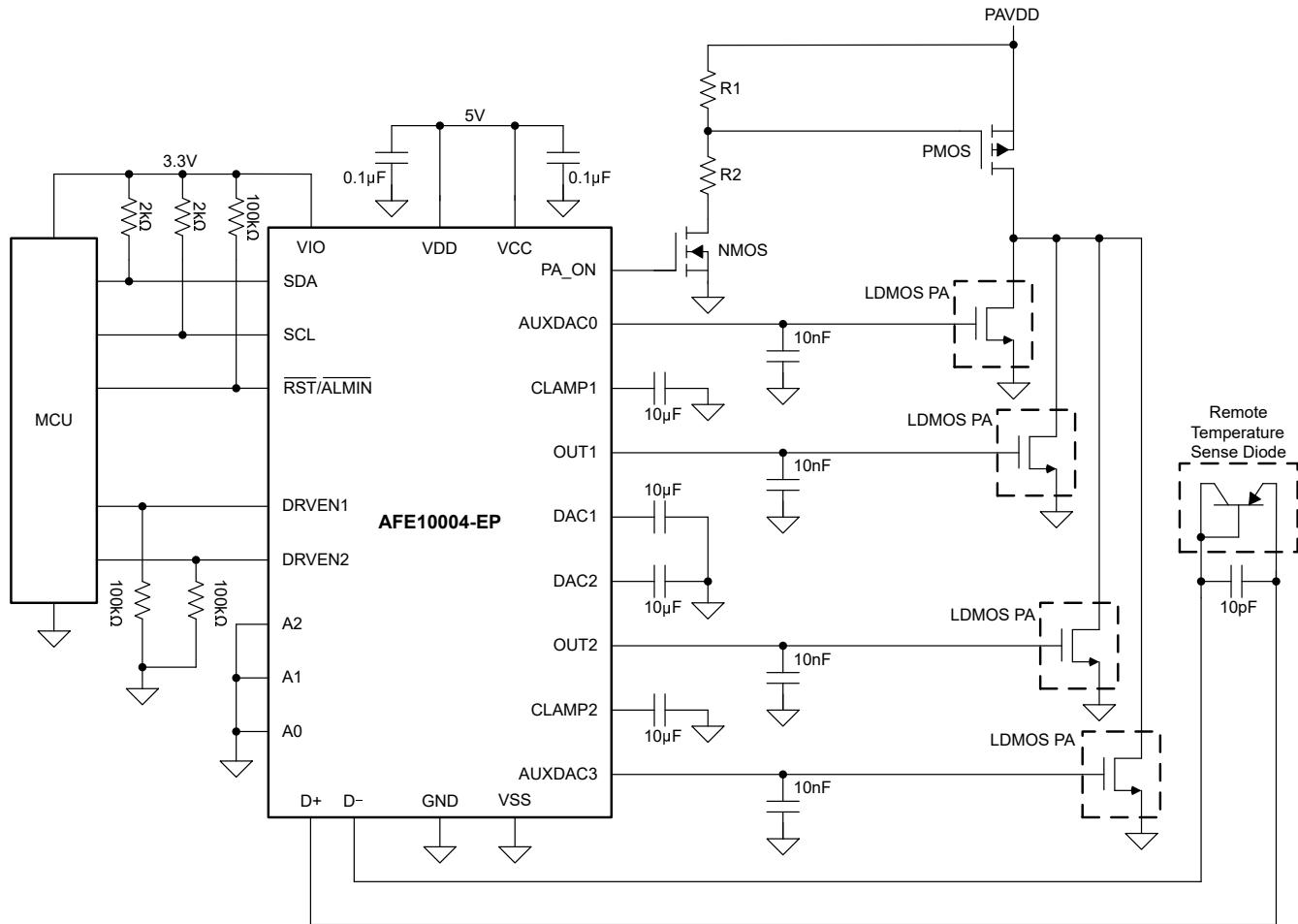

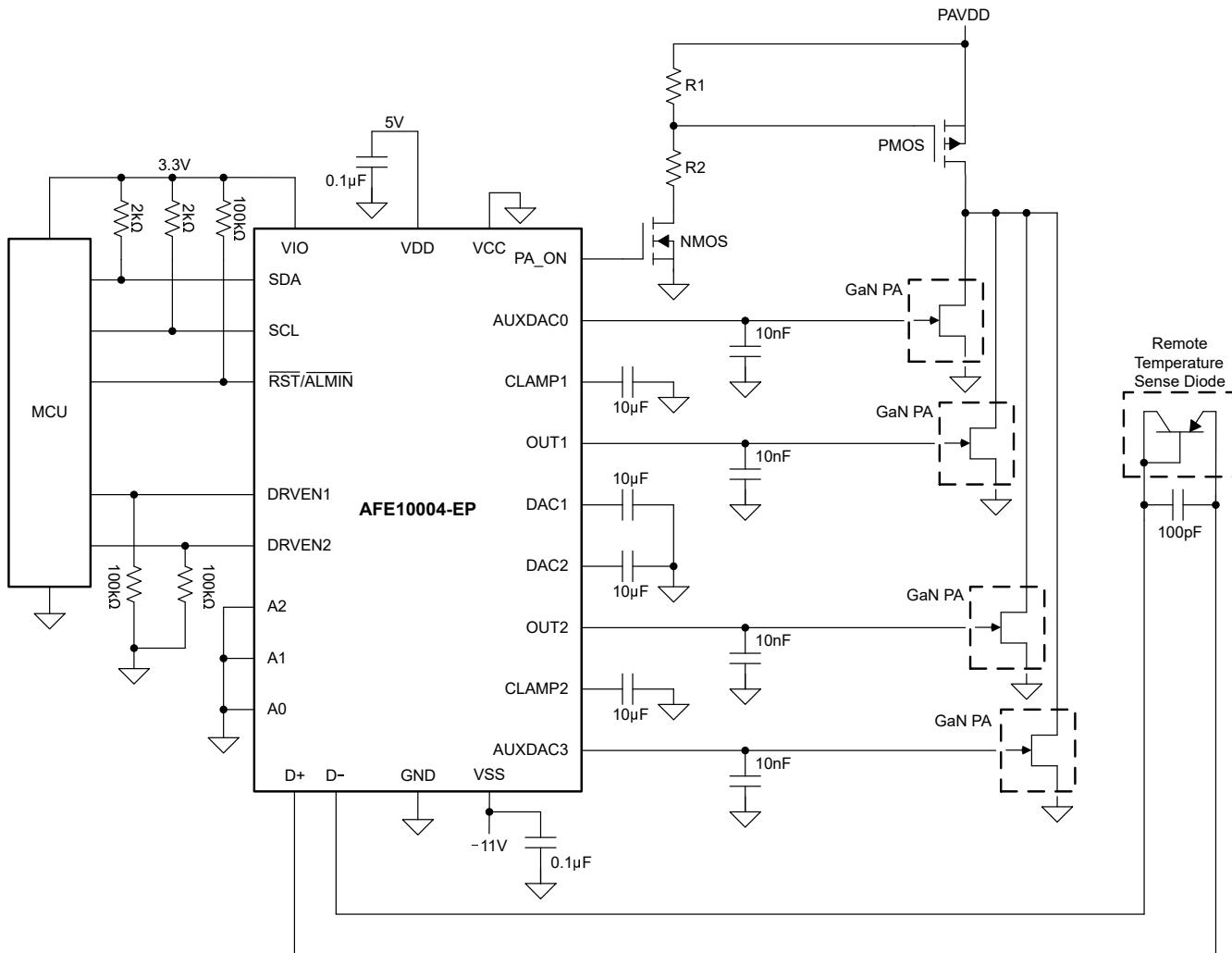

The AFE10004-EP is a highly integrated, autonomous, power-amplifier (PA) precision analog front end (AFE) that includes four temperature compensation digital-to-analog converters (DACs), integrated EEPROM, and gate bias switches. The four DACs are programmed by four independent, user-defined, temperature-to-voltage transfer functions stored in the internal EEPROM. This design allows correction any temperature effects to be corrected without additional external circuitry. After start-up, the device operates without intervention from a system controller to provide a complete system for setting and compensating bias voltages in control applications.

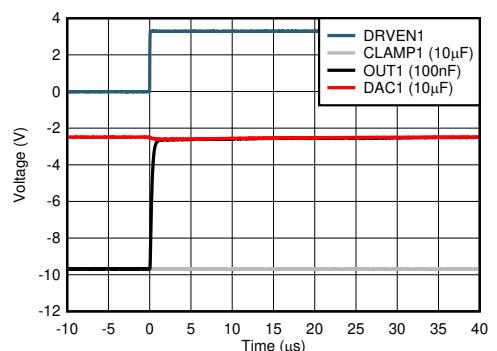

The AFE10004-EP has four gate bias outputs that are switched on and off through dedicated control pins. The gate bias switches are designed for fast response. In combination with the device PA\_ON pin, this fast response enables correct power sequencing and protection of depletion-mode transistors, such as GaAs and GaN.

The function integration and wide operating temperature range make the AFE10004-EP an excellent choice as an all-in-one, autonomous bias control circuit for the power amplifiers found in RF systems. The flexible DAC output ranges and built-in sequencing features let the device be used as a biasing controller for a large variety of transistor technologies, such as LDMOS, GaAs, and GaN.

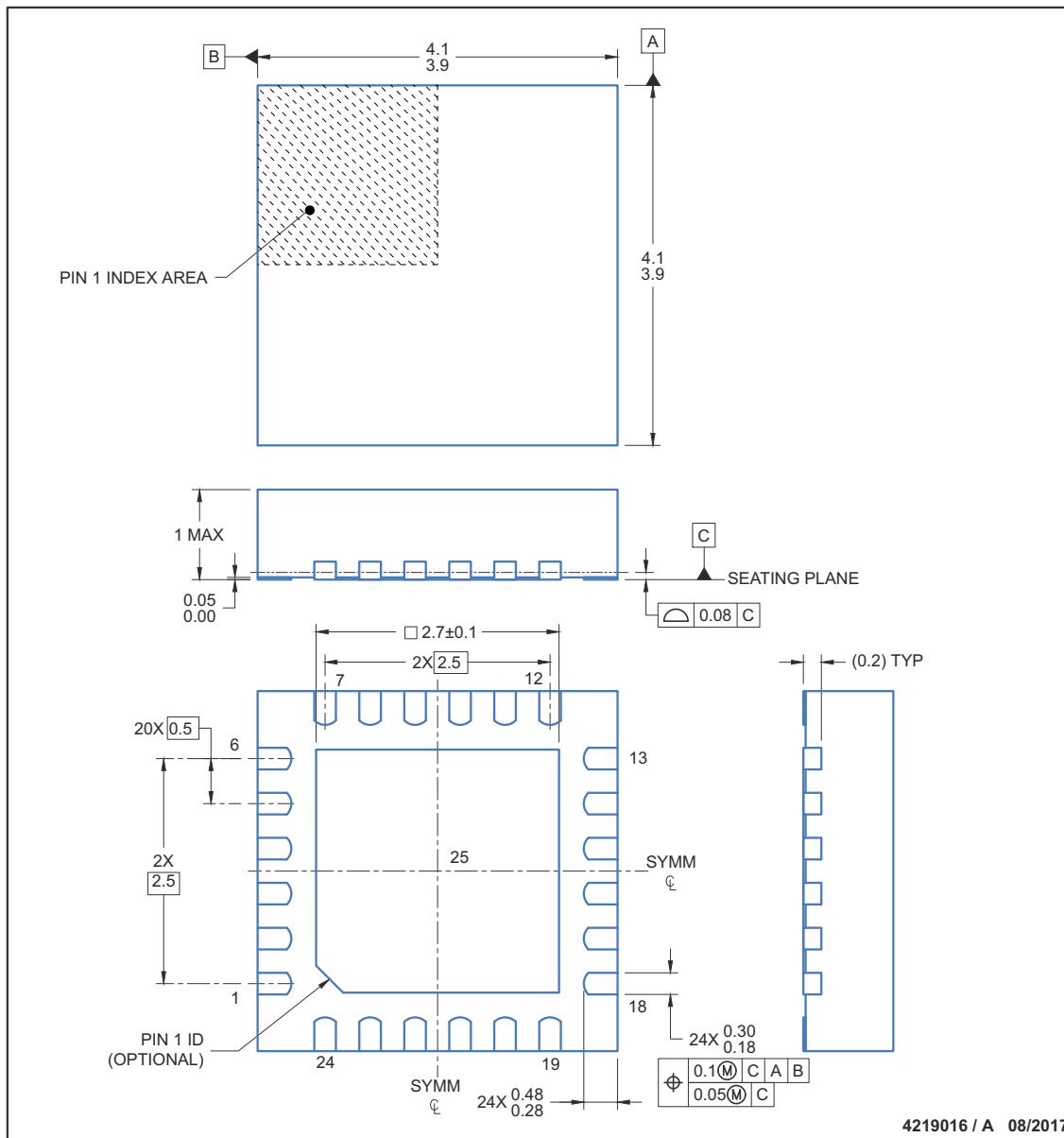

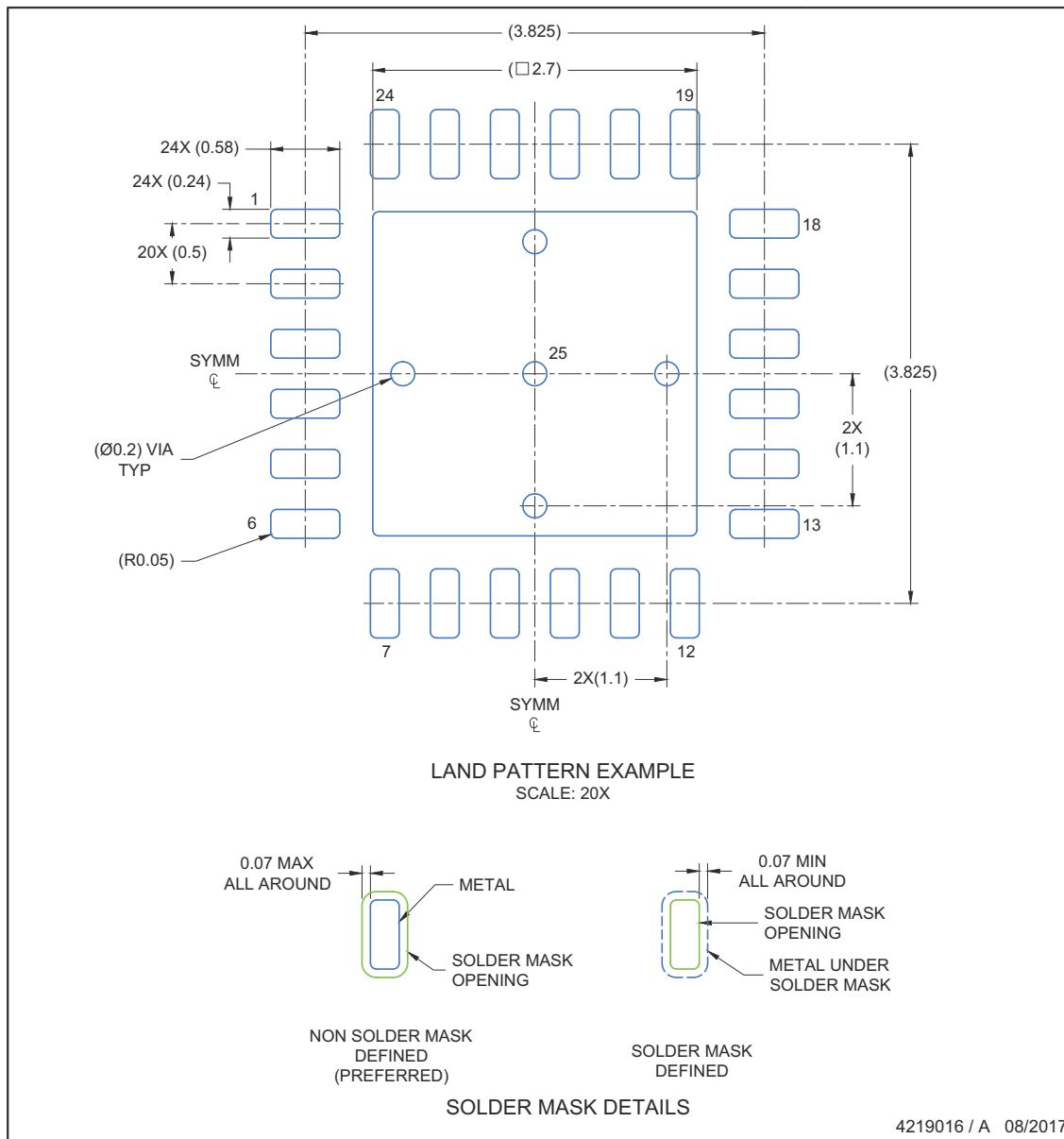

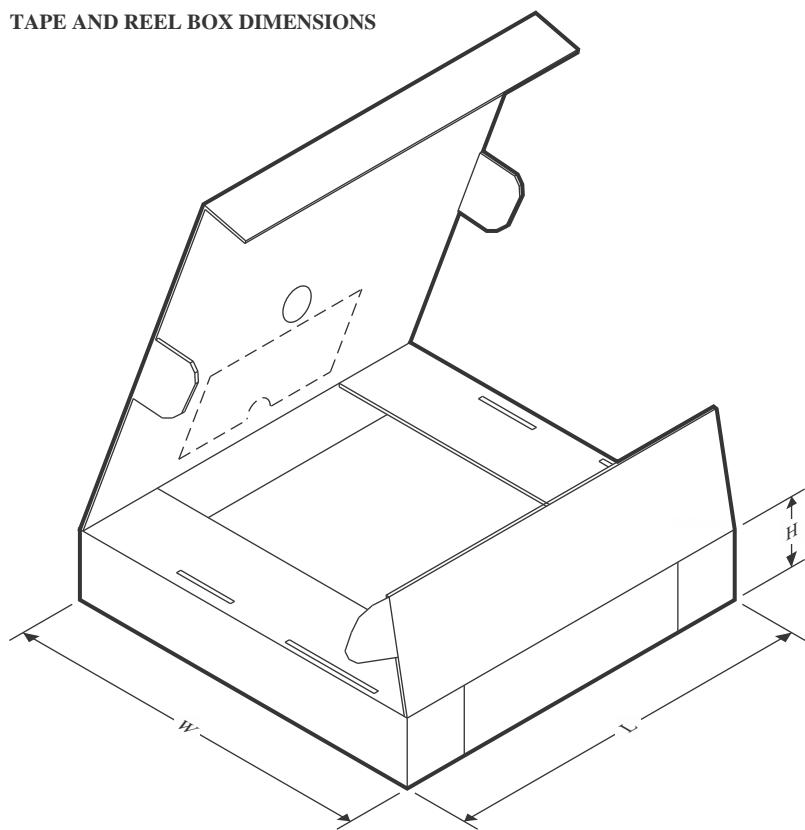

## Package Information

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| AFE10004-EP | RGE (VQFN, 24)         | 4mm × 4mm                   |

(1) For more information, see [Section 11](#).

(2) The package size (length × width) is a nominal value and includes pins, where applicable.

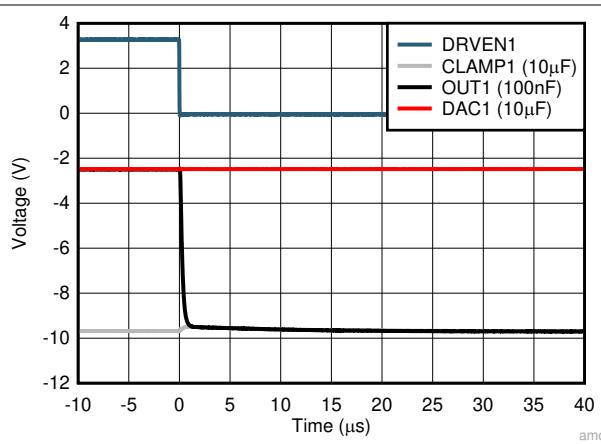

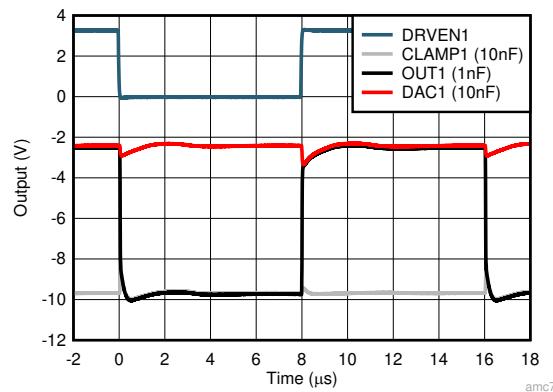

Gate Bias Switch Response

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## Table of Contents

|                                                |           |                                                                            |            |

|------------------------------------------------|-----------|----------------------------------------------------------------------------|------------|

| <b>1 Features</b> .....                        | <b>1</b>  | <b>7 Register Maps</b> .....                                               | <b>52</b>  |

| <b>2 Applications</b> .....                    | <b>1</b>  | 7.1 I <sup>2</sup> C Register Maps.....                                    | <b>52</b>  |

| <b>3 Description</b> .....                     | <b>1</b>  | 7.2 SPI Register Maps.....                                                 | <b>61</b>  |

| <b>4 Pin Configuration and Functions</b> ..... | <b>3</b>  | 7.3 Registers.....                                                         | <b>68</b>  |

| <b>5 Specifications</b> .....                  | <b>5</b>  | <b>8 Application and Implementation</b> .....                              | <b>139</b> |

| 5.1 Absolute Maximum Ratings.....              | 5         | 8.1 Application Information.....                                           | 139        |

| 5.2 ESD Ratings.....                           | 5         | 8.2 Typical Applications.....                                              | 142        |

| 5.3 Recommended Operating Conditions.....      | 5         | 8.3 Initialization Setup.....                                              | 147        |

| 5.4 Thermal Information.....                   | 6         | 8.4 Power Supply Recommendations.....                                      | 147        |

| 5.5 Electrical Characteristics.....            | 6         | 8.5 Layout.....                                                            | 147        |

| 5.6 Timing Requirements.....                   | 9         | <b>9 Device and Documentation Support</b> .....                            | <b>150</b> |

| 5.7 Switching Characteristics.....             | 10        | 9.1 Documentation Support.....                                             | 150        |

| 5.8 Timing Diagrams .....                      | 11        | 9.2 Receiving Notification of Documentation Updates.....                   | 150        |

| 5.9 Typical Characteristics.....               | 12        | 9.3 Support Resources.....                                                 | 150        |

| <b>6 Detailed Description</b> .....            | <b>19</b> | 9.4 Trademarks.....                                                        | 150        |

| 6.1 Overview.....                              | 19        | 9.5 Electrostatic Discharge Caution.....                                   | 150        |

| 6.2 Functional Block Diagram.....              | 19        | 9.6 Glossary.....                                                          | 150        |

| 6.3 Feature Description.....                   | 20        | <b>10 Revision History</b> .....                                           | <b>150</b> |

| 6.4 Device Functional Modes.....               | 43        | <b>11 Mechanical, Packaging, and Orderable</b><br><b>Information</b> ..... | <b>150</b> |

| 6.5 Programming.....                           | 45        |                                                                            |            |

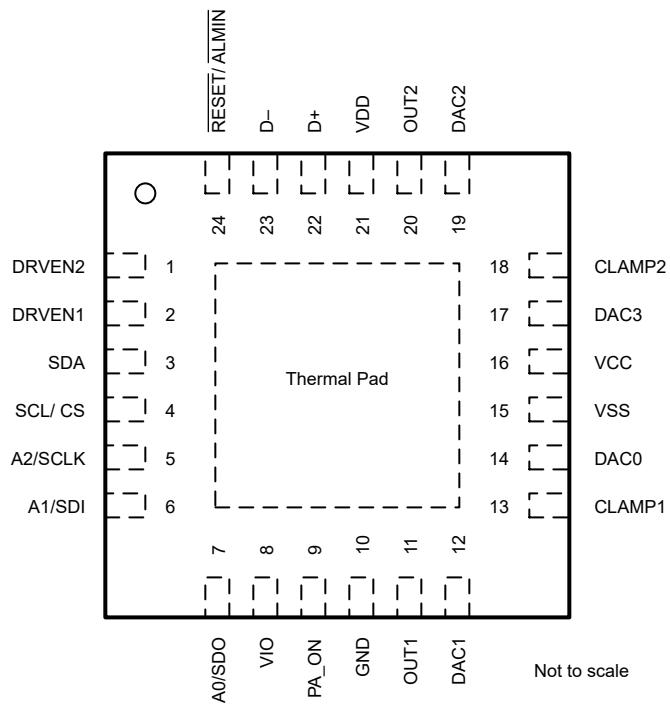

## 4 Pin Configuration and Functions

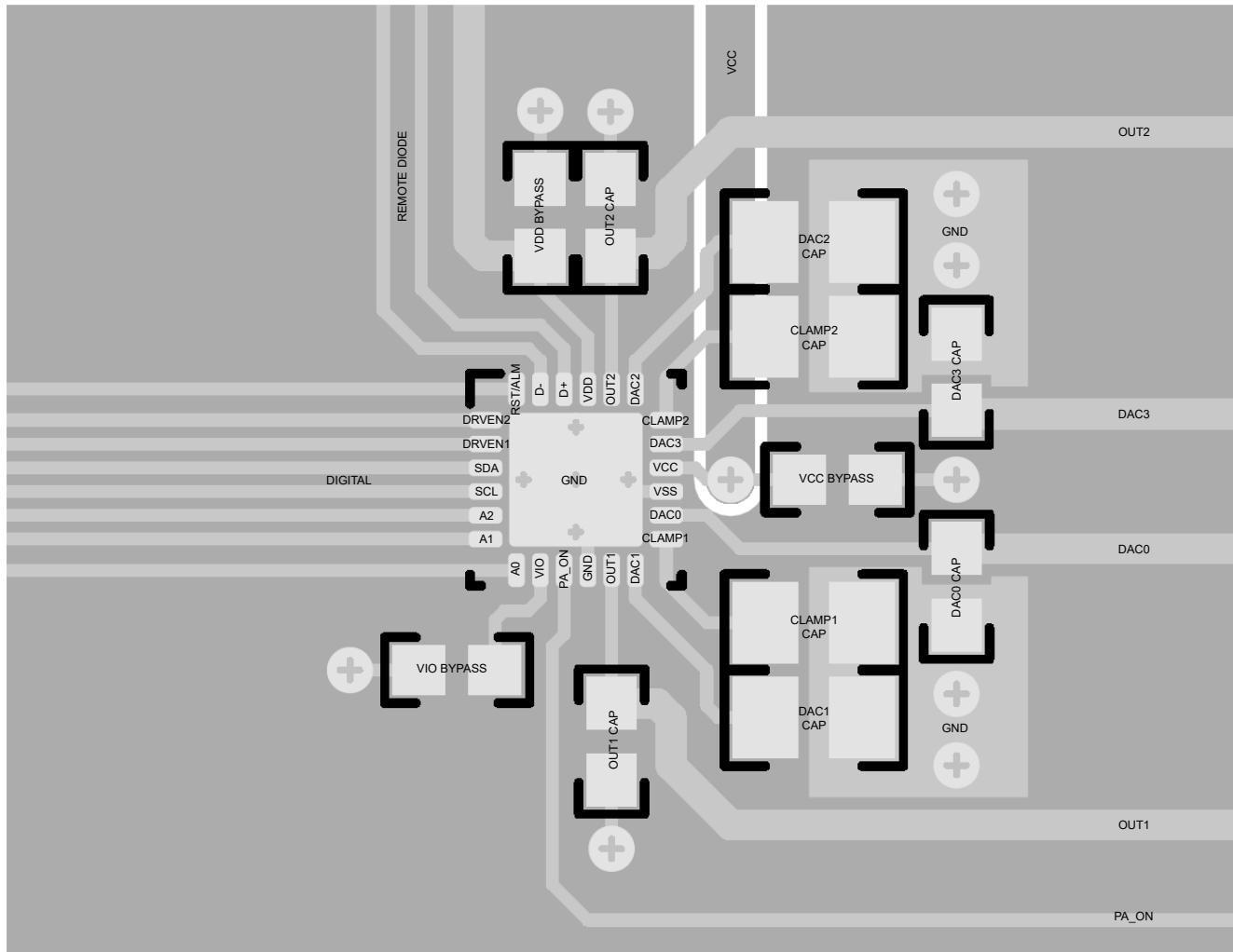

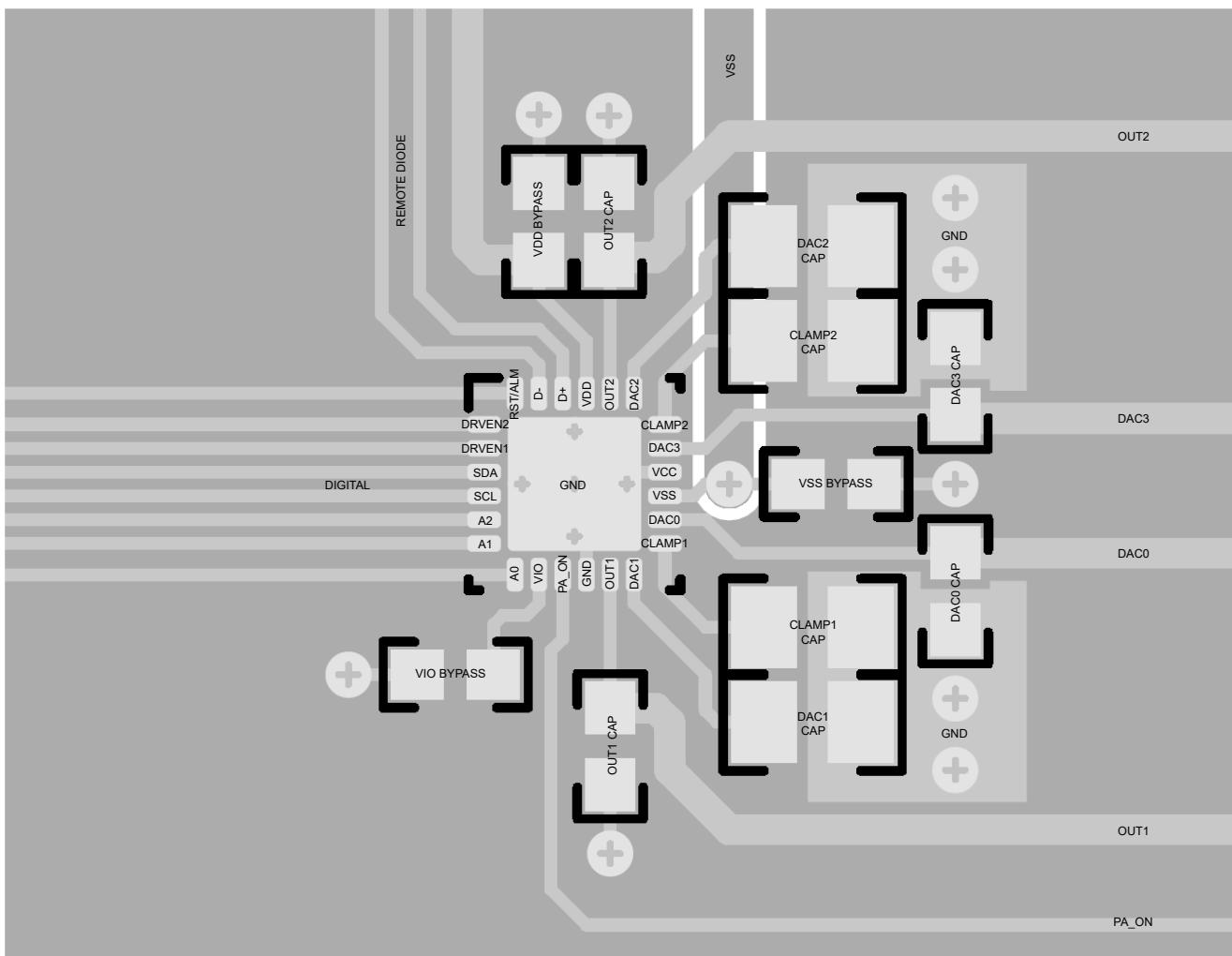

Figure 4-1. RGE Package, 24-Pin VQFN (Top View)

**Table 4-1. Pin Functions**

| PIN         |              | TYPE         | DESCRIPTION                                                                                                                                                                                                                     |

|-------------|--------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.         | NAME         |              |                                                                                                                                                                                                                                 |

| 1           | DRVEN2       | Input        |                                                                                                                                                                                                                                 |

| 2           | DRVEN1       | Input        | Asynchronous switch control signals.                                                                                                                                                                                            |

| 3           | SDA          | Input/Output | I <sup>2</sup> C bidirectional data line. <i>This pin must be connected to GND if communicating to the device through SPI.</i>                                                                                                  |

| 4           | SCL/ CS      | Input        | I <sup>2</sup> C: Clock input.<br>SPI: Active-low serial data enable. This input is the frame synchronization signal for the serial data. When the signal goes low, this pin enables the serial interface input shift register. |

| 5           | A2/SCLK      | Input        | I <sup>2</sup> C: Target address selector.<br>SPI: Clock input.                                                                                                                                                                 |

| 6           | A1/SDI       | Input        | I <sup>2</sup> C: Target address selector.<br>SPI: Data input. Data are clocked into the input shift register on each falling edge of the SCLK pin.                                                                             |

| 7           | A0/SDO       | Input/Output | I <sup>2</sup> C: Target address selector.<br>SPI: Data output. The SDO pin must be enabled before operation by setting the SDOEN bit. Data are clocked out of the input shift register on each rising edge of the SCLK pin.    |

| 8           | VIO          | Power        | IO supply voltage (1.65V to 3.6V). This pin sets the I/O operating voltage for the device.                                                                                                                                      |

| 9           | PA_ON        | Output       | Synchronization signal. PA_ON is a CMOS output. The PA_ON pin is set low until the device is ready for full operation or if an alarm condition is detected.                                                                     |

| 10          | GND          | Ground       | Ground reference point for all circuitry on the device                                                                                                                                                                          |

| 11          | OUT1         | Output       | DAC1 switch output                                                                                                                                                                                                              |

| 12          | DAC1         | Output       | DAC1 buffer output                                                                                                                                                                                                              |

| 13          | CLAMP1       | Output       | CLAMP1 buffer output                                                                                                                                                                                                            |

| 14          | DAC0         | Output       | DAC0 buffer output                                                                                                                                                                                                              |

| 15          | VSS          | Power        | Output buffers negative analog power supply (-11V to 0V)                                                                                                                                                                        |

| 16          | VCC          | Power        | Output buffers positive analog power supply (0V to 5.5V)                                                                                                                                                                        |

| 17          | DAC3         | Output       | DAC3 buffer output                                                                                                                                                                                                              |

| 18          | CLAMP2       | Output       | CLAMP2 buffer output                                                                                                                                                                                                            |

| 19          | DAC2         | Output       | DAC2 buffer output                                                                                                                                                                                                              |

| 20          | OUT2         | Output       | DAC2 switch output                                                                                                                                                                                                              |

| 21          | VDD          | Power        | Analog supply voltage (4.5V to 5.5V)                                                                                                                                                                                            |

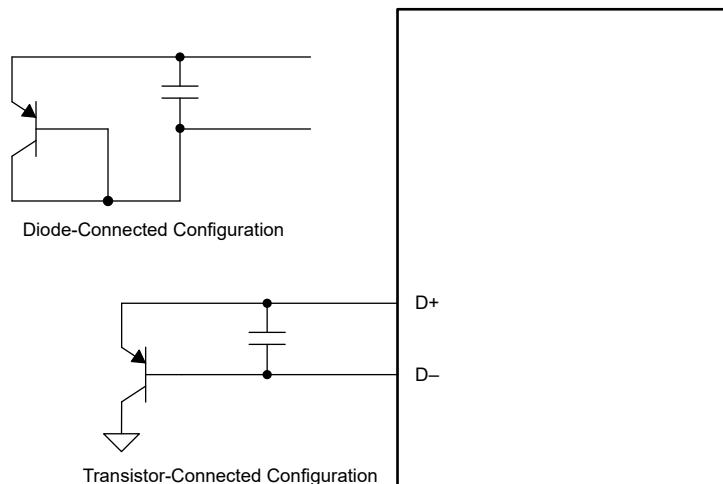

| 22          | D+           | Input        |                                                                                                                                                                                                                                 |

| 23          | D-           | Input        | Remote temperature sensor connections. If unused, connect these pins together.                                                                                                                                                  |

| 24          | RESET/ ALMIN | Input        | Active low reset input. Logic low on this pin causes the device to initiate a reset event. Alternatively, this pin can be configured as an active-low alarm signal into the device to initiate an alarm event.                  |

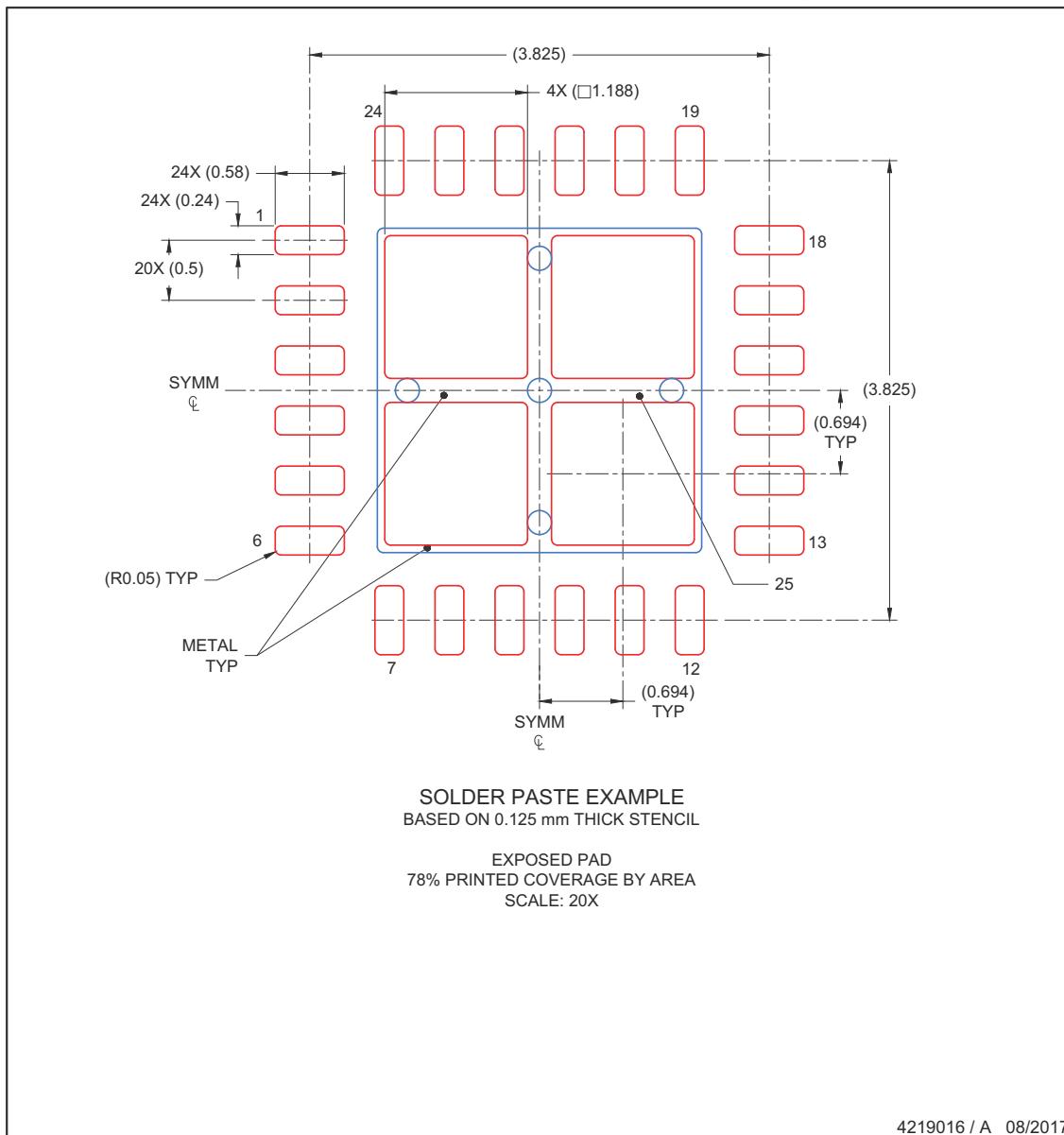

| Thermal Pad | Thermal Pad  | —            | The thermal pad is located on the package underside. Connect the thermal pad to any internal PCB ground plane through multiple vias for good thermal performance.                                                               |

## 5 Specifications

### 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                |                      |                                       | MIN            | MAX            | UNIT |

|----------------|----------------------|---------------------------------------|----------------|----------------|------|

| Supply voltage |                      | $V_{DD}$ to GND                       | -0.3           | 6              | V    |

|                |                      | $V_{IO}$ to GND                       | -0.3           | 6              | V    |

|                |                      | $V_{CC}$ to GND                       | -0.3           | 6              | V    |

|                |                      | $V_{SS}$ to GND                       | -12            | 0.3            | V    |

|                |                      | $V_{CC}$ to $V_{SS}$                  | -0.3           | 12             | V    |

| Pin voltage    |                      | DAC[0:3] and CLAMP[1:2] to GND        | $V_{SS} - 0.3$ | $V_{CC} + 0.3$ | V    |

|                |                      | OUT[1:2] to GND                       | $V_{SS} - 0.3$ | $V_{CC} + 0.3$ | V    |

|                |                      | PA_ON and SDO to GND                  | -0.3           | $V_{IO} + 0.3$ | V    |

|                |                      | Digital input pins to GND             | -0.3           | 6              | V    |

|                |                      | Remote temperature sensor pins to GND | -0.3           | $V_{DD} + 0.3$ | V    |

| $T_J$          | Junction temperature |                                       | -55            | 150            | °C   |

| $T_{stg}$      | Storage temperature  |                                       | -65            | 150            | °C   |

- (1) Operation outside the *Absolute Maximum Ratings* may cause permanent device damage. *Absolute Maximum Ratings* do not imply functional operation of the device at these or any other conditions beyond those listed under *Recommended Operating Conditions*. If used outside the *Recommended Operating Conditions* but within the *Absolute Maximum Ratings*, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

### 5.2 ESD Ratings

|             |                         |                                                                                 | VALUE     | UNIT |

|-------------|-------------------------|---------------------------------------------------------------------------------|-----------|------|

| $V_{(ESD)}$ | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>     | $\pm 500$ | V    |

|             |                         | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002, all pins <sup>(2)</sup> | $\pm 500$ |      |

(1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

### 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                         |                                         | MIN  | NOM  | MAX  | UNIT |

|-------------------------|-----------------------------------------|------|------|------|------|

| $V_{DD}$                | Analog supply voltage                   | 4.5  | 5.5  | 5.5  | V    |

| $V_{IO}$                | Digital IO supply voltage               | 1.65 | 3.6  | 3.6  | V    |

| $V_{CC}$ <sup>(1)</sup> | Output buffer positive supply voltage   | 4.5  | 5.5  | 5.5  | V    |

| $V_{SS}$ <sup>(2)</sup> | Output buffer negative supply voltage   | -11  | -4.5 | -4.5 | V    |

| $V_{CC} - V_{SS}$       | Output buffer supply voltage range      | 4.5  | 11   | 11   | V    |

|                         | Digital pin input voltage               | 0    | 3.6  | 3.6  | V    |

| $T_A$                   | Operating ambient temperature           | -55  | 125  | 125  | °C   |

| $T_{J,SPEC}$            | Specified junction temperature          | -55  | 125  | 125  | °C   |

| $T_{J,OPER}$            | Operating junction temperature          | -55  | 150  | 150  | °C   |

| $T_{J,EEPROM}$          | EEPROM programming junction temperature | 0    | 125  | 125  | °C   |

(1)  $V_{CC}$  must be connected to GND when the device is configured for negative output voltage range operation.

(2)  $V_{SS}$  must be connected to GND when the device is configured for positive output voltage range operation.

## 5.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | AFE10004-EP | UNIT |

|-------------------------------|----------------------------------------------|-------------|------|

|                               |                                              | RGE (VQFN)  |      |

|                               |                                              | 24 PINS     |      |

| $\Theta_{JA}$                 | Junction-to-ambient thermal resistance       | 33.5        | °C/W |

| $\Theta_{JC(\text{top})}$     | Junction-to-case (top) thermal resistance    | 30.2        | °C/W |

| $\Theta_{JB}$                 | Junction-to-board thermal resistance         | 13.6        | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 0.3         | °C/W |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 13.5        | °C/W |

| $\Theta_{JC(\text{bot})}$     | Junction-to-case (bottom) thermal resistance | 3.7         | °C/W |

(1) For more information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics](#) application report.

## 5.5 Electrical Characteristics

all minimum and maximum specifications at  $T_J = -55^\circ\text{C}$  to  $+125^\circ\text{C}$  and all typical specifications at  $T_J = 25^\circ\text{C}$ ,  $V_{DD} = 4.5\text{V}$  to  $5.5\text{V}$ ,  $V_{IO} = 1.65\text{V}$  to  $3.6\text{V}$ , positive output range:  $V_{CC} = 4.5\text{V}$  to  $5.5\text{V}$ ,  $V_{SS} = \text{GND}$ , negative output range:  $V_{SS} = -11\text{V}$  to  $-4.5\text{V}$ ,  $V_{CC} = \text{GND}$ , and DAC outputs unloaded (unless otherwise noted)

| PARAMETER                                    | TEST CONDITIONS                                                                               | MIN                                                                                       | TYP        | MAX        | UNIT      |

|----------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------|------------|-----------|

| <b>DAC CHARACTERISTICS<sup>(1)</sup></b>     |                                                                                               |                                                                                           |            |            |           |

|                                              | Resolution                                                                                    | 13                                                                                        |            |            | Bits      |

| Full-scale output voltage                    | Set at start-up through auto-range detection                                                  | -10                                                                                       | 0          |            | V         |

|                                              | Set at start-up through auto-range detection                                                  | 0                                                                                         | 10         |            |           |

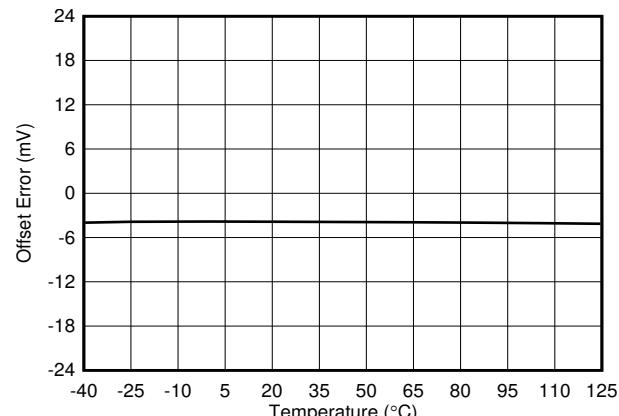

| DNL                                          | Differential nonlinearity                                                                     | Specified 13-bit monotonic                                                                | -1         | 1          | LSB       |

| INL                                          | Integral nonlinearity                                                                         |                                                                                           | -4         | 4          | LSB       |

| TUE                                          | Total unadjusted error                                                                        |                                                                                           | -0.4       | $\pm 0.1$  | 0.4 %FSR  |

|                                              | Total adjusted error                                                                          | After one point calibration at $25^\circ\text{C}$ , DAC output at 1/4 of full-scale range | -0.06      | $\pm 0.01$ | 0.06 %FSR |

| Offset error                                 | Positive output range                                                                         | -24                                                                                       | $\pm 5$    | 24         | mV        |

|                                              | Negative output range                                                                         | -24                                                                                       | $\pm 5$    | 24         |           |

|                                              | Offset error temperature drift                                                                |                                                                                           |            | $\pm 2$    | ppm/°C    |

|                                              | Gain error                                                                                    |                                                                                           | -0.3       | $\pm 0.01$ | 0.3 %FSR  |

|                                              | Gain error temperature drift                                                                  |                                                                                           |            | $\pm 5$    | ppm/°C    |

| Zero-scale error                             | Positive output range: all zeros code                                                         | 0                                                                                         | 5          | 24         | mV        |

|                                              | Negative output range: all ones code                                                          | -24                                                                                       | -5         | 0          |           |

|                                              | Zero-scale error temperature drift                                                            |                                                                                           |            | $\pm 2$    | ppm/°C    |

| Full-scale error                             | Positive output range: all ones code                                                          | -0.25                                                                                     | $\pm 0.03$ | 0.25       | %FSR      |

|                                              | Negative output range: all zeros code                                                         | -0.4                                                                                      | $\pm 0.05$ | 0.4        |           |

|                                              | Full-scale error temperature drift                                                            |                                                                                           |            | $\pm 5$    | ppm/°C    |

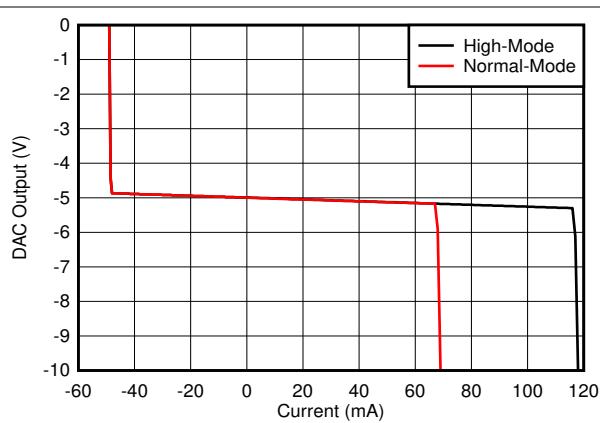

| Load current <sup>(2)</sup>                  | Source with 1V headroom from $V_{CC}$ , high-current mode, number of active channels $\leq 2$ | 100                                                                                       |            |            | mA        |

|                                              | Sink with 1V headroom from $V_{SS}$ , high- and normal-current modes                          | 20                                                                                        |            |            |           |

| Short circuit current, source <sup>(2)</sup> | Start-up current mode                                                                         | 12                                                                                        |            |            | mA        |

|                                              | Normal-current mode                                                                           | 70                                                                                        |            |            |           |

|                                              | High-current mode                                                                             | 120                                                                                       |            |            |           |

## 5.5 Electrical Characteristics (continued)

all minimum and maximum specifications at  $T_J = -55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  and all typical specifications at  $T_J = 25^{\circ}\text{C}$ ,  $V_{DD} = 4.5\text{V}$  to  $5.5\text{V}$ ,  $V_{IO} = 1.65\text{V}$  to  $3.6\text{V}$ , positive output range:  $V_{CC} = 4.5\text{V}$  to  $5.5\text{V}$ ,  $V_{SS} = \text{GND}$ , negative output range:  $V_{SS} = -11\text{V}$  to  $-4.5\text{V}$ ,  $V_{CC} = \text{GND}$ , and DAC outputs unloaded (unless otherwise noted)

| PARAMETER                                  |                                                                                                                | TEST CONDITIONS | MIN  | TYP | MAX | UNIT                         |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------|------|-----|-----|------------------------------|

| Short circuit current, sink <sup>(2)</sup> | Start-up current mode                                                                                          |                 | 12   |     |     | mA                           |

|                                            | Normal-current mode                                                                                            |                 | 40   |     |     |                              |

|                                            | High-current mode                                                                                              |                 | 40   |     |     |                              |

| Capacitive load stability                  |                                                                                                                |                 | 0    | 15  |     | $\mu\text{F}$                |

| DC output impedance                        | DAC[0,3], midscale code                                                                                        |                 | 10   |     |     | $\Omega$                     |

|                                            | DAC[1,2], CLAMP[1,2], midscale code                                                                            |                 | 3    |     |     |                              |

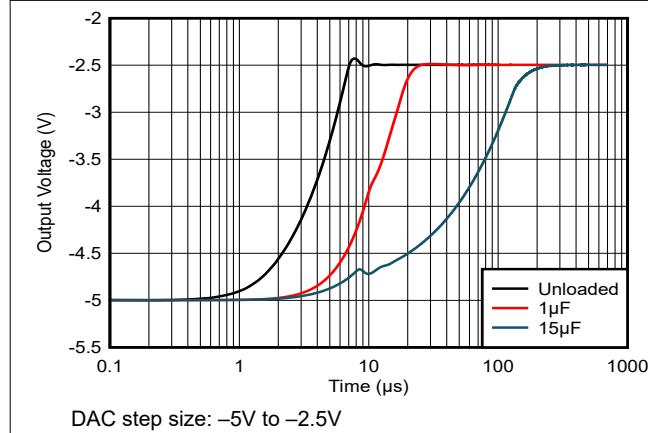

| Output voltage settling time               | $C_L = 15 \mu\text{F}$ , 2.5V step to within 2.5mV                                                             |                 | 400  |     |     | $\mu\text{s}$                |

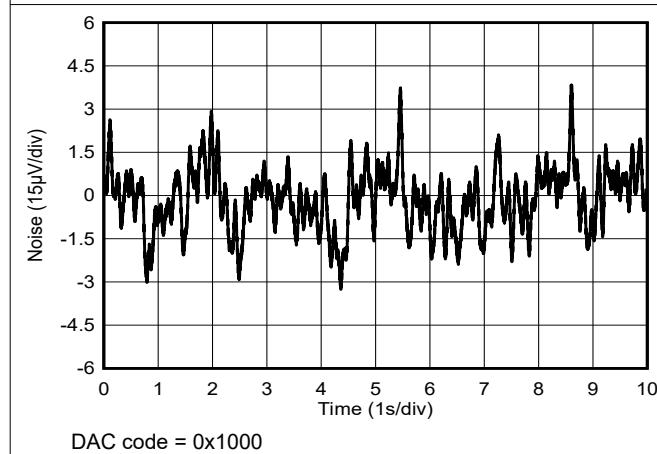

| Output noise                               | 0.1Hz to 10Hz, midscale code                                                                                   |                 | 70   |     |     | $\mu\text{V}_{PP}$           |

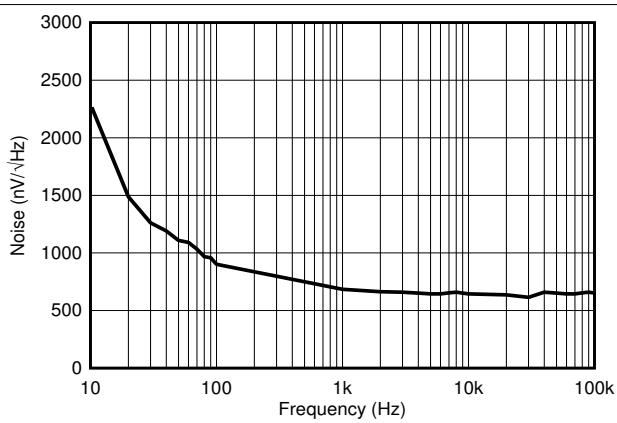

| Output noise density                       | 1kHz, midscale code                                                                                            |                 | 700  |     |     | $\text{nV}/\sqrt{\text{Hz}}$ |

| AC PSRR                                    | Midscale code, frequency = 60Hz, amplitude = 200mV <sub>PP</sub> superimposed on $V_{CC}$ or $V_{SS}$          |                 | 75   |     |     | dB                           |

|                                            | Midscale code, frequency = 60Hz, amplitude = 200mV <sub>PP</sub> superimposed on $V_{DD}$                      |                 | 60   |     |     |                              |

| DC PSRR                                    | Midscale code, $V_{DD} = 5\text{V} \pm 10\%$ , $V_{CC} = 5\text{V} \pm 10\%$ , $V_{SS} = -10\text{V} \pm 10\%$ |                 | 0.15 |     |     | $\text{mV/V}$                |

| Channel-to-channel DC crosstalk            | Measured DAC output at midscale, all other DAC outputs at full-scale, CLAMP outputs at zero-scale              |                 | 150  |     |     | $\mu\text{V}$                |

### AUTO-RANGE THRESHOLD DETECTOR

|             |                               |                                                                                  |      |      |  |   |

|-------------|-------------------------------|----------------------------------------------------------------------------------|------|------|--|---|

| $V_{SSTH}$  | Auto-supply monitor threshold | Narrow $V_{SS}$ supply failure detect (default)                                  | -3.8 | -2.8 |  | V |

| $V_{SSWTH}$ | Auto-supply monitor threshold | Wide $V_{SS}$ supply failure detect, set by register write or loaded from EEPROM | -6.8 | -5.8 |  | V |

| $V_{CCTH}$  | Auto-supply monitor threshold | $V_{CC}$ supply failure detect                                                   | 2.3  | 3.3  |  | V |

### OUTPUT SWITCH DC CHARACTERISTICS

|           |                                                                                   |                                                    |     |    |          |    |

|-----------|-----------------------------------------------------------------------------------|----------------------------------------------------|-----|----|----------|----|

| $R_{1,2}$ | On resistance between DAC[1,2] and OUT[1,2] or CLAMP[1,2] and OUT[1,2]            | Negative output range, 1.5V headroom from $V_{SS}$ | 2   | 3  | $\Omega$ |    |

|           |                                                                                   | Positive output range, 1.5V headroom from $V_{DD}$ | 2   | 3  |          |    |

| $R_{0,3}$ | On resistance between DAC buffers and DAC[0,3] or between DAC[0,3] and CLAMP[1,2] | Negative output range, 1.5V headroom from $V_{SS}$ | 9   | 14 | $\Omega$ |    |

|           |                                                                                   | Positive output range, 1.5V headroom from $V_{CC}$ | 10  | 16 |          |    |

| $C_{OUT}$ | OUT[1,2] output impedance                                                         |                                                    | 100 |    |          | pF |

## 5.5 Electrical Characteristics (continued)

all minimum and maximum specifications at  $T_J = -55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  and all typical specifications at  $T_J = 25^{\circ}\text{C}$ ,  $V_{DD} = 4.5\text{V}$  to  $5.5\text{V}$ ,  $V_{IO} = 1.65\text{V}$  to  $3.6\text{V}$ , positive output range:  $V_{CC} = 4.5\text{V}$  to  $5.5\text{V}$ ,  $V_{SS} = \text{GND}$ , negative output range:  $V_{SS} = -11\text{V}$  to  $-4.5\text{V}$ ,  $V_{CC} = \text{GND}$ , and DAC outputs unloaded (unless otherwise noted)

| PARAMETER                                                                  | TEST CONDITIONS                                             | MIN                                             | TYP            | MAX | UNIT               |

|----------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------|----------------|-----|--------------------|

| <b>LOCAL TEMPERATURE SENSOR CHARACTERISTICS</b>                            |                                                             |                                                 |                |     |                    |

| Operating junction temperature                                             |                                                             | -55                                             | 150            |     | $^{\circ}\text{C}$ |

| Accuracy                                                                   | $T_J = -55^{\circ}\text{C}$ to $+125^{\circ}\text{C}$       |                                                 | 1.25           | 2.5 | $^{\circ}\text{C}$ |

| Resolution                                                                 | LSB size                                                    |                                                 | 0.0625         |     | $^{\circ}\text{C}$ |

| Update time                                                                | 32 conversions per second                                   |                                                 | 31.25          |     | ms                 |

| <b>REMOTE TEMPERATURE SENSOR CHARACTERISTICS (Using 2N3906 Transistor)</b> |                                                             |                                                 |                |     |                    |

| Operating junction temperature                                             |                                                             | -55                                             | 150            |     | $^{\circ}\text{C}$ |

| Accuracy                                                                   | $T_{DIODE} = -55^{\circ}\text{C}$ to $+150^{\circ}\text{C}$ |                                                 | 1.25           | 2.5 | $^{\circ}\text{C}$ |

| Resolution                                                                 | LSB size                                                    |                                                 | 0.0625         |     | $^{\circ}\text{C}$ |

| Update time                                                                | 32 conversions per second                                   |                                                 | 31.25          |     | ms                 |

| <b>DIGITAL INPUTS</b>                                                      |                                                             |                                                 |                |     |                    |

| $V_{IH}$                                                                   | High-level input voltage                                    |                                                 | 1.3            |     | V                  |

| $V_{IL}$                                                                   | Low-level input voltage                                     |                                                 | 0.45           |     | V                  |

|                                                                            | Hysteresis voltage                                          |                                                 | 90             |     | mV                 |

|                                                                            | Input current                                               |                                                 | 1              |     | $\mu\text{A}$      |

|                                                                            | Input pin capacitance                                       |                                                 | 5              |     | pF                 |

| <b>DIGITAL OUTPUTS</b>                                                     |                                                             |                                                 |                |     |                    |

| $V_{OH}$                                                                   | High-level output voltage                                   | Load current = 1mA                              | $V_{IO} - 0.2$ |     | V                  |

| $V_{OL}$                                                                   | Low-level output voltage                                    | Load current = -1mA                             | 0.4            |     | V                  |

|                                                                            | Output pin capacitance                                      |                                                 | 5              |     | pF                 |

| <b>POWER REQUIREMENTS</b>                                                  |                                                             |                                                 |                |     |                    |

| $I_{VDD}$                                                                  | $V_{DD}$ supply current                                     | Positive output range                           |                | 5   | mA                 |

|                                                                            |                                                             | Negative output range                           |                | 5   |                    |

| $I_{VCC}$                                                                  | $V_{CC}$ supply current                                     | Positive output range, midscale output          |                | 3   | mA                 |

| $I_{VSS}$                                                                  | $V_{SS}$ supply current                                     | Negative output range, 1/4 of full-scale output |                | 3   | mA                 |

| $I_{VIO}$                                                                  | $V_{IO}$ supply current                                     |                                                 |                | 10  | $\mu\text{A}$      |

- (1) End point fit between codes 64 to 8128 for negative output range and 64 to 4032 for positive output range.

- (2) Overload condition protection. Junction temperature potentially exceeds during current limit. Operation greater than the specified maximum junction temperature potentially impairs device reliability.

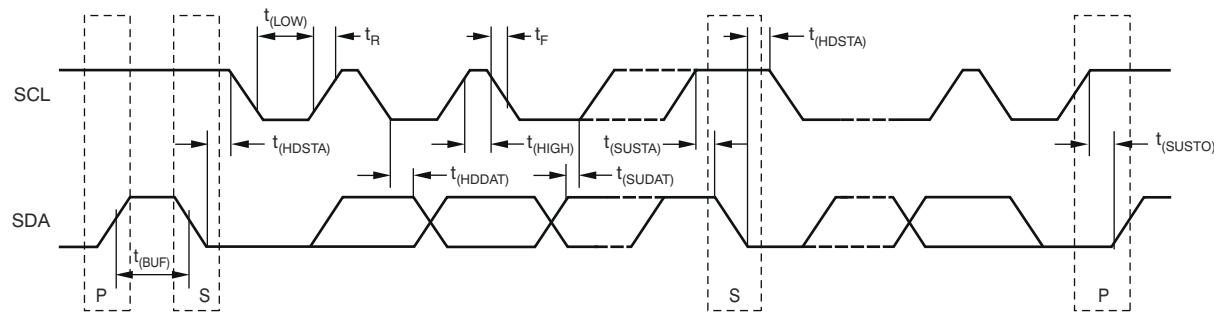

## 5.6 Timing Requirements

all minimum and maximum specifications at  $T_J = -55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  and all typical specifications at  $T_J = 25^{\circ}\text{C}$ ,  $V_{DD} = 4.5\text{V}$  to  $5.5\text{V}$ ,  $V_{IO} = 1.65\text{V}$  to  $3.6\text{V}$ , positive output range:  $V_{CC} = 4.5\text{V}$  to  $5.5\text{V}$ ,  $V_{SS} = \text{GND}$ , negative output range:  $V_{SS} = -11\text{V}$  to  $-4.5\text{V}$ ,  $V_{CC} = \text{GND}$ , and DAC outputs unloaded (unless otherwise noted)

|                                           |                                                                                              | MIN | NOM  | MAX  | UNIT |

|-------------------------------------------|----------------------------------------------------------------------------------------------|-----|------|------|------|

| <b>I<sup>2</sup>C TIMING REQUIREMENTS</b> |                                                                                              |     |      |      |      |

| $f_{(\text{SCL})}$                        | I <sup>2</sup> C clock frequency                                                             | 10  | 400  | 400  | kHz  |

| $t_{(\text{LOW})}$                        | SCL clock low period                                                                         | 1.3 |      |      | μs   |

| $t_{(\text{HIGH})}$                       | SCL clock high period                                                                        | 0.6 |      |      | μs   |

| $t_{(\text{HDSTA})}$                      | Hold time after repeated start condition.<br>After this period, the first clock is generated | 0.6 |      |      | μs   |

| $t_{(\text{SUSTA})}$                      | Repeated start condition setup time                                                          | 0.6 |      |      | μs   |

| $t_{(\text{SUSTO})}$                      | Stop condition setup time                                                                    | 0.6 |      |      | μs   |

| $t_{(\text{BUF})}$                        | Bus free time between stop and start condition                                               | 1.3 |      |      | μs   |

| $t_{(\text{SUDAT})}$                      | Data setup time                                                                              | 100 |      |      | ns   |

| $t_{(\text{HDDAT})}$                      | Data hold time                                                                               | 0   | 900  | 900  | ns   |

| $t_{F, \text{SDA}}$                       | Data fall time                                                                               | 20  | 300  | 300  | ns   |

| $t_{F, \text{SCL}}$                       | Clock fall time                                                                              |     | 300  | 300  | ns   |

| $t_{R, \text{SCL}}$                       | Clock rise time                                                                              |     | 300  | 300  | ns   |

| $t_{R, \text{SCL100}}$                    | Rise time for SCL $\leq 100\text{kHz}$                                                       |     | 1000 | 1000 | ns   |

|                                           | SCL and SDA timeout                                                                          | 20  | 30   | 30   | ms   |

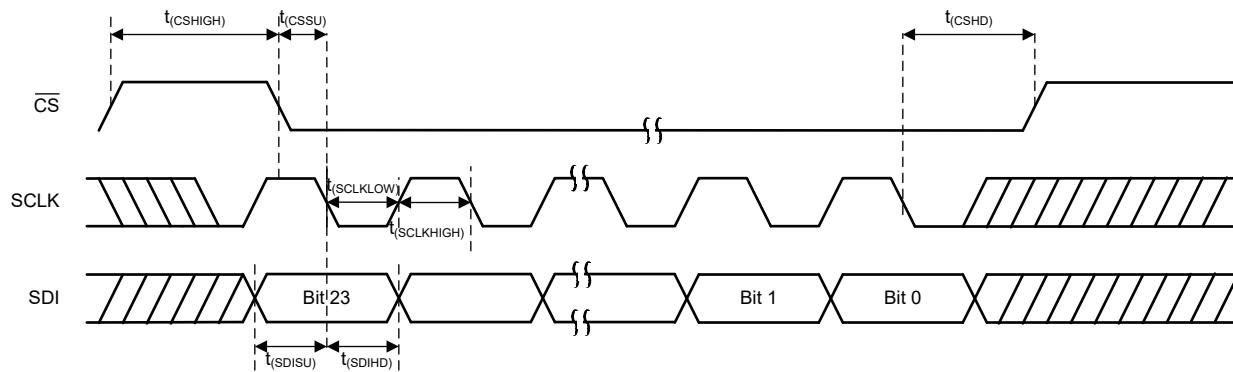

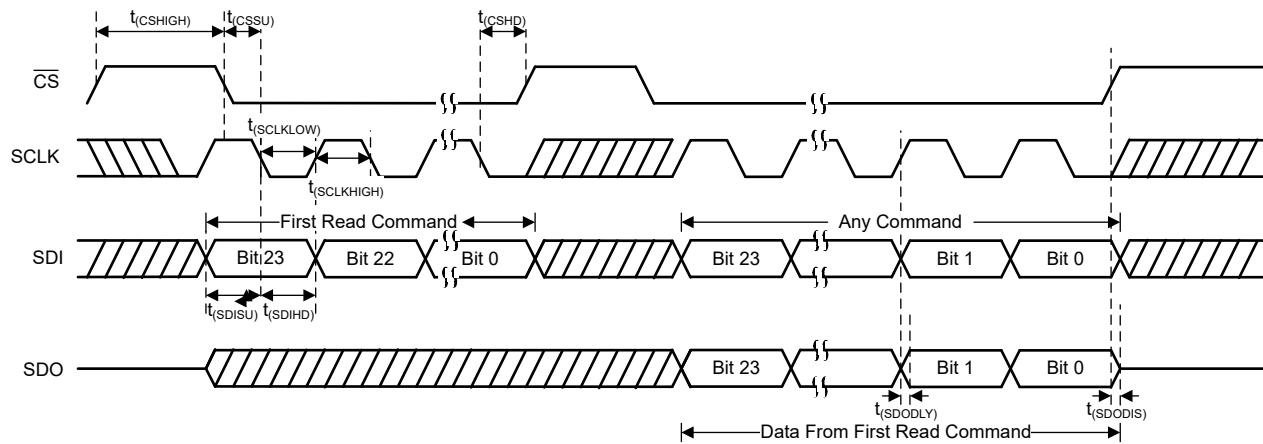

### SPI TIMING REQUIREMENTS, $V_{IO} = 2.7\text{V}$ to $3.6\text{V}$

|                         |                                    |    |     |

|-------------------------|------------------------------------|----|-----|

| $f_{(\text{SCLK})}$     | SPI clock frequency                | 20 | MHz |

| $t_{(\text{SCLKLOW})}$  | Clock high time                    | 20 | ns  |

| $t_{(\text{SCLKHIGH})}$ | Clock low time                     | 20 | ns  |

| $t_{(\text{SDISU})}$    | Data setup time                    | 10 | ns  |

| $t_{(\text{SDIHD})}$    | Data hold time                     | 10 | ns  |

| $t_{(\text{SDODLY})}$   | SDO delay                          | 0  | 20  |

| $t_{(\text{SDODIS})}$   | SDO disable                        | 0  | 20  |

| $t_{(\text{CSSU})}$     | $\overline{\text{CS}}$ setup       | 10 | ns  |

| $t_{(\text{CSHD})}$     | $\overline{\text{CS}}$ hold        | 20 | ns  |

| $t_{(\text{CSHIGH})}$   | $\overline{\text{CS}}$ pulse-width | 25 | ns  |

### SPI TIMING REQUIREMENTS, $V_{IO} = 1.65\text{V}$ to $2.7\text{V}$

|                         |                                    |    |     |

|-------------------------|------------------------------------|----|-----|

| $f_{(\text{SCLK})}$     | SPI clock frequency                | 10 | MHz |

| $t_{(\text{SCLKLOW})}$  | Clock high time                    | 40 | ns  |

| $t_{(\text{SCLKHIGH})}$ | Clock low time                     | 40 | ns  |

| $t_{(\text{SDISU})}$    | Data setup time                    | 10 | ns  |

| $t_{(\text{SDIHD})}$    | Data hold time                     | 10 | ns  |

| $t_{(\text{SDODLY})}$   | SDO delay                          | 0  | 30  |

| $t_{(\text{SDODIS})}$   | SDO disable                        | 0  | 30  |

| $t_{(\text{CSSU})}$     | $\overline{\text{CS}}$ setup       | 10 | ns  |

| $t_{(\text{CSHD})}$     | $\overline{\text{CS}}$ hold        | 20 | ns  |

| $t_{(\text{CSHIGH})}$   | $\overline{\text{CS}}$ pulse-width | 25 | ns  |

## 5.7 Switching Characteristics

all minimum and maximum specifications at  $T_J = -55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  and all typical specifications at  $T_J = 25^{\circ}\text{C}$ ,  $V_{DD} = 4.5\text{V}$  to  $5.5\text{V}$ ,  $V_{IO} = 1.65\text{V}$  to  $3.6\text{V}$ , positive output range:  $V_{CC} = 4.5\text{V}$  to  $5.5\text{V}$ ,  $V_{SS} = \text{GND}$ , negative output range:  $V_{SS} = -11\text{V}$  to  $-4.5\text{V}$ ,  $V_{CC} = \text{GND}$ , and DAC outputs unloaded (unless otherwise noted)

| PARAMETER                               |                     | TEST CONDITIONS                                                                              | MIN | TYP | MAX | UNIT |

|-----------------------------------------|---------------------|----------------------------------------------------------------------------------------------|-----|-----|-----|------|

| <b>OUTPUT SWITCH AC CHARACTERISTICS</b> |                     |                                                                                              |     |     |     |      |

| $t_{ON}$                                | On time             | Midscale code, $R_L = 100\text{k}\Omega$                                                     | 40  |     |     | ns   |

| $t_{OFF}$                               | Off time            | Midscale code, $R_L = 100\text{k}\Omega$                                                     | 50  |     |     | ns   |

| <b>PA_ON CHARACTERISTICS</b>            |                     |                                                                                              |     |     |     |      |

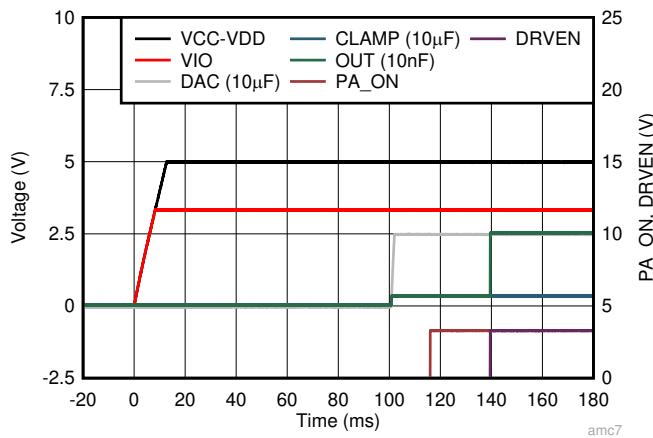

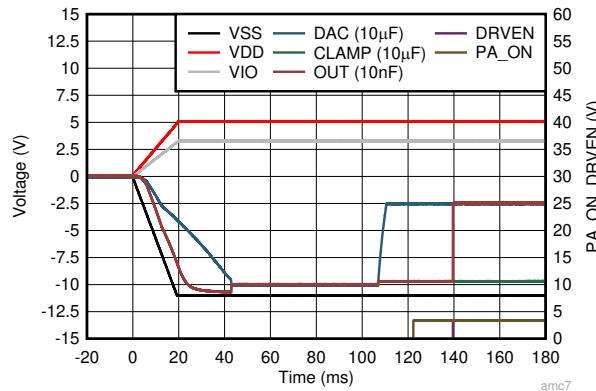

| $t_{PA\_ON}$                            | PA_ON turn-on time  | Measured from reset event, unloaded, default register configuration                          | 120 |     |     | ms   |

| $t_{PA\_OFF}$                           | PA_ON turn-off time | Measured from an $\overline{\text{ALMIN}}$ alarm event, unloaded                             | 50  |     |     | ns   |

| <b>OUTPUT CHARACTERISTICS</b>           |                     |                                                                                              |     |     |     |      |

| $t_{OUT\_CLM}$                          | OUT[1:2] clamp time | Time for output to go to CLAMP DAC voltage, measured from reset event, $C_L = 15\mu\text{F}$ | 100 |     |     | ms   |

| $t_{OUT\_LUT}$                          | OUT[1:2] ready time | Time for LUT-based output to be ready, measured from reset event, $C_L = 15\mu\text{F}$      | 120 |     |     | ms   |

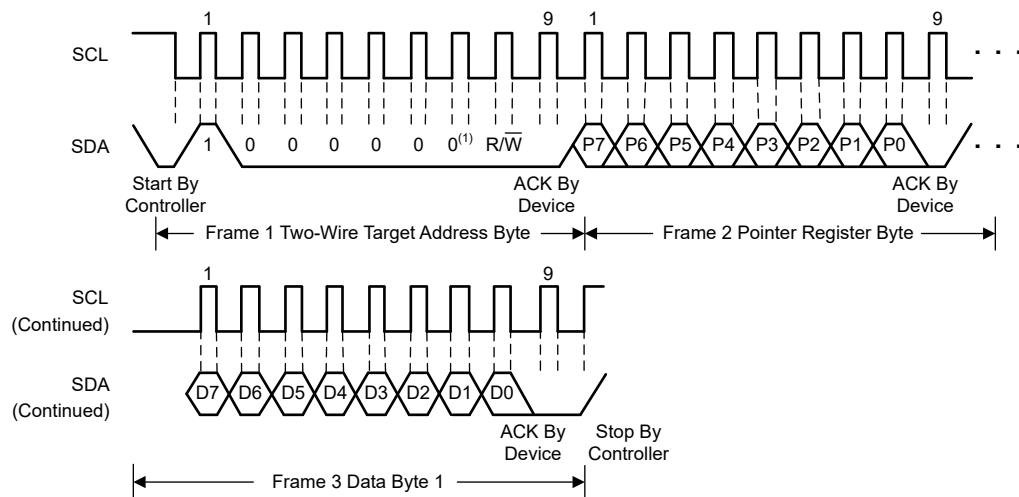

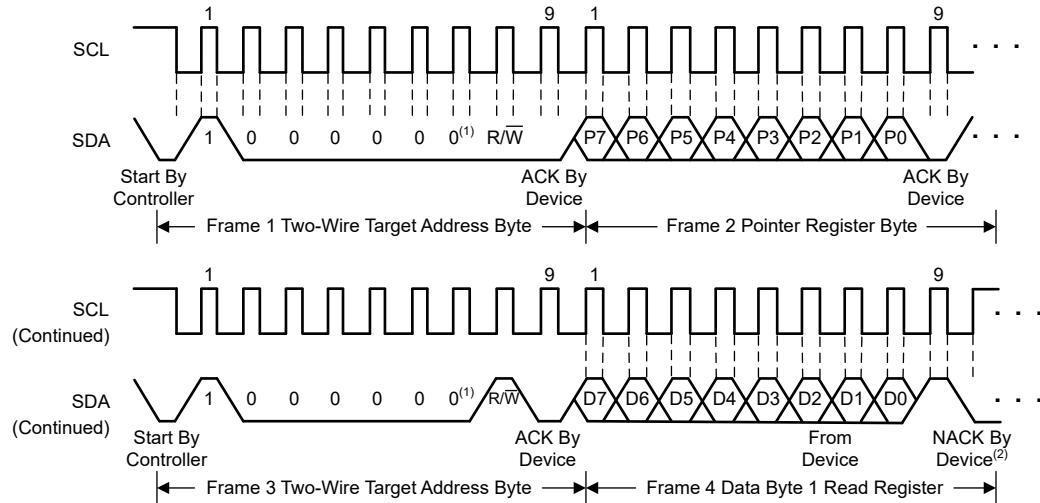

## 5.8 Timing Diagrams

Figure 5-1. I<sup>2</sup>C Timing Diagram

Figure 5-2. SPI Write Timing Diagram

Figure 5-3. SPI Read Timing Diagram

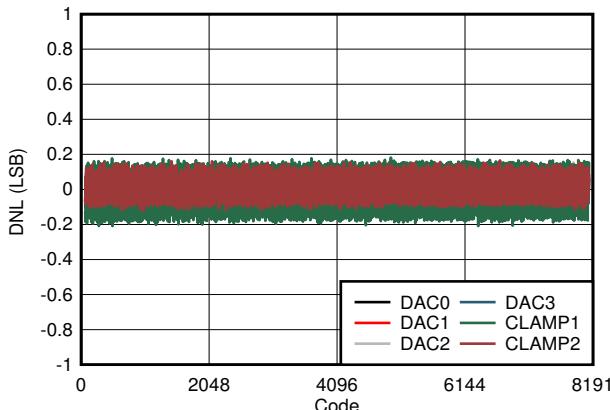

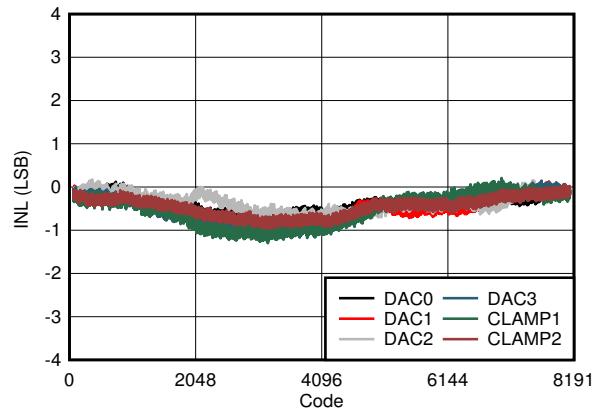

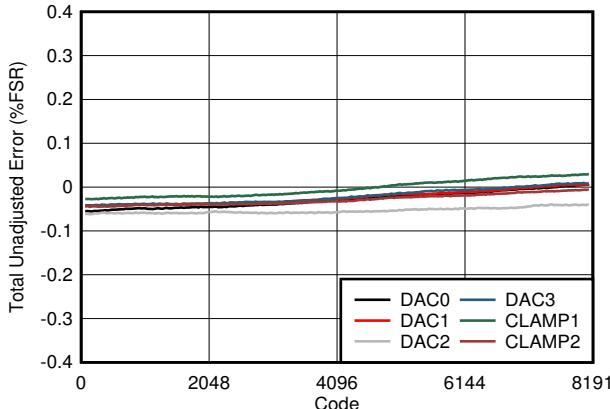

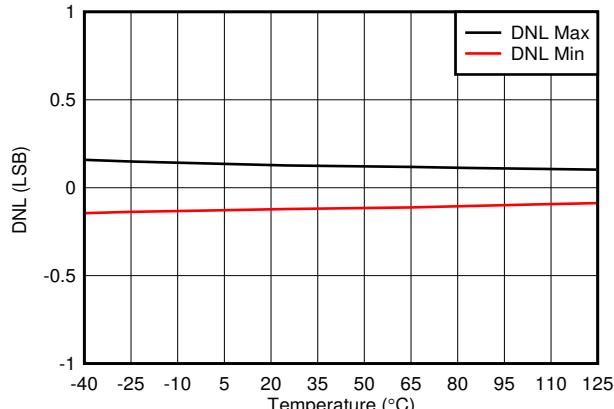

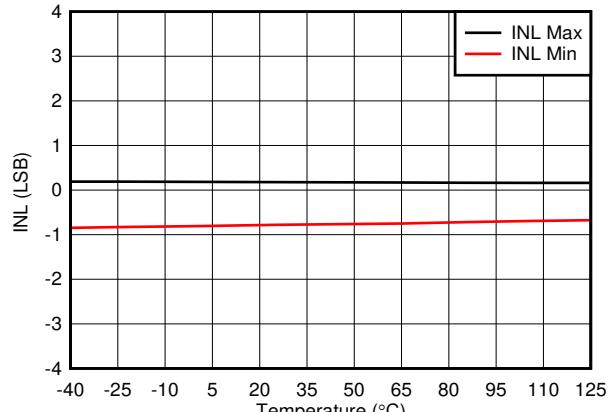

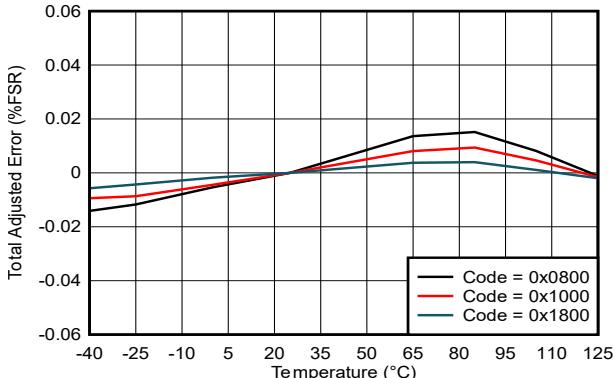

## 5.9 Typical Characteristics

at  $T_A = 25^\circ\text{C}$ ,  $V_{DD} = 5\text{V}$ ,  $V_{IO} = 3.3\text{V}$ , negative output range:  $V_{CC} = \text{GND}$ ,  $V_{SS} = -11\text{V}$ , and DAC outputs unloaded (unless otherwise noted)

Figure 5-4. DAC DNL vs Digital Input Code

Figure 5-5. DAC INL vs Digital Input Code

Figure 5-6. DAC TUE vs Digital Input Code

Figure 5-7. DAC DNL vs Temperature

Figure 5-8. DAC INL vs Temperature

Error after one point calibration at  $25^\circ\text{C}$

Figure 5-9. DAC Total Adjusted Error vs Temperature

## 5.9 Typical Characteristics (continued)

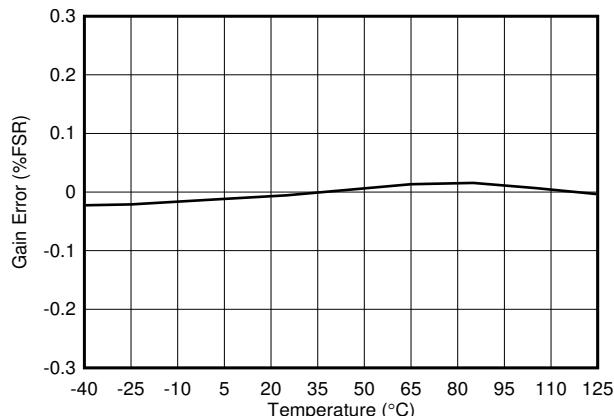

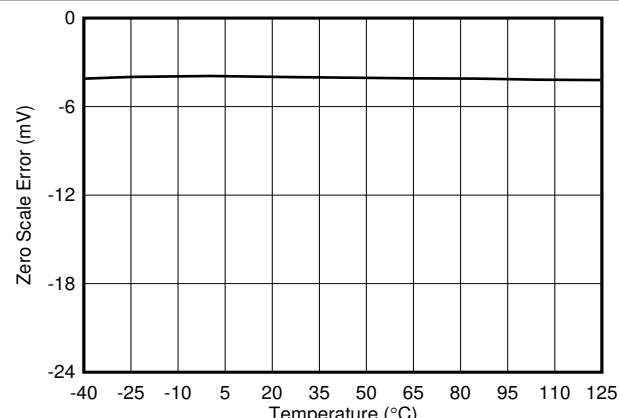

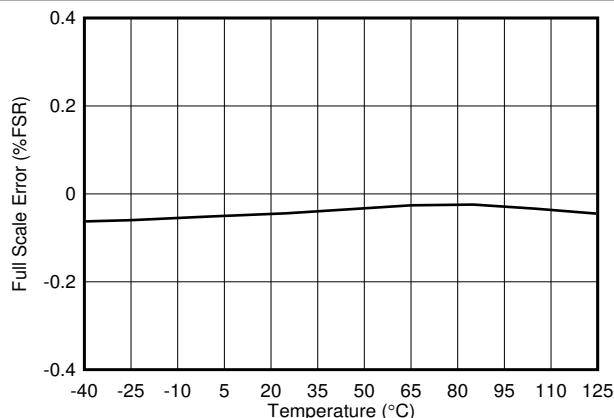

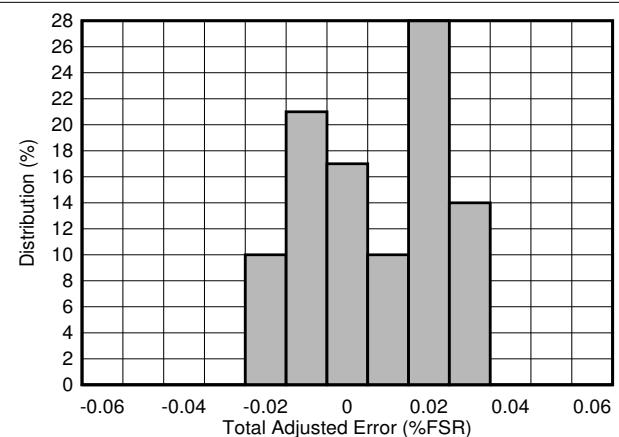

at  $T_A = 25^\circ\text{C}$ ,  $V_{DD} = 5\text{V}$ ,  $V_{IO} = 3.3\text{V}$ , negative output range:  $V_{CC} = \text{GND}$ ,  $V_{SS} = -11\text{V}$ , and DAC outputs unloaded (unless otherwise noted)

Figure 5-10. DAC Offset Error vs Temperature

Figure 5-11. DAC Gain Error vs Temperature

DAC code = 0x1FFF

Figure 5-12. DAC Zero-Scale Error vs Temperature

DAC code = 0x0000

Figure 5-13. DAC Full-Scale Error vs Temperature

DAC code = 0x1800

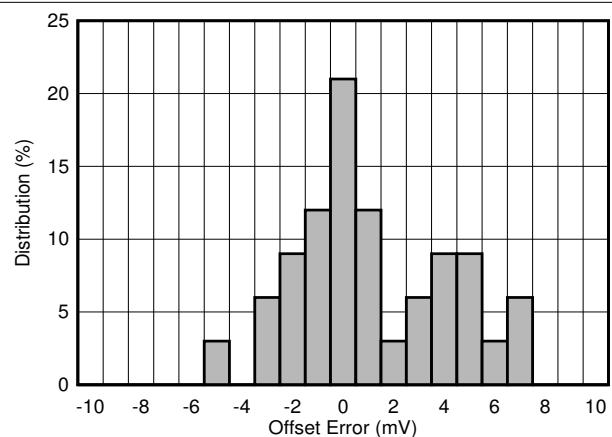

$T_A = -40^\circ\text{C}$  to  $+125^\circ\text{C}$

Figure 5-14. DAC Total Adjusted Error

$T_A = -40^\circ\text{C}$  to  $+125^\circ\text{C}$

Figure 5-15. DAC Offset Error

## 5.9 Typical Characteristics (continued)

at  $T_A = 25^\circ\text{C}$ ,  $V_{DD} = 5\text{V}$ ,  $V_{IO} = 3.3\text{V}$ , negative output range:  $V_{CC} = \text{GND}$ ,  $V_{SS} = -11\text{V}$ , and DAC outputs unloaded (unless otherwise noted)

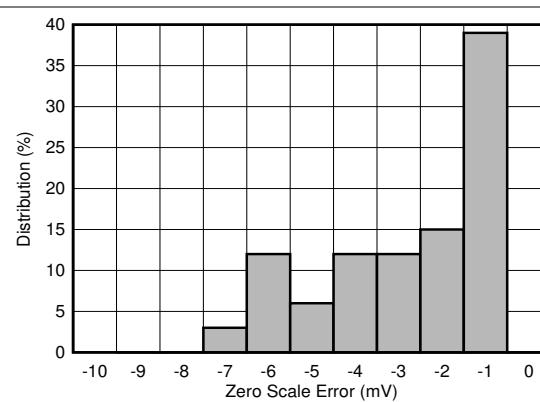

$T_A = -40^\circ\text{C}$  to  $+125^\circ\text{C}$

Figure 5-16. DAC Gain Error

DAC code = 0x1FFF

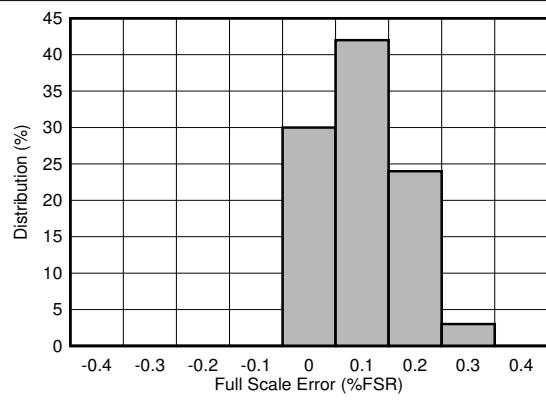

$T_A = -40^\circ\text{C}$  to  $+125^\circ\text{C}$

Figure 5-17. DAC Zero-Scale Error

DAC code = 0x0000

$T_A = -40^\circ\text{C}$  to  $+125^\circ\text{C}$

Figure 5-18. DAC Full-Scale Error

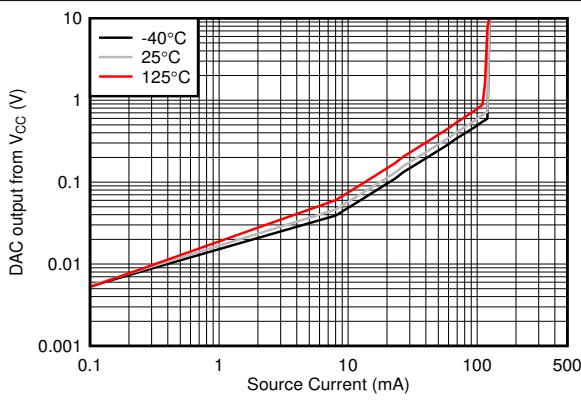

DAC code = 0x1FFF

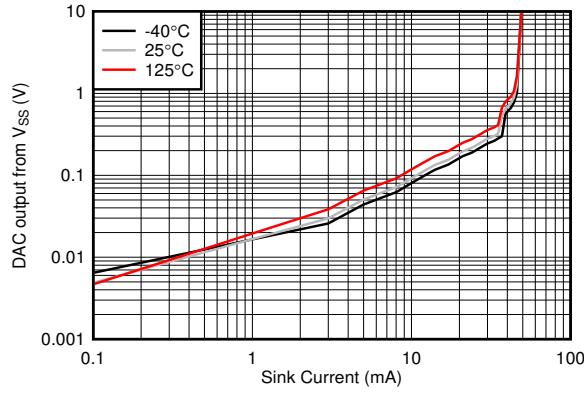

Figure 5-19. DAC[1:2], CLAMP[1:2] Headroom vs High-Mode Sourcing Current

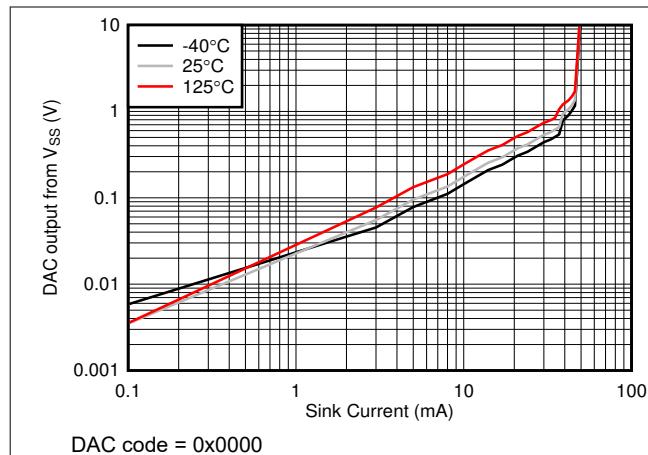

DAC code = 0x0000

Figure 5-20. DAC[1:2], CLAMP[1:2] Headroom vs High-Mode Sinking Current

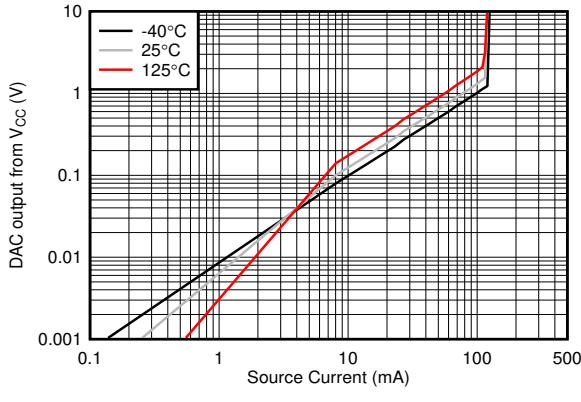

DAC code = 0x1FFF

Figure 5-21. DAC[0:3] Headroom vs High-Mode Sourcing Current

## 5.9 Typical Characteristics (continued)

at  $T_A = 25^\circ\text{C}$ ,  $V_{DD} = 5\text{V}$ ,  $V_{IO} = 3.3\text{V}$ , negative output range:  $V_{CC} = \text{GND}$ ,  $V_{SS} = -11\text{V}$ , and DAC outputs unloaded (unless otherwise noted)

Figure 5-22. DAC[0:3] Headroom vs High-Mode Sinking Current

Figure 5-23. Source and Sink Current Capability

Figure 5-24. DAC Settling Time vs Capacitive Load

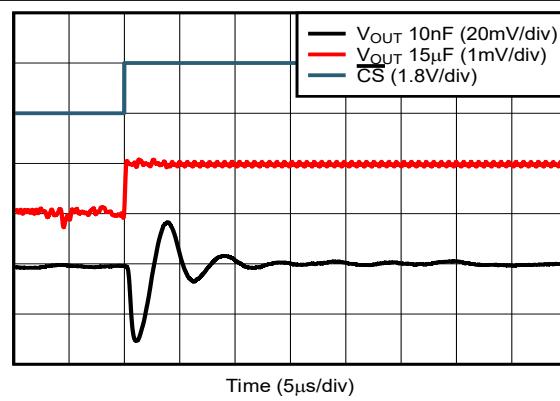

Figure 5-25. DAC Glitch Impulse

Figure 5-26. DAC Output Noise, 0.1Hz to 10Hz

Figure 5-27. DAC Output Noise Density vs Frequency

## 5.9 Typical Characteristics (continued)

at  $T_A = 25^\circ\text{C}$ ,  $V_{DD} = 5\text{V}$ ,  $V_{IO} = 3.3\text{V}$ , negative output range:  $V_{CC} = \text{GND}$ ,  $V_{SS} = -11\text{V}$ , and DAC outputs unloaded (unless otherwise noted)

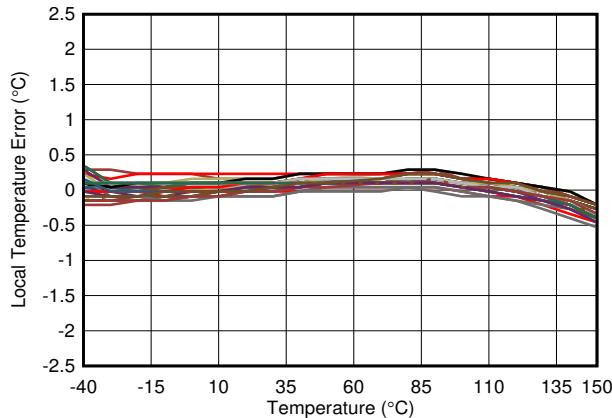

Figure 5-28. Local Temperature Sensor Error vs Temperature

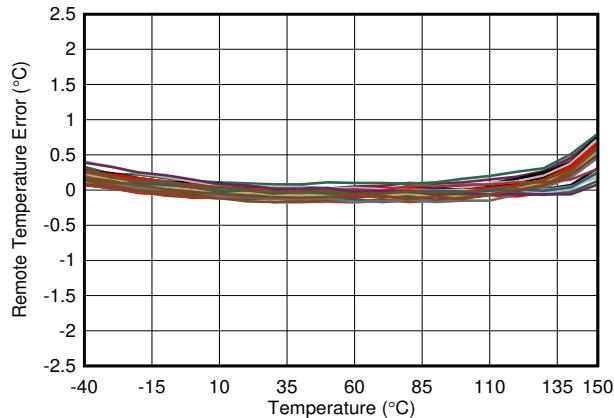

Figure 5-29. Remote Temperature Sensor Error vs Temperature

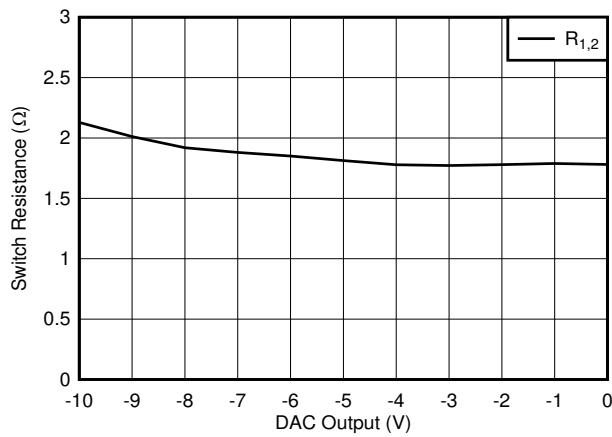

Figure 5-30.  $R_{1,2}$  Switch Resistance vs DAC Output

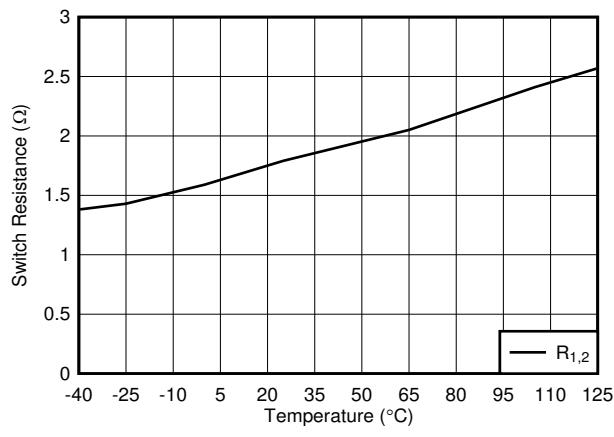

Figure 5-31.  $R_{1,2}$  Switch Resistance vs Temperature

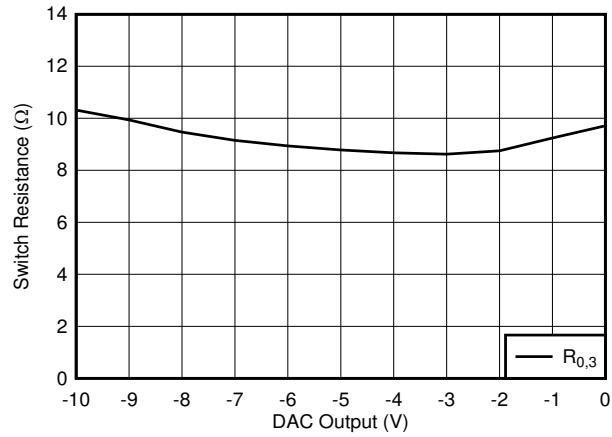

Figure 5-32.  $R_{0,3}$  Switch Resistance vs DAC Output

Figure 5-33.  $R_{0,3}$  Switch Resistance vs Temperature

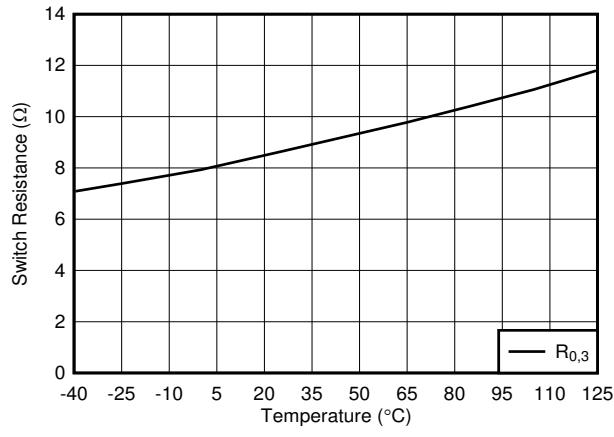

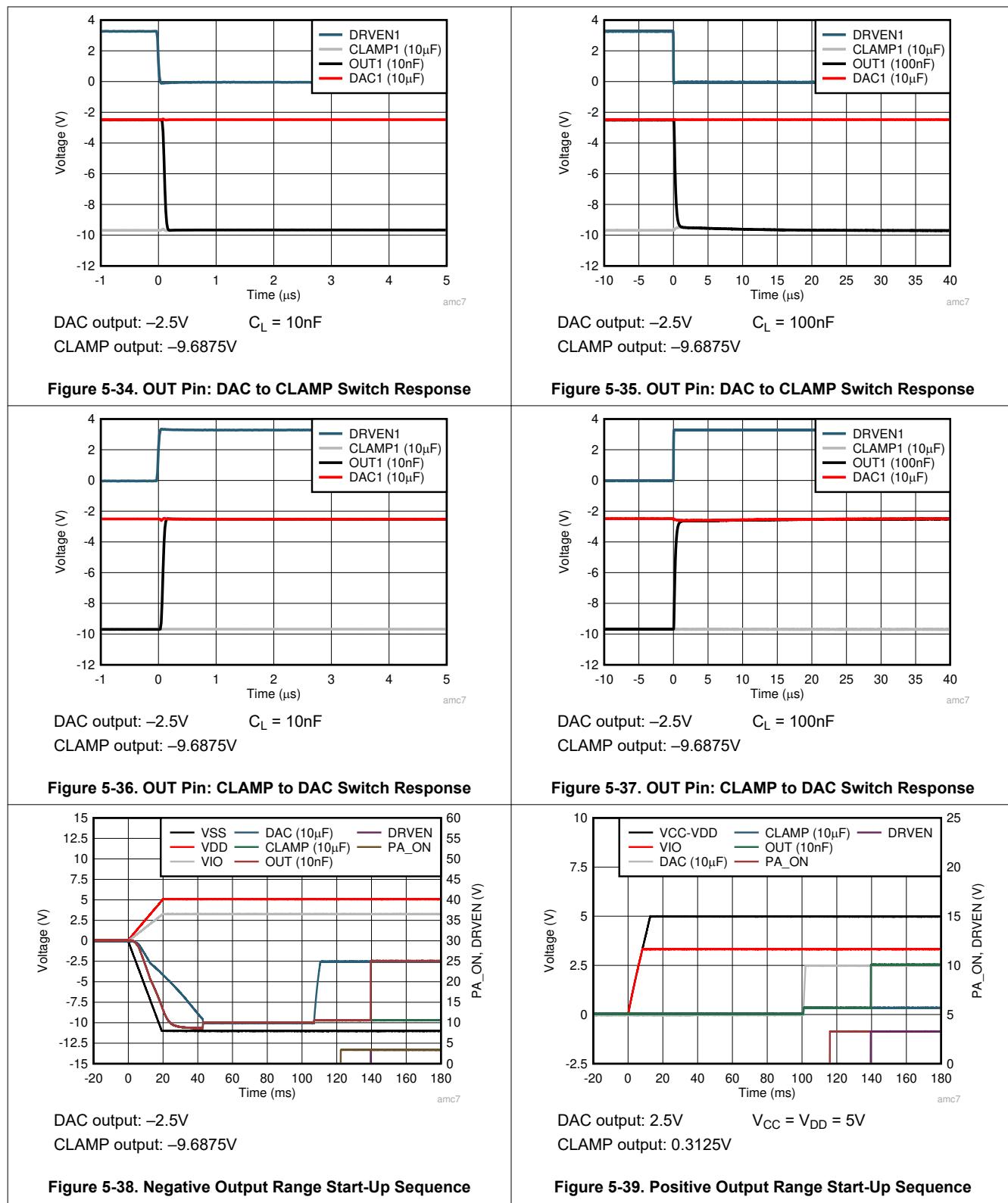

## 5.9 Typical Characteristics (continued)

at  $T_A = 25^\circ\text{C}$ ,  $V_{DD} = 5\text{V}$ ,  $V_{IO} = 3.3\text{V}$ , negative output range:  $V_{CC} = \text{GND}$ ,  $V_{SS} = -11\text{V}$ , and DAC outputs unloaded (unless otherwise noted)

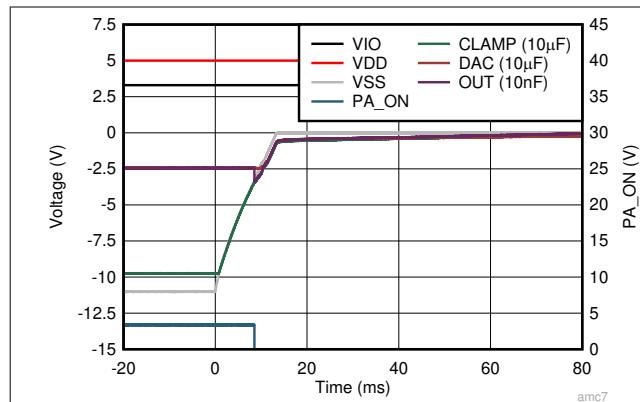

## 5.9 Typical Characteristics (continued)

at  $T_A = 25^\circ\text{C}$ ,  $V_{DD} = 5\text{V}$ ,  $V_{IO} = 3.3\text{V}$ , negative output range:  $V_{CC} = \text{GND}$ ,  $V_{SS} = -11\text{V}$ , and DAC outputs unloaded (unless otherwise noted)

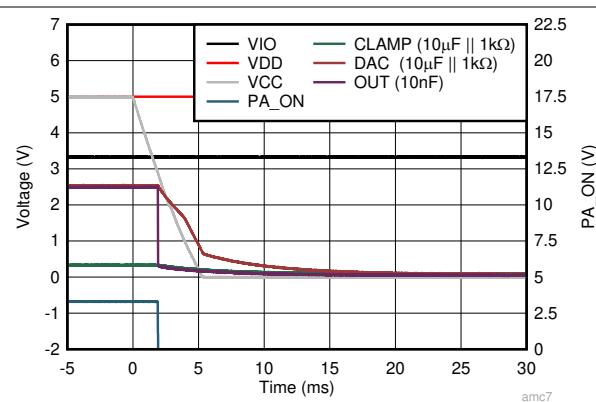

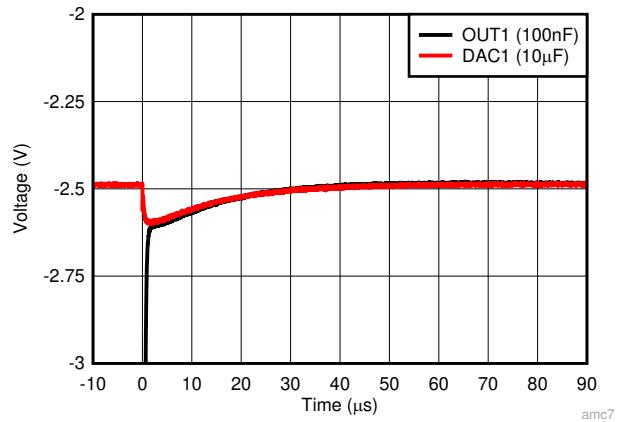

DAC output: -2.5V

CLAMP output: -9.6875V

Figure 5-40.  $V_{SS}$  Supply Collapse Response

DAC output: 2.5V

$V_{CC} = V_{DD} = 5\text{V}$

CLAMP output: 0.3125V

Figure 5-41.  $V_{CC}$  Supply Collapse Response

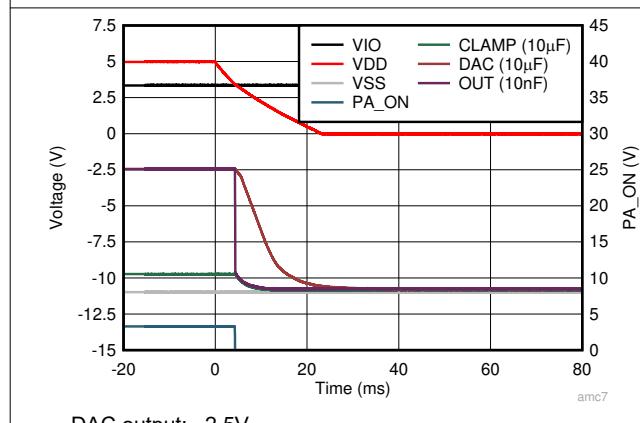

DAC output: -2.5V

CLAMP output: -9.6875V

Figure 5-42.  $V_{DD}$  Supply Collapse Response

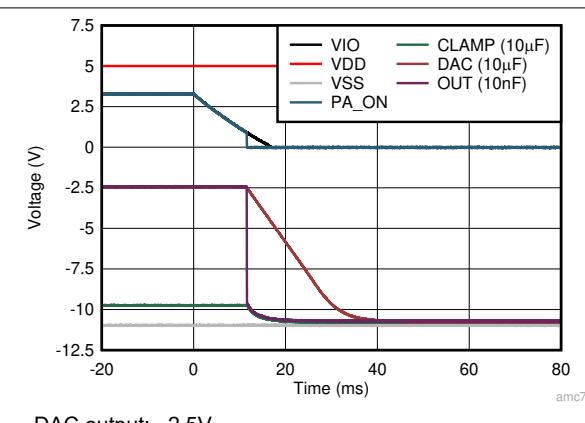

DAC output: -2.5V

CLAMP output: -9.6875V

Figure 5-43.  $V_{IO}$  Supply Collapse Response

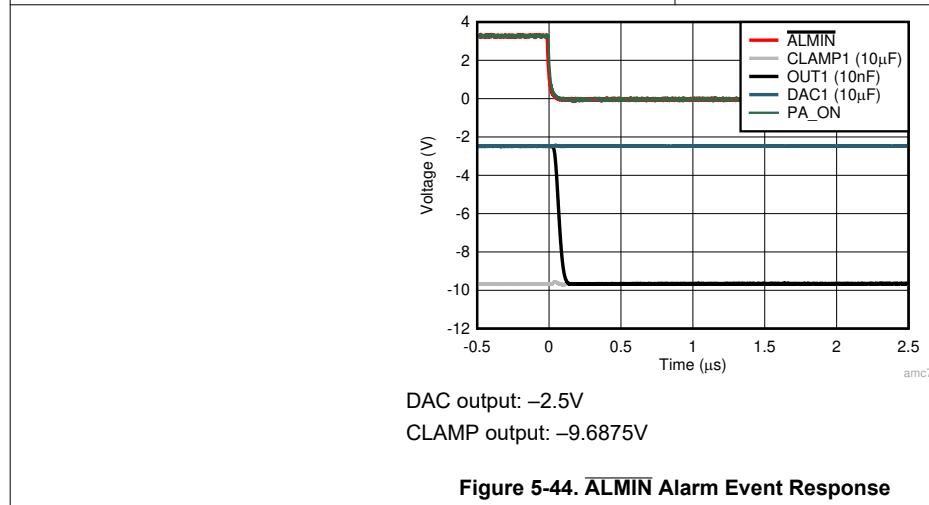

Figure 5-44.  $ALMIN$  Alarm Event Response

## 6 Detailed Description

### 6.1 Overview

The AFE10004-EP is a four-channel power amplifier (PA) precision analog front end (AFE) with dedicated gate bias switch control and built-in sequencing features. The temperature-to-voltage transfer functions are user defined and stored in the internal EEPROM. The device contains both local and remote temperature sensor monitors that address four independently programmed look-up-tables (LUTs). The outputs of the LUTs are sent to the respective DACs to produce four independent output voltages. The device operates in either a positive or negative output voltage range.

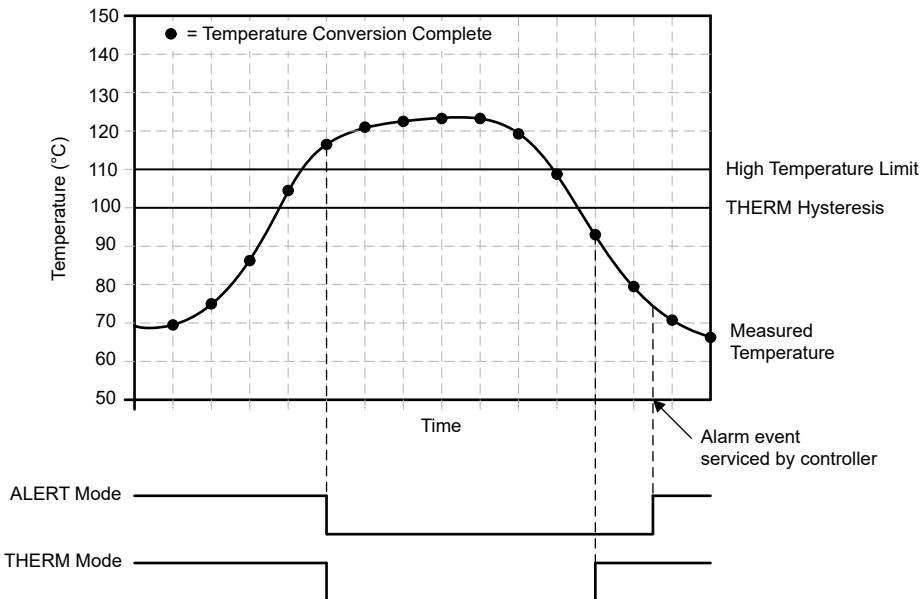

The four gate bias outputs are switched on and off through digital control pins or software. The device enables programmable off voltages through two dedicated DACs. The gate bias switching is designed for fast response, and in combination with the device PA\_ON pin enables a robust PA control system.

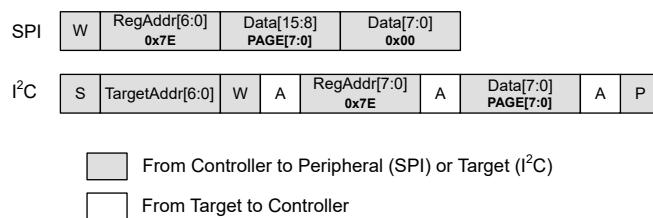

The device registers are configured through an SPI- and I<sup>2</sup>C-compatible interface. The serial interface is also used to commit the device configuration and LUTs to the nonvolatile EEPROM. With the EEPROM properly configured, the device is able to operate autonomously.

### 6.2 Functional Block Diagram

## 6.3 Feature Description

### 6.3.1 Digital-to-Analog Converter (DAC) Overview

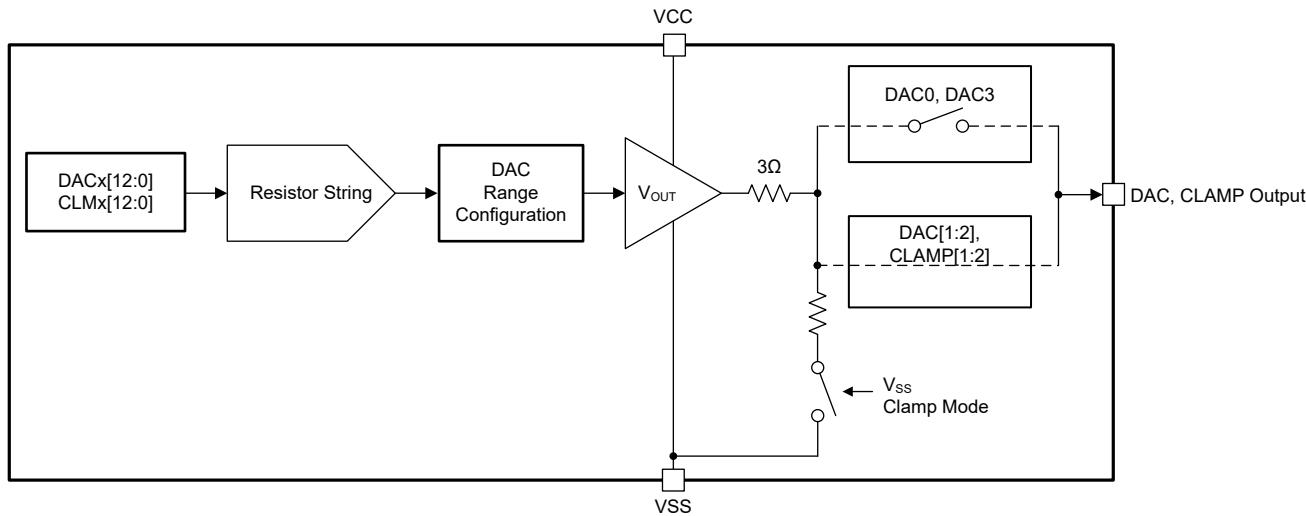

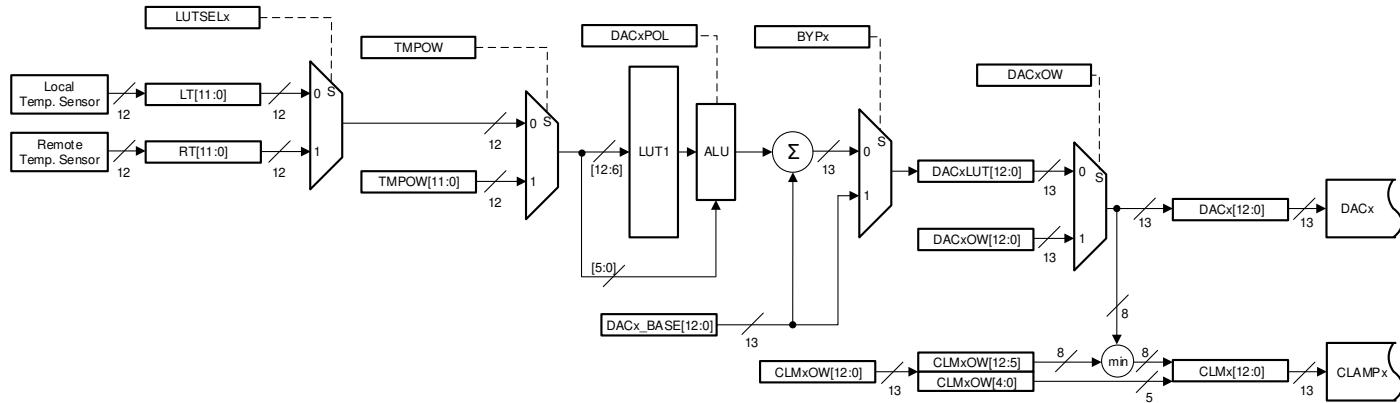

The device features four analog control channels. Each control channel is centered on a DAC that operates from the device internal reference. Two additional dedicated DACs are used for setting the internal switches off voltages. The six DACs in the device consist of a 13-bit string DAC and an output voltage buffer. [Figure 6-1](#) shows a block diagram of the DAC architecture.

**Figure 6-1. DAC Block Diagram**

The DACs can be configured for positive- or negative-output-range operation with identical voltage resolution. All of the DACs in the device share the same output range. In positive-output-range operation, the full-scale range is 0V to 10V; however, the output voltage is limited by  $V_{CC}$  to a value no greater than 5.5V. In negative-output-range operation, the full-scale range is -10V to 0V. Data are written to the DAC data registers directly through the serial interface or automatically set by the look-up table (LUT) and arithmetic logic unit (ALU).

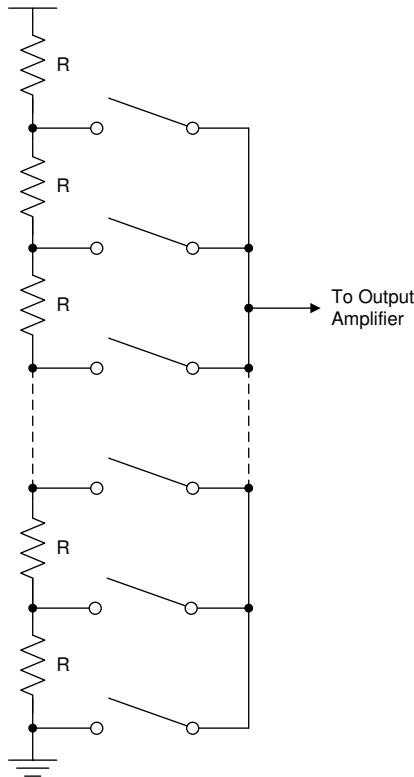

### 6.3.1.1 DAC Resistor String

The resistor string structure consists of a series of resistors, each of value  $R$ , as shown in Figure 6-2. The code loaded to the DAC determines at which node on the string the voltage is tapped off to be fed into the output amplifier. The voltage is tapped off by closing one of the switches connecting the string to the amplifier. This resistor string architecture has inherent monotonicity, voltage output, and low glitch.

Figure 6-2. DAC Resistor String

### 6.3.1.2 DAC Register Structure

The DAC produces unipolar output voltages proportional to a 13-bit input data code. Input data are written to the DAC data register in straight binary format for both output ranges. The input data are either generated by the LUT and ALU or input directly through the serial interface.

[Equation 1](#) gives the DAC transfer function.

$$V_{DAC} = \left( DACIN / 2^{13} \times 10V \right) + V_{MIN} \quad (1)$$

where:

- $DACIN$  = the decimal equivalent of the binary code that is loaded to the DAC.  $DACIN$  range = 0 to  $2^{13} - 1$ .

- $V_{MIN}$  = the lowest voltage for the selected DAC output range. Either 0V for a positive range or  $-10V$  for a negative range.

[Section 6.3.4.3](#) describes the maximum output code span of the LUT for the given base value. The maximum slope of the transfer function stored in the LUT and the full temperature range define the maximum  $V_{DAC}$  output voltage excursion over temperature. When the DAC data are generated by the LUT and ALU, [Equation 2](#) gives the maximum  $V_{DAC}$  output excursion over temperature.

$$dV_{DAC} = \text{SLOPE}_{MAX} \times T_{RANGE} \times V_{LSB} = 3.75 \text{ LSB}/^{\circ}\text{C} \times 200^{\circ}\text{C} \times \frac{10V}{2^{13}} = 916 \text{ mV} \quad (2)$$

However, this limitation is lifted when data are input directly to the DAC through the serial interface. In this case, the DAC input range is the full 8192 codes, and the DAC output spans the voltage ranges. [Table 6-1](#) shows the DAC data format.

**Table 6-1. DAC Data Format**

| DAC DATA REGISTER<br>(1.22mV RESOLUTION) |      | NEGATIVE DAC OUTPUT<br>VOLTAGE (V)<br>$V_{SS} = -11V$ , $V_{CC} = \text{GROUND}$ | POSITIVE DAC OUTPUT<br>VOLTAGE (V)<br>$V_{CC} = 5.5V$ , $V_{SS} = \text{GROUND}$ |

|------------------------------------------|------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| BINARY                                   | HEX  |                                                                                  |                                                                                  |

| 0 0000 0000 0000                         | 0000 | -10                                                                              | 0                                                                                |

| 0 0000 0000 0001                         | 0001 | -9.99878                                                                         | 0.00122                                                                          |

| 1 0000 0000 0000                         | 1000 | -5                                                                               | 5                                                                                |

| 1 0001 1001 1001                         | 1199 | -4.50073                                                                         | 5.49927                                                                          |

| 1 0001 1001 1010                         | 119A | -4.49951                                                                         | 5.5                                                                              |

| 1 0001 1001 1011                         | 119B | -4.49829                                                                         | 5.5                                                                              |

| 1 1111 1111 1110                         | 1FFE | -0.00244                                                                         | 5.5                                                                              |

| 1 1111 1111 1111                         | 1FFF | -0.00122                                                                         | 5.5                                                                              |

### 6.3.1.3 DAC Buffer Amplifier

The DAC output buffer amplifiers are capable of rail-to-rail operation. The amplifier outputs are available at the DAC[0:3] and CLAMP[1:2] output pins. The buffer amplifiers are biased from the dedicated supply rails:  $V_{CC}$  and  $V_{SS}$ . The maximum DAC output voltage range is limited by these supplies.

The output amplifier is designed to drive capacitive loads as high as  $15\mu F$  without oscillation. The output buffers are able to source 100mA and sink 20mA. The device implements short-circuit protection for momentary output shorts to ground and either supply. The sink short-circuit current is 40mA. The source short-circuit current is configurable to either 120mA (high-current mode) or 70mA (normal-current mode).

The high output current of the device gives good slewing characteristics even with large capacitive loads. To estimate the positive and negative slew rates for large capacitive loads, divide the source and sink short-circuit current values by the capacitor.

After start-up, the DAC output range is set automatically by the voltage present in the  $V_{SS}$  and  $V_{CC}$  pins. The DAC buffer amplifiers are automatically configured for positive voltage operation when  $V_{SS} = 0V$  and  $4.5V \leq V_{CC} \leq 5.5V$ . Alternatively, the amplifiers are configured for negative voltage operation when  $V_{CC} = 0V$  and  $4.5V \leq V_{SS} \leq 11V$ .

The device continuously monitors the buffer amplifier supplies to provide proper operation. In negative voltage operation, the valid  $V_{SS}$  supply range is optimized through the VSSRANGE bit to distinguish between the wide  $V_{SS}$  configuration ( $-11V \leq V_{SS} < -7V$ ) and the narrow  $V_{SS}$  configuration ( $-7V \leq V_{SS} \leq -4.5V$ ). The  $V_{SS}$  range selection allows the device to detect supply failure conditions faster. The valid supply range for the device is determined at start-up. [Table 6-2](#) shows the valid supply matrix.

**Table 6-2. Valid Supply Matrix**

| SUPPLY CONFIGURATION          | SUPPLY                       |                              |

|-------------------------------|------------------------------|------------------------------|

|                               | $V_{CC}$                     | $V_{SS}$                     |

| Invalid configuration         | $0V \leq V_{CC} < 4.5V$      | $-4.5V < V_{SS} \leq 0V$     |

| $V_{CC}$ configuration        | $4.5V \leq V_{CC} \leq 5.5V$ | $V_{SS} = 0V$                |

| Invalid configuration         | $4.5V \leq V_{CC} \leq 5.5V$ | $V_{SS} < 0V$                |

| Narrow $V_{SS}$ configuration | $V_{CC} = 0V$                | $-7V \leq V_{SS} \leq -4.5V$ |

| Invalid configuration         | $V_{CC} > 0V$                | $-7V \leq V_{SS} \leq -4.5V$ |

| Wide $V_{SS}$ configuration   | $V_{CC} = 0V$                | $-11V \leq V_{SS} < -7V$     |

| Invalid configuration         | $V_{CC} > 0V$                | $-11V \leq V_{SS} < -7V$     |

During operation, if  $V_{CC}$  or  $V_{SS}$  fall to less than the specified threshold value associated to the supply configuration, or  $V_{DD}$  drops to less than 4.5V, a reset event is generated and the DAC outputs enter the special  $V_{SS}$  clamp mode. In  $V_{SS}$  clamp mode, the DAC output pins are internally connected to the  $V_{SS}$  pin.

The six DAC buffer amplifiers share the  $V_{CC}$  and  $V_{SS}$  supplies; therefore, all DACs are configured to the same output range.

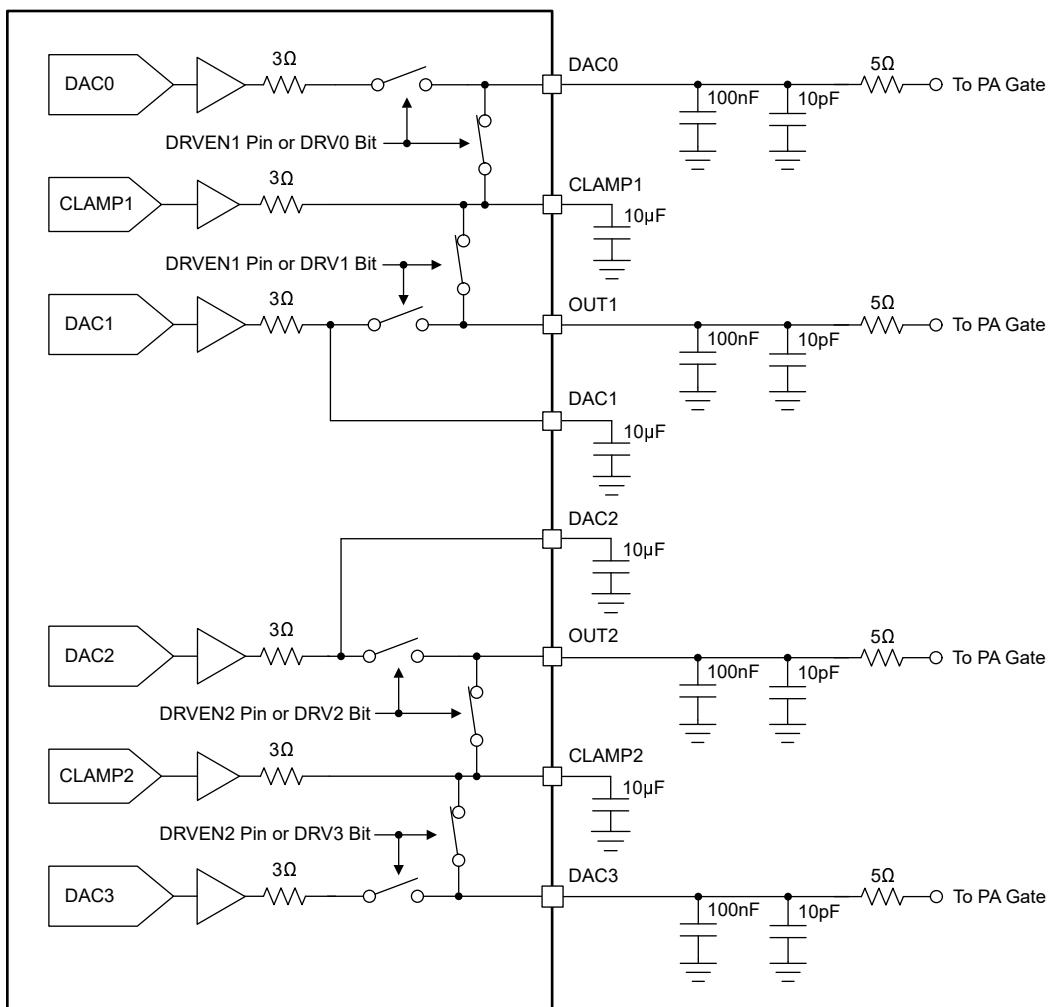

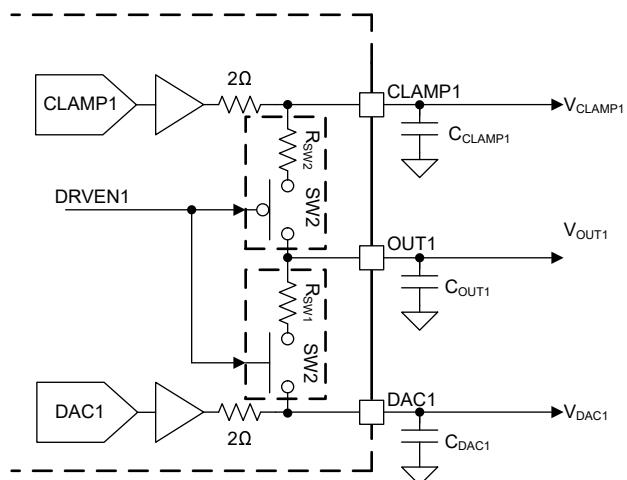

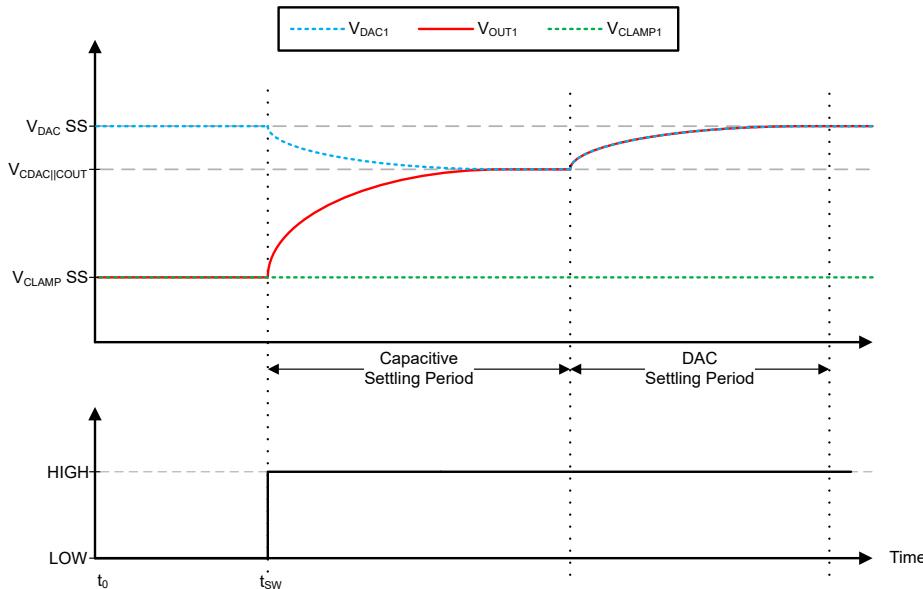

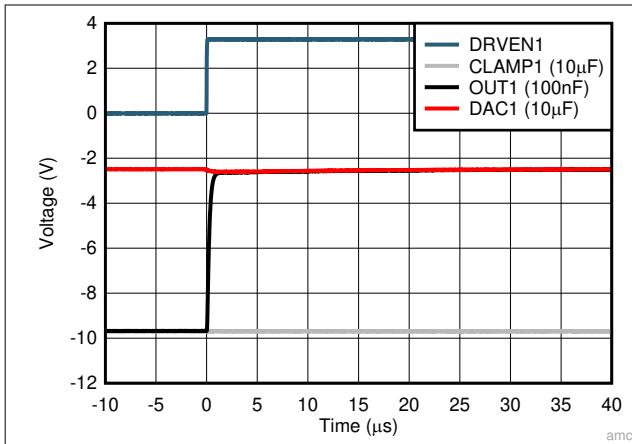

### 6.3.2 Output Switch Overview

The device facilitates rapid turn on and turn off of the voltage at the device OUT[1:2] outputs. The OUT[1:2] outputs can be switched on or off by the DRV[1:2] inputs or alternatively through software. The *on* voltages are set by the DAC[1:2] outputs while the *off* voltages are set by the CLAMP[1:2] outputs. The OUT[1:2] pins are driven by DAC[1:2] when the corresponding switch control pin or bit is asserted high. Otherwise, the OUT[1:2] pins are driven by the dedicated CLAMP[1:2] DAC outputs.

Additionally, the DAC0 and DAC3 outputs include a simplified switch network that facilitates fast turnoff. Switch the DAC0 and DAC3 pins on or off through one of the DRV[1:2] pins or through software. The DAC0 and DAC3 output pins are driven by the DAC0 and DAC3 buffers when on, and by the CLAMP[1:2] outputs when off. While fast turnoff is possible as a result of the CLAMP[1:2] output pins, turn-on time is limited by the DAC0 and DAC3 buffer bandwidth. [Figure 6-3](#) shows a typical switch application.

**Figure 6-3. Typical Switch Application**

The control and switch design is optimized for minimum delay between the DRV[1:2] input and the output pins voltage switching. The switches default to the off state at start-up or after an alarm event.

### 6.3.3 Temperature Sensors

The device includes a remote temperature sensor monitor and a local temperature sensor. The device is configurable to continuously monitor both temperature inputs and use the conversion results as inputs to the four LUTs.

Remote temperature sensors are typically low-cost discrete NPN or PNP transistors, substrate thermal transistors, or diodes.

#### 6.3.3.1 Temperature Data Format

The local and remote temperature sensors have a resolution of 12 bits ( $0.0625^{\circ}\text{C}$ ). Temperature data that result from conversions within the default measurement range are represented in binary form. [Table 6-3](#) shows the temperature data format. Any temperatures greater than  $127^{\circ}\text{C}$  result in a value that rails to 127.9375 (7FFh). To set the device to measure over an extended temperature range, set the TMPRANGE bit. The change in measurement range and data format from standard binary to extended binary occurs at the next temperature conversion. For data captured in the extended temperature range configuration, an offset of 64 (40h) is added to the standard binary value; see the *Extended Binary* column of the table. This configuration allows measurement of temperatures as low as  $-64^{\circ}\text{C}$  and as high as  $191.9375^{\circ}\text{C}$ , whereas most other remote temperature sensors operate within the range of only  $-55^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$ . Additionally, although the local temperature sensor operates at junction temperatures ranging from  $-55^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$ , the accuracy is specified only from  $-55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ . Observe the parameter values listed in the *Absolute Maximum Ratings*.

**Table 6-3. Temperature Data Format (High Byte)**

| TEMPERATURE<br>( $^{\circ}\text{C}$ ) | TEMPERATURE REGISTER HIGH BYTE VALUE<br>( $1^{\circ}\text{C}$ RESOLUTION) |     |                                |     |

|---------------------------------------|---------------------------------------------------------------------------|-----|--------------------------------|-----|

|                                       | STANDARD BINARY <sup>(1)</sup>                                            |     | EXTENDED BINARY <sup>(2)</sup> |     |

|                                       | BINARY                                                                    | HEX | BINARY                         | HEX |

| -64                                   | 1100 0000                                                                 | C0  | 0000 0000                      | 00  |

| -50                                   | 1100 1110                                                                 | CE  | 0000 1110                      | 0E  |

| -25                                   | 1110 0111                                                                 | E7  | 0010 0111                      | 27  |

| -1                                    | 1111 1111                                                                 | FF  | 0011 1111                      | 3F  |

| 0                                     | 0000 0000                                                                 | 00  | 0100 0000                      | 40  |

| 1                                     | 0000 0001                                                                 | 01  | 0100 0001                      | 41  |

| 10                                    | 0000 1010                                                                 | 0A  | 0100 1010                      | 4A  |

| 25                                    | 0001 1001                                                                 | 19  | 0101 1001                      | 59  |

| 50                                    | 0011 0010                                                                 | 32  | 0111 0010                      | 72  |

| 75                                    | 0100 1011                                                                 | 4B  | 1000 1011                      | 8B  |

| 100                                   | 0110 0100                                                                 | 64  | 1010 0100                      | A4  |

| 125                                   | 0111 1101                                                                 | 7D  | 1011 1101                      | BD  |

| 127                                   | 0111 1111                                                                 | 7F  | 1011 1111                      | BF  |

| 150                                   | 0111 1111                                                                 | 7F  | 1101 0110                      | D6  |

| 175                                   | 0111 1111                                                                 | 7F  | 1110 1111                      | EF  |

| 191                                   | 0111 1111                                                                 | 7F  | 1111 1111                      | FF  |

(1) Resolution is  $1^{\circ}\text{C}/\text{count}$ . Negative values are represented in 2's complement format.

(2) Resolution is  $1^{\circ}\text{C}/\text{count}$ . All values are unsigned with a  $-64^{\circ}\text{C}$  offset.

Both local and remote temperature data use two bytes for data storage. The high byte stores the temperature with 1°C resolution. The second, or low, byte stores the decimal fraction value of the temperature and allows a higher measurement resolution. [Table 6-4](#) shows the decimal fraction temperature data format. The measurement resolution for both the local and remote temperature sensors is 0.0625°C.

**Table 6-4. Decimal Fraction Temperature Data Format (Low Byte)**

| TEMPERATURE<br>(°C) | TEMPERATURE REGISTER LOW BYTE VALUE<br>(0.0625°C RESOLUTION) <sup>(1)</sup> |     |

|---------------------|-----------------------------------------------------------------------------|-----|

|                     | STANDARD AND EXTENDED BINARY                                                | HEX |

| 0                   | 0000 0000                                                                   | 00  |

| 0.0625              | 0001 0000                                                                   | 10  |

| 0.1250              | 0010 0000                                                                   | 20  |

| 0.1875              | 0011 0000                                                                   | 30  |

| 0.2500              | 0100 0000                                                                   | 40  |

| 0.3125              | 0101 0000                                                                   | 50  |

| 0.3750              | 0110 0000                                                                   | 60  |

| 0.4375              | 0111 0000                                                                   | 70  |

| 0.5000              | 1000 0000                                                                   | 80  |

| 0.5625              | 1001 0000                                                                   | 90  |

| 0.6250              | 1010 0000                                                                   | A0  |

| 0.6875              | 1011 0000                                                                   | B0  |

| 0.7500              | 1100 0000                                                                   | C0  |

| 0.8125              | 1101 0000                                                                   | D0  |

| 0.8750              | 1110 0000                                                                   | E0  |

| 0.9375              | 1111 0000                                                                   | F0  |

(1) Resolution is 0.0625°C/count. All possible values are shown.

#### 6.3.3.1.1 Standard Binary-to-Decimal Temperature Data Calculation Example

High-byte conversion (for example, 0111 0011):

- Convert the right-justified binary high byte to hexadecimal.

- From hexadecimal, multiply the first number by  $16^0 = 1$  and the second number by  $16^1 = 16$ .

- The sum equals the decimal equivalent: 0111 0011b → 73h →  $(3 \times 16^0) + (7 \times 16^1) = 115$

Low-byte conversion (for example, 0111 0000):

- To convert the left-justified binary low-byte to decimal, use bits 7 through 4 and ignore bits 3 through 0 because these bits do not affect the value of the number.

- $0111b \rightarrow (0 \times 1/2)^1 + (1 \times 1/2)^2 + (1 \times 1/2)^3 + (1 \times 1/2)^4 = 0.4375$

#### 6.3.3.1.2 Standard Decimal-to-Binary Temperature Data Calculation Example

For positive temperatures (for example, 20°C):

- $(20°C) / (1°C/count) = 20 \rightarrow 14h \rightarrow 0001 0100$

- Convert the number to binary code with 8-bit, right-justified format, and MSB = 0 to denote a positive sign.

- 20°C is stored as 0001 0100 → 14h.

For negative temperatures (for example, -20°C):

- $(|-20|) / (1°C/count) = 20 \rightarrow 14h \rightarrow 0001 0100$

- Generate the 2's complement of a negative number by complementing the absolute value binary number and adding 1.

- 20°C is stored as 1110 1100 → ECh.

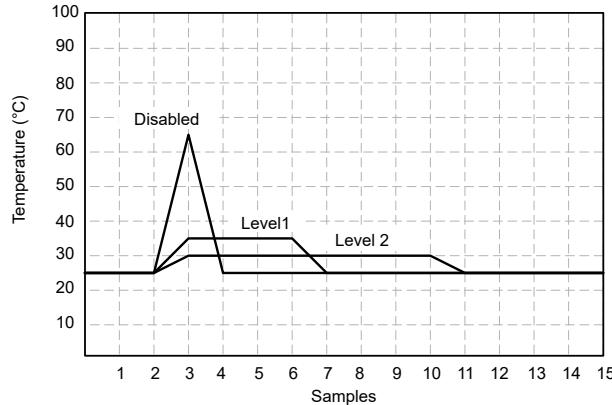

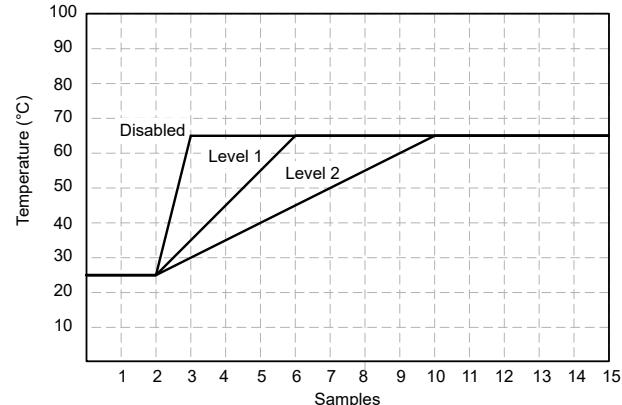

### 6.3.3.2 Temperature Sensor Conversion Rate

The temperature sensor conversion rate setting controls the rate at which temperature conversions are performed. The conversion rate adjusts the idle time between conversions but does not adjust the conversion time. **Table 6-5** lists the conversion rate options and corresponding time between conversions. The default value of the register is 08h, which gives a default rate of 16 conversions per second.

**Table 6-5. Temperature Sensor Conversion Rate**

| VALUE | CONVERSIONS PER SECOND | TIME (SECONDS)   |

|-------|------------------------|------------------|

| 00h   | 0.0625                 | 16               |

| 01h   | 0.125                  | 8                |

| 02h   | 0.25                   | 4                |

| 03h   | 0.5                    | 2                |

| 04h   | 1                      | 1                |

| 05h   | 2                      | 0.5              |

| 06h   | 4                      | 0.25             |

| 07h   | 8                      | 0.125            |

| 08h   | 16 (default)           | 0.0625 (default) |

| 09h   | 32                     | 0.03125          |

### 6.3.3.3 Remote Temperature Sensor

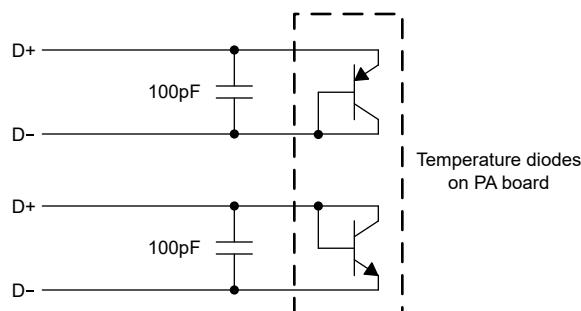

The device includes a remote temperature-measurement channel. Remote temperature sensors are typically low-cost discrete NPN or PNP transistors, substrate thermal transistors, or diodes. Use either NPN or PNP transistors, as long as the base-emitter junction is used as the remote temperature sense. Use diode-connected NPN transistors. Use either transistor- or diode-connected PNP transistors. **Figure 6-4** shows the remote temperature sensor connection. Advanced features, such as series resistance cancellation, programmable nonideality factor ( $\eta$ -factor), and a programmable offset, are combined to provide a robust thermal monitoring device with improved accuracy and noise immunity.

**Figure 6-4. Remote Temperature Sensor Connection**

### 6.3.3.3.1 Series Resistance Cancellation

Series resistance cancellation automatically eliminates the temperature error caused by the resistance of the routing to the remote transistor, or by the resistors of the optional external low-pass filter. The device is able to cancel a total of up to  $1\text{k}\Omega$  of series resistance, thus eliminating the need for additional characterization and temperature offset correction.

### 6.3.3.3.2 Differential Input Capacitance

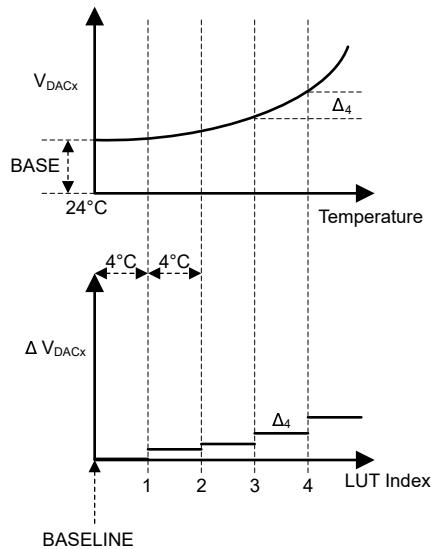

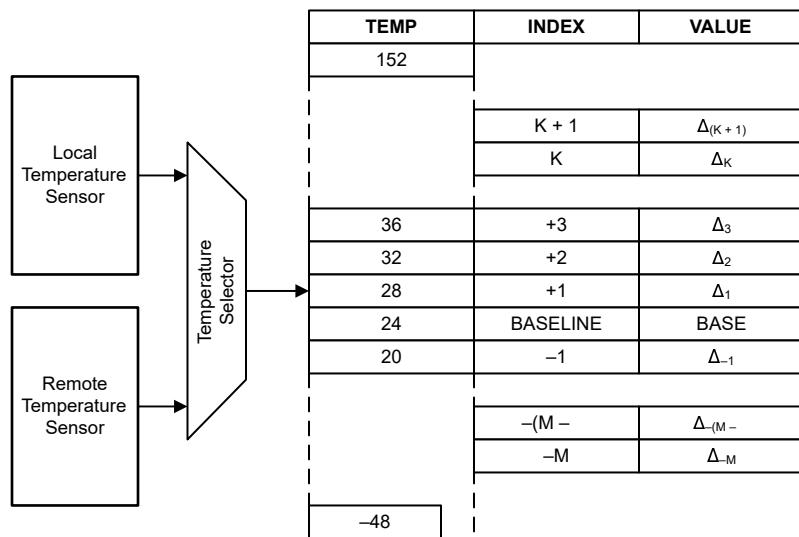

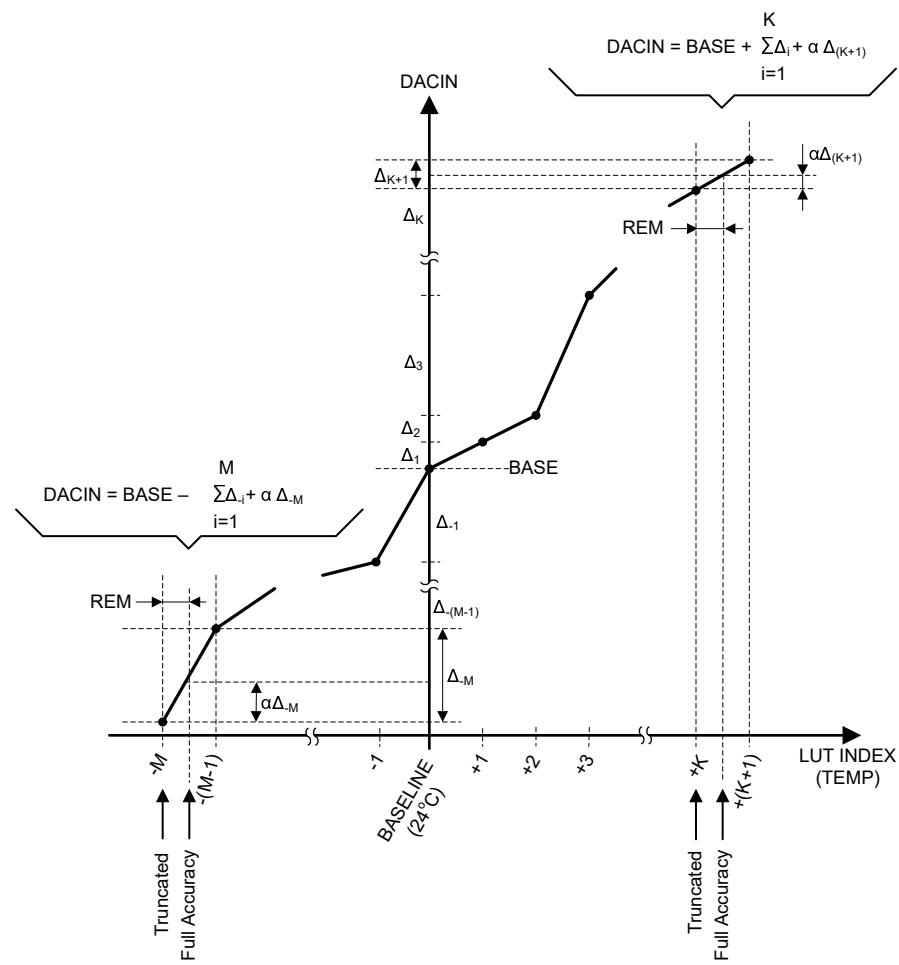

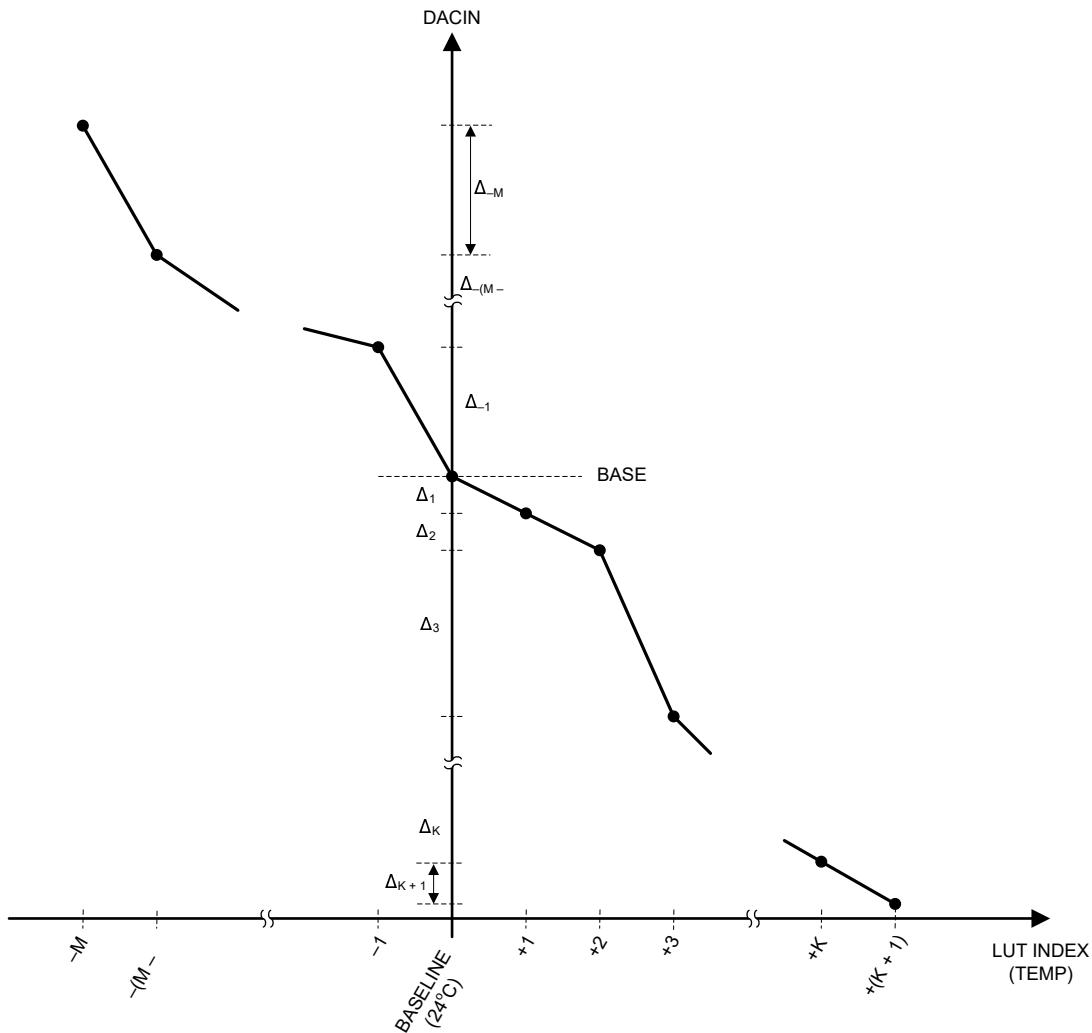

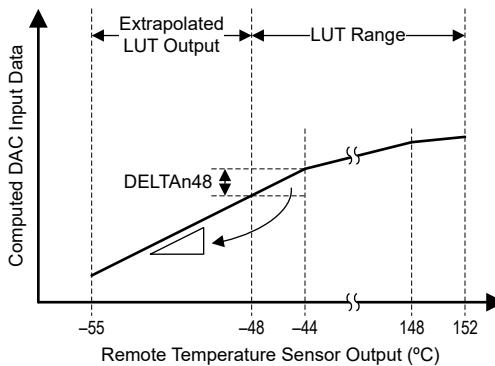

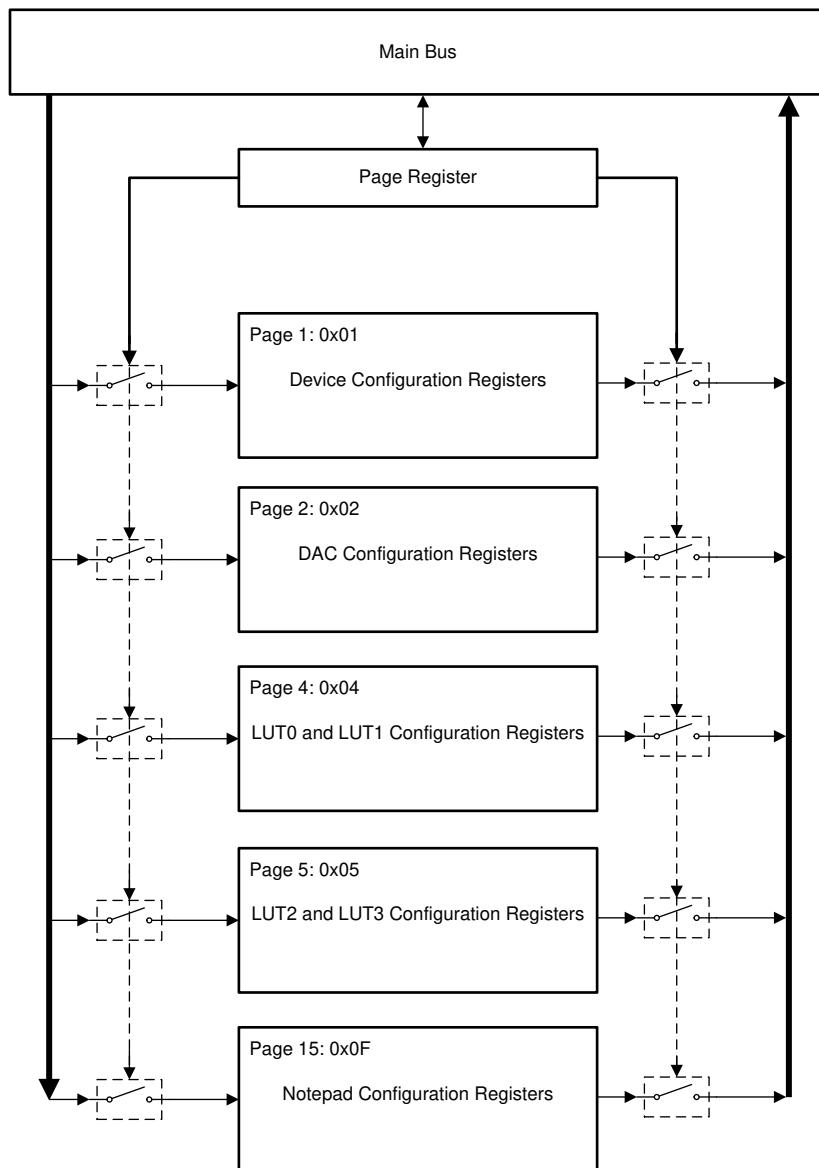

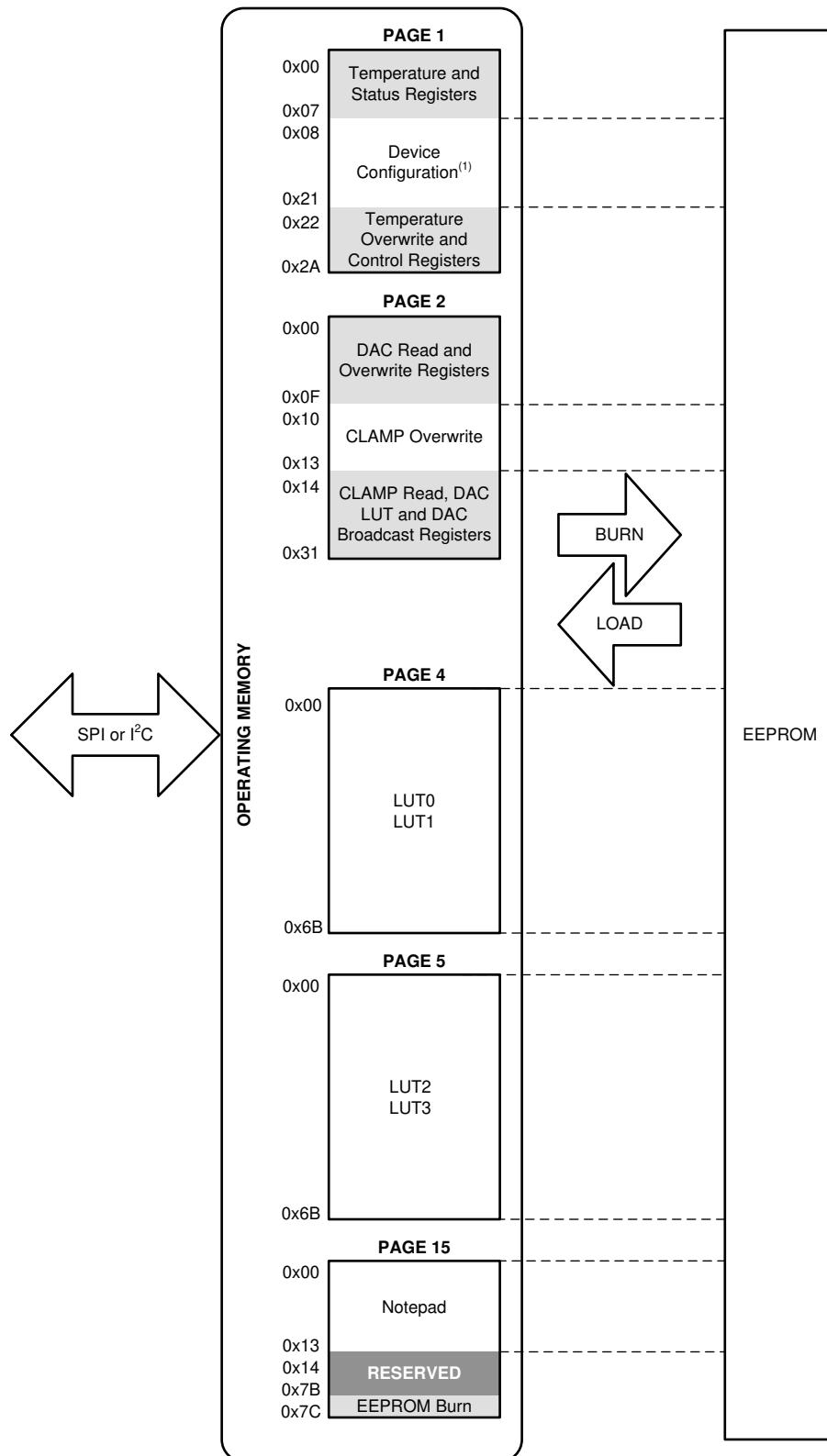

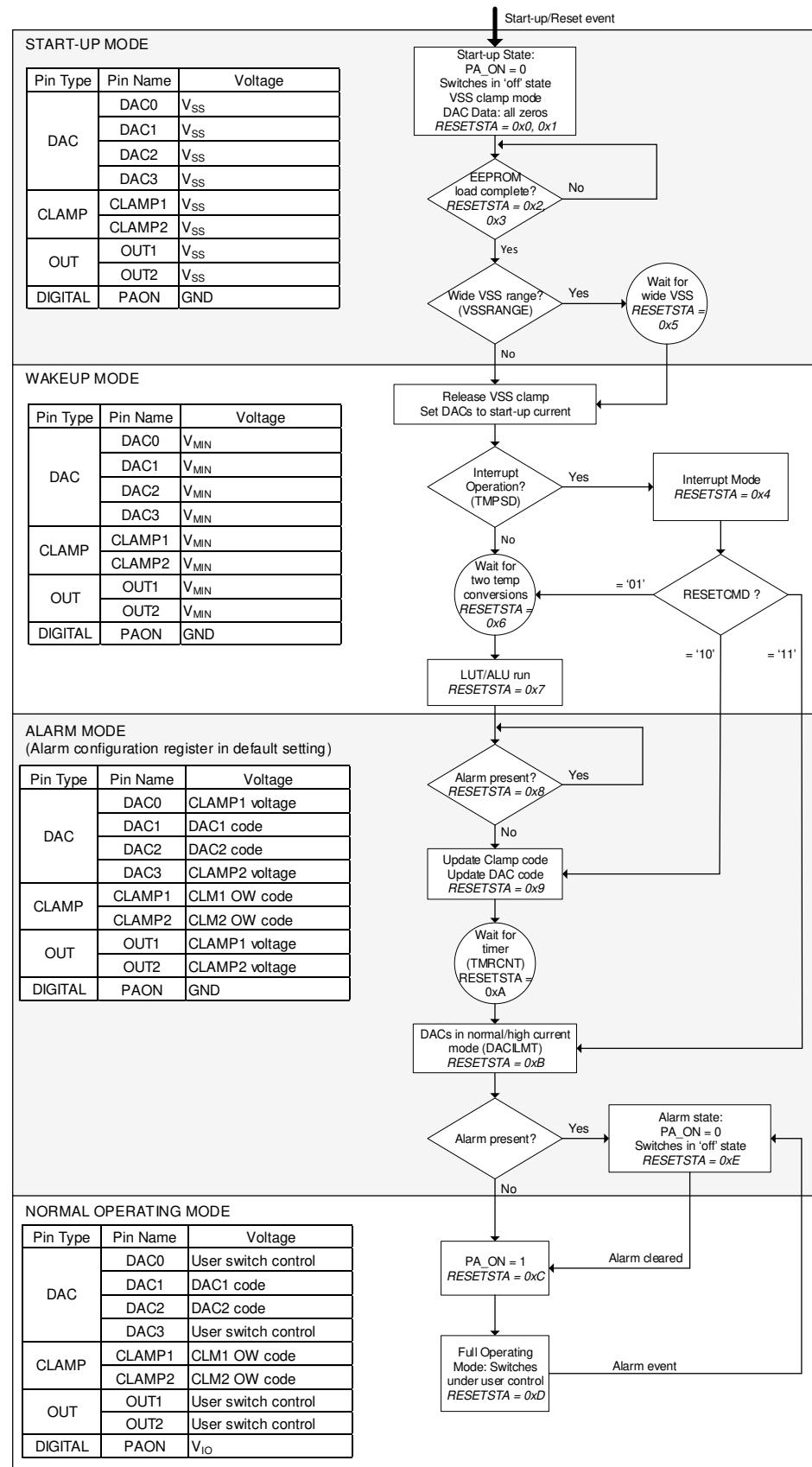

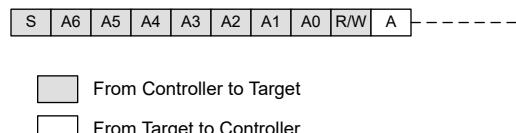

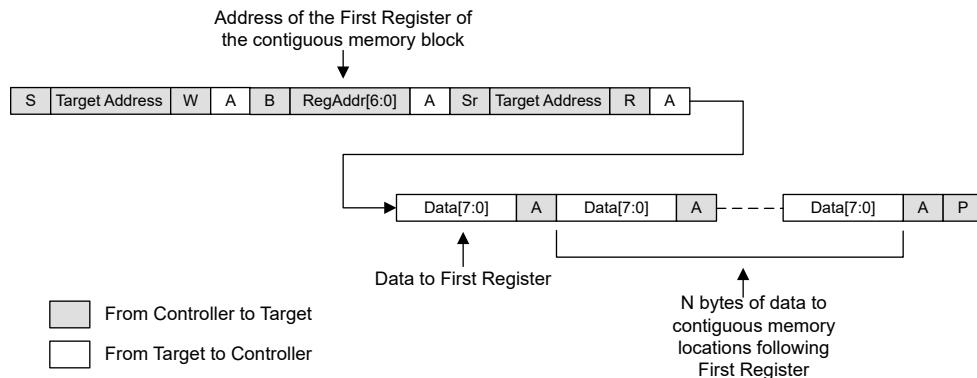

The device tolerates differential input capacitance of up to  $1000\text{pF}$  with minimal change in temperature error.