SBAS632 - OCTOBER 2013 www.ti.com

# 8-Channel, High-Bandwidth, Analog Front-End

Check for Samples: PGA5807A

### **FEATURES**

- 8-Channel Complete AFE:

- LNA, PGA, and LPF

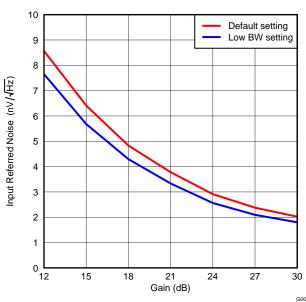

- Full-Channel Gain: 12 dB to 30 dB Input-Referred Noise: 2.1 nV/√Hz

- LNA:

- Gain: 12 dB Fully Differential

- Wide Input Common-Mode Support:

- 2.1 ± 200 mV

- Maximum Linear Input Range: 500 mV<sub>PP</sub>

- PGA Gain: 0 dB to 18 dB With 3-dB Gain Steps

- Programmable via Either Serial Interface or **External Pins**

- Maximum Total Channel Gain: 30 dB

- **Programmable LPF:**

- Corner Frequency: 75 MHz, 60 MHz

- Power (Full-Chain):

- 60 mW per Channel

- **Fast and Consistent Overload Recovery**

- Small Package: 9-mm × 9-mm QFN-64

### **APPLICATIONS**

- **Data Acquisition Front Ends**

- **Ultrasound Imaging**

#### DESCRIPTION

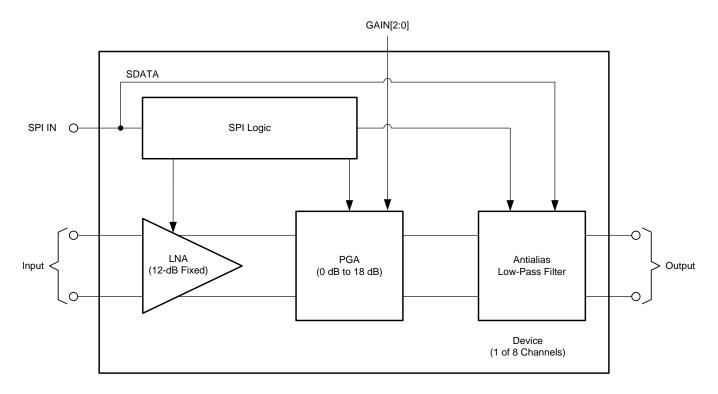

The PGA5807A is an 8-channel, high-bandwidth, analog front-end (AFE). The device functions on a single 3.3-V analog supply. The device supports highbandwidth input frequencies with a total power of 60 mW per channel. The PGA5807A consists of a lownoise amplifier (LNA), a programmable gain amplifier (PGA), and a programmable low-pass filter (LPF). The LNA has a fixed 12-dB gain (the differential amplifier supports both direct and capacitive input coupling) and supports a maximum linear input range of 500 mV<sub>PP</sub>.

The device provides gain options from 0 dB to 18 dB, in 3-dB gain steps. This 18-dB PGA gain can be programmed using either the serial interface or external pins. The PGA5807A integrates an antialiasing filter in the form of an LPF to reduce noise. The device is available in a very small, 9-mm x 9-mm QFN-64 package and is specified for operation over the -40°C to +85°C temperature range.

SBAS632 – OCTOBER 2013 www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### ORDERING INFORMATION(1)

| PRODUCT  | PACKAGE-LEAD | PACKAGE DESIGNATOR |  |  |  |

|----------|--------------|--------------------|--|--|--|

| PGA5807A | QFN-64       | RGC                |  |  |  |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or visit the device product folder at www.ti.com.

#### **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature range, unless otherwise noted. (1)

|                                                              |                           | VALUE                             | UNIT |

|--------------------------------------------------------------|---------------------------|-----------------------------------|------|

| Supply voltage range                                         | AVDD                      | -0.3 to 3.9                       | V    |

| Voltage at analog input and digital input                    | t                         | -0.3 to minimum (3.6, AVDD + 0.3) | V    |

| Tomporatura range                                            | Operating, T <sub>A</sub> | -40 to +85                        | °C   |

| Temperature range                                            | Storage, T <sub>stg</sub> | –55 to +150                       | °C   |

| Electrostatic discharge (ESD) ratings Human body model (HBM) |                           | 1                                 | kV   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

|                |                                 | MIN  | NOM MAX | UNIT |

|----------------|---------------------------------|------|---------|------|

| AVDD           | Analog voltage supply           | 3.15 | 3.6     | V    |

| T <sub>A</sub> | Operating temperature           | -40  | +85     | °C   |

|                | Input common-mode voltage range | 1.9  | 2.3     | V    |

### THERMAL INFORMATION

|                                                        |                                              | PGA5807   |       |

|--------------------------------------------------------|----------------------------------------------|-----------|-------|

|                                                        | THERMAL METRIC <sup>(1)</sup>                | RGC (QFN) | UNITS |

|                                                        |                                              | 64 PINS   |       |

| θ <sub>JA</sub> Junction-to-ambient thermal resistance |                                              | 22.8      |       |

| $\theta_{JCtop}$                                       | Junction-to-case (top) thermal resistance    | 6.9       |       |

| $\theta_{JB}$                                          | Junction-to-board thermal resistance         | 2.4       | °C/W  |

| ΨЈТ                                                    | Junction-to-top characterization parameter   | 0.1       | C/VV  |

| ΨЈВ                                                    | Junction-to-board characterization parameter | 2.4       |       |

| $\theta_{JCbot}$                                       | Junction-to-case (bottom) thermal resistance | 0.2       |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

### **ELECTRICAL CHARACTERISTICS**

Typical values are at  $T_A$  = +25°C, AVDD = 3.3 V, input dc-coupled with a 2.1-V common-mode voltage, LNA gain = 12 dB, PGA gain = 18 dB, total channel gain = 30 dB, bandwidth = high, and  $V_{OUT}$  = -1 dBFS, unless otherwise specified. Minimum and maximum values are specified across the full temperature range of  $T_{MIN}$  = -40°C to  $T_{MAX}$  = +85°C with AVDD = 3.3 V.

|                        | PARAMETE                          | :R                 | TEST CONDITIONS                                                                                     | MIN | TYP   | MAX | UNIT               |

|------------------------|-----------------------------------|--------------------|-----------------------------------------------------------------------------------------------------|-----|-------|-----|--------------------|

|                        | Input-referred noise              |                    | f = 25 MHz, total channel gain = 30 dB                                                              |     | 2.1   |     | nV/√ <del>Hz</del> |

|                        | Noise figure                      |                    | $R_S = 100 \Omega$ , differential                                                                   |     | 6.4   |     | dB                 |

|                        | Maximum linear inp                | ut voltage         | Total channel gain = 12 dB, differential                                                            |     | 500   |     | $mV_{PP}$          |

|                        | Maximum linear out                | put swing          |                                                                                                     |     | 2     |     | $V_{PP}$           |

| G <sub>LNA</sub>       | LNA gain                          |                    |                                                                                                     |     | 12    |     | dB                 |

|                        | Maximum channel gain              |                    |                                                                                                     | 29  | 30    | 31  | dB                 |

|                        | PGA gain range                    |                    |                                                                                                     | 0   |       | 18  | dB                 |

|                        | Gain step                         |                    |                                                                                                     |     | 3     |     | dB                 |

|                        | Total output-referre              | d noise            | Total channel gain = 30 dB                                                                          |     | 450   |     | μV                 |

|                        | Input resistance                  |                    |                                                                                                     |     | 5     |     | kΩ                 |

| Ci                     | Input capacitance                 |                    |                                                                                                     |     | 3     |     | pF                 |

| LPF –3-dE<br>Gain mato | LPF -3-dB cutoff fre              | equency            |                                                                                                     |     | 75    |     | MHz                |

|                        | Online and tables as              |                    | Across devices, T <sub>A</sub> = +25°C                                                              | -1  |       | 1   | dB                 |

|                        | Gain matching                     |                    | Across channels in the same device                                                                  |     | ±0.25 |     | dB                 |

| $V_{ICR}$              | Input common-mode voltage range   |                    |                                                                                                     | 1.9 |       | 2.3 | V                  |

|                        | Output offset                     |                    |                                                                                                     | -50 |       | 50  | mV                 |

| V <sub>OCR</sub>       | Output common-mo                  | de voltage         |                                                                                                     |     | 950   |     | mV                 |

| HD2                    |                                   | Second             | f = 25 MHz, V <sub>OUT</sub> = -1 dBFS                                                              |     | -55   |     | dBc                |

| HD3                    | Harmonic distortion               | Third              | f = 25 MHz, V <sub>OUT</sub> = -1 dBFS                                                              |     | -50   |     | dBc                |

| THD                    | diotortion                        | Total              | f = 25 MHz, V <sub>OUT</sub> = -1 dBFS                                                              |     | -48   |     | dBc                |

| IMD3                   | Intermodulation dist              | ortion             | f <sub>1</sub> = 25 MHz at -7 dBFS, f <sub>2</sub> = 25 MHz,<br>1 MHz at -7 dBFS, for all PGA gains |     | -45   |     | dBc                |

|                        | Fundamental cross                 | alk                | f = 25 MHz, V <sub>OUT</sub> = -1 dBFS                                                              |     | -50   |     | dBc                |

|                        |                                   | Total, per channel |                                                                                                     |     | 60    | 69  | mW/ch              |

| $P_D$                  | Power dissipation                 | Danier danie da    | Partial power-down                                                                                  |     | 4.2   |     | mW/ch              |

|                        |                                   | Power-down mode    | Complete power-down                                                                                 |     |       | 2.5 | mW/ch              |

|                        | AVDD current (3.3 '               | V)                 |                                                                                                     |     | 145   |     | mA                 |

|                        | Settling time for over            | erload recovery    | For 12-dB higher signal than linear input                                                           |     | -30   |     | ns                 |

|                        | Dames ver errer                   | 4:                 | Partial power-down                                                                                  |     | 1     |     | μs                 |

|                        | Power-up response                 | time               | Full power-down                                                                                     |     | 1     |     | ms                 |

| DODD                   | D                                 | tala madia         | f = 10 kHz, gain = 30 dB                                                                            |     | -40   |     | dBc                |

| PSRR                   | PSRR Power-supply rejection ratio |                    | f = 10 kHz, gain = 12 dB                                                                            |     | -38   |     | dBc                |

## **DIGITAL CHARACTERISTICS**

Typical values are at  $T_A$  = +25°C and AVDD = 3.3 V, unless otherwise specified. Minimum and maximum values are specified across the full temperature range of  $T_{MIN}$  = -40°C to  $T_{MAX}$  = +85°C.

|                        | PARAMETER                 | TEST CONDITIONS | MIN | TYP  | MAX | UNIT |  |  |  |  |

|------------------------|---------------------------|-----------------|-----|------|-----|------|--|--|--|--|

| DIGITAL INPUTS/OUTPUTS |                           |                 |     |      |     |      |  |  |  |  |

| V <sub>IH</sub>        | Logic high input voltage  |                 | 2   |      |     | V    |  |  |  |  |

| V <sub>IL</sub>        | Logic low input voltage   |                 | 0   |      |     | V    |  |  |  |  |

| I <sub>IH</sub>        | Logic high input current  |                 |     | 200  |     | μΑ   |  |  |  |  |

| I <sub>IL</sub>        | Logic low input current   |                 |     | 200  |     | μΑ   |  |  |  |  |

| Ci                     | Input capacitance         |                 |     | 5    |     | pF   |  |  |  |  |

| V <sub>OH</sub>        | Logic high output voltage | SDOUT pin       |     | AVDD |     | V    |  |  |  |  |

| V <sub>OL</sub>        | Logic low output voltage  | SDOUT pin       |     | 0    |     | V    |  |  |  |  |

#### PIN CONFIGURATION

#### **RGC PACKAGE** QFN-64 (TOP VIEW) SDOUT SCLK AVDD 63 62 49 61 9 59 58 54 53 52 51 20 22 26 22 48 OUTP1 1 INP1 47 OUTM1 INM1 2 INP2 3 46 OUTP2 INM2 4 45 OUTM2 INP3 5 44 OUTP3 INM3 6 43 OUTM3 INP4 7 42 OUTP4 INM4 41 OUTM4 8 Thermal Pad INP5 40 OUTP5 9 39 OUTM5 INM5 10 INP6 11 38 OUTP6 37 OUTM6 INM6 12 36 OUTP7 INP7 13 35 OUTM7 INM7 14 INP8 34 OUTP8 15 33 OUTM8 INM8 16 9 22 23 25 26 28 29 30 24 27 31 AVDD

### **Table 1. PIN FUNCTIONS**

| NAME     | NO.                               | FUNCTION       |                                                                                             | DESCRIPTION                                                                                                            |  |  |  |  |  |

|----------|-----------------------------------|----------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| AVDD     | 17, 28, 31, 49,<br>62-64          | Supply         | Analog supply pin, 3.3 V                                                                    |                                                                                                                        |  |  |  |  |  |

| AVSS     | 19, 20, 24, 27,<br>29, 50, 54, 61 | Ground         | Analog ground                                                                               |                                                                                                                        |  |  |  |  |  |

| GAIN0    | 51                                | Digital input  | When RESET is high, this pin is used to pro<br>Refer to Table 2 for more details. Note: Use |                                                                                                                        |  |  |  |  |  |

| GAIN1    | 52                                | Digital input  | When RESET is high, this pin is used to pro<br>Refer to Table 2 for more details. Note: Use |                                                                                                                        |  |  |  |  |  |

| GAIN2    | 56                                | Digital input  | When RESET is high, this pin is used to pro<br>Refer to Table 2 for more details. Note: Use |                                                                                                                        |  |  |  |  |  |

| INM1     | 2                                 | Input          | Complimentary analog input for channel 1                                                    |                                                                                                                        |  |  |  |  |  |

| INP1     | 1                                 | Input          | Analog input for channel 1                                                                  |                                                                                                                        |  |  |  |  |  |

| INM2     | 4                                 | Input          | Complimentary analog input for channel 2                                                    |                                                                                                                        |  |  |  |  |  |

| INP2     | 3                                 | Input          | Analog input for channel 2                                                                  |                                                                                                                        |  |  |  |  |  |

| INM3     | 6                                 | Input          | Complimentary analog input for channel 3                                                    |                                                                                                                        |  |  |  |  |  |

| INP3     | 5                                 | Input          | Analog input for channel 3                                                                  |                                                                                                                        |  |  |  |  |  |

| INM4     | 8                                 | Input          | Complimentary analog input for channel 4                                                    |                                                                                                                        |  |  |  |  |  |

| INP4     | 7                                 | Input          | Analog input for channel 4                                                                  |                                                                                                                        |  |  |  |  |  |

| INM5     | 10                                | Input          | Complimentary analog input for channel 5                                                    | The dc input common-mode can be 2.1 V ± 200 mV.                                                                        |  |  |  |  |  |

| INP5     | 9                                 | Input          | Analog input for channel 5                                                                  |                                                                                                                        |  |  |  |  |  |

| INM6     | 12                                | Input          | Complimentary analog input for channel 6                                                    |                                                                                                                        |  |  |  |  |  |

|          |                                   | •              | 7 7 0 1                                                                                     |                                                                                                                        |  |  |  |  |  |

| INP6     | 11                                | Input          | Analog input for channel 6                                                                  |                                                                                                                        |  |  |  |  |  |

| INM7     | 14                                | Input          | Complimentary analog input for channel 7                                                    |                                                                                                                        |  |  |  |  |  |

| INP7     | 13                                | Input          | Analog input for channel 7                                                                  |                                                                                                                        |  |  |  |  |  |

| INM8     | 16                                | Input          | Complimentary analog input for channel 8                                                    |                                                                                                                        |  |  |  |  |  |

| INP8     | 15                                | Input          | Analog input for channel 8                                                                  |                                                                                                                        |  |  |  |  |  |

| NC       | 21-23, 25, 26,<br>30, 32          | _              | Unused pins; do not connect                                                                 |                                                                                                                        |  |  |  |  |  |

| OUTM1    | 47                                | Output         | Complimentary output pin for channel 1                                                      |                                                                                                                        |  |  |  |  |  |

| OUTP1    | 48                                | Output         | Output pin for channel 1                                                                    |                                                                                                                        |  |  |  |  |  |

| OUTM2    | 45                                | Output         | Complimentary output pin for channel 2                                                      |                                                                                                                        |  |  |  |  |  |

| OUTP2    | 46                                | Output         | Output pin for channel 2                                                                    |                                                                                                                        |  |  |  |  |  |

| OUTM3    | 43                                | Output         | Complimentary output pin for channel 3                                                      |                                                                                                                        |  |  |  |  |  |

| OUTP3    | 44                                | Output         | Output pin for channel 3                                                                    |                                                                                                                        |  |  |  |  |  |

| OUTM4    | 41                                | Output         | Complimentary output pin for channel 4                                                      |                                                                                                                        |  |  |  |  |  |

| OUTP4    | 42                                | Output         | Output pin for channel 4                                                                    | TI                                                                                                                     |  |  |  |  |  |

| OUTM5    | 39                                | Output         | Complimentary output pin for channel 5                                                      | The common-mode voltage is 0.95 V.                                                                                     |  |  |  |  |  |

| OUTP5    | 40                                | Output         | Output pin for channel 5                                                                    |                                                                                                                        |  |  |  |  |  |

| OUTM6    | 37                                | Output         | Complimentary output pin for channel 6                                                      |                                                                                                                        |  |  |  |  |  |

| OUTP6    | 38                                | Output         | Output pin for channel 6                                                                    |                                                                                                                        |  |  |  |  |  |

| OUTM7    | 35                                | Output         | Complimentary output pin for channel 7                                                      |                                                                                                                        |  |  |  |  |  |

| OUTP7    | 36                                | Output         | Output pin for channel 7                                                                    |                                                                                                                        |  |  |  |  |  |

| OUTM8    | 33                                | Output         | Complimentary output pin for channel 8                                                      |                                                                                                                        |  |  |  |  |  |

| OUTP8    | 34                                | Output         | Output pin for channel 8                                                                    |                                                                                                                        |  |  |  |  |  |

| PDN      | 53                                | Digital input  |                                                                                             | device with an internal 20-k $\Omega$ pull-down resistor; active high.                                                 |  |  |  |  |  |

| RESET    | 60                                | Digital input  | Logic hardware reset pin. Note: Use 3.3-V lo                                                | ogic.                                                                                                                  |  |  |  |  |  |

| SCLK     | 59                                | Digital input  | 0 1                                                                                         | -kΩ pull-down resistor. Note: Use 3.3-V logic.                                                                         |  |  |  |  |  |

| SDATA    | 58                                | Digital input  | Serial interface data input with an internal 20                                             | 0-kΩ pull-down resistor. When RESET is high, the corner rammed to a lower frequency (60 MHz) by setting this pin high. |  |  |  |  |  |

| SDOUT    | 55                                | Digital output | Serial interface readout pin                                                                |                                                                                                                        |  |  |  |  |  |

| SEN      | 57                                | Digital input  | ·                                                                                           | with an internal 20-kΩ pull-up resistor; active low.                                                                   |  |  |  |  |  |

| VBIAS    | 18                                | Decap          | -                                                                                           | capacitor or greater                                                                                                   |  |  |  |  |  |

| 1 DII 10 | 10                                | Doodp          | Bias voltage; bypass to ground with a 1-μF capacitor or greater                             |                                                                                                                        |  |  |  |  |  |

### **Table 2. PGA Gain Control**

| GAIN[2:0] | PGA_GAIN (dB) |

|-----------|---------------|

| 000       | 18            |

| 001       | 15            |

| 010       | 12            |

| 011       | 9             |

| 100       | 6             |

| 101       | 3             |

| 110       | 0             |

## **FUNCTIONAL BLOCK DIAGRAM**

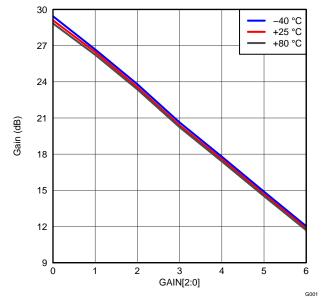

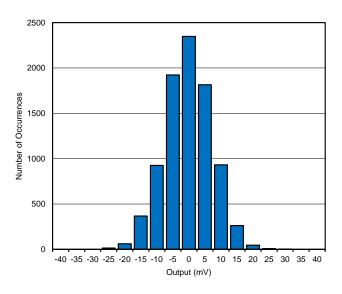

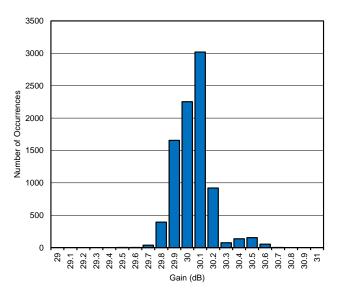

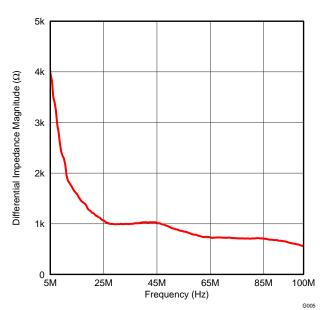

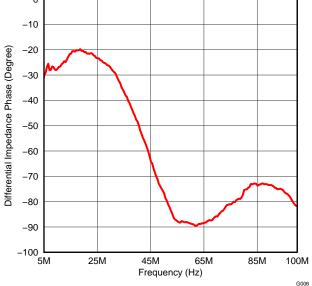

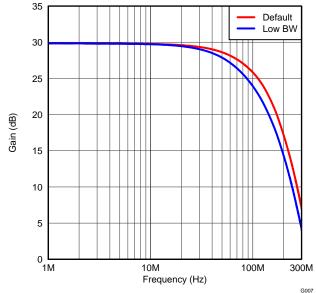

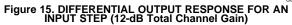

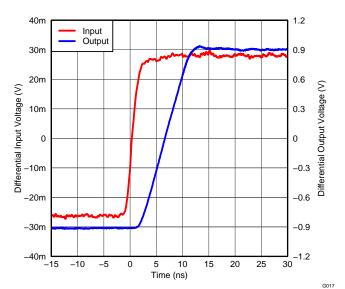

#### TYPICAL CHARACTERISTICS

At  $T_A$  = +25°C, AVDD = 3.3 V, input dc-coupled with 2.1-V input common-mode, LNA gain = 12 dB, PGA gain = 18 dB, total channel gain = 30 dB, GAIN[2:0] = 000,  $f_{IN}$  = 5 MHz, default LPF filter corner, and  $V_{OUT}$  = -1 dBFS, unless otherwise noted.

Figure 1. GAIN vs GAIN[2:0] ACROSS TEMPERATURE

Figure 3. OUTPUT OFFSET HISTOGRAM (Gain = 30 dB)

Figure 2. GAIN-MATCHING HISTOGRAM (Gain = 30 dB)

Figure 4. INPUT IMPEDANCE MAGNITUDE

Instruments

SBAS632 – OCTOBER 2013 www.ti.com

### TYPICAL CHARACTERISTICS (continued)

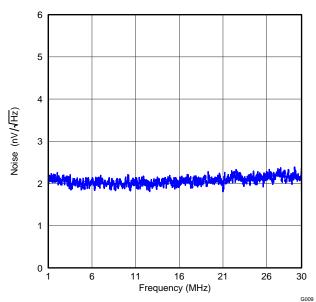

At  $T_A = +25$ °C, AVDD = 3.3 V, input dc-coupled with 2.1-V input common-mode, LNA gain = 12 dB, PGA gain = 18 dB, total channel gain = 30 dB, GAIN[2:0] = 000,  $f_{IN} = 5$  MHz, default LPF filter corner, and  $V_{OUT} = -1$  dBFS, unless otherwise noted.

Figure 5. INPUT IMPEDANCE PHASE

Figure 6. LOW-PASS FILTER RESPONSE

Figure 7. INPUT-REFERRED NOISE vs GAIN

Figure 8. INPUT-REFERRED NOISE vs FREQUENCY (Gain = 30 dB)

Submit Documentation Feedback

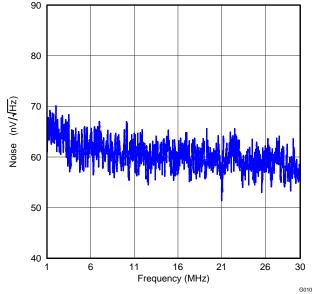

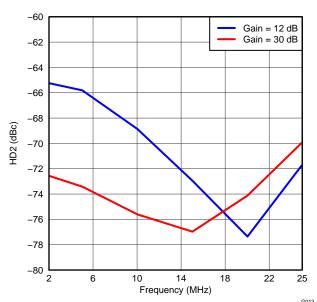

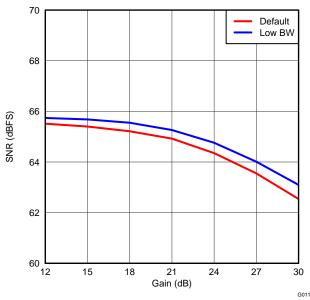

### TYPICAL CHARACTERISTICS (continued)

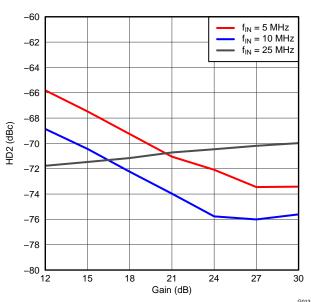

At  $T_A$  = +25°C, AVDD = 3.3 V, input dc-coupled with 2.1-V input common-mode, LNA gain = 12 dB, PGA gain = 18 dB, total channel gain = 30 dB, GAIN[2:0] = 000,  $f_{IN}$  = 5 MHz, default LPF filter corner, and  $V_{OUT}$  = -1 dBFS, unless otherwise noted.

Figure 9. OUTPUT-REFERRED NOISE vs FREQUENCY (Gain = 30 dB)

Figure 11. SECOND-HARMONIC DISTORTION vs FREQUENCY

Figure 10. SIGNAL-TO-NOISE RATIO vs GAIN ACROSS BANDWIDTH MODE

Figure 12. SECOND-HARMONIC DISTORTION vs GAIN

SBAS632 – OCTOBER 2013 www.ti.com

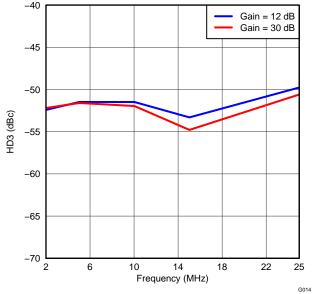

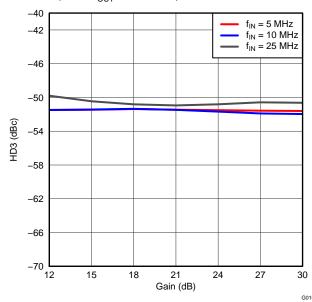

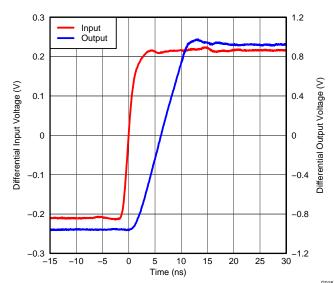

### TYPICAL CHARACTERISTICS (continued)

At  $T_A = +25$ °C, AVDD = 3.3 V, input dc-coupled with 2.1-V input common-mode, LNA gain = 12 dB, PGA gain = 18 dB, total channel gain = 30 dB, GAIN[2:0] = 000,  $f_{IN} = 5$  MHz, default LPF filter corner, and  $V_{OUT} = -1$  dBFS, unless otherwise noted.

Figure 13. THIRD-HARMONIC DISTORTION vs FREQUENCY

Figure 16. DIFFERENTIAL OUTPUT RESPONSE FOR AN INPUT STEP (30-dB Total Channel Gain)

Submit Documentation Feedback

## **TYPICAL CHARACTERISTICS (continued)**

At  $T_A$  = +25°C, AVDD = 3.3 V, input dc-coupled with 2.1-V input common-mode, LNA gain = 12 dB, PGA gain = 18 dB, total channel gain = 30 dB, GAIN[2:0] = 000,  $f_{IN}$  = 5 MHz, default LPF filter corner, and  $V_{OUT}$  = -1 dBFS, unless otherwise noted.

Figure 17. POWER-SUPPLY REJECTION RATIO (100-mV<sub>PP</sub> Supply Noise with Different Frequencies)

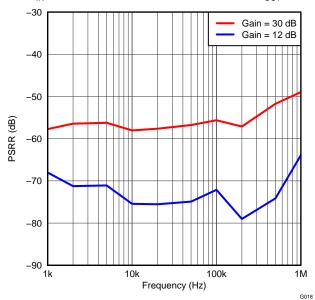

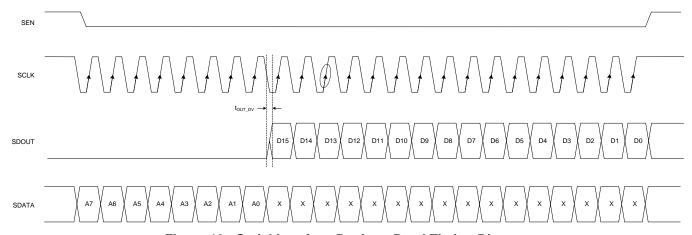

#### SERIAL REGISTER TIMING

#### SERIAL REGISTER WRITE DESCRIPTION

Programming different modes can be accomplished through the serial interface formed by the SEN (serial interface enable), SCLK (serial interface clock), SDATA (serial interface data), and RESET pins. Each of these pins has a  $20\text{-k}\Omega$  pull-down resistor to GND. Serially shifting bits into the device is enabled when SEN is low. SDATA serial data are latched at every SCLK rising edge when SEN is active (low). Serial data are loaded into the register at every 24th SCLK rising edge when SEN is low. If the word length exceeds a multiple of 24 bits, the excess bits are ignored. Data can be loaded in multiples of 24-bit words within a single active SEN pulse (an internal counter counts groups of 24 clocks after the SEN falling edge). The interface can function with SCLK frequencies from 20 MHz down to low speeds (of a few Hertz) and even with a non-50% duty cycle SCLK. Data are divided into two main portions to load on the addressed register: a register address (eight bits) and the actual data (16 bits). When writing to a register with unused bits, these bits should be set to '0'. Figure 18 shows a timing diagram of the write operation. Table 3 lists the serial interface timing characteristics.

Figure 18. Serial Interface Timing Diagram

Table 3. Serial Interface Timing Characteristics<sup>(1)</sup>

|                                    | PARAMETER                                             | MIN | TYP | MAX | UNIT |

|------------------------------------|-------------------------------------------------------|-----|-----|-----|------|

| t <sub>SCLK</sub>                  | SCLK period                                           | 50  |     |     | ns   |

| t <sub>SCLK_H</sub>                | SCLK high time                                        | 20  |     |     | ns   |

| t <sub>SCLK_L</sub>                | SCLK low time                                         | 20  |     |     | ns   |

| t <sub>DSU</sub>                   | Data setup time                                       | 5   |     |     | ns   |

| t <sub>DHO</sub>                   | Data hold time                                        | 5   |     |     | ns   |

| t <sub>SEN_SU</sub>                | SEN falling edge to SCLK rising edge                  | 8   |     |     | ns   |

| t <sub>SEN_HO</sub>                | Time between last SCLK rising edge to SEN rising edge | 8   |     |     | ns   |

| t <sub>OUT_DV</sub> <sup>(2)</sup> | Delay from SCLK falling edge to SDOUT valid           | 12  | 20  | 28  | ns   |

<sup>(1)</sup> Minimum values are across the full temperature range of  $T_{MIN} = -40$ °C to  $T_{MAX} = +85$ °C and AVDD = 3.3 V.

12

<sup>(2)</sup> See Figure 19.

#### REGISTER READOUT

The device includes an option where the contents of the internal registers can be read back. This readout may be useful as a diagnostic test to verify the serial interface communication between the external controller and the AFE. First, the REGISTER READOUT ENABLE bit (bit 1, register 00h) must be set to '1'. Then, initiate a serial interface cycle specifying the register address (A[7:0]) to be read. The data bits are *don't care*. The device outputs the contents (D[15:0]) of the selected register on the SDOUT pin. SDOUT has a typical 20-ns delay (t<sub>OUT\_DV</sub>) from the SCLK falling edge. For a lower speed SCLK, SDOUT can be latched on the SCLK rising edge. For a higher speed SCLK (for example, with an SCLK period less than 60 ns), latching SDOUT at the next SCLK falling edge is preferable. Figure 19 shows the read operation timing diagram (timing specifications follow the same information provided in Table 3). In readout mode, REGISTER READOUT ENABLE can still be accessed through SDATA, SCLK, and SEN. To enable serial register writes, set the REGISTER READOUT ENABLE bit back to '0'.

Figure 19. Serial Interface Register Read Timing Diagram

SBAS632 - OCTOBER 2013 www.ti.com

#### REGISTER MAP

A reset process is required at the device initialization stage. Initialization can be accomplished in one of two ways:

- 1. Through a hardware reset, by applying a positive pulse on the RESET pin, or

- 2. Through a software reset (using the serial interface), by setting the SW\_RESET bit high. Setting this bit initializes the internal registers to the respective default values (all '0's) and then self-resets the SW\_RESET bit low. In this case, the RESET pin can remain low (inactive).

After reset, all PGA registers are set to '0' (default). During register programming, all reserved or unlisted register bits must be set to '0'. Register settings are maintained when the device is in either partial or complete power-down mode. Table 4 lists the PGA register map.

|                   | 5 ,              |                  |                |           |           |           |           |       |       |       |       |       |       |       |       |                                              |          |

|-------------------|------------------|------------------|----------------|-----------|-----------|-----------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|----------------------------------------------|----------|

| REGISTER<br>(Hex) | DECIMAL<br>VALUE | Bit 15           | BIT 14         | BIT<br>13 | BIT<br>12 | BIT<br>11 | BIT<br>10 | BIT 9 | BIT 8 | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1                                        | BIT 0    |

| 00                | 0                | X <sup>(1)</sup> | Х              | х         | х         | х         | Х         | Х     | х     | Х     | Х     | х     | х     | х     | Х     | REGISTER<br>READOUT<br>ENABLE <sup>(2)</sup> | SW_RESET |

| 35                | 53               | COMPLETE<br>PDN  | PARTIAL<br>PDN | Х         | Х         | Х         | Х         | Х     | Х     | X     | Х     | Х     | Х     | Х     | Х     | X                                            | Х        |

| 3B                | 59               | X                | X              | Х         | Х         | Х         | Х         | Х     | Х     | LOW _ | Р     | GA_GA | IN    | х     | Х     | X                                            | Х        |

FILTER BW

Table 4. PGA Register Map

Submit Documentation Feedback Copyright © 2013, Texas Instruments Incorporated

<sup>(1)</sup> X = don't care.

Shaded cells indicate used bits.

### **Register Descriptions**

### Table 5. Register 00h

| 15 | 14 | 13 | 12 | 11 | 10 | 9                             | 8        |

|----|----|----|----|----|----|-------------------------------|----------|

| X  | X  | X  | X  | X  | X  | X                             | X        |

| 7  | 6  | 5  | 4  | 3  | 2  | 1                             | 0        |

| Х  | Х  | Х  | Х  | Х  | Х  | REGISTER<br>READOUT<br>ENABLE | SW_RESET |

Bits 15:2 Don't care

Default = 0.

Bit 1 REGISTER READOUT ENABLE

0 = Readout disabled (default)

1 = Register readout enabled at SDOUT pin

Bit 0 SW\_RESET

0 = Normal operation (default)

1 = Resets the device and self-clears the bit to '0'

### Table 6. Register 35h

| 15              | 14          | 13 | 12 | 11 | 10 | 9 | 8 |  |

|-----------------|-------------|----|----|----|----|---|---|--|

| COMPLETE<br>PDN | PARTIAL PDN | X  | X  | X  | X  | Х | X |  |

| 7               | 6           | 5  | 4  | 3  | 2  | 1 | 0 |  |

| X               | X           | X  | Х  | X  | Х  | Х | Х |  |

Bit 15 COMPLETE PDN

Bit 14 PARTIAL PDN

0 = Normal operation (default)1 = LNA and PGA powered down

Bits 13:0 Don't care

Default = 0.

SBAS632 – OCTOBER 2013 www.ti.com

|                   |    |          | Table 7. Register 3Bh |    |    |   |   |  |  |  |

|-------------------|----|----------|-----------------------|----|----|---|---|--|--|--|

| 15                | 14 | 13       | 14DIE 7. RE           | 11 | 10 | 9 | 8 |  |  |  |

| X                 | X  | X        | X                     | X  | X  | X | X |  |  |  |

| 7                 | 6  | 5        | 4                     | 3  | 2  | 1 | 0 |  |  |  |

| LOW_FILTER_<br>BW |    | PGA_GAIN |                       | х  | Х  | Х | Х |  |  |  |

Bits 15:8 Don't care

Default = 0.

Bit 7 LOW\_FILTER\_BW

0 = 75-MHz bandwidth (default)

1 = 60-MHz bandwidth

Bits 6:4 PGA\_GAIN

000 = 18-dB PGA gain (default)

001 = 15-dB PGA gain 010 = 12-dB PGA gain 011 = 9-dB PGA gain 100 = 6-dB PGA gain 101 = 3-dB PGA gain 110 = 0-dB PGA gain

Bits 3:0 Don't care

Default = 0.

#### **APPLICATION INFORMATION**

#### THEORY OF OPERATION

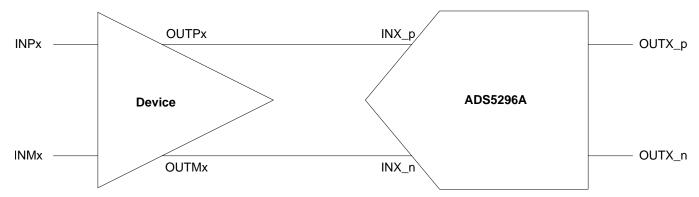

The PGA5807A is a programmable gain amplifier (PGA) for applications with input frequencies up to 25 MHz. The device includes a low-noise amplifier (LNA) with a fixed gain, followed by a PGA and an antialiasing filter to reduce noise. The LNA is a fully-differential amplifier with a 12-dB fixed gain and can support a 500-mV<sub>PP</sub> maximum linear differential input swing. The PGA is implemented as an attenuator followed by a fixed-gain amplifier with 18-dB gain. The attenuator can provide attenuation from 0 dB to -18 dB in 3-dB steps. The attenuator can be controlled by the GAIN[2:0] pins or by using register 3Bh (bits 6 to 4). The antialiasing filter is combined with the fixed-gain amplifier. The filter has one active pole and a passive pole for a combined bandwidth of 75 MHz. For low-frequency applications, bandwidth can be reduced to 60 MHz where better noise can be achieved. The device can be programmed in this mode either by using the SDATA pin while RESET is high or by using bit 7 of register 3Bh. This device can directly drive ADCs such as the ADS5296.

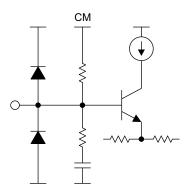

### Low-Noise Amplifier (LNA)

In most data-acquisition systems, an LNA is required at the front-end to obtain good noise performance. The PGA5807A has a fully-differential LNA with a 12-dB fixed gain. The LNA input-referred noise is 1.9 nV/ $\sqrt{\text{Hz}}$ , and supports a differential 500-mV<sub>PP</sub> input swing. The LNA input can be applied either directly or through an accoupling capacitor. Internally, the LNA input is connected to a 2.1-V common-mode voltage via a large resistor (8 k $\Omega$ ). For direct input coupling, the LNA supports an input common-mode range from 1.9 V to 2.3 V. The LNA input circuits are shown in Figure 20.

Figure 20. INP and INM Equivalent Circuits of LNA Inputs

SBAS632 – OCTOBER 2013 www.ti.com

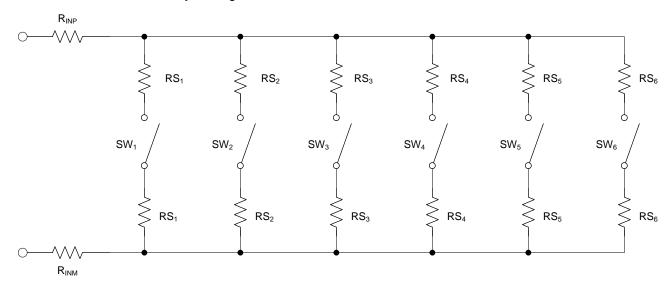

#### Programmable Gain Amplifier (PGA) and Filter

The LNA output is transmitted to a PGA with a programmable gain from 0 dB to 18 dB in 3-dB steps. This gain can either be controlled through a serial interface or through pins, as explained in the *Serial Register Write Description* section. The PGA is implemented as a programmable attenuator and as a fixed-gain amplifier with an 18-dB gain. This architecture helps achieve the same bandwidth across different gain settings. The attenuator provides programmable attenuation from 0 dB to 18 dB.

The attenuator architecture is shown in Figure 21. There are six shunt resistors that can be connected or disconnected to achieve programmable attenuation. The network provides 0-dB attenuation when no shunt resistors are connected. When the first shunt resistor ( $RS_1$ ) is turned on, an attenuation of 3 dB is obtained. For achieving 6-dB attenuation, both  $RS_1$  and  $RS_2$  are turned on. Similarly, by turning on additional resistors, greater attenuation can be achieved; by turning on all resistors, an effective 18-dB attenuation is achieved.

Figure 21. Programmable Attenuator

8 Submit Documentation Feedback

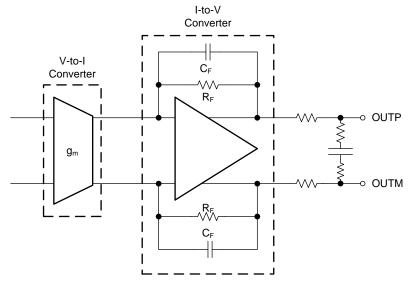

The attenuator is followed by a 18-dB fixed-gain amplifier. The amplifier is implemented as a voltage-to-current (V-to-I) converter followed by a current-to-voltage (I-to-V) converter. The I-to-V bandwidth is limited so that it functions as an LPF and is followed by a passive filter, as shown in Figure 22. Both the active and passive filters provide an antialiasing filter action, which helps reduce noise when the PGA output is sampled by an ADC. The architecture of the passive filter is selected to reduce the glitches that can occur when the PGA5807A output is sampled by an ADC. For example, the PGA5807A can be directly connected to ADC devices (such as the ADS5295 or ADS5296) without any external components between the ADC and PGA5807A. Figure 23 shows an example of the PGA5807A connected directly to the ADS5296.

Figure 22. Antialias Filter

Figure 23. PGA Connected to an ADC

#### DEVICE CONFIGURATION USING SERIAL INTERFACE OR PARALLEL PINS

Different device modes (such as channel gain and bandwidth) can be programmed by either using the serial interface or external pins. The device can be configured via the serial interface only when the device RESET pin is pulsed and remains low. In this configuration, device gain can be programmed through register 3Bh (bits 6 to 4) and bandwidth can be programmed by register 3Bh (bit 7). When the RESET pin is connected to 3.3 V or is pulled high, the serial interface is unable to control the device. In this configuration, the GAIN[2:0] pins can be used to control gain and the SDATA pin can be used to control bandwidth.

www.ti.com 11-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                 |                       |      | (4)                           | (5)                        |              |                  |

| PGA5807ARGCR          | Active | Production    | VQFN (RGC)   64 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | PGA5807          |

| PGA5807ARGCR.B        | Active | Production    | VQFN (RGC)   64 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | PGA5807          |

| PGA5807ARGCT          | Active | Production    | VQFN (RGC)   64 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | PGA5807          |

| PGA5807ARGCT.B        | Active | Production    | VQFN (RGC)   64 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-3-260C-168 HR        | -40 to 85    | PGA5807          |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-Mar-2024

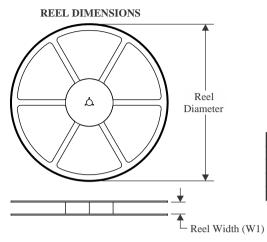

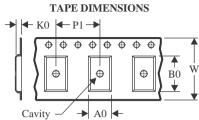

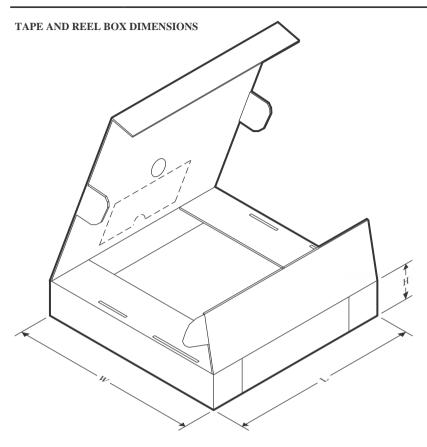

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

|   | Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| ĺ | PGA5807ARGCR | VQFN            | RGC                | 64 | 2000 | 330.0                    | 16.4                     | 9.3        | 9.3        | 1.5        | 12.0       | 16.0      | Q2               |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-Mar-2024

### \*All dimensions are nominal

| Device |              | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|--------|--------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

|        | PGA5807ARGCR | VQFN         | RGC             | 64   | 2000 | 350.0       | 350.0      | 43.0        |  |

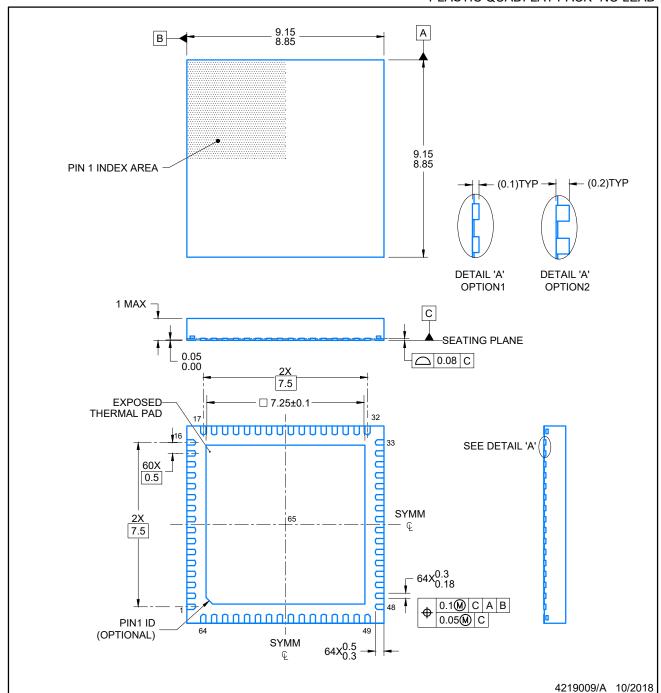

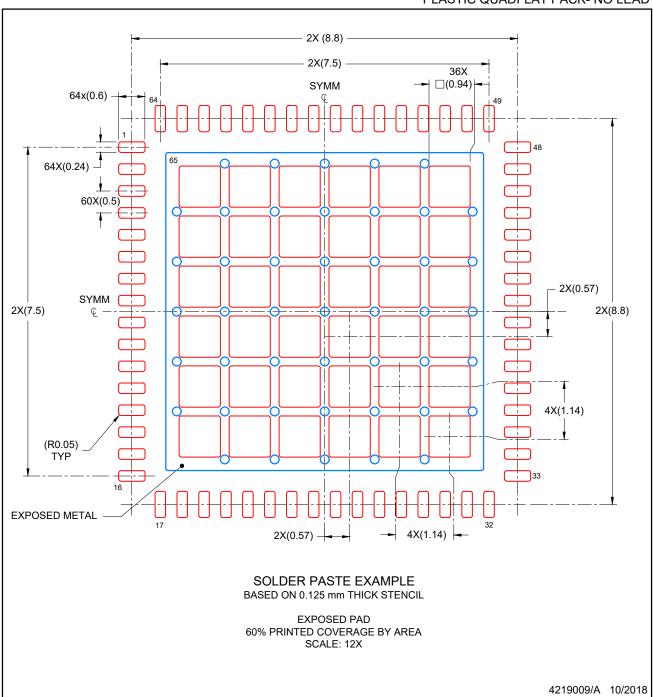

9 x 9, 0.5 mm pitch

PLASTIC QUAD FLATPACK - NO LEAD

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4224597/A

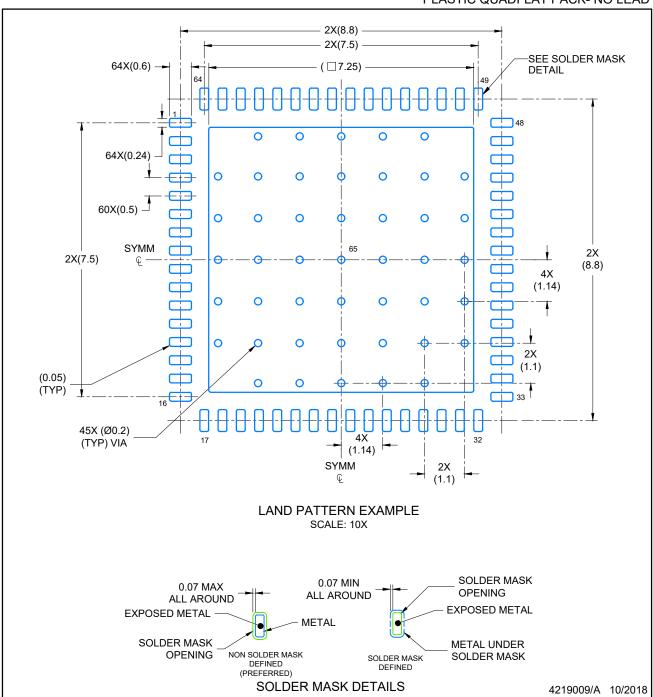

PLASTIC QUADFLAT PACK- NO LEAD

### NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

PLASTIC QUADFLAT PACK- NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUADFLAT PACK- NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025