## TPS2HC08-Q1 9.5mΩ Dual-Channel Automotive Smart High-Side Switch

### 1 Features

- Dual-Channel smart high-side switch with full diagnostics

- Control using GPIO pins

- Open-drain status output

- Current sense analog output: sense accuracy  $<\pm 4\%$  at  $\geq 1A$

- Wide operating voltage: 3V to 28V

- Low  $R_{ON}$ : 9.5mΩ typical, 16.5mΩ max at 150°C

- Ultra-low standby current:  $<1.4\mu A$  at 85°C

- Adjustable current limit with and without thermal regulation

- Current limit range: 7.5A to 25A

- Protection

- Overload and short-circuit protection

- Undervoltage lockout (UVLO)

- Thermal shutdown and swing with self recovery

- Integrated output clamp to demagnetize inductive loads

- Loss-of-GND, loss-of-battery, and reverse battery protection

- Diagnostics

- Global fault report for fast interrupt

- Overcurrent and short-to-ground detection

- Open-load and short-to-battery detection

- Qualified for automotive applications

- AEC-Q100 qualified with the following results:

- Temperature grade 1:  $-40^{\circ}C$  to  $125^{\circ}C$  ambient operating temperature range

- Passed electrical transient disturbance immunity tests (ISO7637-2 and ISO16750-2)

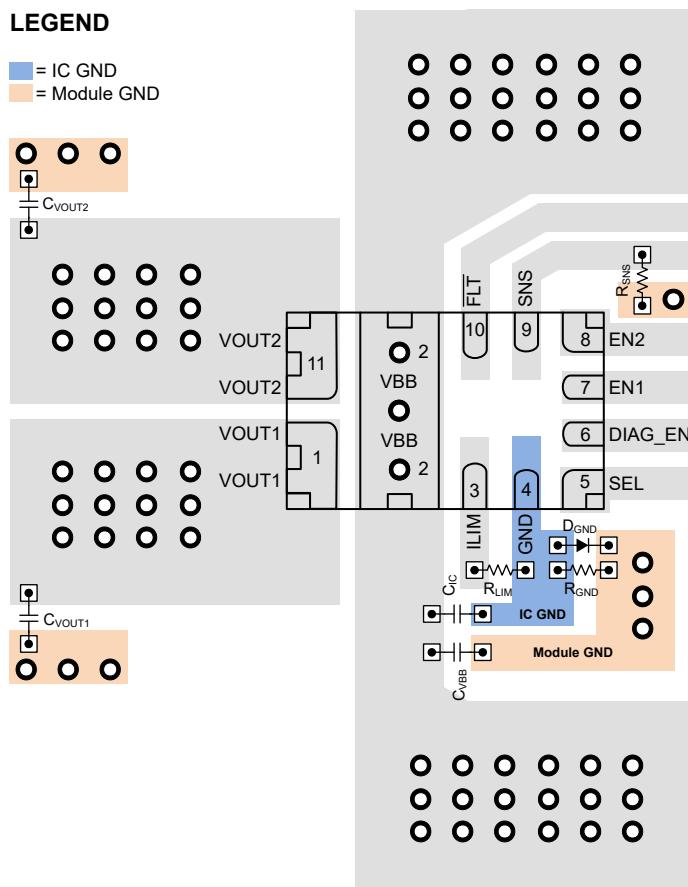

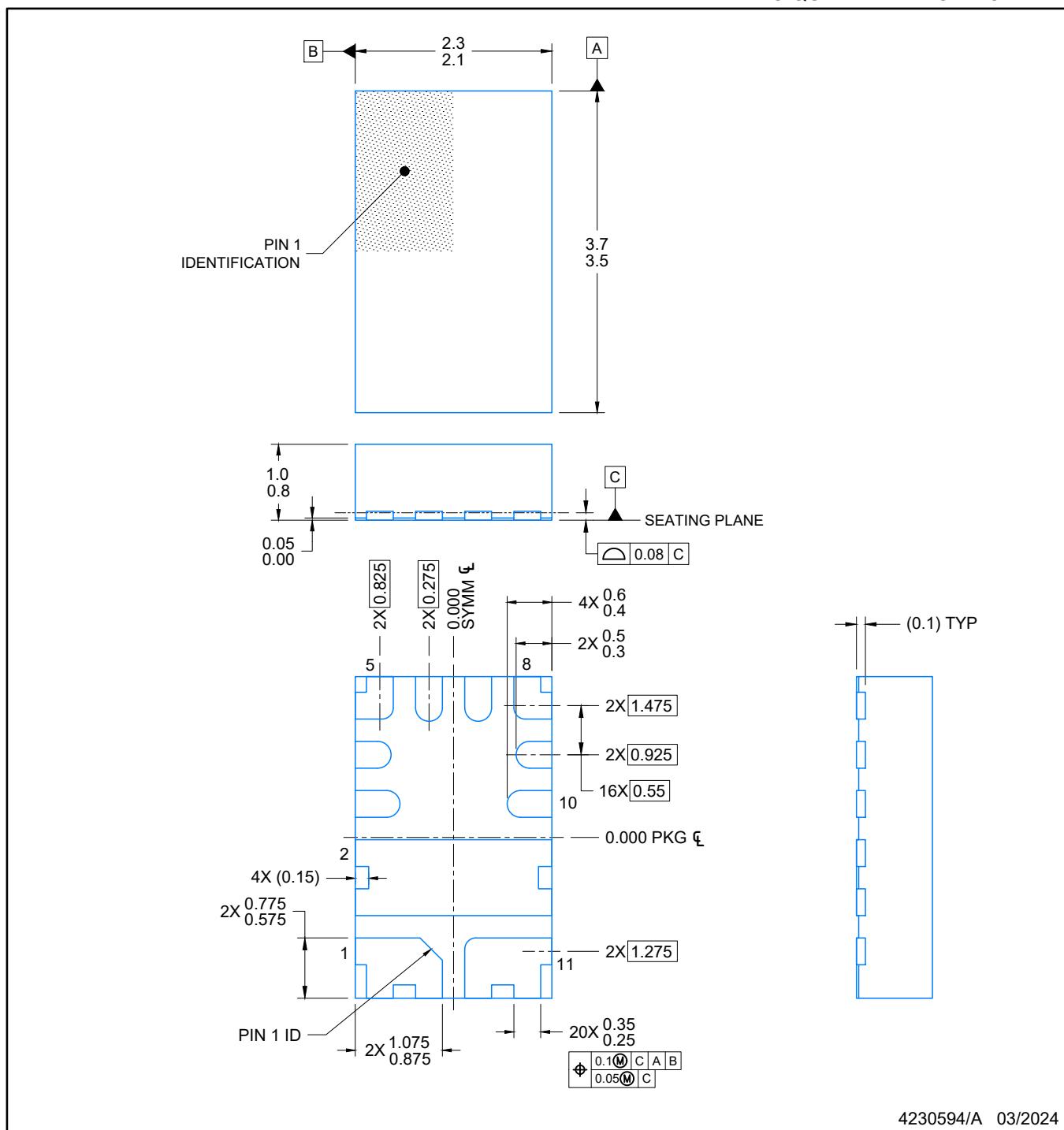

- Small footprint: 11-pin wettable flank VQFN-HR 2.2mm × 3.6mm, 0.55mm pitch

- **Functional Safety Capable**

- Documentation available to aid functional safety system design

### 2 Applications

- Zone control module

- Body control module

- Incandescent and LED lighting

- Front door module

- Seat heater

### 3 Description

TPS2HC08-Q1 is a dual-channel, smart high-side switch, with integrated NMOS power FETs and charge pump, designed for 12V automotive battery systems. The low on-resistance (9.5mΩ) minimizes device power dissipation when driving output load current up to 7.5A DC when both channels are enabled or 10A DC when only one channel is enabled.

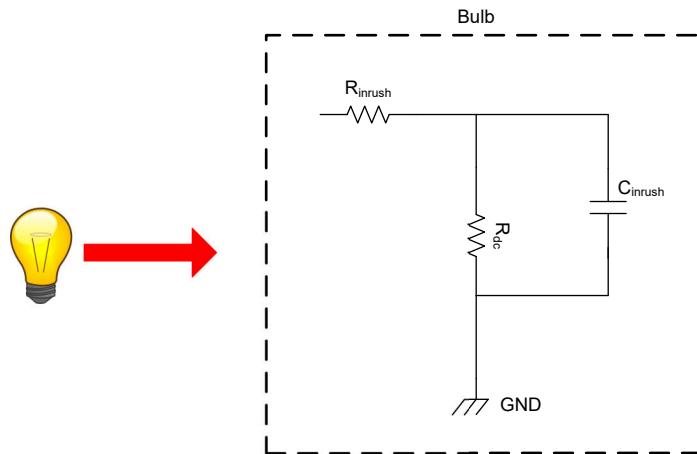

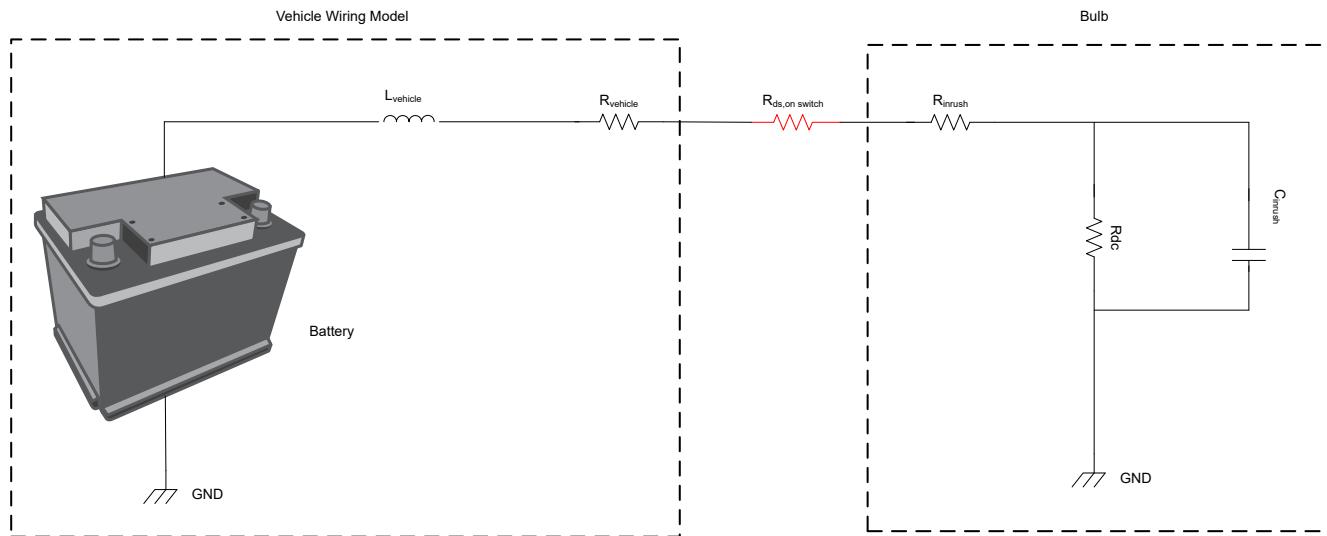

The device integrates protection features such as thermal shutdown, output clamp, and current limit. TPS2HC08-Q1 implements an adjustable current limiting circuit that improves the reliability of the system by reducing inrush current when driving large capacitive loads and minimizing overload current. The adjustable current limit can be adjusted from (7.5A to 25A) using an external resistor on the ILIM pin. The device offers both thermal-regulated current limiting for capacitive loads at startup and non-regulated current limiting for motor inrush or bulb applications.

The device also provides an accurate current sense that allows for improved load diagnostics such as overload and open-load detection, enabling better predictive maintenance. TPS2HC08-Q1 is available in a 11-pin, 2.2mm × 3.6mm VQFN-HR wettable-flank package with 0.55mm pitch, minimizing the PCB footprint.

#### Package Information

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| TPS2HC08-Q1 | VAH (VQFN-HR, 11)      | 2.2mm × 3.6mm               |

(1) See the orderable addendum at the end of the data sheet.

(2) The package size is a nominal value and includes pins.

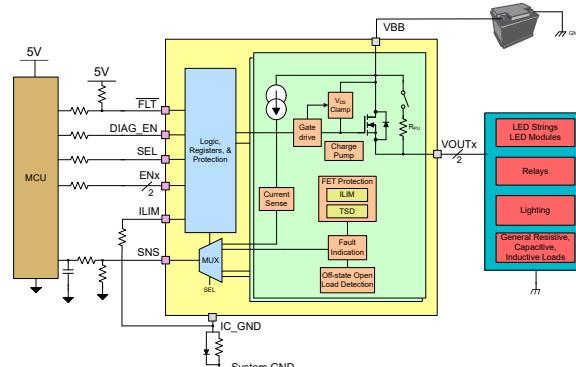

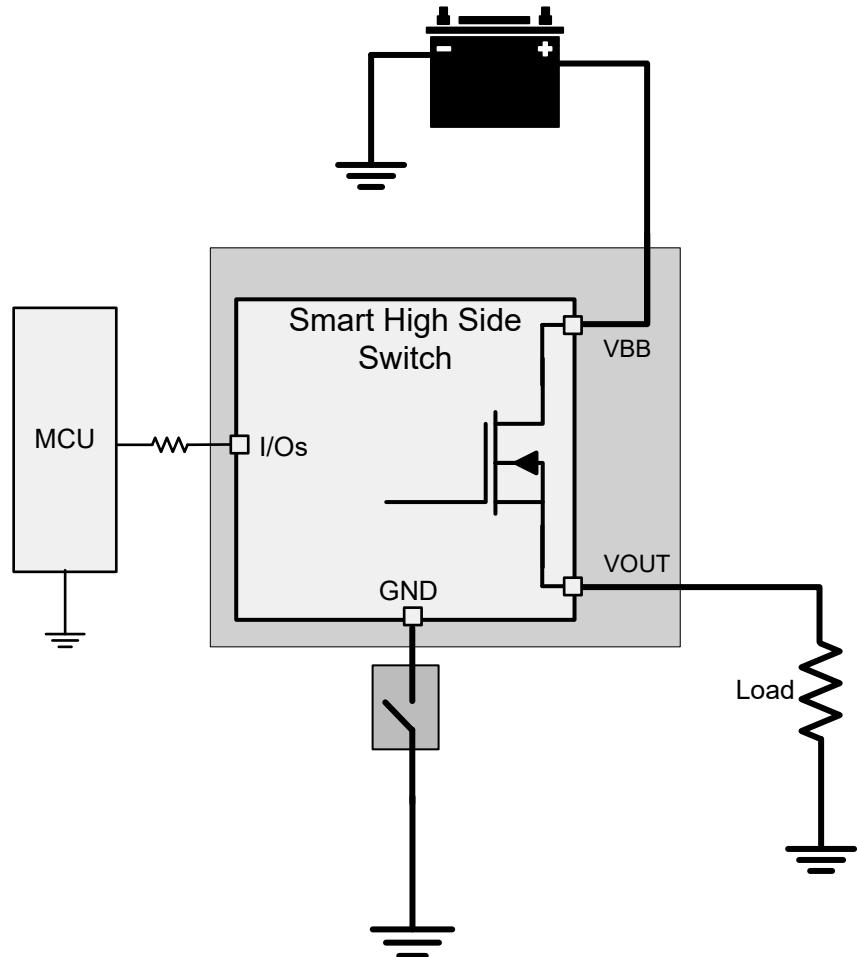

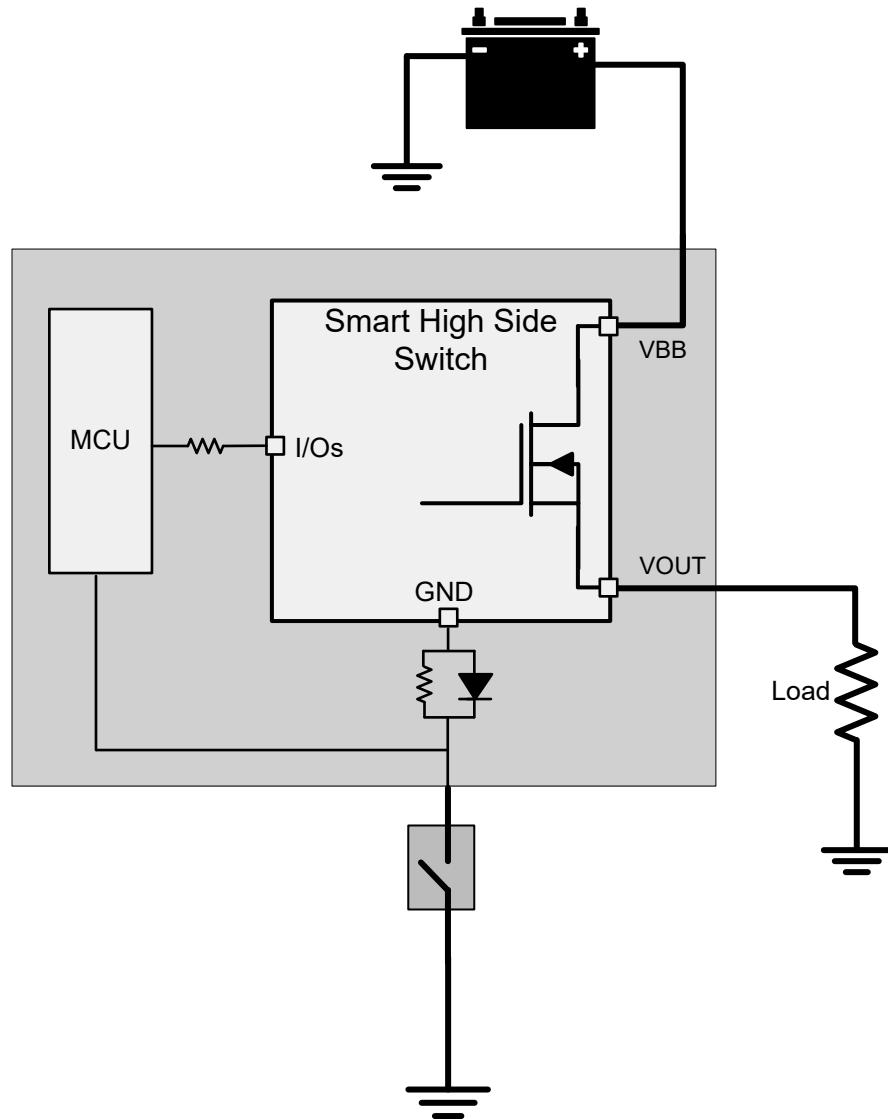

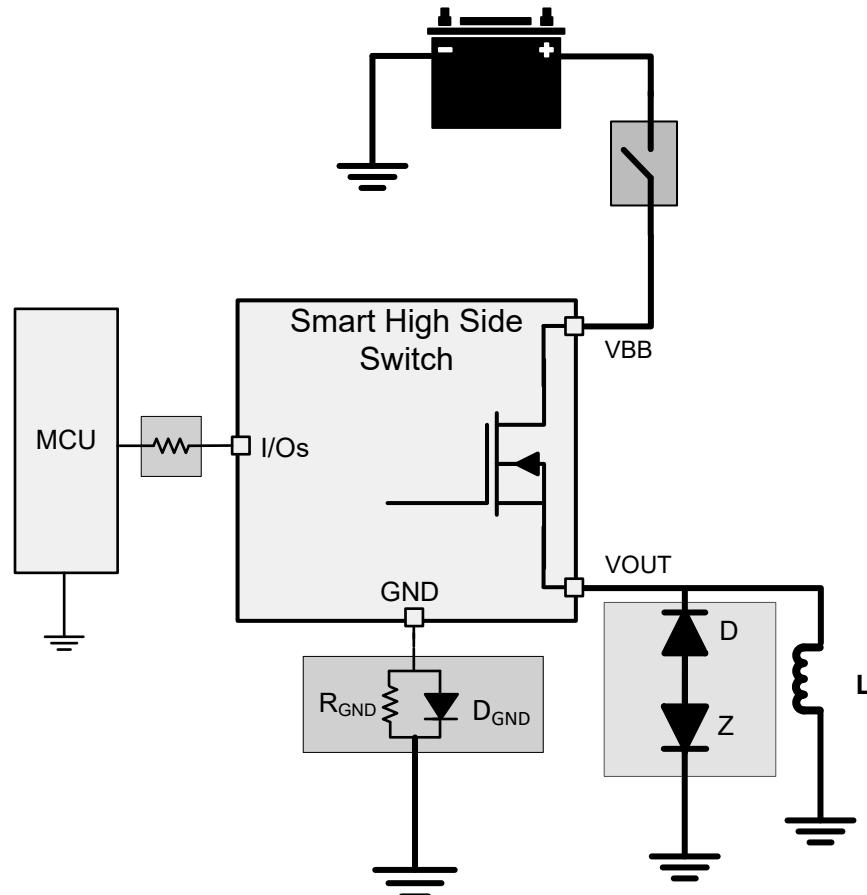

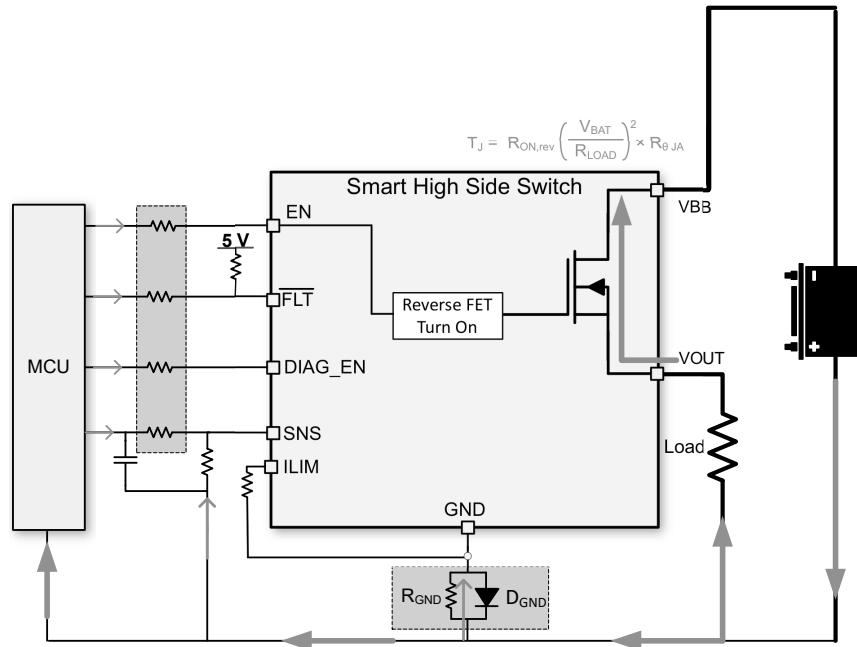

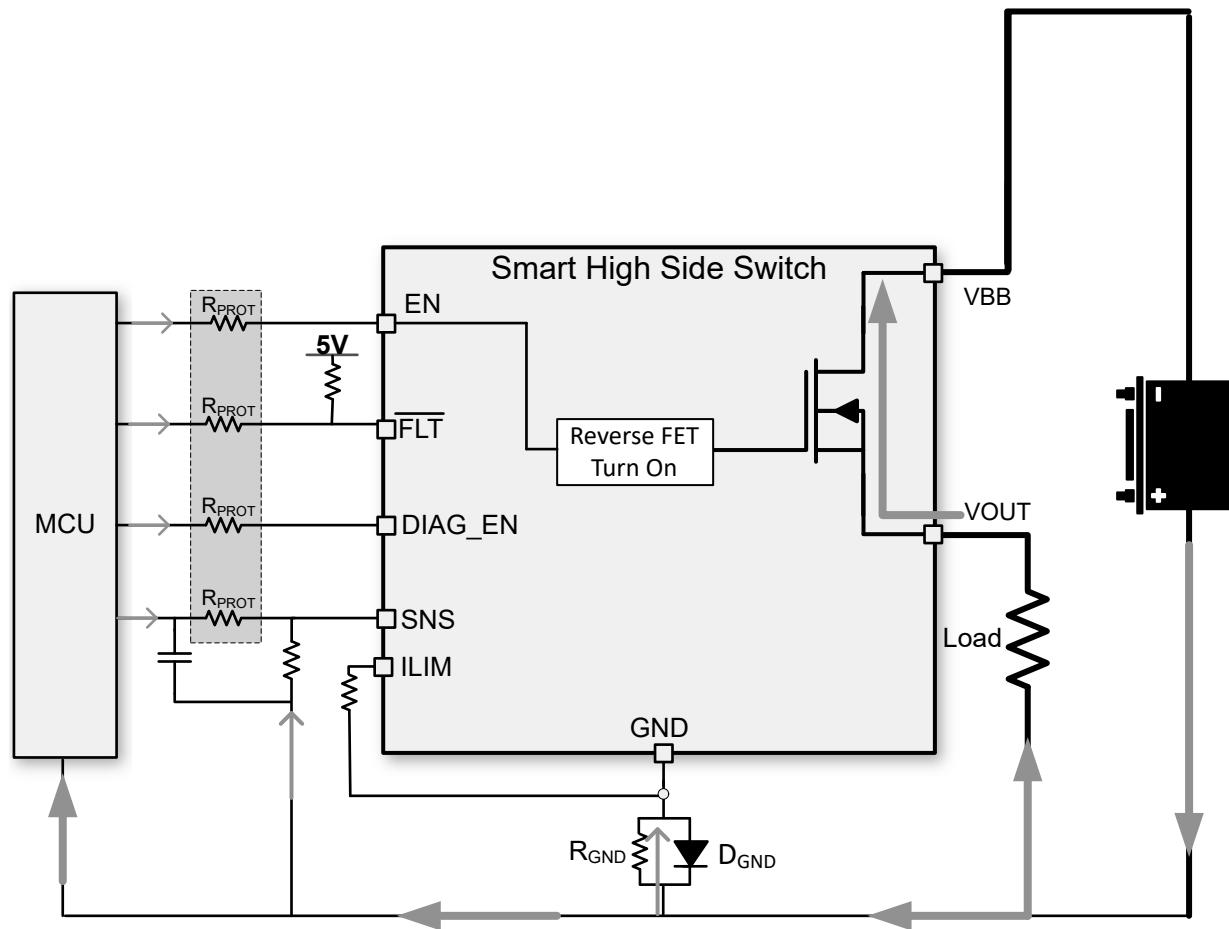

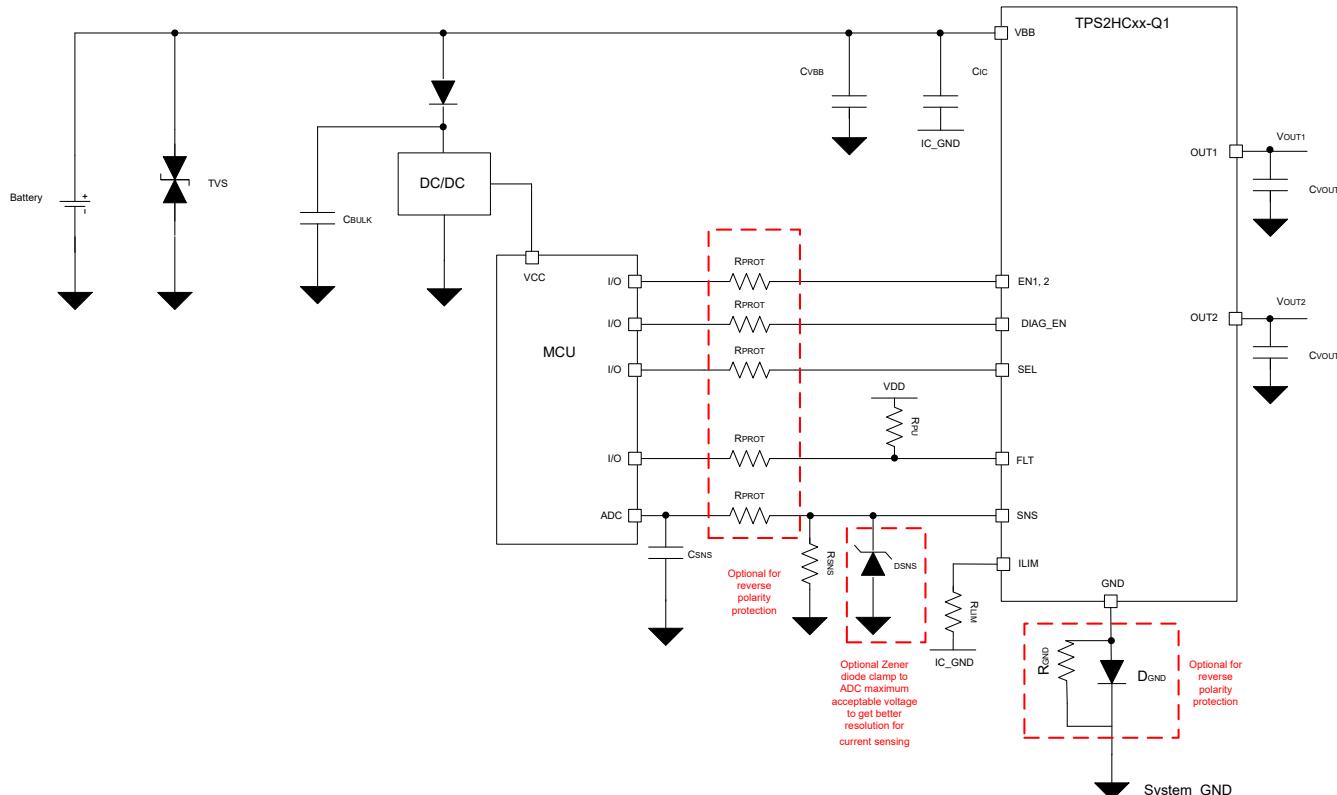

Typical Application Schematic

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## Table of Contents

|                                                  |           |                                                                            |           |

|--------------------------------------------------|-----------|----------------------------------------------------------------------------|-----------|

| <b>1 Features</b> .....                          | <b>1</b>  | 8.3 Feature Description.....                                               | <b>20</b> |

| <b>2 Applications</b> .....                      | <b>1</b>  | 8.4 Device Functional Modes.....                                           | <b>56</b> |

| <b>3 Description</b> .....                       | <b>1</b>  | <b>9 Application and Implementation</b> .....                              | <b>58</b> |

| <b>4 Device Comparison Table</b> .....           | <b>3</b>  | 9.1 Application Information.....                                           | <b>58</b> |

| <b>5 Pin Configuration and Functions</b> .....   | <b>4</b>  | 9.2 Typical Application.....                                               | <b>58</b> |

| <b>6 Specifications</b> .....                    | <b>5</b>  | 9.3 Power Supply Recommendations.....                                      | <b>63</b> |

| 6.1 Absolute Maximum Ratings.....                | 5         | 9.4 Layout.....                                                            | <b>63</b> |

| 6.2 ESD Ratings.....                             | 5         | <b>10 Device and Documentation Support</b> .....                           | <b>67</b> |

| 6.3 Recommended Operating Conditions.....        | 5         | 10.1 Third-Party Products Disclaimer.....                                  | <b>67</b> |

| 6.4 Thermal Information.....                     | 6         | 10.2 Receiving Notification of Documentation Updates.....                  | <b>67</b> |

| 6.5 Electrical Characteristics.....              | 6         | 10.3 Support Resources.....                                                | <b>67</b> |

| 6.6 SNS Timing Characteristics.....              | 9         | 10.4 Trademarks.....                                                       | <b>67</b> |

| 6.7 Switching Characteristics.....               | 10        | 10.5 Electrostatic Discharge Caution.....                                  | <b>67</b> |

| 6.8 Typical Characteristics.....                 | 11        | 10.6 Glossary.....                                                         | <b>67</b> |

| <b>7 Parameter Measurement Information</b> ..... | <b>17</b> | <b>11 Revision History</b> .....                                           | <b>67</b> |

| <b>8 Detailed Description</b> .....              | <b>18</b> | <b>12 Mechanical, Packaging, and Orderable</b><br><b>Information</b> ..... | <b>68</b> |

| 8.1 Overview.....                                | 18        |                                                                            |           |

| 8.2 Functional Block Diagram.....                | 19        |                                                                            |           |

## 4 Device Comparison Table

TPS2HC08-Q1 is part of a high current, smart high-side switch family, which has multiple device versions. The following tables shows the details of the versions and which versions are going to be available for each device.

**Table 4-1. Version Table**

| VERSION <sup>(2)</sup> | SLEW RATE          | OPEN LOAD DETECTION DELAY |

|------------------------|--------------------|---------------------------|

| P                      | Nominal (0.45V/μs) | 0.4ms delay               |

| M <sup>(1)</sup>       | Nominal (0.45V/μs) | 2.4ms delay               |

| D <sup>(1)</sup>       | Slow (0.06V/μs)    | 0.4ms delay               |

| B <sup>(1)</sup>       | Slow (0.06V/μs)    | 2.4ms delay               |

(1) Device in preview. Please contact TI for more information.

(2) All versions are GPIO controlled.

**Table 4-2. Device Comparison Table**

| PART NUMBER | PLANNED VERSIONS | NUMBER OF CHANNELS | ON-RESISTANCE at 25°C | ADJUSTABLE CURRENT LIMIT RANGE | OVERCURRENT BEHAVIOR                                                                                                                                                                                               |

|-------------|------------------|--------------------|-----------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPS2HC08-Q1 | P, D, M, B       | 2                  | 9.5mΩ                 | 7.5A - 25A                     |                                                                                                                                                                                                                    |

| TPS2HC16-Q1 | P, M             | 2                  | 18.7mΩ                | 5A - 15A                       |                                                                                                                                                                                                                    |

| TPS1HC08-Q1 | P, D, M          | 1                  | 9.8mΩ                 | 10A - 20A                      |                                                                                                                                                                                                                    |

| TPS1HC04-Q1 | P, D             | 1                  | 4.9mΩ                 | 15A - 48A                      |                                                                                                                                                                                                                    |

| TPS1HC03-Q1 | P, D, M          | 1                  | 3.2mΩ                 | 20A - 55A                      |                                                                                                                                                                                                                    |

| TPS1HC16-Q1 | P                | 1                  | 16mΩ                  | 7A - 14A                       |                                                                                                                                                                                                                    |

| TPS2HC30-Q1 | P                | 2                  | 30mΩ                  | 3.5A - 11A                     | <ul style="list-style-type: none"> <li>• Current limiting with thermal regulation when external resistor is used on ILIM pin</li> <li>• Current limiting with no thermal regulation when ILIM pin = GND</li> </ul> |

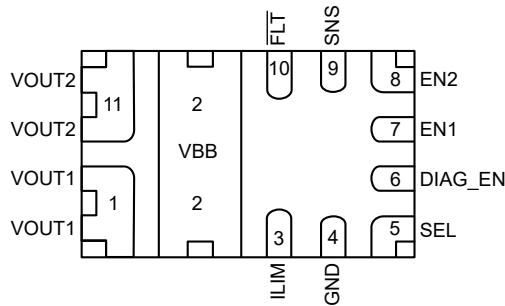

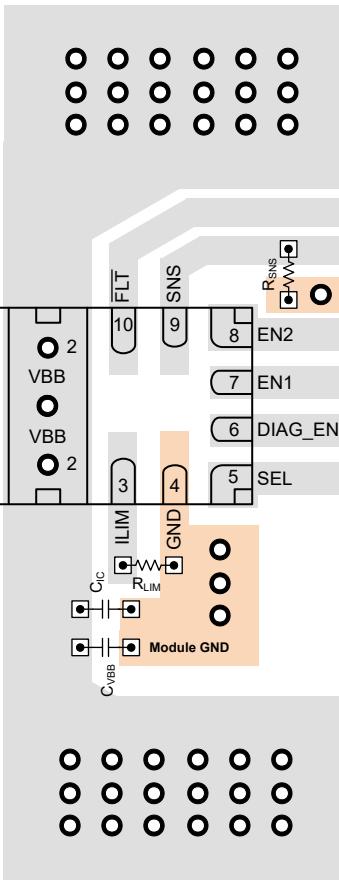

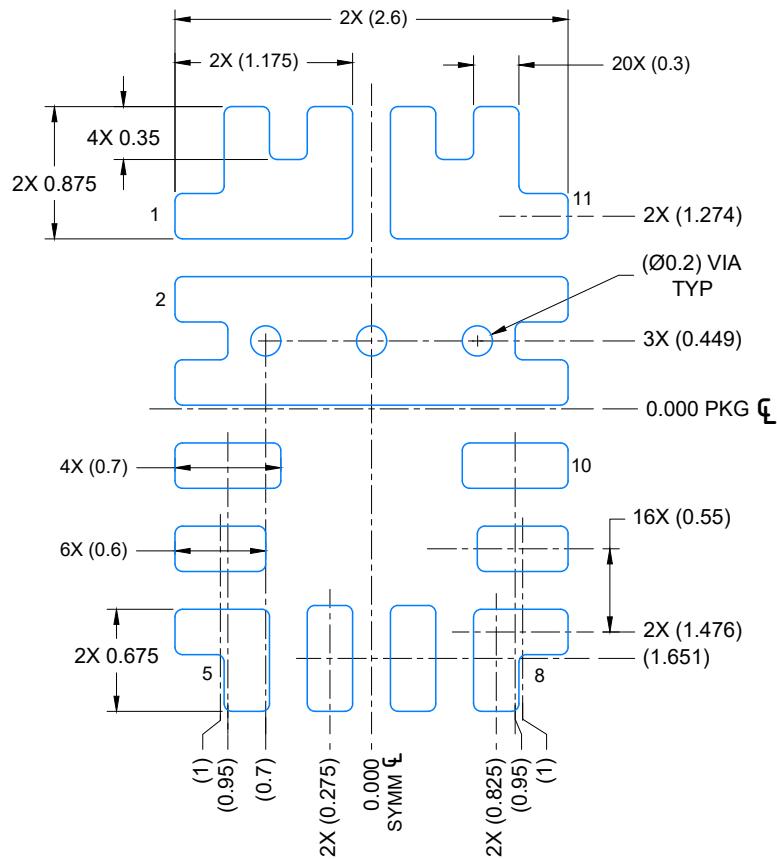

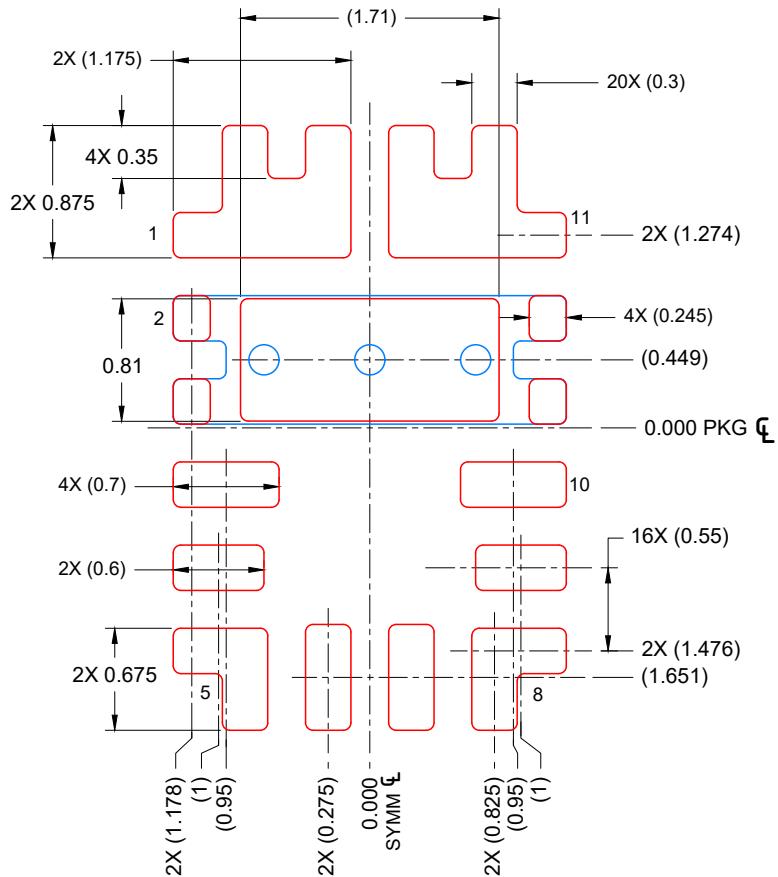

## 5 Pin Configuration and Functions

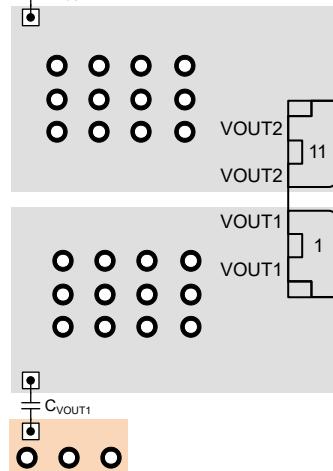

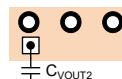

**Figure 5-1. VAH (VQFN-HR-11 Package, TPS2HC08-Q1 (top view)**

**Table 5-1. Pin Functions**

| PIN |                  | TYPE   | DESCRIPTION                                                                                                                                            |

|-----|------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME             |        |                                                                                                                                                        |

| 1   | VOUT1            | Power  | Channel 1 output, connect to load.                                                                                                                     |

| 2   | VBB              | Power  | Power supply.                                                                                                                                          |

| 3   | ILIM             | Output | Adjustable current limit. Connect $R_{LIM}$ to GND to set the current limit.                                                                           |

| 4   | GND              | Power  | Ground of device. Connect to resistor-diode ground network to have reverse battery protection.                                                         |

| 5   | SEL              | Input  | Selects the channel to output on the SNS pin.                                                                                                          |

| 6   | DIAG_EN          | Input  | Enable-disable pin for diagnostics, internal pulldown.                                                                                                 |

| 7   | EN1              | Input  | Input control for channel 1 activation, internal pulldown.                                                                                             |

| 8   | EN2              | Input  | Input control for channel 2 activation, internal pulldown.                                                                                             |

| 9   | SNS              | Output | Analog current sense output corresponding to load current. Connect $R_{SNS}$ to ground to convert to a voltage. Also shows fault status by going high. |

| 10  | $\overline{FLT}$ | Output | Open drain global fault output. Referred to FAULT, FLT, or fault pin.                                                                                  |

| 11  | VOUT2            | Power  | Channel 2 output, connect to load.                                                                                                                     |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                     |                                                                                                                                         | MIN               | MAX             | UNIT |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|------|

| Maximum continuous supply voltage, V <sub>BB</sub>  |                                                                                                                                         | 28                |                 | V    |

| Load dump voltage, V <sub>LD</sub>                  | ISO16750-2:2010(E)                                                                                                                      | 35                |                 | V    |

| Reverse Polarity Voltage                            | Maximum duration of 3 minutes and with the application circuit                                                                          | -18               |                 | V    |

| Enable pin current, I <sub>ENx</sub>                |                                                                                                                                         | -1                | 20              | mA   |

| Enable pin voltage, V <sub>ENx</sub>                |                                                                                                                                         | -1                | 7               | V    |

| Diagnostic Enable pin current, I <sub>DIAG_EN</sub> |                                                                                                                                         | -1                | 20              | mA   |

| Diagnostic Enable pin voltage, V <sub>DIAG_EN</sub> |                                                                                                                                         | -1                | 7               | V    |

| SEL pin current, I <sub>SEL</sub>                   |                                                                                                                                         | -1                | 20              | mA   |

| SEL pin voltage, V <sub>SEL</sub>                   |                                                                                                                                         | -1                | 7               | V    |

| Sense pin current, I <sub>SNS</sub>                 |                                                                                                                                         | -150              | 10              | mA   |

| FLT pin current, I <sub>FLT</sub>                   |                                                                                                                                         | -30               | 10              | mA   |

| FLT pin voltage, V <sub>FLT</sub>                   |                                                                                                                                         | -0.3              | V <sub>BB</sub> | V    |

| ILIM pin current, I <sub>ILIM</sub>                 |                                                                                                                                         | -30               | 10              | mA   |

| ILIM pin voltage, V <sub>ILIM</sub>                 |                                                                                                                                         | -0.3              | V <sub>BB</sub> | V    |

| Reverse ground current, I <sub>GND</sub>            | V <sub>BB</sub> < 0V                                                                                                                    | -50               |                 | mA   |

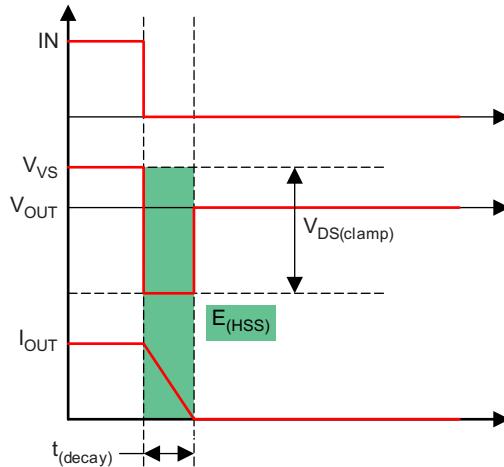

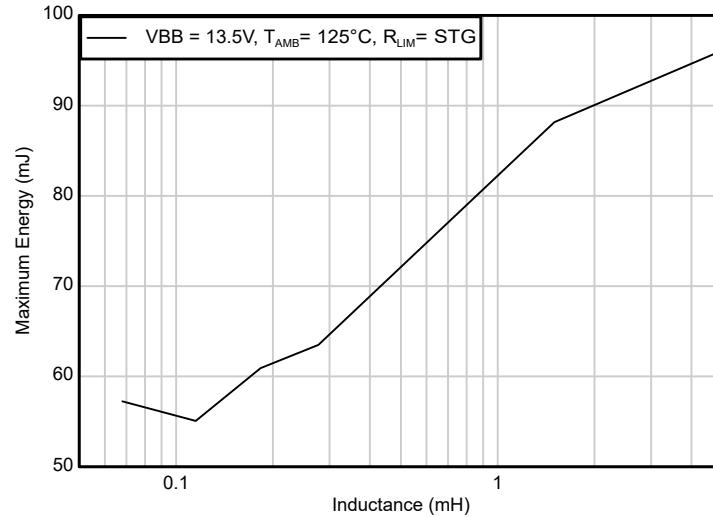

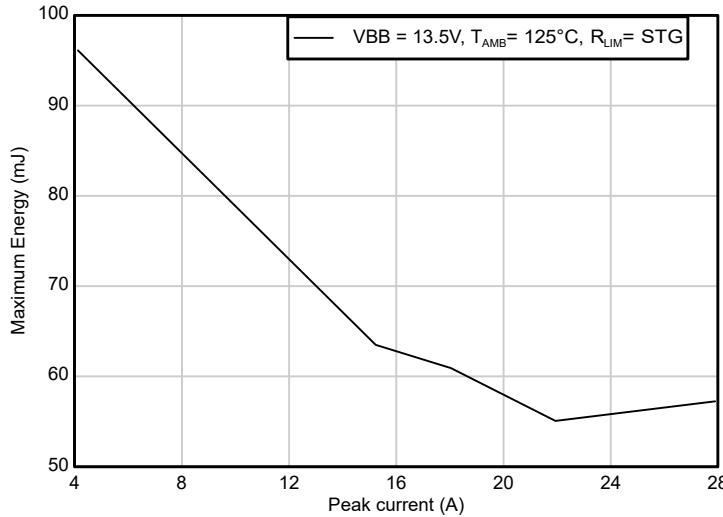

| Energy dissipation during turnoff, E <sub>AS</sub>  | Single pulse, one channel, V <sub>BB</sub> = 13.5V, I <sub>OUT</sub> = 5mH, T <sub>J,start</sub> = 125°C, nominal slew rate (version P) | 96 <sup>(2)</sup> |                 | mJ   |

| Energy dissipation during turnoff, E <sub>AR</sub>  | Repetitive pulse, one channel, 13.5V, I <sub>OUT</sub> = 10A, T <sub>J,start</sub> = 125°C, nominal slew rate (version P)               | 13 <sup>(2)</sup> |                 | mJ   |

| Maximum junction temperature, T <sub>J</sub>        |                                                                                                                                         | 150               |                 | °C   |

| Storage temperature, T <sub>stg</sub>               |                                                                                                                                         | -65               | 150             | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) For further details, see the section regarding switch-off of an inductive load.

### 6.2 ESD Ratings

|                    |                                           |                                                                                   | VALUE                                                | UNIT  |

|--------------------|-------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------|-------|

| V <sub>(ESD)</sub> | Electrostatic<br>discharge <sup>(1)</sup> | Human-body model (HBM), per AEC Q100-002<br>Classification Level 2 <sup>(2)</sup> | All pins except V <sub>BB</sub> and V <sub>OUT</sub> | ±2000 |

|                    |                                           |                                                                                   | V <sub>BB</sub> and V <sub>OUT</sub>                 | ±4000 |

|                    |                                           | Charged-device model (CDM), per AEC Q100-011<br>Classification Level C5           | All pins                                             | ±750  |

(1) All ESD strikes are with reference from the pin mentioned to GND

(2) AEC-Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specifications.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                      |                                        | MIN | MAX | UNIT |

|----------------------|----------------------------------------|-----|-----|------|

| V <sub>VBB_NOM</sub> | Nominal supply voltage <sup>(1)</sup>  | 4   | 18  | V    |

| V <sub>VBB_EXT</sub> | Extended supply voltage <sup>(2)</sup> | 3   | 28  | V    |

## 6.3 Recommended Operating Conditions (continued)

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                      |                                         | MIN | MAX | UNIT |

|----------------------|-----------------------------------------|-----|-----|------|

| V <sub>VBB_SC</sub>  | Short circuit supply voltage capability |     | 24  | V    |

| V <sub>ENx</sub>     | Enable voltage                          | -1  | 5.5 | V    |

| V <sub>DIAG_EN</sub> | Diagnostic Enable voltage               | -1  | 5.5 | V    |

| V <sub>SEL</sub>     | Select voltage                          | -1  | 5.5 | V    |

| V <sub>SNS</sub>     | Sense voltage                           | -1  | 5.5 | V    |

| T <sub>A</sub>       | Operating free-air temperature          | -40 | 125 | °C   |

(1) All operating voltage conditions are measured with respect to device GND

(2) Device will function within extended operating range, however some timing parametric values might not apply. See the respective sections for what voltages are used. Additionally more explanation can be found in [Power Supply Recommendations](#)

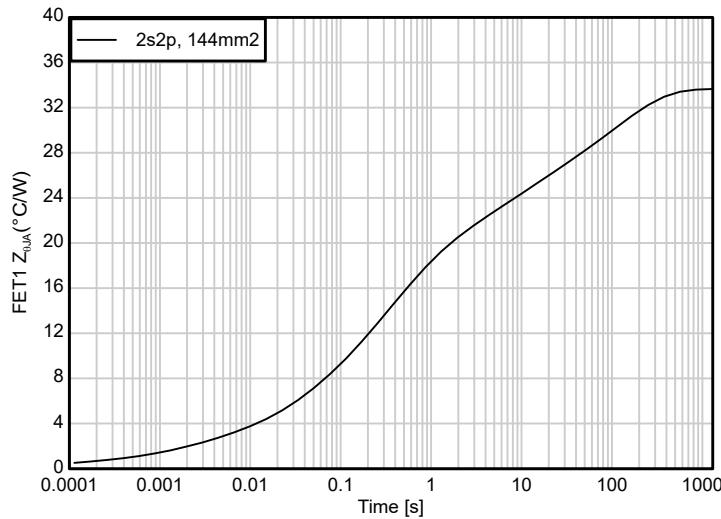

## 6.4 Thermal Information

| THERMAL METRIC <sup>(1) (2)</sup> |                                              | TPS2HC08-Q1 | UNIT |

|-----------------------------------|----------------------------------------------|-------------|------|

|                                   |                                              | VAH         |      |

|                                   |                                              | 11 PINS     |      |

| R <sub>θJA</sub>                  | Junction-to-ambient thermal resistance       | 41.6        | °C/W |

| R <sub>θJC(top)</sub>             | Junction-to-case (top) thermal resistance    | 37.3        | °C/W |

| R <sub>θJB</sub>                  | Junction-to-board thermal resistance         | 9.3         | °C/W |

| Ψ <sub>JT</sub>                   | Junction-to-top characterization parameter   | 1.9         | °C/W |

| Ψ <sub>JB</sub>                   | Junction-to-board characterization parameter | 9.3         | °C/W |

| R <sub>θJC(bot)</sub>             | Junction-to-case (bottom) thermal resistance | 9.8         | °C/W |

(1) For more information about traditional and new thermal metrics, see the [SPRA953](#) application report.

(2) The thermal parameters are based on a 4-layer PCB according to the JESD51-5 and JESD51-7 standards.

## 6.5 Electrical Characteristics

V<sub>BB</sub> = 6V to 18V, T<sub>J</sub> = -40°C to 150°C (unless otherwise noted); Typical application is V<sub>BB</sub> = 13.5V, R<sub>LIM</sub> = Open (unless otherwise specified)

| PARAMETER                        | TEST CONDITIONS                                |                                                                   | MIN                               | TYP  | MAX  | UNIT |   |

|----------------------------------|------------------------------------------------|-------------------------------------------------------------------|-----------------------------------|------|------|------|---|

| <b>INPUT VOLTAGE AND CURRENT</b> |                                                |                                                                   |                                   |      |      |      |   |

| V <sub>UVLOR</sub>               | V <sub>BB</sub> undervoltage lockout           | Measured with respect to device GND pin                           | V <sub>BB</sub> rising threshold  | 3.7  | 3.85 | 4.0  | V |

| V <sub>UVLOF</sub>               |                                                |                                                                   | V <sub>BB</sub> falling threshold | 2.8  | 2.9  | 3.0  | V |

| V <sub>DET1</sub>                | V <sub>BB</sub> detection 1 threshold          | Active, diagnostic, or standby state                              | V <sub>BB</sub> rising threshold  | 19   | 20.5 | 22.5 | V |

|                                  |                                                |                                                                   | V <sub>BB</sub> falling threshold | 18.4 | 19.5 | 20.7 | V |

| V <sub>DET2</sub>                | V <sub>BB</sub> detection 2 threshold          | active state                                                      | V <sub>BB</sub> rising threshold  | 24.5 | 26   | 28   | V |

|                                  |                                                |                                                                   | V <sub>BB</sub> falling threshold | 22.5 | 24   | 26   | V |

| V <sub>HV_R</sub>                | V <sub>BB</sub> high voltage wake-up threshold | V <sub>BB</sub> voltage to transition from sleep to standby state | V <sub>BB</sub> rising threshold  | 20.9 | 25   | 28.1 | V |

| V <sub>HV_F</sub>                | V <sub>BB</sub> high voltage wake-up threshold | V <sub>BB</sub> voltage to transition from standby to sleep state | V <sub>BB</sub> falling threshold | 18   |      |      | V |

| V <sub>Clamp</sub>               | VDS clamp voltage                              | V <sub>BB</sub> ≥ V <sub>DET1</sub>                               | T <sub>J</sub> = 25°C             | 35   | 37   |      | V |

|                                  |                                                |                                                                   | T <sub>J</sub> = -40°C to 150°C   | 31   | 42   |      | V |

|                                  |                                                | V <sub>BB</sub> < V <sub>DET1</sub>                               | T <sub>J</sub> = -40°C to 150°C   | 24   | 35   |      | V |

## 6.5 Electrical Characteristics (continued)

$V_{BB} = 6V$  to  $18V$ ,  $T_J = -40^{\circ}C$  to  $150^{\circ}C$  (unless otherwise noted); Typical application is  $V_{BB} = 13.5V$ ,  $R_{LIM} = \text{Open}$  (unless otherwise specified)

| PARAMETER        |                                                                       | TEST CONDITIONS                                                         |                      | MIN | TYP  | MAX | UNIT    |

|------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------|-----|------|-----|---------|

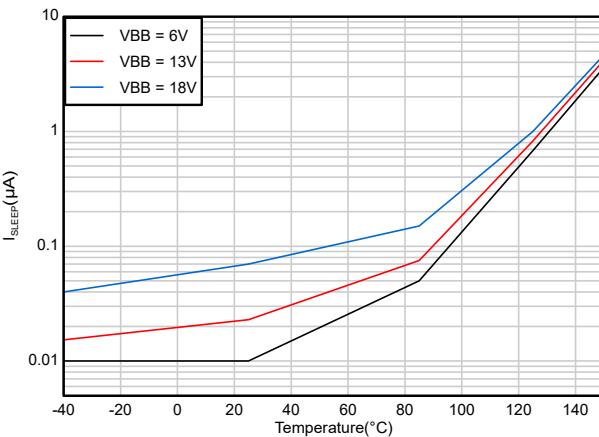

| $I_{SLEEP}$      | Standby current (total device leakage including both MOSFET channels) | $V_{ENx} = V_{DIAG\_EN} = 0V$ , $V_{OUT} = 0V$                          | $T_J = 25^{\circ}C$  |     |      | 1.2 | $\mu A$ |

|                  |                                                                       |                                                                         | $T_J = 85^{\circ}C$  |     |      | 1.4 | $\mu A$ |

|                  |                                                                       |                                                                         | $T_J = 150^{\circ}C$ |     |      | 12  | $\mu A$ |

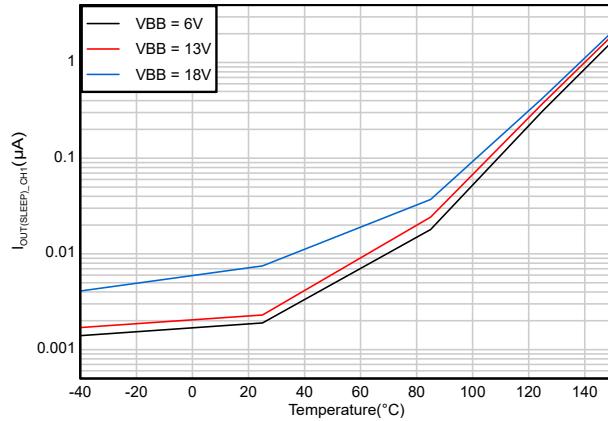

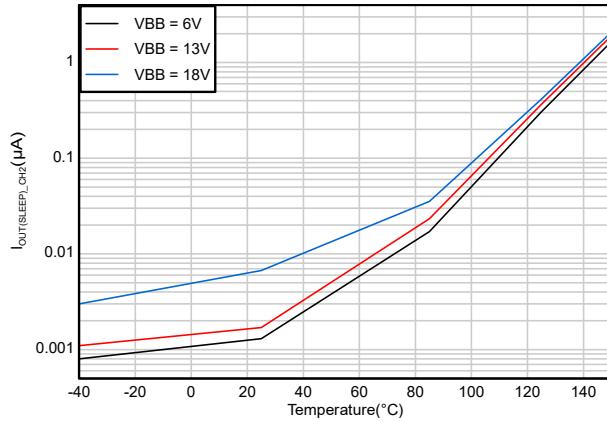

| $I_{OUT(SLEEP)}$ | Output leakage current per channel                                    | $V_{EN} = V_{DIAG\_EN} = 0V$ , $V_{OUT} = 0V$                           | $T_J = 25^{\circ}C$  |     | 0.01 | 0.5 | $\mu A$ |

|                  |                                                                       |                                                                         | $T_J = 85^{\circ}C$  |     |      | 0.7 | $\mu A$ |

|                  |                                                                       |                                                                         | $T_J = 150^{\circ}C$ |     |      | 6   | $\mu A$ |

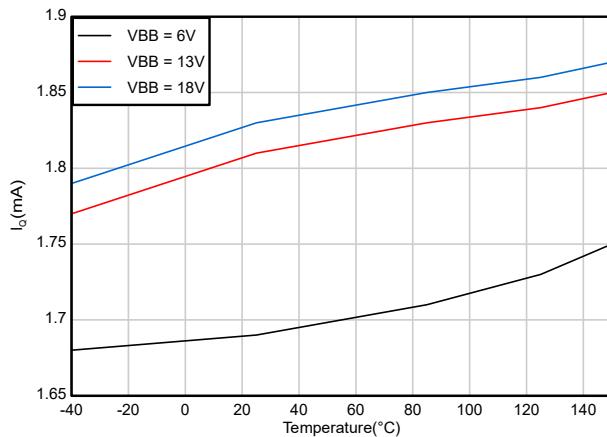

| $I_{DIAG}$       | Diagnostic state current consumption                                  | $V_{ENx} = 5V$ , $V_{DIAG\_EN} = 0V$ , $V_{OUT} = 0V$ , $I_{SNS} = 0mA$ |                      |     | 1.9  | 2.4 | mA      |

|                  |                                                                       | $V_{ENx} = 0V$ , $V_{DIAG\_EN} = 5V$ , $V_{OUT} = 0V$ , $I_{SNS} = 0mA$ |                      |     | 1.9  | 2.4 | mA      |

| $I_{Q\_1CH}$     | Quiescent current, one channel enabled                                | $V_{EN} = V_{DIA\_EN} = 5V$ , $I_{OUT} = 0A$                            |                      |     |      | 3   | mA      |

| $I_Q$            | Quiescent current both channels enabled                               | $V_{EN} = V_{DIA\_EN} = 5V$ , $I_{OUT} = 0A$                            |                      |     |      | 3.2 | mA      |

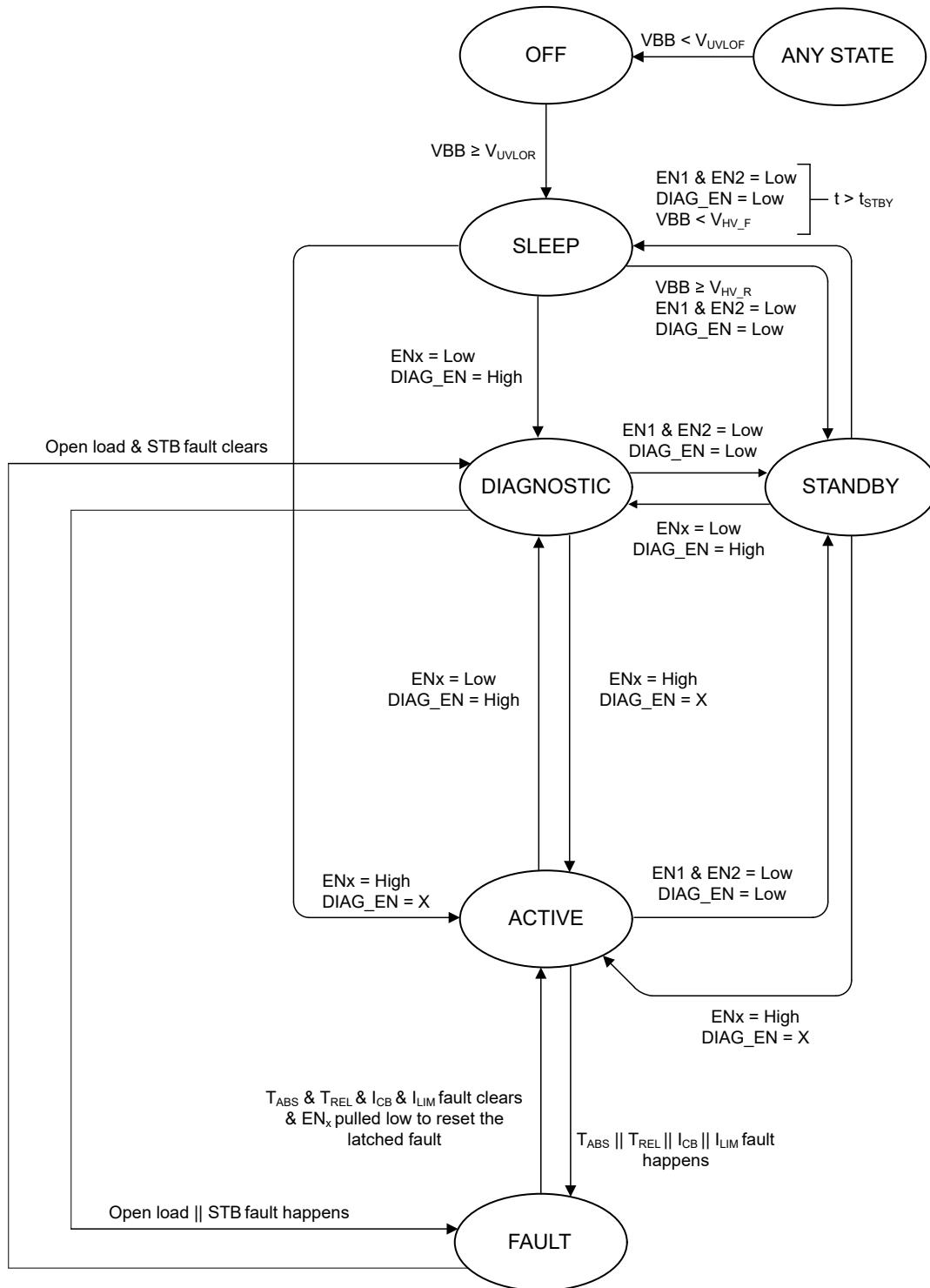

| $t_{STBY}$       | Standby mode delay time                                               | $V_{ENx} = V_{DIAG\_EN} = 0V$ , $V_{BB} < V_{HV\_F}$ to standby         |                      | 13  | 16   | 19  | ms      |

### RON CHARACTERISTICS

|                 |                                       |                                                                                       |                                        |      |     |      |           |

|-----------------|---------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------|------|-----|------|-----------|

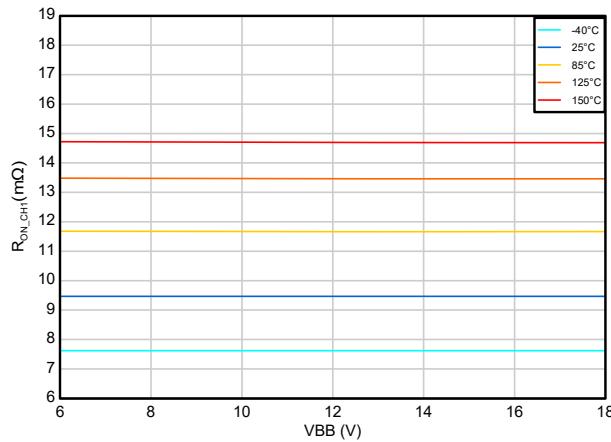

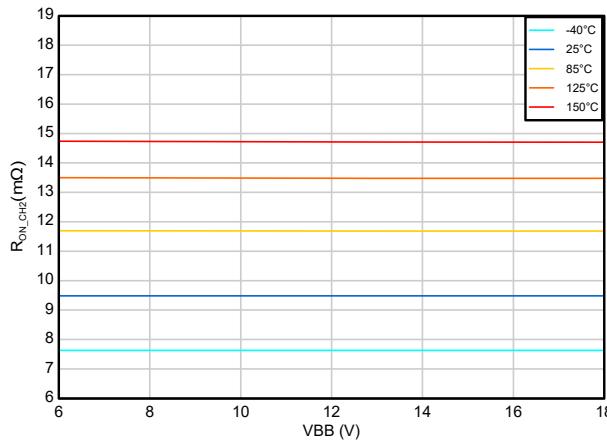

| $R_{ON}$        | On-resistance                         | $3V \leq V_{BB} \leq 28V$ , $I_{OUT} = 1A$                                            | $T_J = 25^{\circ}C$                    |      | 9.5 | 11   | $m\Omega$ |

|                 |                                       |                                                                                       | $T_J = 150^{\circ}C$                   |      |     | 16.5 | $m\Omega$ |

| $\Delta R_{ON}$ | Delta On-resistance between channels  | $6V \leq V_{BB} \leq 28V$ , $I_{OUT} = 1A$                                            | $T_J = -40^{\circ}C$ to $150^{\circ}C$ |      | 0.5 | 5    | %         |

| $R_{ON(REV)}$   | On-resistance during reverse polarity | $-18V \leq V_{BB} \leq -6V$                                                           | $T_J = 25^{\circ}C$                    |      | 9.5 | 11   | $m\Omega$ |

|                 |                                       |                                                                                       | $T_J = 150^{\circ}C$                   |      |     | 16.8 | $m\Omega$ |

| $I_{L_{NOM}}$   | Continuous load current, per channel  | Two channels enabled, $T_A = 85^{\circ}C$<br>One channel enabled, $T_A = 85^{\circ}C$ |                                        |      | 7.5 |      | A         |

|                 |                                       |                                                                                       |                                        |      |     | 10   | A         |

| $V_F$           | Source-to-drain body diode voltage    | $V_{EN} = 0V$ , $I_{OUT} = -1A$                                                       |                                        | 0.15 | 0.6 | 0.8  | V         |

### CURRENT SENSE CHARACTERISTICS

|                        |                                                                                    |                                                        |                     |      |      |     |    |

|------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------|------|------|-----|----|

| $V_{BB\_ISNS}$         | V <sub>BB</sub> headroom needed for full current sense and fault functionality (2) | $V_{DIAG\_EN} = 3.3V$<br>$V_{DIAG\_EN} = 5V$           |                     |      | 5.3  |     | V  |

|                        |                                                                                    |                                                        |                     |      | 6.5  |     | V  |

| $K_{SNS}$              | Current sense ratio $I_{OUT} / I_{SNS}$                                            | $I_{OUT} = 1A$                                         |                     |      | 3008 |     |    |

| $K_{SNS}$              | Current sense ratio $I_{OUT} / I_{SNS}$ across $I_{OUT}$                           | $V_{BB} > V_{BB\_ISNS}$ , $V_{EN} = V_{DIAG\_EN} = 5V$ | $I_{OUT} = 5A$      |      | 3020 |     |    |

|                        |                                                                                    |                                                        |                     | -3.5 | 4    |     | %  |

|                        |                                                                                    |                                                        | $I_{OUT} = 2A$      |      | 3016 |     |    |

|                        |                                                                                    |                                                        |                     | -3.5 | 4    |     | %  |

|                        |                                                                                    |                                                        | $I_{OUT} = 1A$      |      | 3008 |     |    |

|                        |                                                                                    |                                                        |                     | -4.5 | 4.5  |     | %  |

|                        |                                                                                    |                                                        | $I_{OUT} = 500mA$   |      | 2990 |     |    |

|                        |                                                                                    |                                                        |                     | -9.5 | 8.5  |     | %  |

|                        |                                                                                    |                                                        |                     |      | 2931 |     |    |

|                        |                                                                                    |                                                        | $I_{OUT} = 200mA$   |      | -24  | 19  | %  |

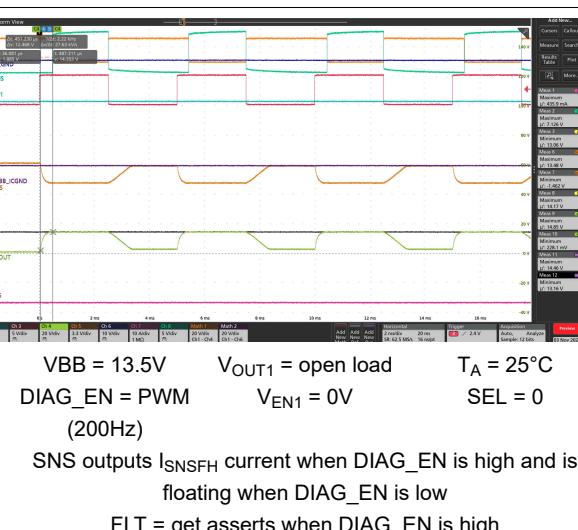

| $I_{SNSFH}$            | $I_{SNS}$ fault high-level                                                         | $V_{DIAG\_EN} > V_{IH,DIAG\_EN}$                       |                     | 5.5  | 7.4  | 9.5 | mA |

| $I_{SNSleak\_disbled}$ | $I_{SNS}$ leakage (Diagnostics disabled)                                           | $V_{DIA\_EN} = 0V$                                     | Force 0V on SNS Pin | -100 | 1    | 100 | nA |

### CURRENT LIMIT CHARACTERISTICS

## 6.5 Electrical Characteristics (continued)

$V_{BB} = 6V$  to  $18V$ ,  $T_J = -40^{\circ}C$  to  $150^{\circ}C$  (unless otherwise noted); Typical application is  $V_{BB} = 13.5V$ ,  $R_{LIM} = \text{Open}$  (unless otherwise specified)

| PARAMETER           |                                                                                          | TEST CONDITIONS                            |                                          | MIN | TYP          | MAX                  | UNIT               |

|---------------------|------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------------------|-----|--------------|----------------------|--------------------|

| $R_{LIM}$           | $R_{LIM}$ Short Circuit Detection Range                                                  |                                            |                                          |     | 20           |                      | $k\Omega$          |

|                     | $R_{LIM}$ Open Detection Range                                                           |                                            |                                          |     | 66.66        |                      | $k\Omega$          |

| $I_{CL\_FLT\_Trip}$ | Ratio of Current at which fault assertion happens to actual current limit <sup>(2)</sup> | $T_J = -40^{\circ}C$ to $150^{\circ}C$     | $R_{LIM} = 20 k\Omega$ to $66.5 k\Omega$ | 74  | 80           |                      | %                  |

| $K_{CL}$            | Current Limit Ratio <sup>(1)</sup>                                                       | $T_J = -40^{\circ}C$ to $150^{\circ}C$     | $R_{LIM} = 20 k\Omega$                   | 405 | 500          | 635                  | $A \times k\Omega$ |

|                     |                                                                                          |                                            | $R_{LIM} = 33.2 k\Omega$                 | 405 | 500          | 635                  | $A \times k\Omega$ |

|                     |                                                                                          |                                            | $R_{LIM} = 66.5 k\Omega$                 | 405 | 500          | 635                  | $A \times k\Omega$ |

| $I_{CL}$            | $I_{CL}$ Current Limit Threshold                                                         | $T_J = -40^{\circ}C$ to $150^{\circ}C$     | $R_{LIM} = \text{GND}$                   |     | 25           |                      | A                  |

|                     |                                                                                          |                                            | $R_{LIM} = \text{OPEN}$                  |     | 7.5          |                      | A                  |

| $I_{CB}$            | Peak current threshold when short is applied while switch enabled <sup>(2)</sup>         | $R_{LIM} = 16.9 k\Omega$ to $66.5 k\Omega$ | $T_J = -40^{\circ}C$                     |     | 23           |                      | A                  |

|                     |                                                                                          |                                            | $T_J = 25^{\circ}C$                      |     | 25           |                      | A                  |

|                     |                                                                                          |                                            | $T_J = 150^{\circ}C$                     |     | 22           |                      | A                  |

| $I_{CL\_HV}$        | $I_{CL}$ current limit derating at high voltage <sup>(2)</sup>                           | $T_J = -40^{\circ}C$ to $150^{\circ}C$     | $V_{BB} < V_{DET1}$                      |     | $I_{CL}$     |                      | A                  |

|                     |                                                                                          |                                            | $V_{DET1} \leq V_{BB} < V_{DET2}$        |     | $(I_{CL})/2$ | 20                   |                    |

|                     |                                                                                          |                                            | $V_{BB} \geq V_{DET2}$                   |     | $(I_{CL})/3$ | 10                   |                    |

| $I_{CL\_LNPK}$      | Linear mode peak <sup>(2)</sup>                                                          | $T_J = -40^{\circ}C$ to $150^{\circ}C$     | $R_{LIM} \geq 24.9 k\Omega$              |     |              | $1.45 \times I_{CL}$ | A                  |

|                     |                                                                                          |                                            | $R_{LIM} < 24.9 k\Omega$                 |     |              | $1.45 \times I_{CL}$ | $I_{CB}$           |

### FAULT CHARACTERISTICS

|                       |                                                                |                                                                                                        |     |     |      |             |

|-----------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----|-----|------|-------------|

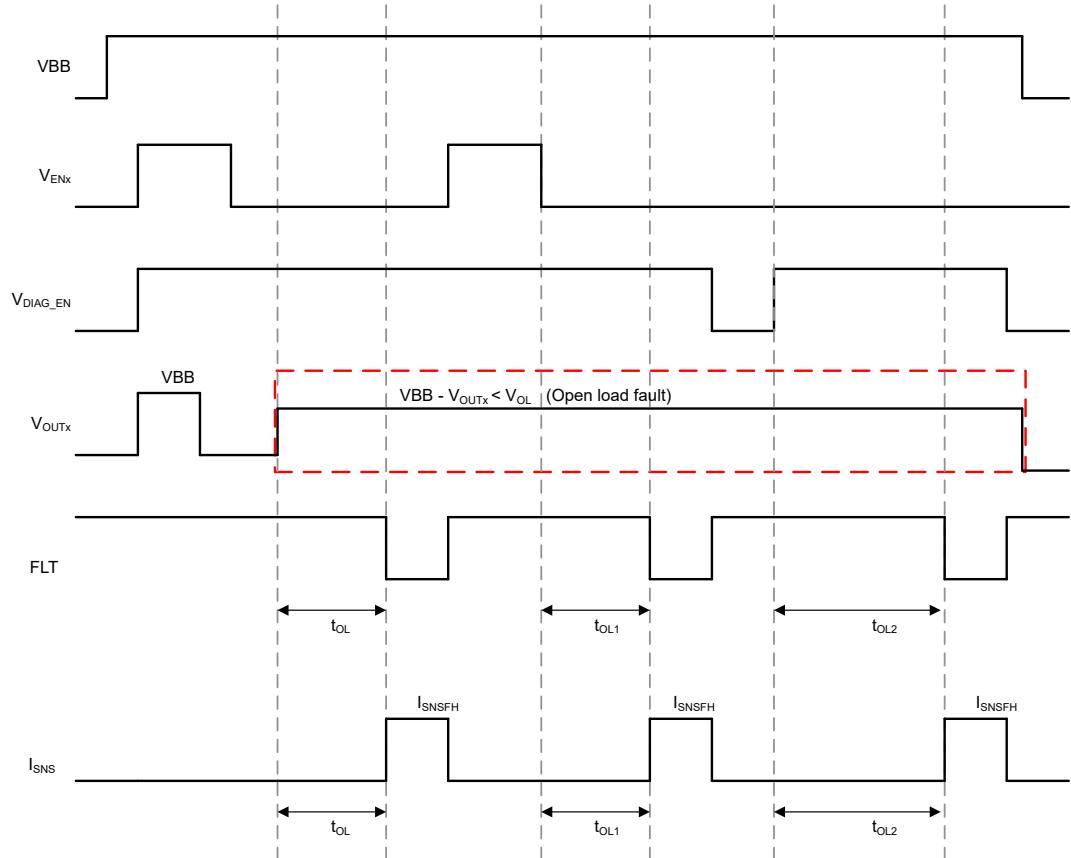

| $V_{OL}$              | Open-load detection voltage ( $V_{BB} - V_{OUTx}$ voltage)     | $V_{EN} = 0V$ , $V_{DIAG\_EN} = 5V$ , diagnostic state                                                 | 1.5 | 2.2 | 2.9  | V           |

| $R_{PU}$              | Open-load (OL) detection internal pull-up resistor per channel | $V_{EN} = 0V$ , $V_{DIAG\_EN} = 5V$ , diagnostic state, ( $V_{BB} - V_{OUTx} = 2.7V$ )                 |     | 90  |      | $k\Omega$   |

| $t_{OL}$              | Open-load (OL) detection deglitch time                         | $V_{EN} = 0V$ , $V_{DIAG\_EN} = 5V$ , When $V_{BB} - V_{OUT} < V_{OL}$ , duration longer than $t_{OL}$ | 200 |     | 550  | $\mu s$     |

| $t_{OL1}$             | OL and STB indication-time from EN falling                     | $V_{EN} = 5V$ to $0V$ , $V_{DIAG\_EN} = 5V$ , $I_{OUT} = 0mA$ , $V_{OUT} = V_{BB} - V_{OL}$            | 200 |     | 550  | $\mu s$     |

| $t_{OL2}$             | OL and STB indication-time from DIAG_EN rising                 | $V_{EN} = 0V$ , $V_{DIAG\_EN} = 0V$ to $5V$ , $I_{OUT} = 0mA$ , $V_{OUT} = V_{BB} - V_{OL}$            | 200 |     | 4050 | $\mu s$     |

| $T_{ABS}$             | Thermal shutdown <sup>(2)</sup>                                |                                                                                                        | 150 | 165 | 180  | $^{\circ}C$ |

| $T_{REL}$             | Relative thermal shutdown                                      |                                                                                                        |     | 85  |      | $^{\circ}C$ |

| $T_{HYS}$             | Thermal shutdown hysteresis                                    |                                                                                                        |     | 28  |      | $^{\circ}C$ |

| $V_{FLT}$             | FLT low output voltage                                         | $I_{FLT} = 2.5mA$                                                                                      |     |     | 0.2  | V           |

| $t_{FAULT\_FLT}$      | Fault indication-time <sup>(2)</sup>                           | $V_{DIAG\_EN} = 5V$ , time between fault and $\overline{FLT}$ asserting                                |     | 20  |      | $\mu s$     |

| $t_{FAULT\_SNS}$      | Fault indication-time <sup>(2)</sup>                           | $V_{DIAG\_EN} = 5V$ , time between fault and $I_{SNS}$ settling at $I_{SNSFH}$                         |     |     | 30   | $\mu s$     |

| $t_{RETRY\_WIN\_DOW}$ | Initial retry time window                                      |                                                                                                        |     | 40  |      | ms          |

| $t_{RETRY\_INT}$      | Retry time in initial retry window                             | Time from thermal shutdown to switch re-enable                                                         | 100 | 160 | 300  | $\mu s$     |

| $t_{RETRY\_EXTD}$     | Retry time in extended overcurrent window                      |                                                                                                        | 50  | 80  | 150  | ms          |

## 6.5 Electrical Characteristics (continued)

$V_{BB} = 6V$  to  $18V$ ,  $T_J = -40^{\circ}C$  to  $150^{\circ}C$  (unless otherwise noted); Typical application is  $V_{BB} = 13.5V$ ,  $R_{LIM} = \text{Open}$  (unless otherwise specified)

| PARAMETER                          | TEST CONDITIONS                         |                       | MIN | TYP | MAX | UNIT |            |

|------------------------------------|-----------------------------------------|-----------------------|-----|-----|-----|------|------------|

| <b>EN PIN CHARACTERISTICS</b>      |                                         |                       |     |     |     |      |            |

| $V_{IL, ENx}$                      | Input voltage low-level                 | No GND Network        |     |     | 0.8 | V    |            |

| $V_{IH, ENx}$                      | Input voltage high-level                |                       |     |     | 1.5 | V    |            |

| $V_{IHYS, ENx}$                    | Input voltage hysteresis                |                       |     |     | 320 | mV   |            |

| $R_{ENx}$                          | Internal pulldown resistor              |                       |     | 150 | 200 | 500  | k $\Omega$ |

| $I_{IL\_ENx}$                      | Input current low-level <sup>(2)</sup>  | $V_{ENx} = 0.8V$      |     | 1.6 | 4   | 5.5  | $\mu A$    |

| $I_{IH, ENx}$                      | Input current high-level <sup>(2)</sup> | $V_{ENx} = 5V$        |     | 19  | 25  | 35   | $\mu A$    |

| <b>DIAG_EN PIN CHARACTERISTICS</b> |                                         |                       |     |     |     |      |            |

| $V_{IL, DIAG\_EN}$                 | Input voltage low-level                 | No GND Network        |     |     | 0.8 | V    |            |

| $V_{IH, DIAG\_EN}$                 | Input voltage high-level                |                       |     |     | 1.5 | V    |            |

| $V_{IHYS, DIAG\_EN}$               | Input voltage hysteresis                |                       |     |     | 320 | mV   |            |

| $R_{DIAG\_EN}$                     | Internal pulldown resistor              |                       |     | 100 | 200 | 500  | k $\Omega$ |

| $I_{IL, DIAG\_EN}$                 | Input current low-level <sup>(2)</sup>  | $V_{DIAG\_EN} = 0.8V$ |     | 1.6 | 4   | 5.5  | $\mu A$    |

| $I_{IH, DIAG\_EN}$                 | Input current high-level <sup>(2)</sup> | $V_{DIAG\_EN} = 5V$   |     | 19  | 25  | 35   | $\mu A$    |

| <b>SEL PIN CHARACTERISTIC</b>      |                                         |                       |     |     |     |      |            |

| $V_{IL, SEL}$                      | Input voltage low-level                 | No GND Network        |     |     | 0.8 | V    |            |

| $V_{IH, SEL}$                      | Input voltage high-level                |                       |     |     | 1.5 | V    |            |

| $V_{IHYS, SEL}$                    | Input voltage hysteresis                |                       |     |     | 320 | mV   |            |

| $R_{SEL}$                          | Internal pulldown resistor              |                       |     | 100 | 350 | 500  | k $\Omega$ |

| $I_{IL, SEL}$                      | Input current low-level <sup>(2)</sup>  | $V_{SEL} = 0.8V$      |     | 1.7 | 2.3 | 3.3  | $\mu A$    |

| $I_{IH, SEL}$                      | Input current high-level <sup>(2)</sup> | $V_{SEL} = 5V$        |     | 11  | 14  | 20   | $\mu A$    |

(1) To calculate  $I_{CL}$  from  $K_{CL}$  use equation  $I_{CL} = K_{CL} / R_{LIM}$

(2) Parameter specified by design; not subject to production test.

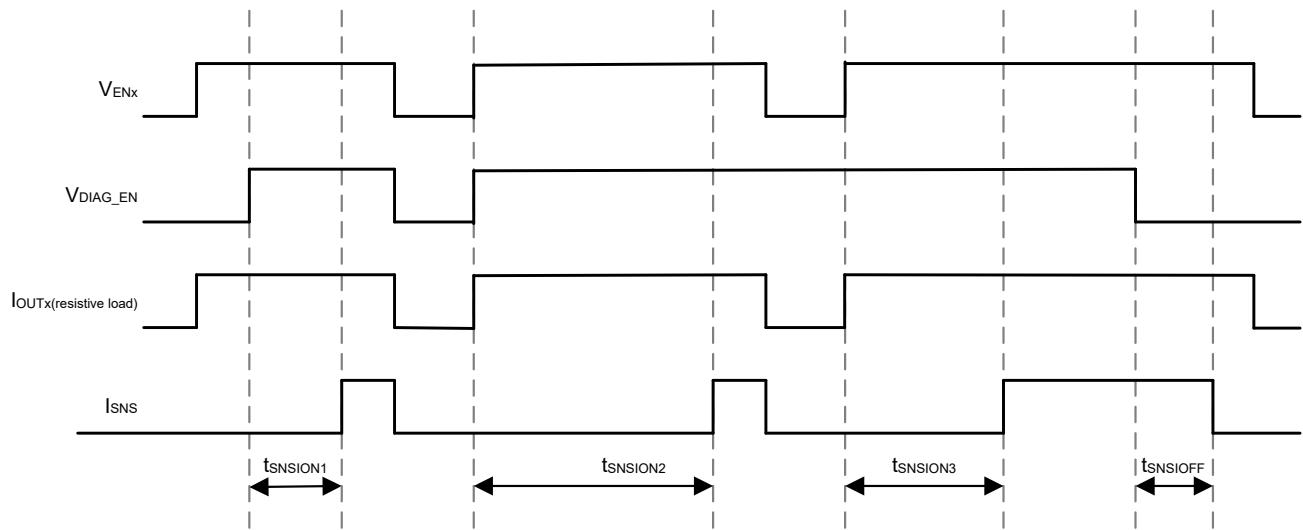

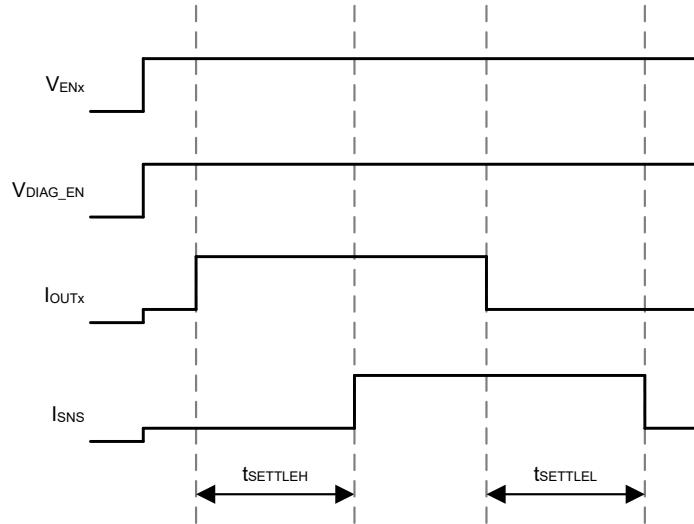

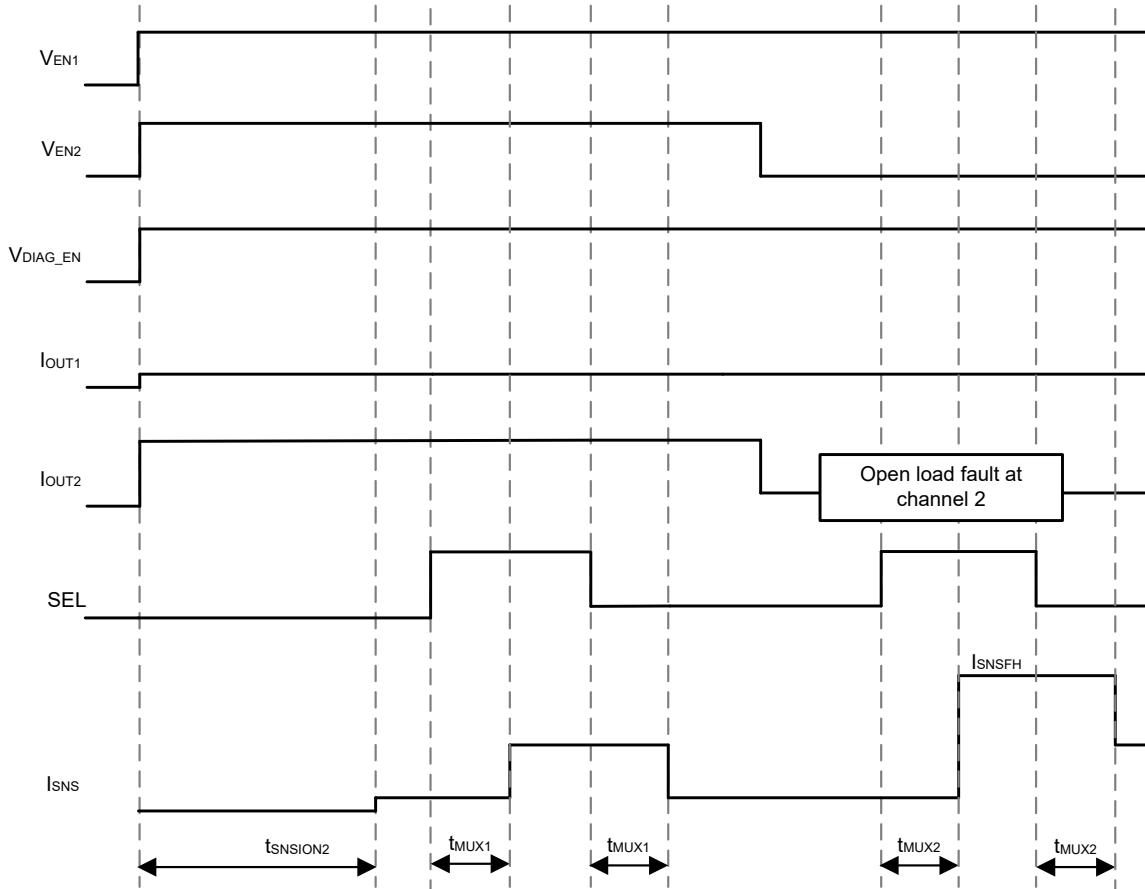

## 6.6 SNS Timing Characteristics

$V_{BB} = 6V$  to  $18V$ ,  $V_{ENx} = 5V$ ,  $V_{DIAG\_EN} = 5V$ ,  $R_{SNS} = 1k\Omega$ ,  $T_J = -40^{\circ}C$  to  $+150^{\circ}C$  (unless otherwise noted)

| PARAMETER                         | TEST CONDITIONS                                                                                | MIN | TYP | MAX | UNIT    |

|-----------------------------------|------------------------------------------------------------------------------------------------|-----|-----|-----|---------|

| <b>SNS TIMING - CURRENT SENSE</b> |                                                                                                |     |     |     |         |

| $t_{SNSION1}$                     | $V_{DIAG\_EN} = 0V$ to $5V$ , $I_{OUTx} = 1A$                                                  |     |     | 20  | $\mu s$ |

|                                   | $V_{DIAG\_EN} = 0V$ to $5V$ , $I_{OUTx} = 50mA$                                                |     |     | 20  | $\mu s$ |

| $t_{SNSION2}$                     | $V_{EN} = V_{DIAG\_EN} = 0V$ to $5V$ , $I_{OUTx} = 1A$                                         |     |     | 170 | $\mu s$ |

|                                   | $V_{EN} = V_{DIAG\_EN} = 0V$ to $5V$ , $I_{OUTx} = 50mA$                                       |     |     | 170 |         |

| $t_{SNSION3}$                     | $V_{ENx} = 0V$ to $5V$ , $V_{DIAG\_EN} = 5V$ , $I_{OUTx} = 1A$                                 |     |     | 110 | $\mu s$ |

| $t_{SNSIOFF}$                     | $V_{ENx} = 5V$ , $V_{DIAG\_EN} = 5V$ to $0V$ , $I_{OUTx} = 1A$                                 |     |     | 10  | $\mu s$ |

| $t_{SETTLEH}$                     | $I_{OUTx} = 50mA$ to $1A$                                                                      |     |     | 20  | $\mu s$ |

| $t_{SETTLEL}$                     | $I_{OUTx} = 1A$ to $50mA$                                                                      |     |     | 20  | $\mu s$ |

| $t_{MUX1}$                        | $V_{SEL} = 0V$ to $5V$ , $I_{OUT1} = 50mA$ , $I_{OUT2} = 1A$                                   |     |     | 20  | $\mu s$ |

| $t_{MUX2}$                        | $V_{EN1} = 5V$ , $V_{EN2} = 0V$ , $V_{SEL} = 0V$ to $5V$ , $I_{OUT1} = 1A$ , $CH2 = I_{SNSFH}$ |     |     | 20  | $\mu s$ |

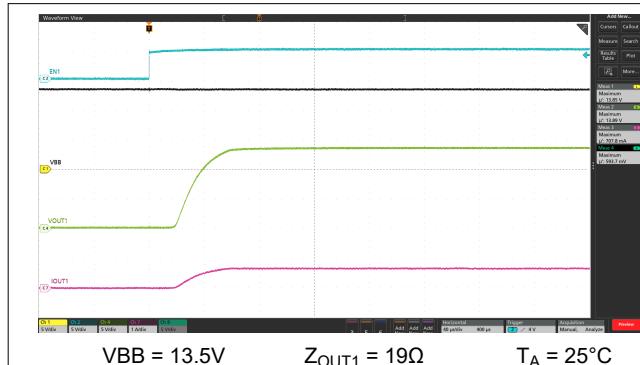

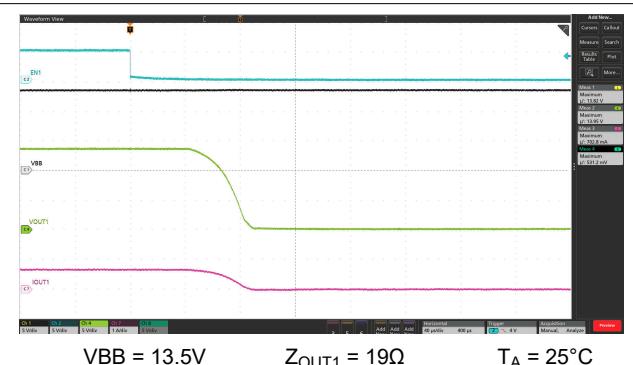

## 6.7 Switching Characteristics

$V_{BB} = 13.5V$ ,  $R_L = 10\Omega$ ,  $T_J = -40^\circ C$  to  $+150^\circ C$  (unless otherwise noted)

| PARAMETER          |                                                    | TEST CONDITIONS                                         | MIN  | TYP  | MAX     | UNIT      |

|--------------------|----------------------------------------------------|---------------------------------------------------------|------|------|---------|-----------|

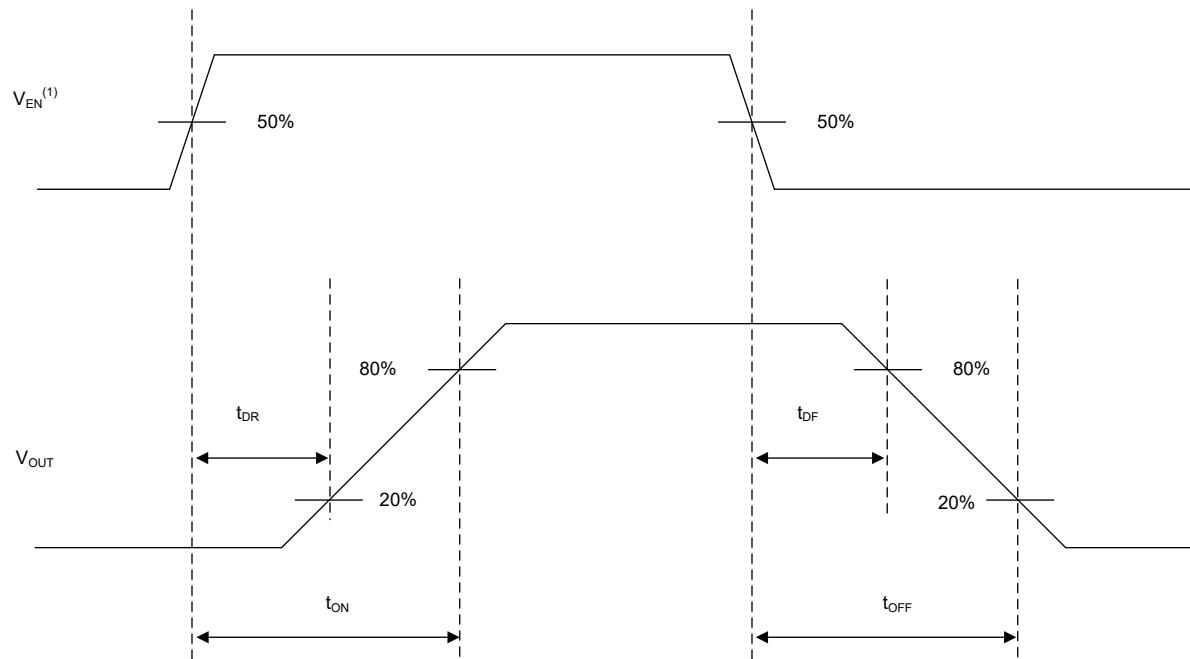

| $t_{DR}$           | Channel Turn-on delay time                         | 50% of ENx to 20% of VOUTx from standby state           | 6    | 12   | 30      | $\mu s$   |

|                    |                                                    | 50% of ENx to 20% of VOUTx from sleep state             | 10   | 45   | 70      | $\mu s$   |

| $t_{DF}$           | Channel Turn-off delay time                        | 50% of ENx to 80% of VOUTx                              | 35   | 80   | 121     | $\mu s$   |

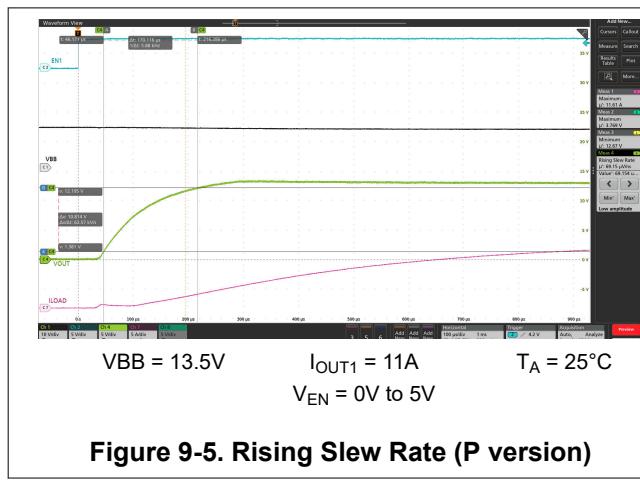

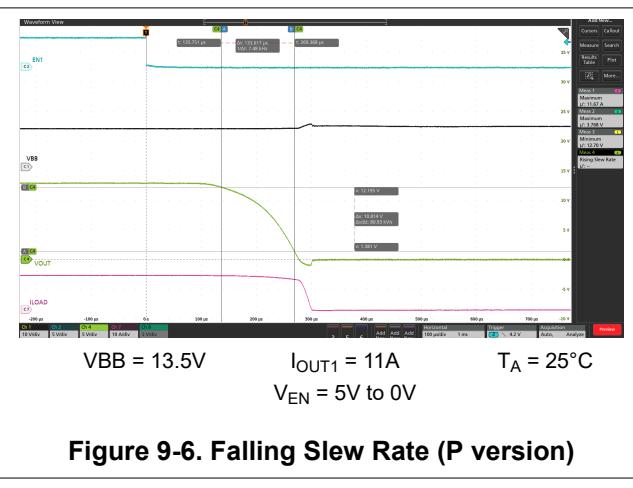

| $SR_R$             | VOUT rising slew rate                              | 20% to 80% of VOUTx (version = D, B)                    | 0.02 | 0.06 | 0.1     | $V/\mu s$ |

|                    |                                                    | 20% to 80% of VOUTx (version = P, M)                    | 0.3  | 0.45 | 0.65    | $V/\mu s$ |

| $SR_F$             | VOUT falling slew rate                             | 80% to 20% of VOUTx (version = D, B)                    | 0.02 | 0.06 | 0.1     | $V/\mu s$ |

|                    |                                                    | 80% to 20% of VOUTx (version = P, M)                    | 0.3  | 0.5  | 0.7     | $V/\mu s$ |

| $t_{ON}$           | Channel Turn-on time                               | 50% of EN to 80% of VOUT, from sleep state              | 35   | 60   | 110     | $\mu s$   |

|                    |                                                    | 50% of EN to 80% of VOUT, from standby state            | 15   | 30   | 90      | $\mu s$   |

| $t_{OFF}$          | Channel Turn-off time                              | 50% of EN to 20% of VOUT                                | 50   | 90   | 130     | $\mu s$   |

| $t_{ON} - t_{OFF}$ | Turn-on and off matching <sup>(1)</sup>            | 1ms enable pulse                                        | -75  | 40   | $\mu s$ |           |

|                    |                                                    | 200 $\mu s$ enable pulse                                | -90  | 40   | $\mu s$ |           |

| $\Delta_{PWM}$     | PWM accuracy - average load current <sup>(1)</sup> | 200 $\mu s$ enable pulse (1ms period)                   | -45  | 25   | %       |           |

|                    |                                                    | $\leq 500Hz$ , 50% Duty cycle                           | -12  | 12   | %       |           |

| $E_{ON}$           | Switching energy losses during turn-on             | $V_{BB} = 18V$ , $R_L = 3.3\Omega$ , 0% to 100% of VOUT |      | 0.63 |         | $mJ$      |

|                    |                                                    | $V_{BB} = 18V$ , $R_L = 3.3\Omega$ , 10% to 90% of VOUT |      | 0.59 |         | $mJ$      |

| $E_{OFF}$          | Switching energy losses during turn-off            | $V_{BB} = 18V$ , $R_L = 3.3\Omega$ , 100% to 0% of VOUT |      | 0.77 |         | $mJ$      |

|                    |                                                    | $V_{BB} = 18V$ , $R_L = 3.3\Omega$ , 90% to 10% of VOUT |      | 0.67 |         | $mJ$      |

(1) Parameter specified by design; not subject to production test.

## 6.8 Typical Characteristics

Figure 6-1. Standby Current ( $I_{SLEEP}$ ) vs Temperature

Figure 6-2. Quiescent Current ( $I_Q$ ) vs Temperature with Both Channels Enabled

Figure 6-3. Output Leakage Current ( $I_{OUT(SLEEP)}$ ) vs Temperature for Channel 1

Figure 6-4. Output Leakage Current ( $I_{OUT(SLEEP)}$ ) vs Temperature for Channel 2

Figure 6-5. On-resistance ( $R_{ON}$ ) vs VBB for Channel 1

Figure 6-6. On-resistance ( $R_{ON}$ ) vs VBB for Channel 2

## 6.8 Typical Characteristics (continued)

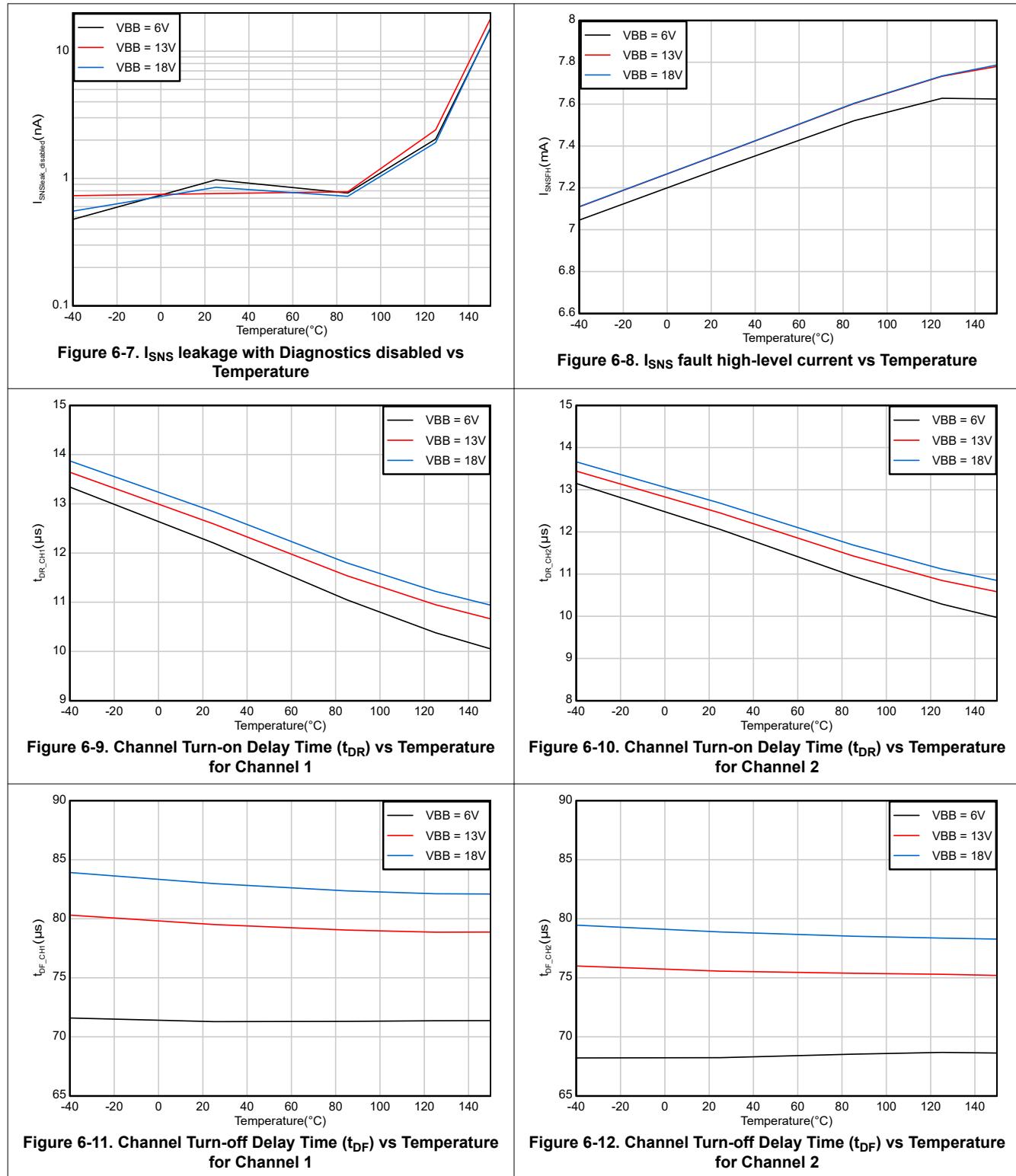

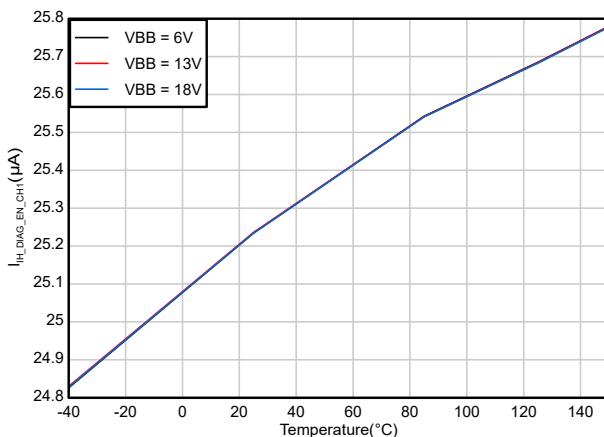

**Figure 6-7.  $I_{SNS}$  leakage with Diagnostics disabled vs Temperature**

**Figure 6-8.  $I_{SNS}$  fault high-level current vs Temperature**

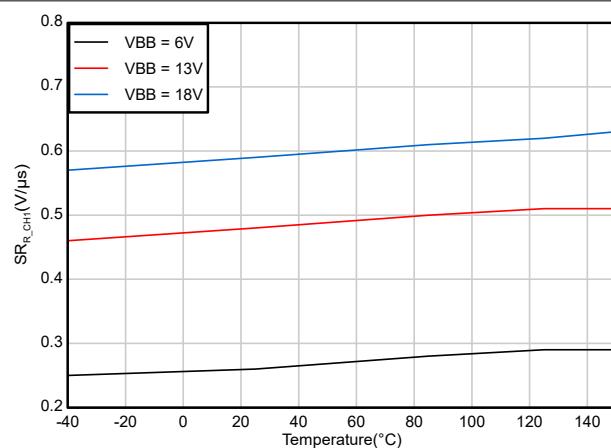

**Figure 6-9. Channel Turn-on Delay Time ( $t_{DR}$ ) vs Temperature for Channel 1**

**Figure 6-10. Channel Turn-on Delay Time ( $t_{DR}$ ) vs Temperature for Channel 2**

**Figure 6-11. Channel Turn-off Delay Time ( $t_{DF}$ ) vs Temperature for Channel 1**

**Figure 6-12. Channel Turn-off Delay Time ( $t_{DF}$ ) vs Temperature for Channel 2**

## 6.8 Typical Characteristics (continued)

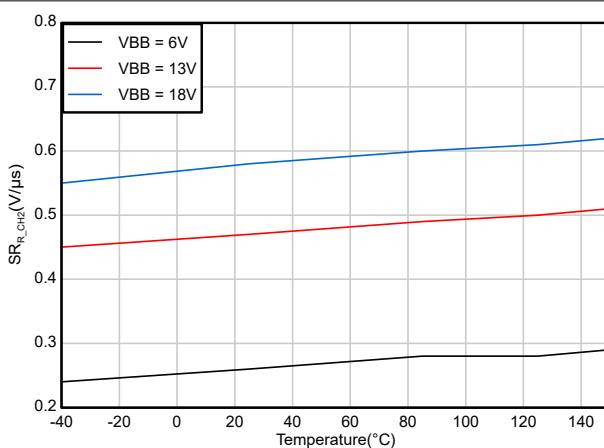

Figure 6-13. VOUT Rising Slew Rate ( $SR_R$ ) vs Temperature for Channel 1 (P version)

Figure 6-14. VOUT Rising Slew Rate ( $SR_R$ ) vs Temperature for Channel 2 (P version)

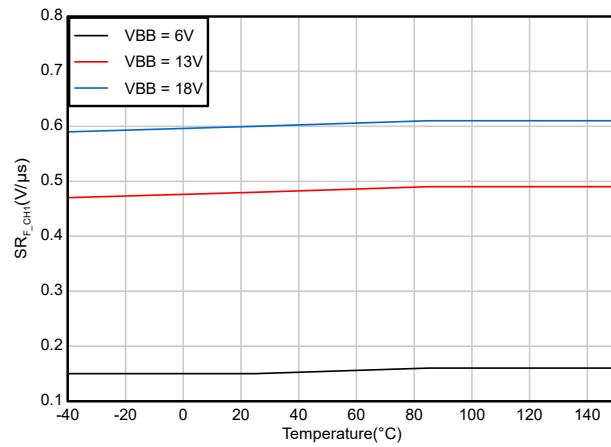

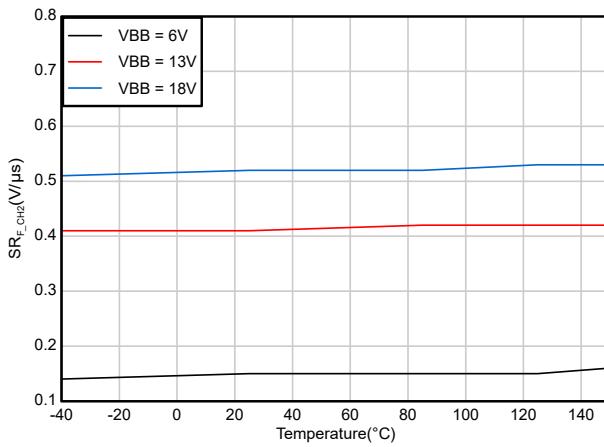

Figure 6-15. VOUT Falling Slew Rate ( $SR_F$ ) vs Temperature for Channel 1 (P version)

Figure 6-16. VOUT Falling Slew Rate ( $SR_F$ ) vs Temperature for Channel 2 (P version)

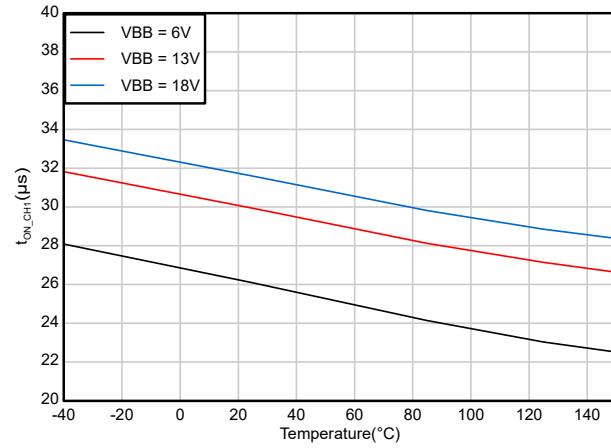

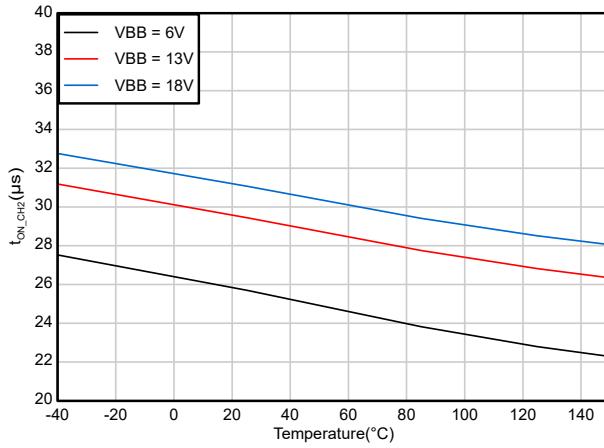

Figure 6-17. Channel Turn-on Time ( $t_{ON}$ ) vs Temperature for Channel 1

Figure 6-18. Channel Turn-on Time ( $t_{ON}$ ) vs Temperature for Channel 2

## 6.8 Typical Characteristics (continued)

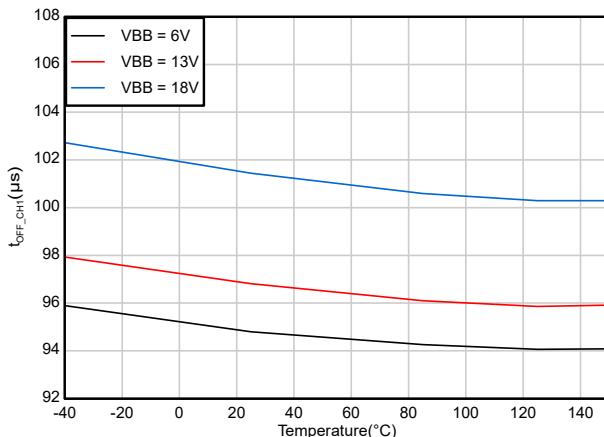

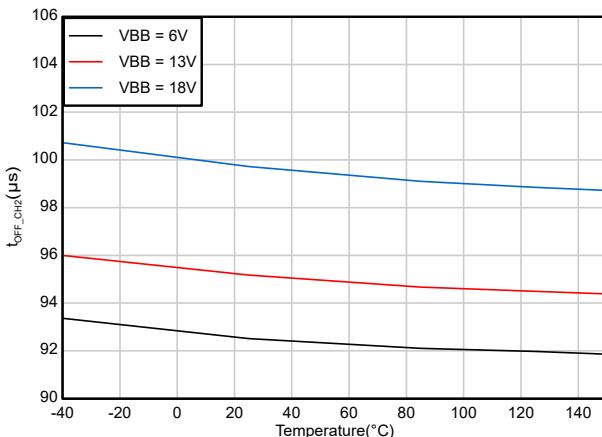

Figure 6-19. Channel Turn-off Time ( $t_{OFF}$ ) vs Temperature for Channel 1

Figure 6-20. Channel Turn-off Time ( $t_{OFF}$ ) vs Temperature for Channel 2

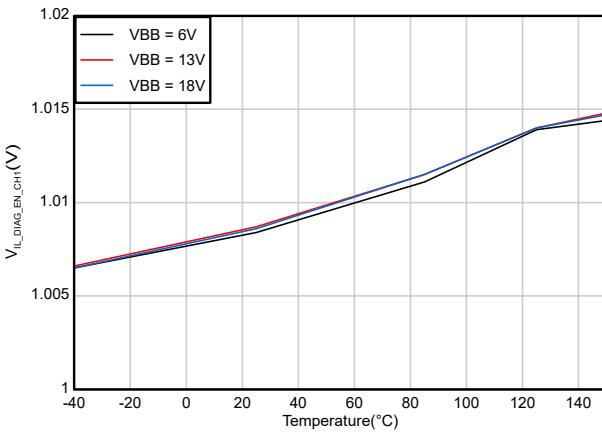

Figure 6-21. DIAG\_EN Input Voltage High Level vs Temperature

Figure 6-22. DIAG\_EN Input Voltage Low Level vs Temperature

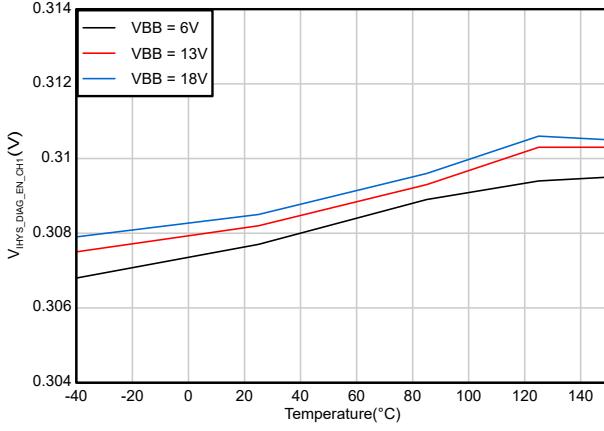

Figure 6-23. DIAG\_EN Input Voltage Hysteresis vs Temperature

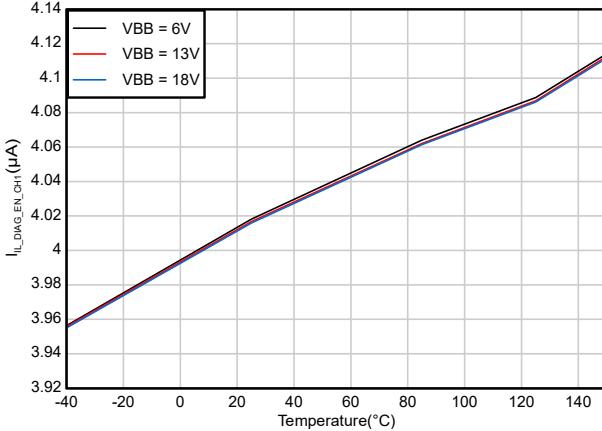

Figure 6-24. DIAG\_EN Input Current Low Level vs Temperature

## 6.8 Typical Characteristics (continued)

Figure 6-25. DIAG\_EN Input Current High Level vs Temperature for Channel 1

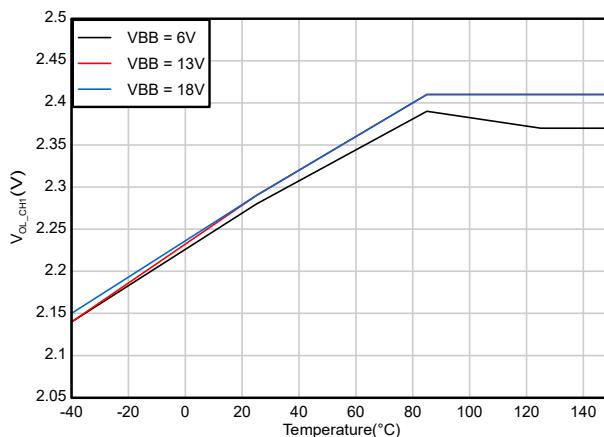

Figure 6-26. Open-Load Detection Voltage (VOL) vs Temperature for Channel 1

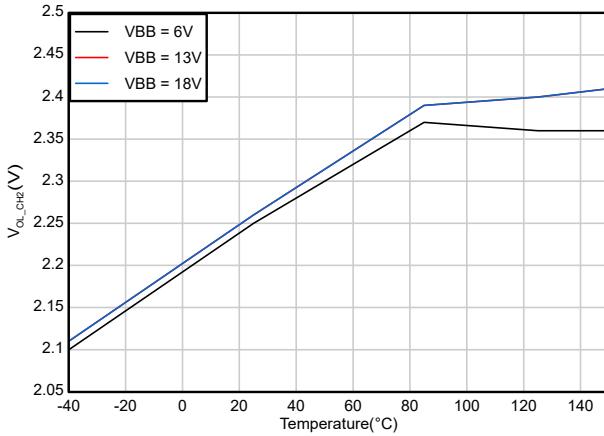

Figure 6-27. Open-Load Detection Voltage (VOL) vs Temperature for Channel 2

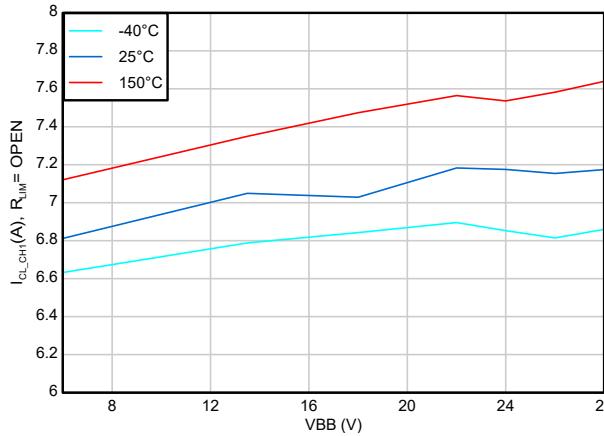

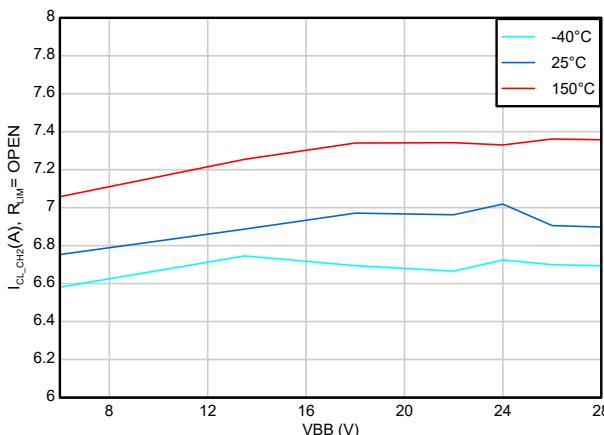

Figure 6-28. Current Limit Regulation Level (ICL) vs VBB for Channel 1,  $R_{LIM} = OPEN$

Figure 6-29. Current Limit Regulation Level (ICL) vs VBB for Channel 2,  $R_{LIM} = OPEN$

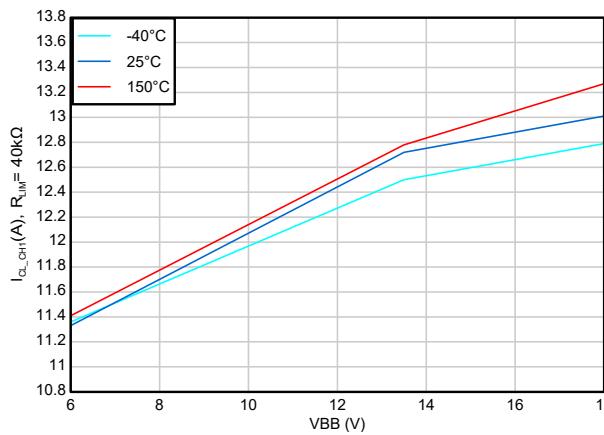

Figure 6-30. Current Limit Regulation Level (ICL) vs VBB for Channel 1,  $R_{LIM} = 40k\Omega$

## 6.8 Typical Characteristics (continued)

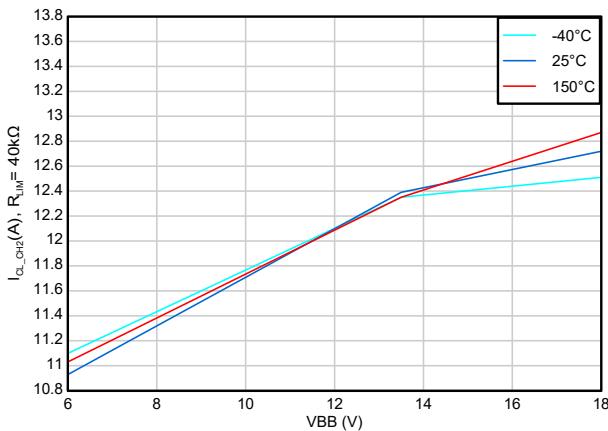

Figure 6-31. Current Limit Regulation Level ( $I_{CL}$ ) vs VBB for Channel 2,  $R_{LIM} = 40k\Omega$

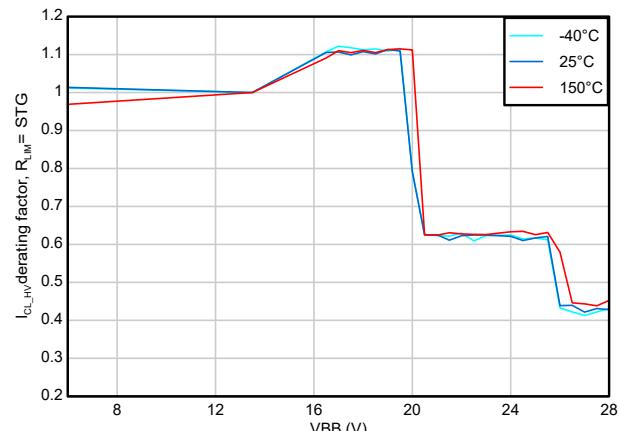

Figure 6-32. Current Limit Derating factor ( $I_{CL_HV}$ ) vs VBB for both channels,  $R_{LIM} = GND$

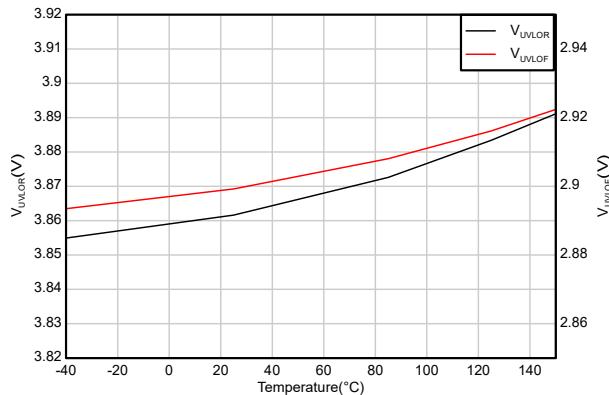

Figure 6-33. Undervoltage Lockout Thresholds ( $V_{UVLOR}$ ,  $V_{UVLOF}$ ) vs Temperature

## 7 Parameter Measurement Information

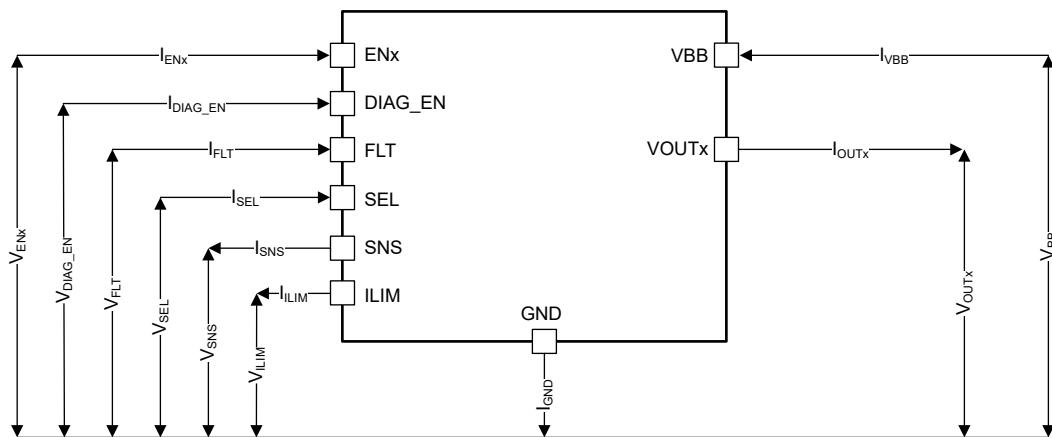

For reference purposes throughout the data sheet, current directions on the respective pins are as shown by the arrows in [Figure 7-1](#). All voltages are measured relative to the ground plane.

Figure 7-1. Voltage and Current Conventions

Rise and fall time of VEN is 100 ns.

Figure 7-2. Switching Characteristics Definitions

## 8 Detailed Description

### 8.1 Overview

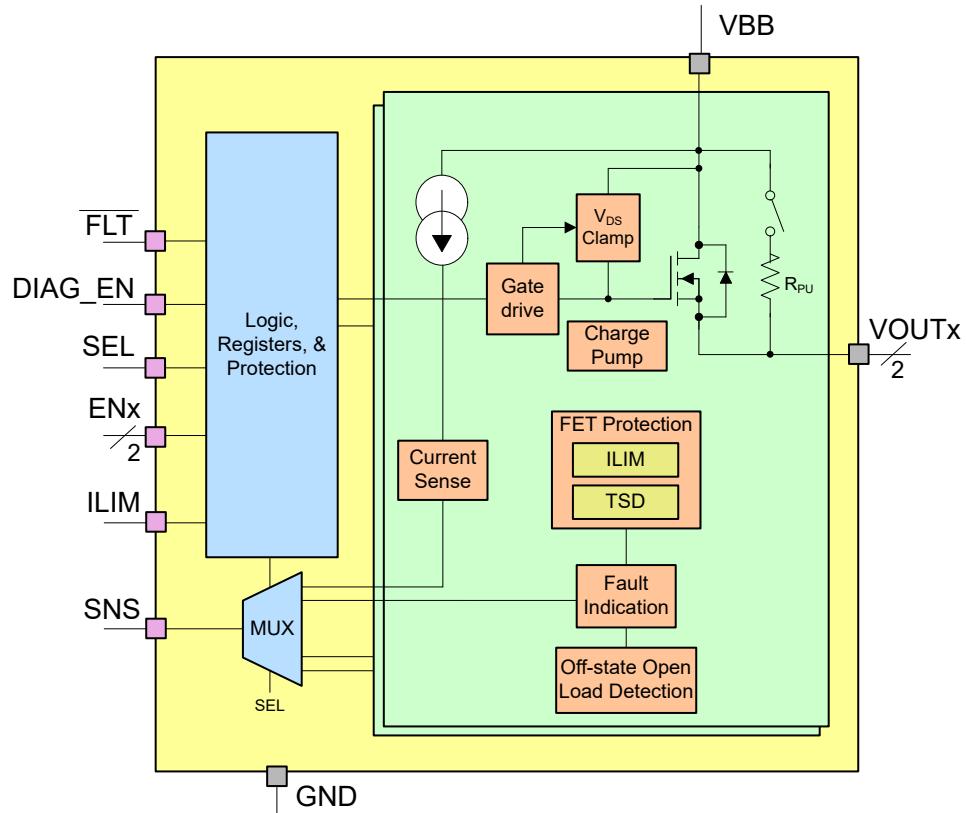

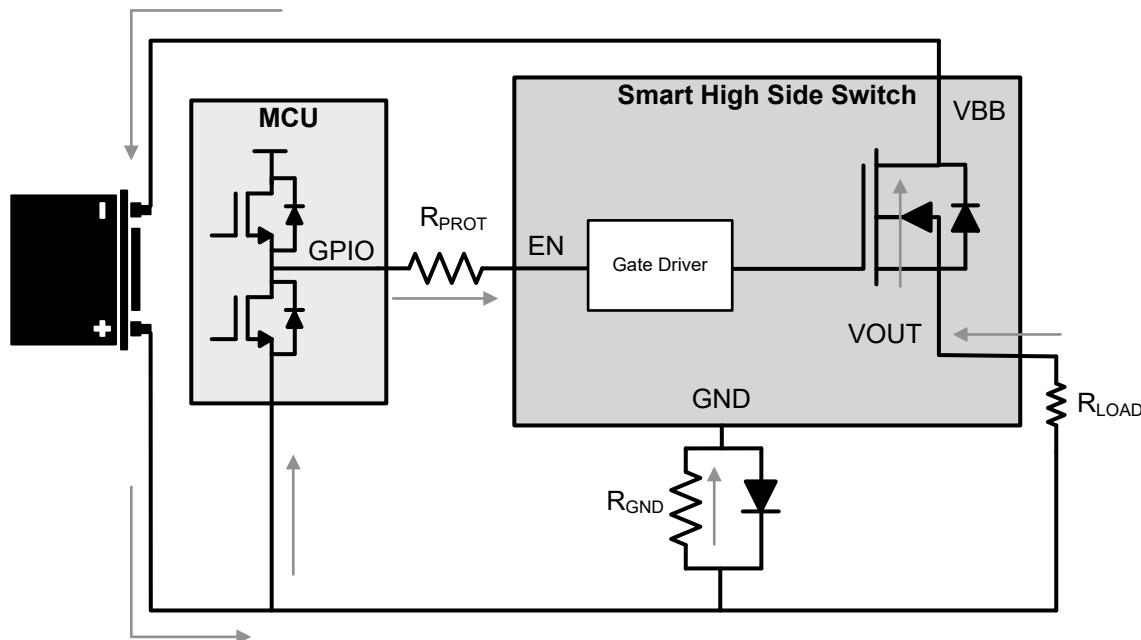

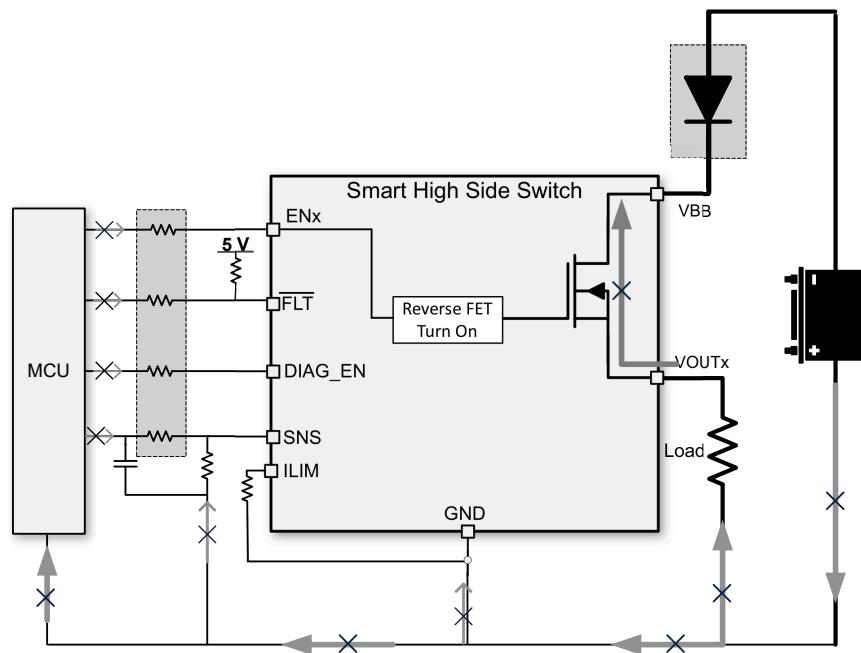

The TPS2HC08-Q1 is a dual-channel, fully-protected, high side power switch with integrated NMOS power FETs and charge pump. Full diagnostics and high-accuracy current-sense features enable intelligent control of the load. The device offers two pins to support both digital status and analog current-sense output. The current-sense output can be set to high-impedance state when diagnostics are disabled, which can enable multiplexing of the MCU analog interface between multiple devices.

The device has dedicated logic pins to enable each of the two channels and a separate DIAG\_EN pin to enable the diagnostic output. The SEL pin allows to select the channel to be output on the analog current sense (SNS) pin. The device also implements a global FLT pin with an open-drain structure, to be used as an interrupt to the MCU. When a fault condition occurs, the pin is pulled down to GND. An external pullup is required to match the microcontroller supply level.

High-accuracy current sensing allows for better real-time monitoring and more-accurate diagnostics without additional in-line calibration. A current mirror is used to source  $1 / K_{SNS}$  of the load current, which is reflected as voltage across a resistor on the SNS pin. The SNS pin can also report a fault by sourcing a current of  $I_{SNSFH}$  out of the SNS pin. During fault the SNS pin voltage is represented by  $I_{SNSFH} \times R_{SNS}$ . If this voltage violates the acceptable voltage range of the MCU ADC, an external Zener diode or resistor divider on the SNS pin has to be connected.

The device also offers a programmable current-limit function which greatly improves the reliability of the whole system by clamping the inrush current effectively at start-up when charging large capacitances or during short-circuit conditions. The high-accuracy current limit of the device can be set using an external resistor between 7.5A to 25A. The device also offers current limit settings with and without thermal regulation. The thermal regulated current limit can be useful when charging large capacitors at startup. The current limit setting without thermal regulation is useful for loads such high motor stall currents or bulb loads.

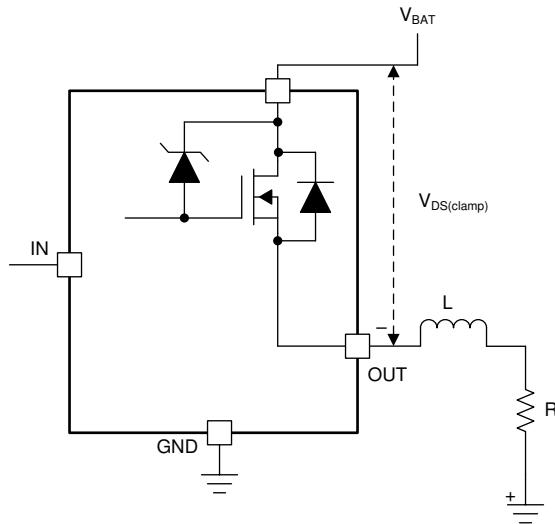

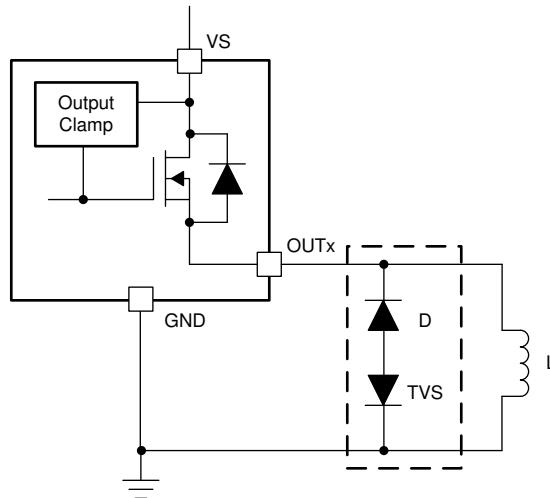

A voltage clamp is built in to address switching off the energy of inductive loads, such as relays, solenoids, pumps, motors, and so forth. With the benefits of process technology and excellent IC layout, the TPS2HC08-Q1 device can achieve excellent power dissipation capacity, which can help save the external free-wheeling circuitry in most cases. For more details, see Inductive-Load Switching-Off Clamp.

The TPS2HC08-Q1 device can be used as a high side power switch for a wide variety of resistive, inductive, and capacitive loads, including bulbs, LEDs, relays, solenoids, and heaters.

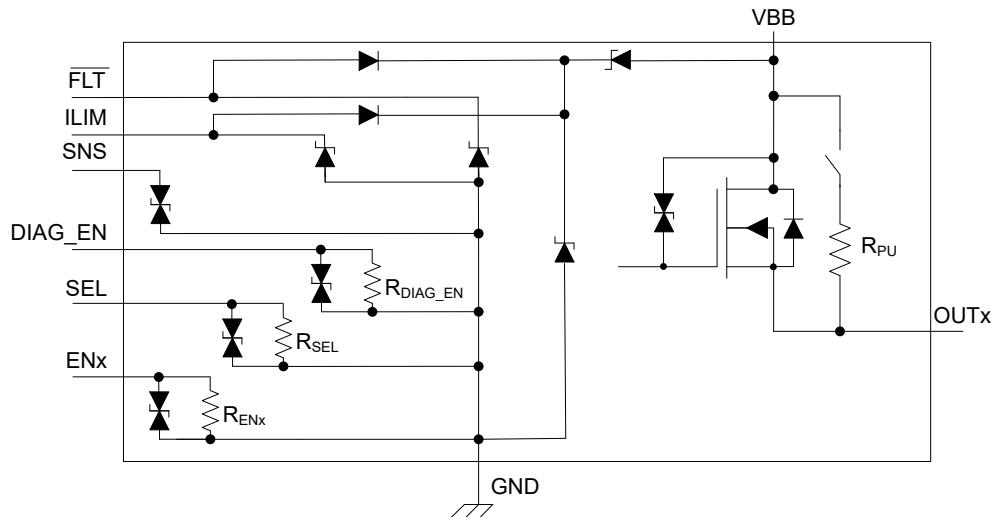

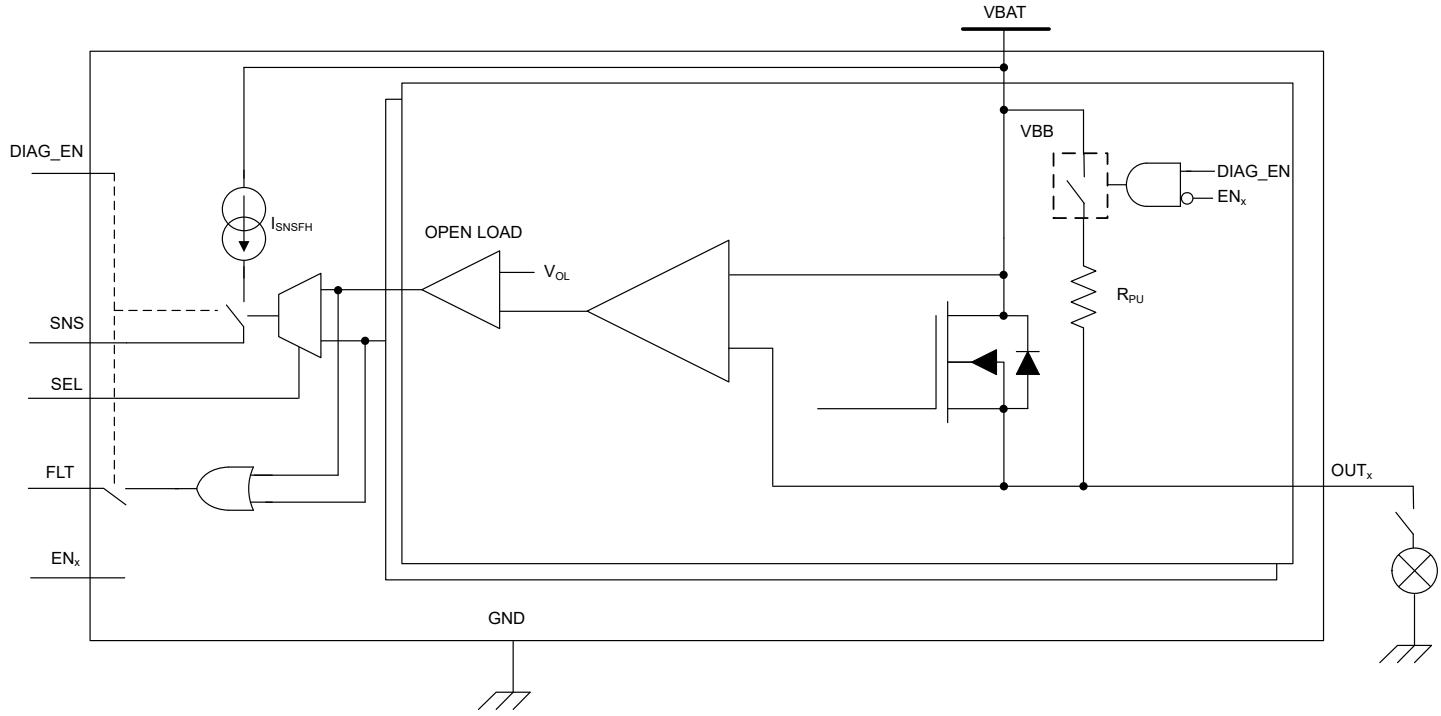

## 8.2 Functional Block Diagram

Figure 8-1. Functional Block Diagram

Figure 8-2. Internal Diodes Diagram

The above figure shows the internal diodes structure of the device. There are back-to-back diodes connected between **GND** pin and low voltage IO pins to provide voltage clamp along with the internal pulldown resistor to keep pins in known state. The **FLT** and **ILIM** pins have internal protection structure to withstand voltage up to **VBB**, making it robust against adjacent pin short. A drain-to-source clamp structure, comprising back-to-back zener and diode, is also implemented across the power switch to protect against inductive energy demagnetisation.

## 8.3 Feature Description

### 8.3.1 Accurate Current Sense

The high-accuracy current-sense function allows a better real-time monitoring effect and accurate diagnostics without further calibration. A current mirror is used to source  $1 / K_{SNS}$  of the load current, flowing out to the external resistor between the SNS pin and GND, and reflected as voltage on the SNS pin.

$K_{SNS}$  is the ratio of the output current and the sense current. The accuracy values of  $K_{SNS}$  quoted in the electrical characteristics do take into consideration temperature and supply voltage. Each device is internally calibrated while in production, so post-calibration by users is not required.

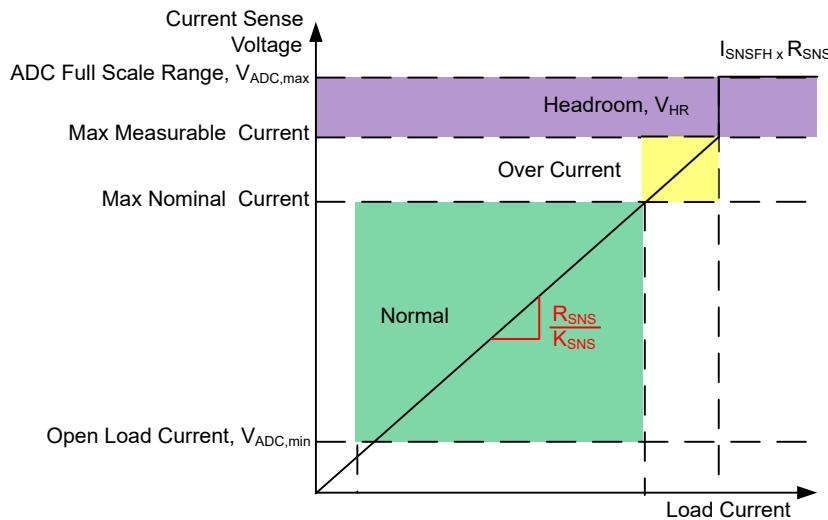

The sense resistor value,  $R_{SNS}$ , can be chosen to maximize the range of currents needed to be measured by the system. The  $R_{SNS}$  value must be chosen based on application need. The minimum  $R_{SNS}$  value is bounded by the ADC minimum acceptable voltage,  $V_{ADC,min}$ , for the minimum load current needed to be measured by the system,  $I_{LOAD,min}$ . The maximum  $R_{SNS}$  value is bounded by the ADC maximum acceptable voltage,  $V_{ADC,max}$ , for the  $I_{SNSFH}$  (check [Electrical Characteristics](#) for the minimum specification) during fault condition. The SNS pin current during fault condition,  $I_{SNSFH}$  should be significantly higher than the SNS pin current at maximum load current ( $I_{LOAD,max}$ ), to provide sufficient headroom voltage ( $V_{HR}$ ) to determine difference between the maximum readable current and a fault condition. Use [Equation 1](#) to calculate the value of  $R_{SNS}$  without any external zener diode or resistor divider on SNS pin.

$$\frac{(V_{ADC,min} \times K_{SNS})}{I_{LOAD,min}} \leq R_{SNS} \leq \frac{V_{ADC,max}}{I_{SNSFH}} \quad (1)$$

To get better resolution in current sense voltage, an external Zener diode or resistor divider can be connected to the SNS pin to clamp the SNS pin voltage to ADC maximum acceptable voltage,  $V_{ADC,max}$  during the fault condition. In this case, user needs to select  $R_{SNS}$  resistor to achieve required headroom voltage ( $V_{HR}$ ) between the maximum readable current and a fault condition. Use [Equation 2](#) to calculate the value of  $R_{SNS}$  in this scenario.

$$\frac{(V_{ADC,min} \times K_{SNS})}{I_{LOAD,min}} \leq R_{SNS} \leq \frac{((V_{ADC,max} - V_{HR}) \times K_{SNS})}{I_{LOAD,max}} \quad (2)$$

In some applications, where there is a higher load current range the above applicable boundary equation can only satisfy either the lower or upper bound. In these cases, more emphasis can be put on the lower measurable current values which increases  $R_{SNS}$ . Likewise, if the higher currents are of more interest the  $R_{SNS}$  can be decreased. In case a GND network is used for reverse polarity protection, the voltage drop across the GND network has to be taken into account to ensure that the SNS pin voltage does not exceed the maximum acceptable ADC voltage.

Figure 8-3. Voltage Indication on the Current-Sense Pin

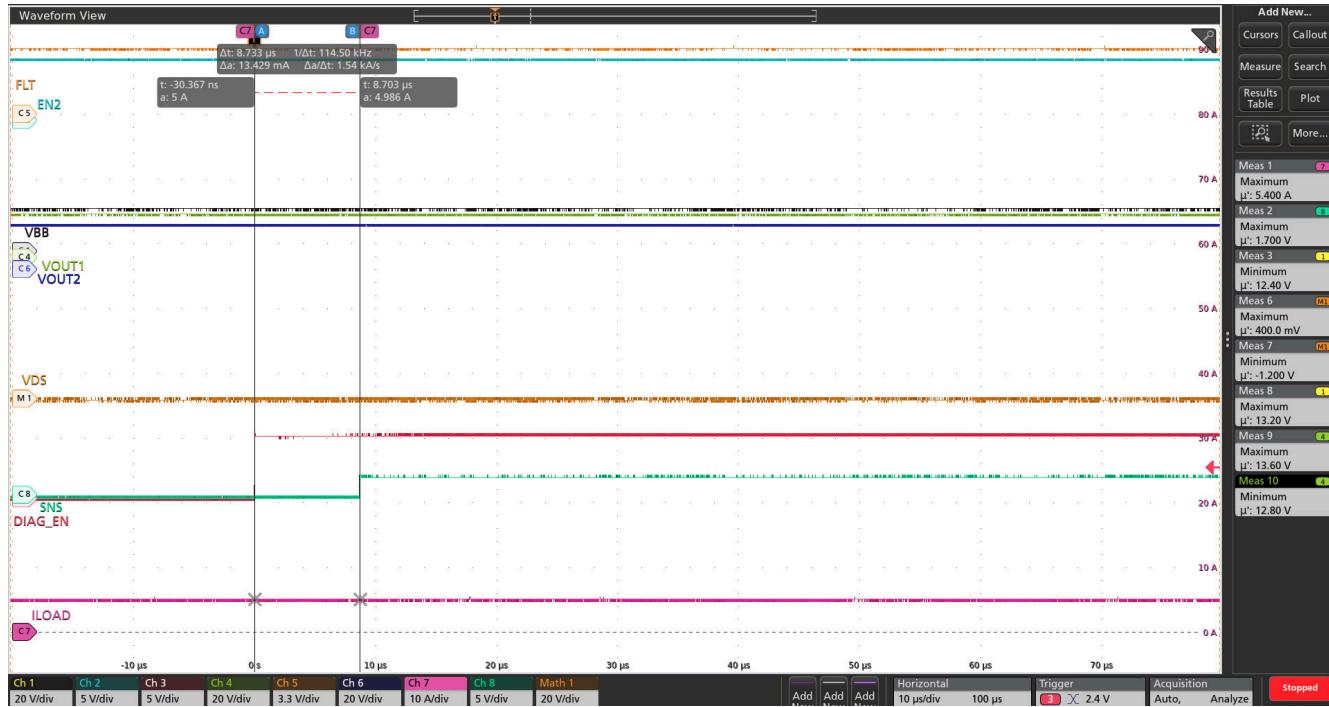

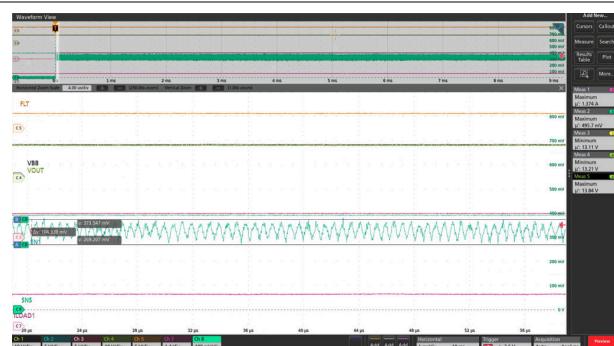

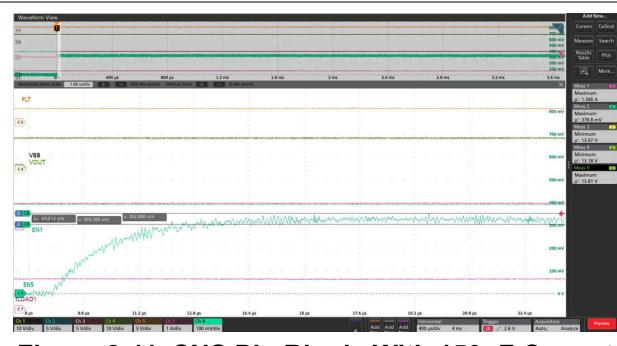

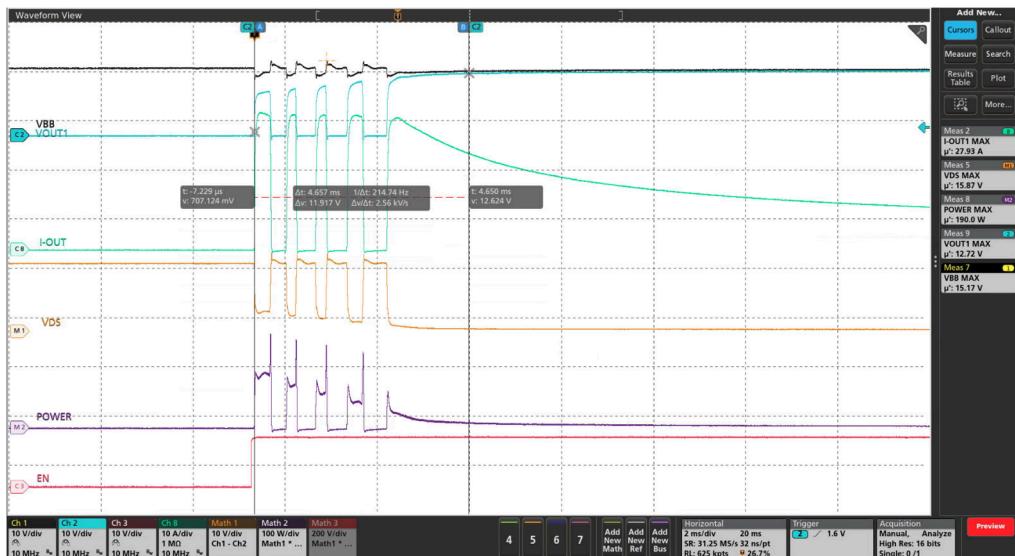

The maximum current the system wants to read,  $I_{LOAD,max}$ , must be below the current-limit threshold because after the current-limit threshold is tripped the SNS pin current goes to  $I_{SNSFH}$ . Figure 8-4 shows the SNS pin behavior for 5A load step on channel 1 of the device with  $1\text{k}\Omega R_{SNS}$ .

Figure 8-4. SNS Pin Voltage with Varying Load Current on Channel 1 ( $R_{SNS} = 1\text{k}\Omega$ , SEL = 0)

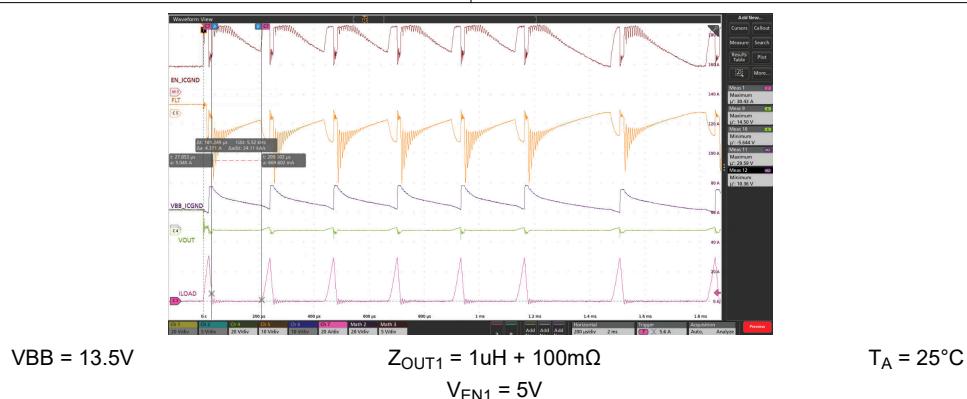

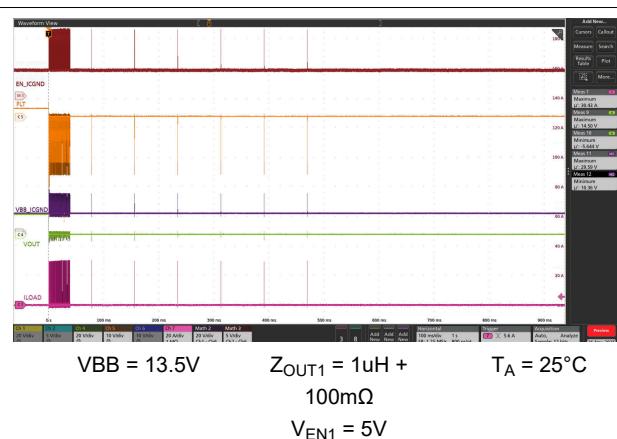

### 8.3.1.1 SNS Response Time

Some applications can operate with a high frequency, low duty cycle PWM. Such applications require fast settling of the SNS output. For example, a 250Hz, 5% duty cycle PWM has an on-time of only 200 $\mu\text{s}$ . The microcontroller ADC can sample the SNS signal after the defined settling time. The following figures shows response time of SNS signal with EN and DIAG\_EN being pulled high respectively. The fast response time of the device SNS signal easily allows current sense read by ADC in such applications.

**Figure 8-5. SNS Response Time with **DIAG\_EN** ( $t_{SNSION1}$ )**

**Figure 8-6. SNS Response Time with **EN** ( $t_{SNSION3}$ )**

### Note

Rise and fall times of control signals are 100ns. Control signals include: ENx, **DIAG\_EN** and **SEL**. Both the channels have same sense timings with appropriate **SEL** setting.

**Figure 8-7. SNS Settling Time From EN or DIAG\_EN**

**Figure 8-8. SNS Settling Time From Load step**

**Figure 8-9. SNS Settling Time From Switching From CHx to CHy**

### 8.3.1.2 SNS Output Filter

Due to the internal architecture, the SNS pin signal has a ripple component at a frequency of approximately 1.6MHz. Based on the  $R_{SNS}$  value, appropriate  $C_{SNS}$  can be connected on SNS pin to filter out this ripple component and reduce the peak-to-peak ripple of the SNS pin voltage. **Table 8-1** shows the typical peak-to-peak ripple voltage values with and without  $C_{SNS}$  on SNS pin. The designer can select a  $C_{SNS}$  capacitor value based on system requirements. A larger value can provide improved filtering. A smaller value can allow for faster transient response. For example, the 150pF  $C_{SNS}$  with 1k $\Omega$   $R_{SNS}$  adds 750ns (5RC) to the settling time of SNS voltage.

**Table 8-1. SNS Ripple (Typical measurement at  $V_{BB} = 13.5V$ ,  $I_{LIM} = OPEN$ ,  $T_A = 25^\circ C$ )**

| $R_L$ (Load resistor) | $R_{SNS}$   | $C_{SNS}$ | PEAK-TO-PEAK RIPPLE WITHOUT $C_{SNS}$ (mV) | PEAK-TO-PEAK RIPPLE WITH $C_{SNS}$ (mV) |

|-----------------------|-------------|-----------|--------------------------------------------|-----------------------------------------|

| 10 $\Omega$           | 1k $\Omega$ | 150pF     | 105mV                                      | 50mV                                    |

| 2.2 $\Omega$          | 1k $\Omega$ | 150pF     | 157mV                                      | 55mV                                    |

Figure 8-10. SNS Pin Ripple Without  $C_{SNS}$  at  $V_{BB} = 13.5V$ ,  $I_{LIM} = \text{OPEN}$ ,  $R_L = 10\Omega$ ,  $R_{SNS} = 1k\Omega$  and  $T_A = 25^\circ\text{C}$

Figure 8-11. SNS Pin Ripple With  $150\text{pF}$   $C_{SNS}$  at  $V_{BB} = 13.5V$ ,  $I_{LIM} = \text{OPEN}$ ,  $R_L = 10\Omega$ ,  $R_{SNS} = 1k\Omega$  and  $T_A = 25^\circ\text{C}$

### 8.3.1.3 Multiplexing of Current Sense Across Channels

The SEL pin is used to multiplex the shared current-sense function between the two channels. Pulling the SEL pin high or low sets the corresponding channel to be output on the SNS pin if DIAG\_EN is high.  $\overline{FLT}$  still represents a global interrupt that goes low if a fault occurs on any channel. See [Table 8-6](#) for more details.

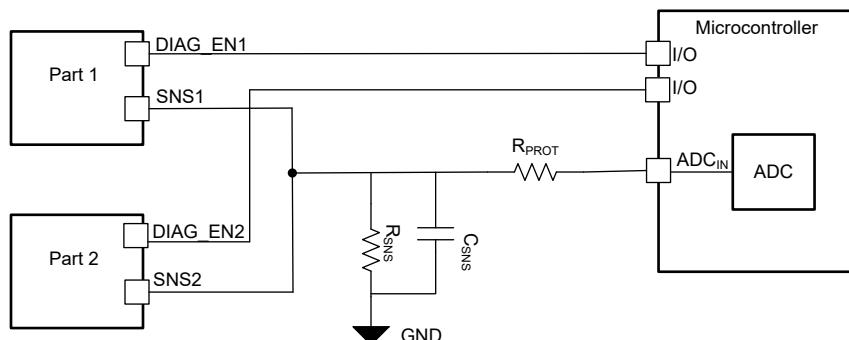

### 8.3.1.4 Multiplexing of Current Sense Across Devices

[Figure 8-12](#) shows SNS pin sharing across two devices using common  $R_{SNS}$  resistor. Similarly multiple devices can be configured to share SNS pin. When DIAG\_EN is set high, the selected channel current sense output can be enabled using associated ENx and SEL signal, and a current proportional to the load current ( $I_{LOAD}/K_{SNS}$ ) flows out of the SNS pin through the external sense resistor to ground. This current is reflected as a voltage that can be measured by an MCU's ADC input. When DIAG\_EN is set low, the SNS pin is placed in a high-impedance (tri-state) condition. This feature allows multiple TPS2HC08-Q1 devices to share the same sense resistor and ADC input pin, as only one device can drive the SNS pin at any given time.

$K_{SNS}$  is designed such that SNS pin current at maximum rated load current is same across the device family. This allows for devices with different current ratings to be multiplexed by having same  $R_{SNS}$  resistor and ADC full scale range.

When implementing current sense multiplexing across devices, the disabled state SNS pin leakage current ( $I_{SNS\text{leak\_disabled}}$ ) from devices (with DIAG\_EN set to low) introduces measurement error when reading the current from an active device. For TPS2HC08-Q1 device, the disabled state SNS pin leakage is very low (typical few nA), allowing higher count of devices to be multiplexed.

Figure 8-12. SNS Multiplexing Across Multiple Devices

### 8.3.2 Overcurrent Protection

The TPS2HC08-Q1 provides thermal shutdown and current limiting protection during overcurrent events to protect the internal power MOSFETs. These protection functions are enabled when the device is in the active

state. Each channel has an independent thermal shutdown and current limiting circuitry. The current limit fault gets asserted at about 80% ( $I_{CL\_FLT\_Trip}$ ) of set current limit value.

### 8.3.2.1 Adjustable Current Limit

The TPS2HC08-Q1 offers a high accuracy, adjustable current which enables higher reliability and provides protection to the power supply during a short circuit or power up with large capacitance. An adjustable current limit can also save system costs by reducing PCB traces, connector size, and the capacity of the preceding power stage by setting the current limit at a lower level.

The current limit of the device can be adjusted via an external resistor on the ILIM pin. The value which is set by the ILIM pin is applied to both the channels. The device provides ILIM settings with a thermal regulated current limit which adjusts the current limit level based on the relative temperature of the FET and the controller. This avoids fast heating of the FET and delays the trigger of relative thermal shutdown, which enables the device to charge up large capacitors at startup. With ILIM pin shorted to GND, the device current limit can be configured without thermal regulation where the device limits the current at the set ILIM value. [Table 8-2](#) details the different settings that are possible based on the ILIM pin configuration.

**Table 8-2. Current Limit Settings Through ILIM Pin**

| $R_{LIM}$ VALUE on ILIM pin                        | TYP $I_{CL} = K_{CL} / R_{LIM}$ | THERMAL REGULATION |

|----------------------------------------------------|---------------------------------|--------------------|

| ILIM = GND or $R_{LIM} < 20\text{k}\Omega$         | Maximum setting of 25A          | Disabled           |

| $R_{LIM} = 20\text{k}\Omega$                       | 25A                             | Enabled            |

| $20\text{k}\Omega < R_{LIM} < 66.66\text{k}\Omega$ | $I_{CL} = K_{CL} / R_{LIM}$     | Enabled            |

| $R_{LIM} = 66.66\text{k}\Omega$                    | 7.5A                            | Enabled            |

| ILIM = Open or $R_{LIM} > 66.66\text{k}\Omega$     | Minimum setting of 7.5A         | Enabled            |

The device also offers a fast-trip circuit breaker function which is used when a short-circuit occurs while a channel is enabled which is also known as a hot-short. Once the  $I_{CB}$  threshold is reached, the device quickly turns off the channel to protect the internal MOSFET. Additionally, the device provides a current limit foldback function at higher voltages to help protect the internal power MOSFETs during high  $V_{DS}$  events.

The different overcurrent events that can occur in a system are:

- hot-short

- enable into short

- current overload (slow creep)

A hot-short occurs when a channel is enabled and a short-circuit condition is applied to the output of a channel. Enabling in to short occurs when there is already a short on the output of the MOSFET and the channel is enabled into the short-circuit condition. Current overload or also known as slow creep can occur if there is a slow rising overcurrent event at the output.

The next sections describe how the current limiting with thermal regulation and without thermal regulation work along with the circuit breaker and thermal shutdown functions to help protect against the various overcurrent conditions that can occur.

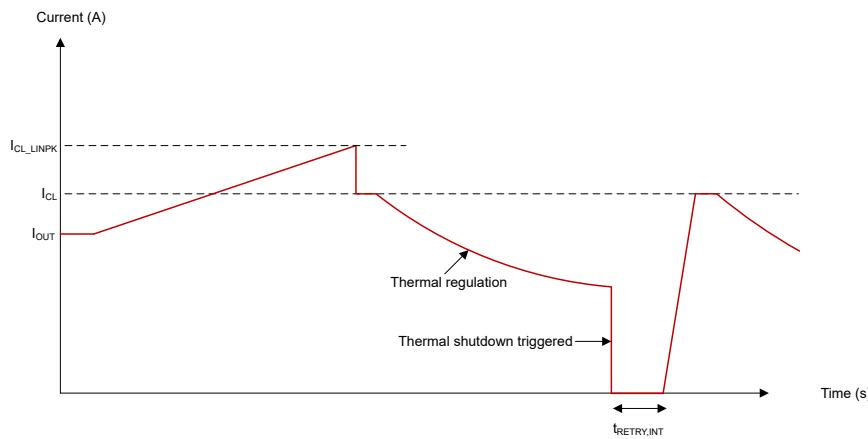

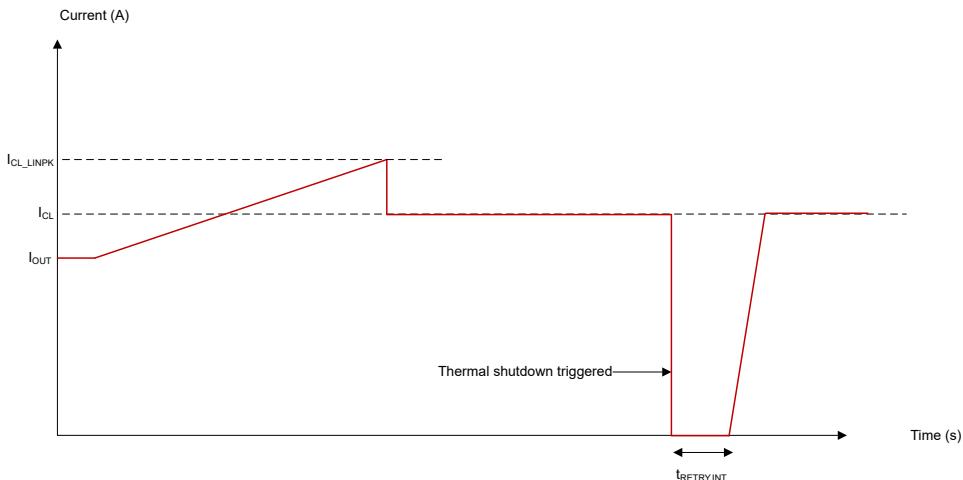

#### 8.3.2.1.1 Current Limiting With Thermal Regulation

Based on the ILIM setting the device can be configured to limit current with thermal regulation. The thermal regulation works by monitoring the relative temperature of the MOSFET ( $T_{J,FET}$ ) to the temperature of controller ( $T_{J,CONTROLLER}$ ) and reducing the current limit based on the relative temperature.

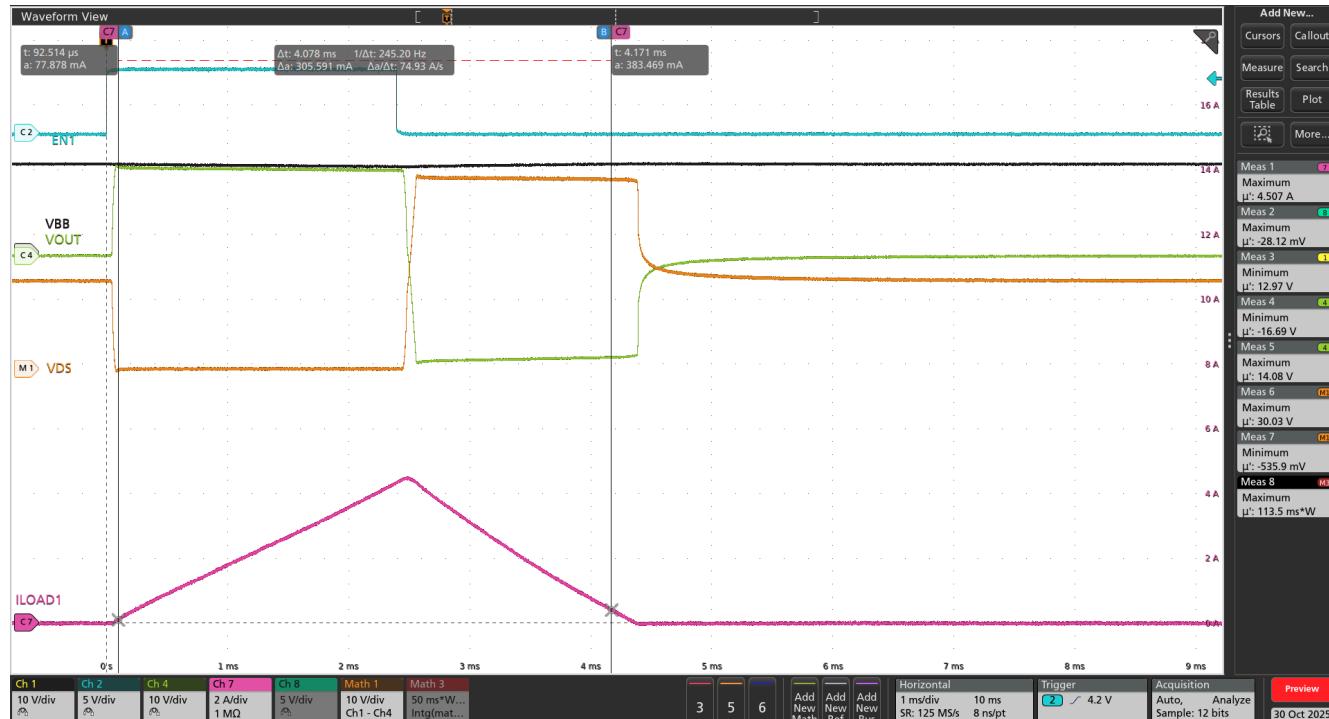

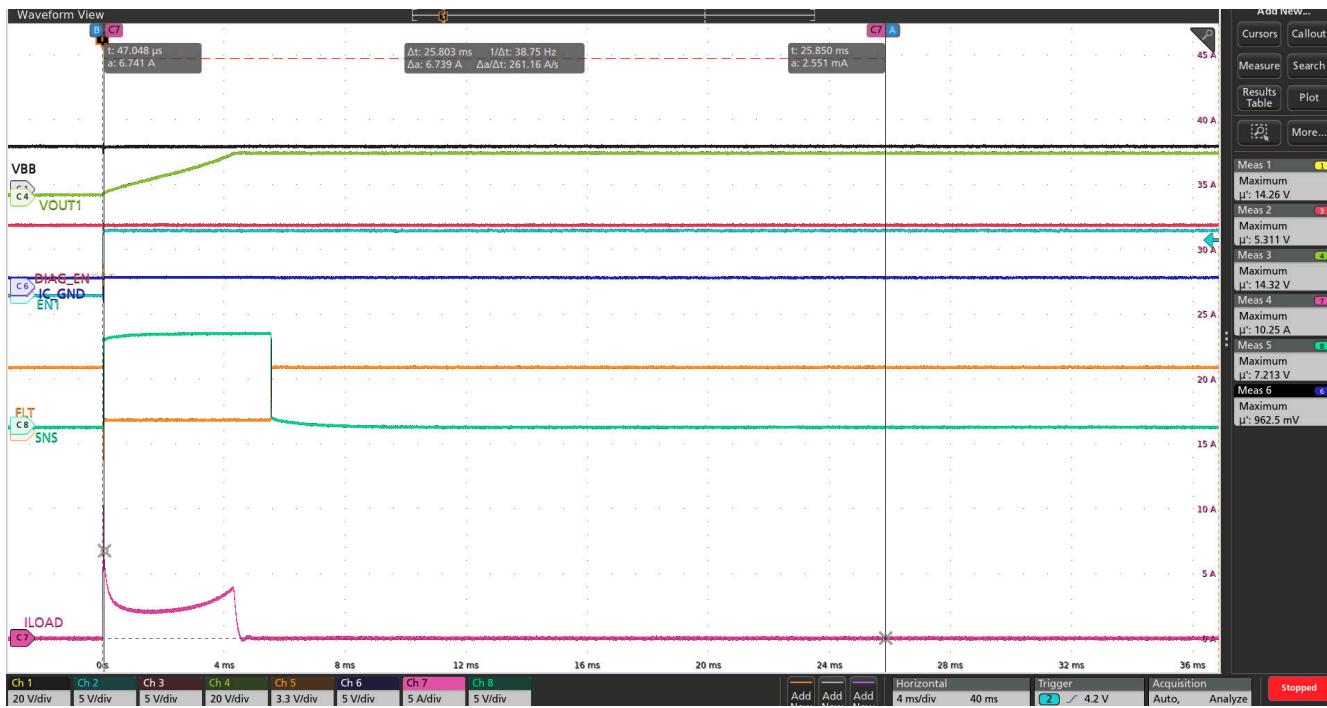

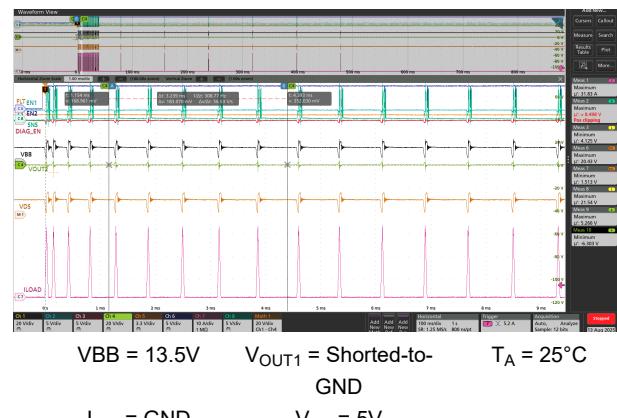

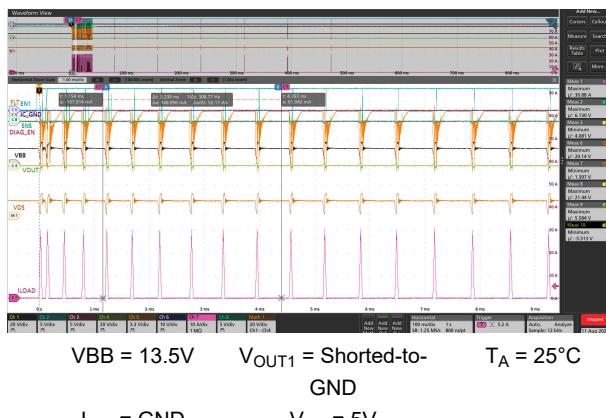

**Figure 8-13. On-State Short-Circuit Behavior with Thermal Regulation**

**Figure 8-14. Enable Into Short with Thermal Regulation**

**Figure 8-15. Overload Behavior (current creep) with Thermal Regulation**

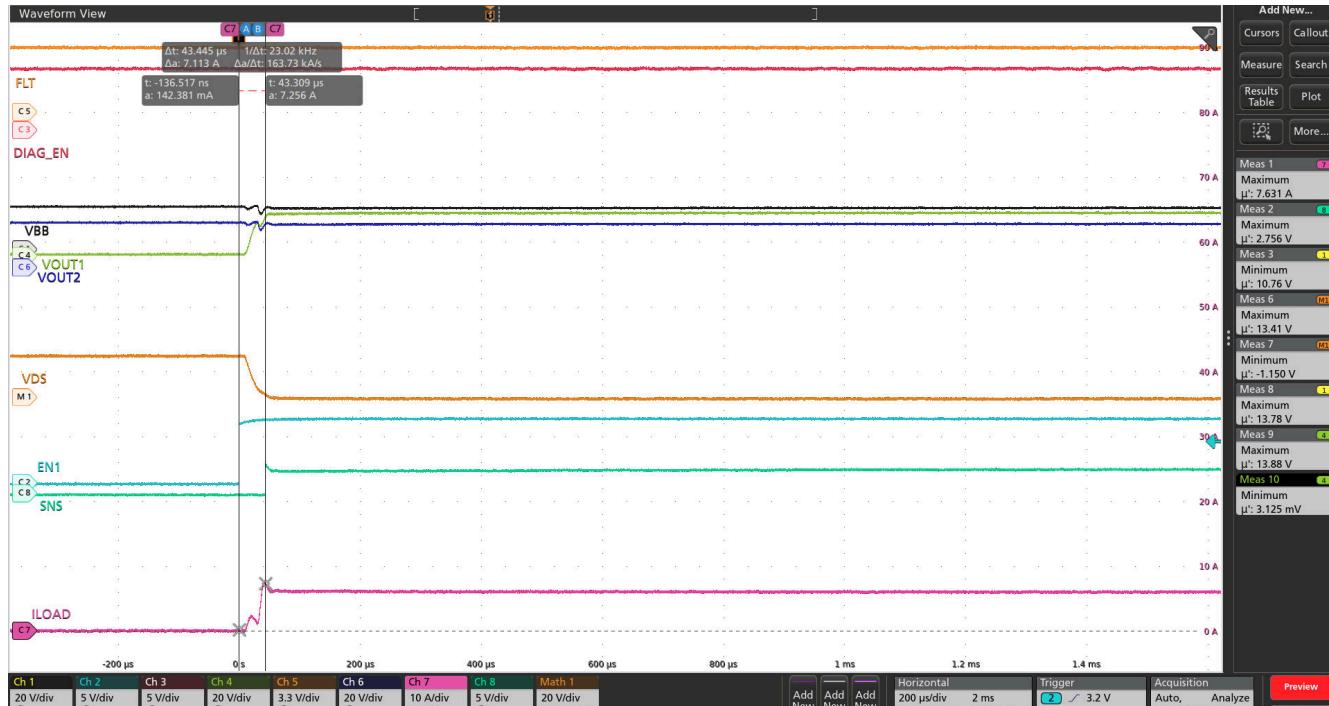

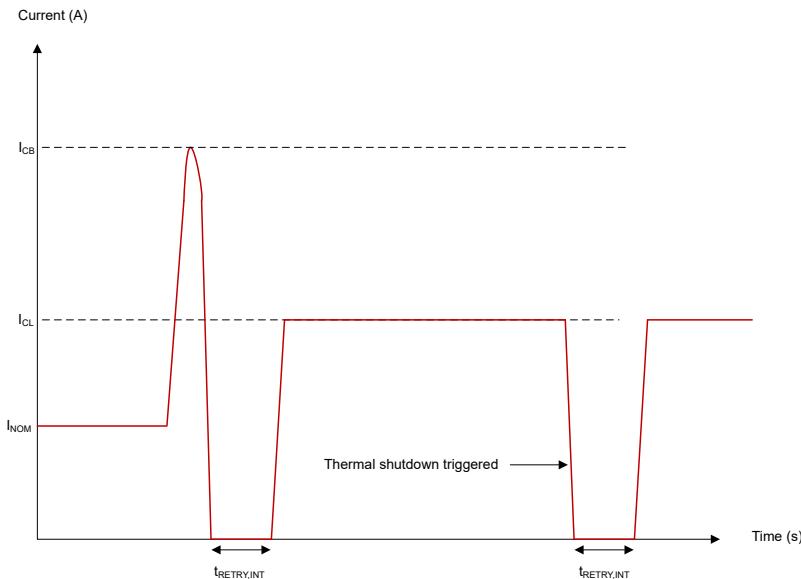

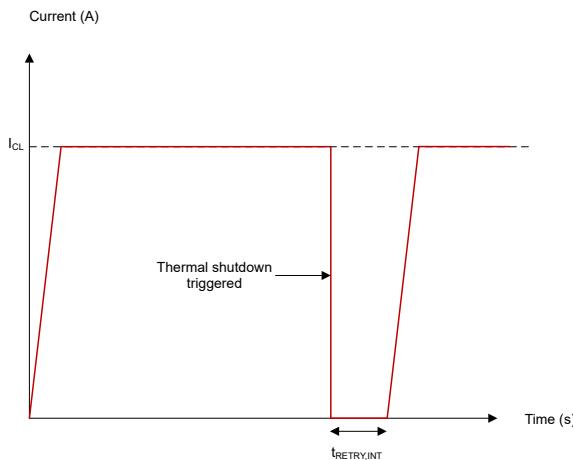

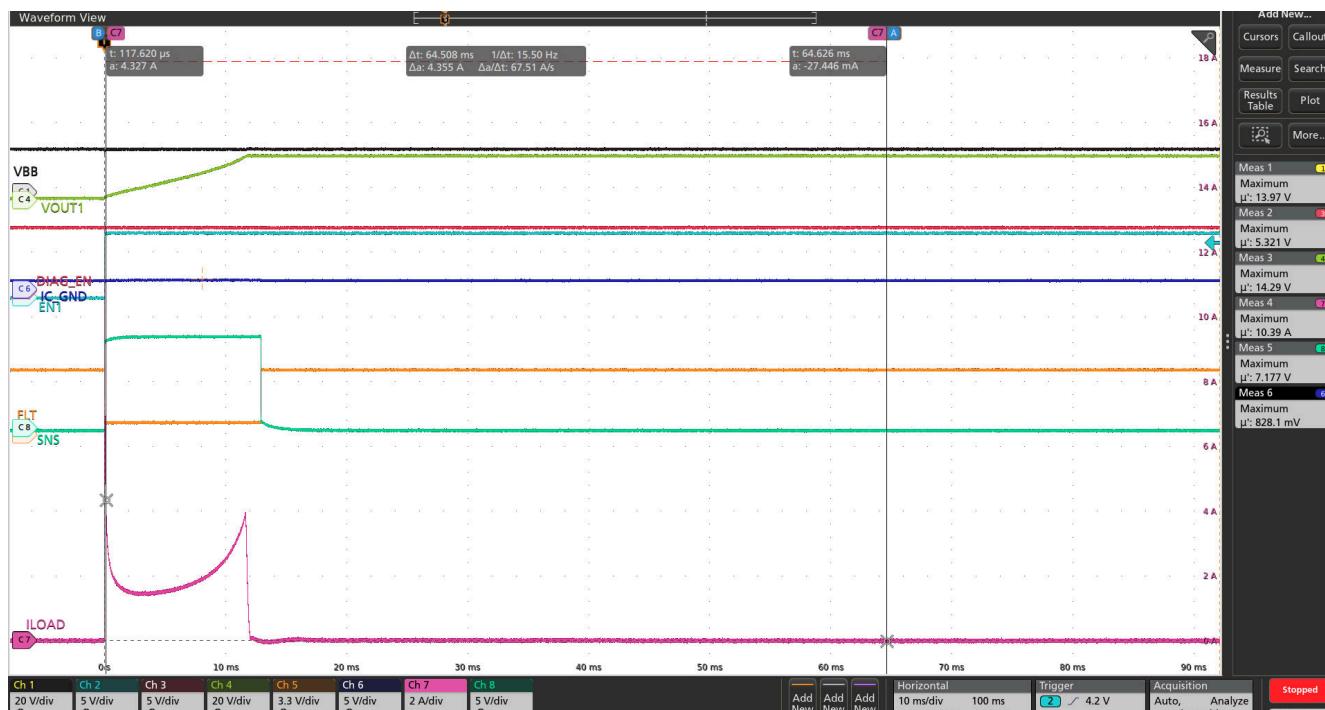

### 8.3.2.1.2 Current Limiting With No Thermal Regulation

Based on the ILIM setting, the device can be configured to limit current without thermal regulation. The device limits the current based on the setting at the ILIM pin. Applications where this can be used are bulb loads and motor loads with high inrush currents.

**Figure 8-16. On-State Short-Circuit Behavior with No Thermal Regulation**

**Figure 8-17. Enable Into Short with No Thermal Regulation**

**Figure 8-18. Overload Behavior (current creep) with No Thermal Regulation**

#### 8.3.2.1.3 Current Limit Foldback

To protect the MOSFET from overcurrent at high  $V_{DS}$  voltages the device offers a current limit foldback mechanism. If the ILIM is set to greater than nominal load current value and the VBB voltage is greater than  $V_{DET1}$  then the current limit folds back to 1/2 of current limit setting. If the VBB voltage is above  $V_{DET2}$ , the current limit folds back 1/3 of current limit setting. [Figure 6-32](#) shows device current limit foldback behavior across VBB voltage.

#### 8.3.2.1.4 Current Limit Accuracy

The adjustable current limit of the device can be set using [Equation 3](#) for valid range of  $R_{LIM}$  resistor mentioned in [Table 8-2](#).

$$R_{LIM} = K_{CL} / I_{CL} \quad (3)$$

The accuracy of current limit depends on  $R_{LIM}$  resistor tolerance and  $K_{CL}$  parameter variation ( $K_{CL\_min}$ ,  $K_{CL\_max}$ ) mentioned in [Section 6.5](#). For example, for 33.2k $\Omega$   $R_{LIM}$  resistor with 1% tolerance, the  $I_{CL}$  can be calculated as below.

$$I_{CL}(\max) = K_{CL\_max} / R_{LIM\_min}, \text{ where } R_{LIM\_min} = 0.99 * R_{LIM}$$

$$I_{CL}(\min) = K_{CL\_min} / R_{LIM\_max}, \text{ where } R_{LIM\_max} = 1.01 * R_{LIM}$$

For  $R_{LIM}$  GND and OPEN case,  $K_{CL}$  parameter variation contributes to  $I_{CL}$  variation.

#### 8.3.2.2 Thermal Shutdown

The device includes a temperature sensor on each power FET and within the controller portion of the device to monitor the temperature of each FET ( $T_{J,FET}$ ) and the temperature of the controller ( $T_{J,CONTROLLER}$ ). There are two cases that the device considers to be a thermal shutdown fault:

- **Relative thermal shutdown ( $T_{REL}$ ):**  $T_{J,FET} - T_{J,CONTROLLER} > T_{REL}$

- **Absolute thermal shutdown ( $T_{ABS}$ ):**  $T_{J,FET} > T_{ABS}$

If either the above faults occur, the relevant switch is turned off. Each channel is turned off based on the measurement of the temperature sensor for that channel. As a result, if the thermal fault is detected on only one channel, the other channel continues normal operation.

##### 8.3.2.2.1 Relative Thermal Shutdown

A relative thermal shutdown event can occur when there is a large peak power event such as a short-to-ground event where the FET temperature ( $T_{J,FET}$ ) quickly rises relative to the controller temperature ( $T_{J,CONTROLLER}$ ). Once the relative temperature ( $T_{J,FET} - T_{J,CONTROLLER}$ ) exceeds  $T_{REL}$  the relevant channel is turned off.

### 8.3.2.2 Absolute Thermal Shutdown

An absolute thermal shutdown occurs when the FET temperature ( $T_{J,FET}$ ) rises above  $T_{ABS}$ . This can occur when a channel is subjected to long durations of overcurrent such as a permanent short use case. Once the FET temperature ( $T_{J,FET}$ ) exceeds  $T_{ABS}$  the relevant channel is turned off.

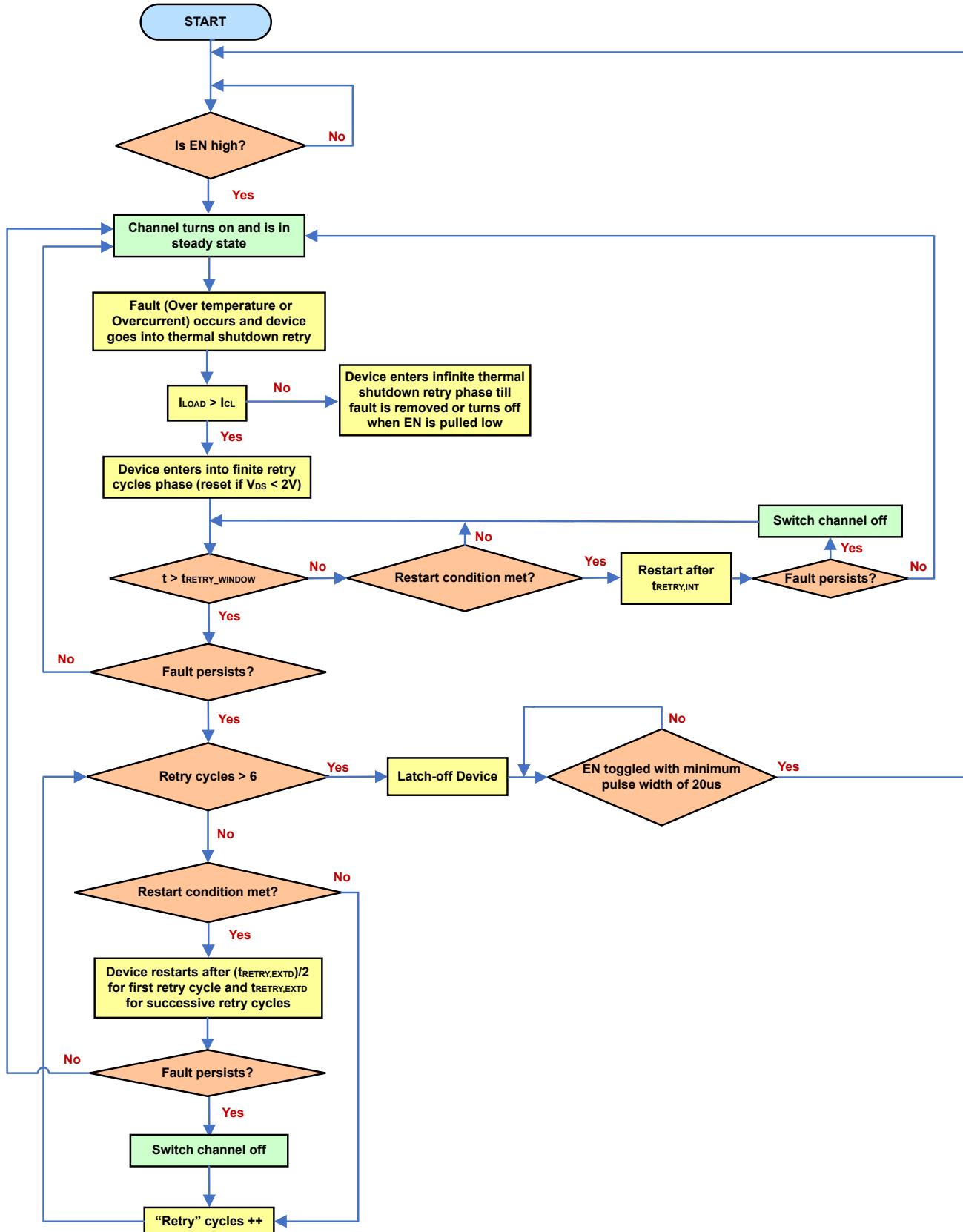

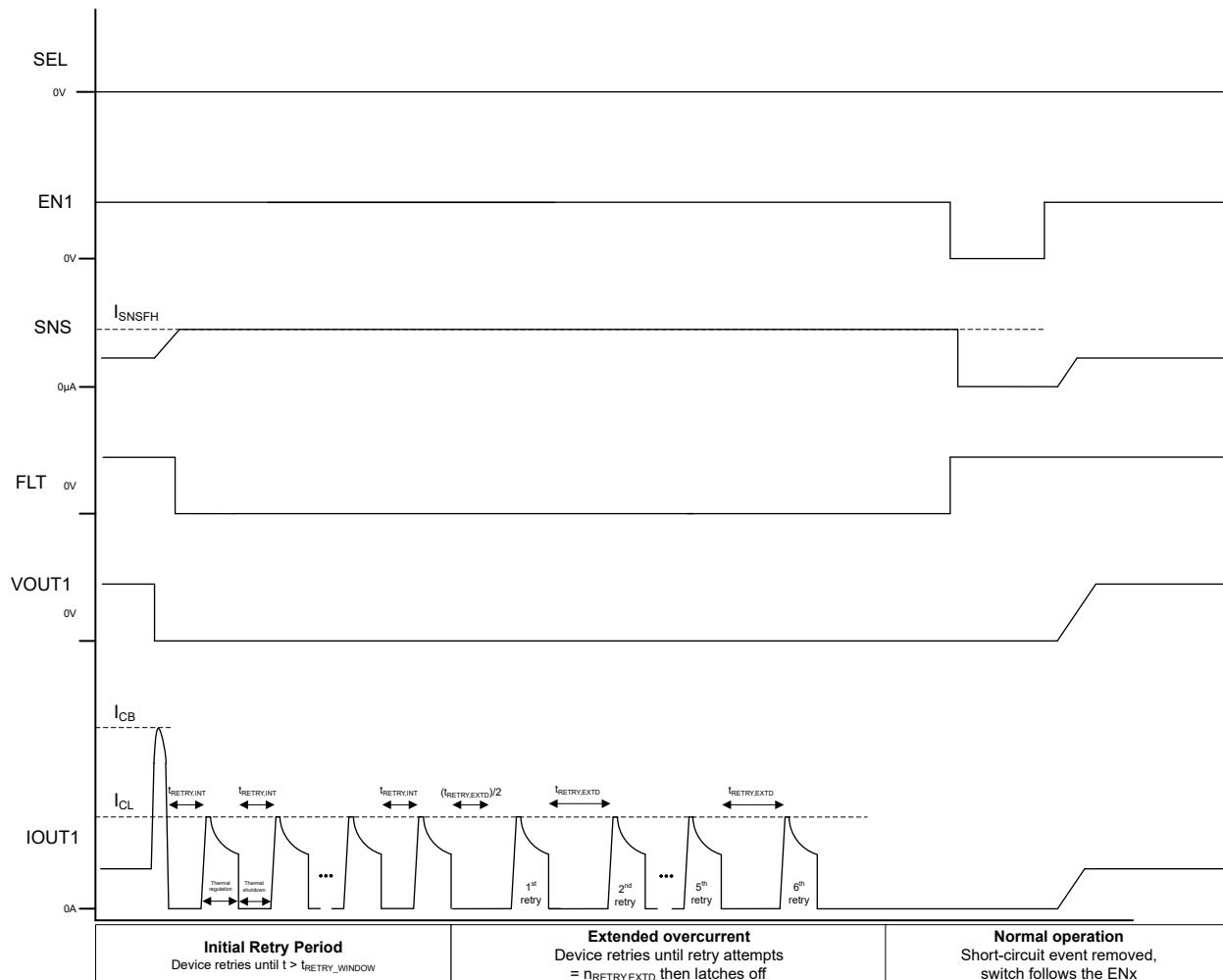

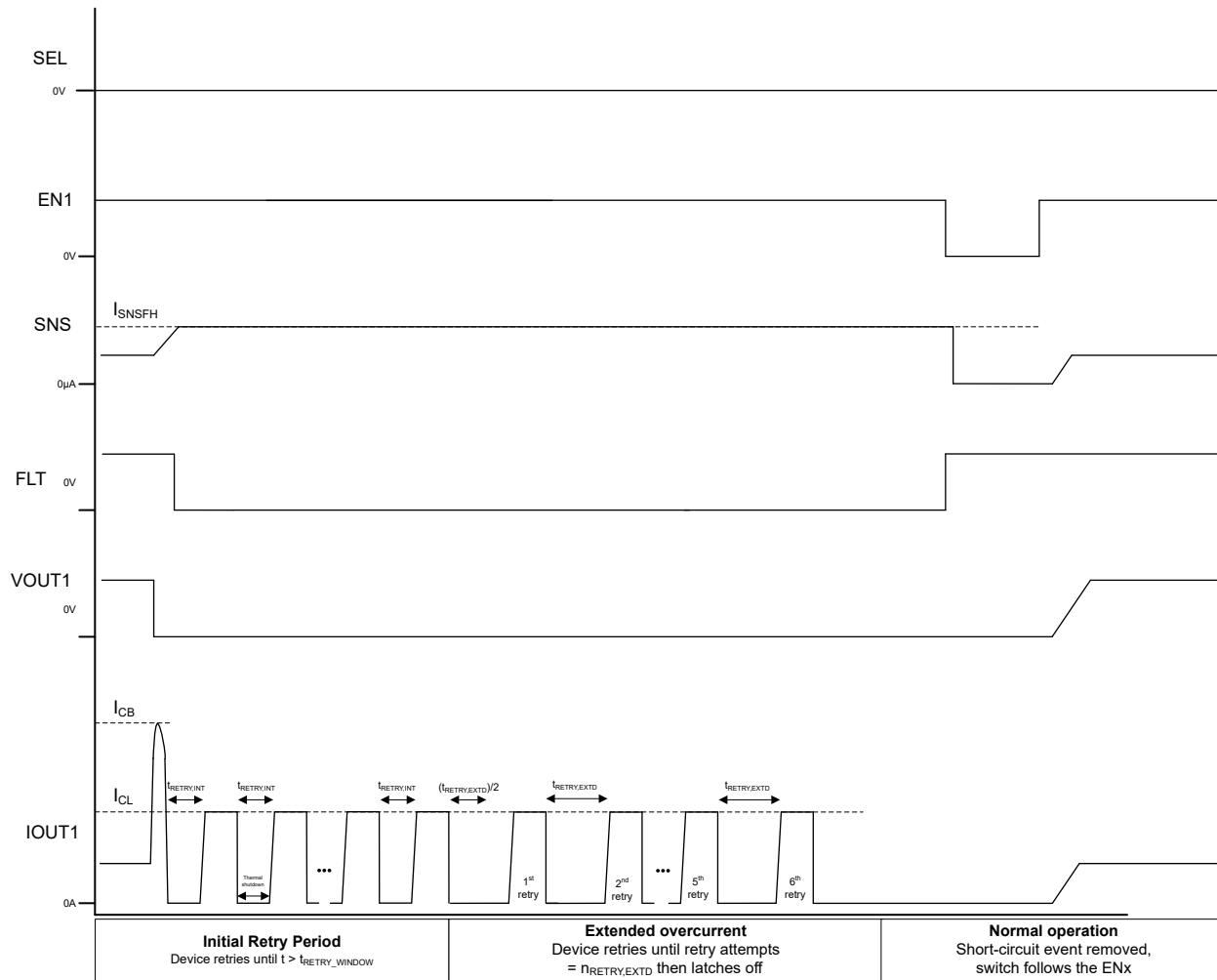

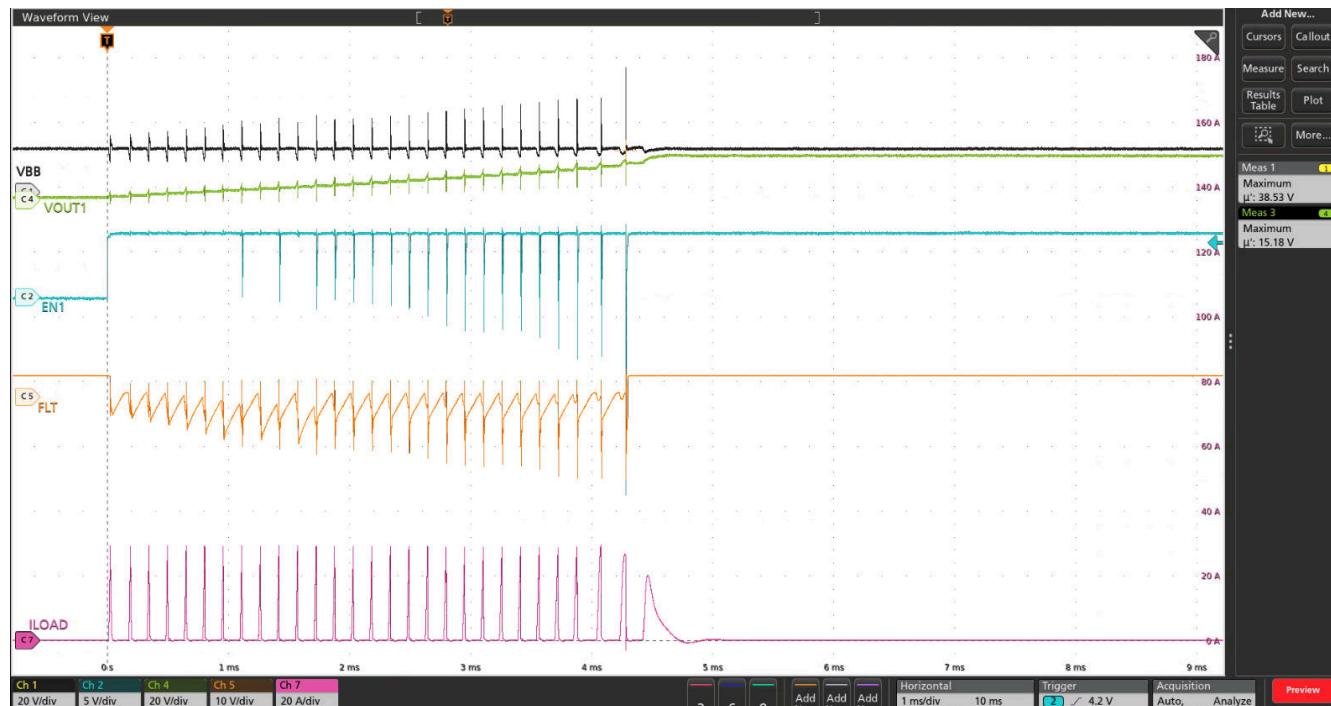

### 8.3.3 Retry Protection Mechanism From Thermal Shutdown

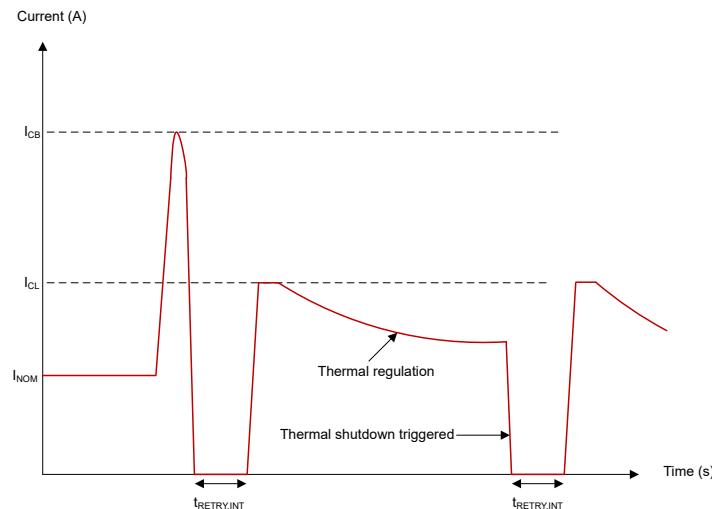

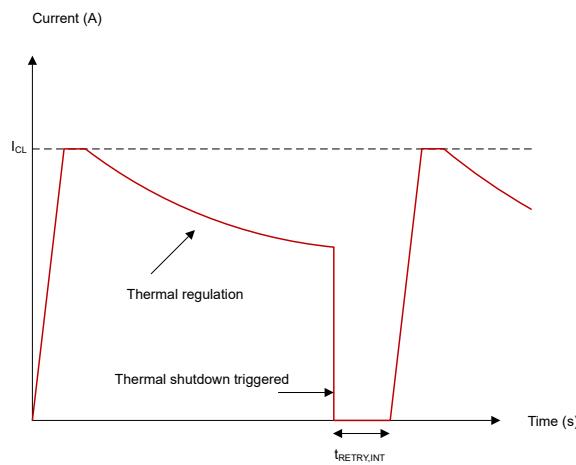

When a thermal shutdown occurs, the associated device channel shuts off and implements a retry protection mechanism to improve system reliability. [Figure 8-20](#) explains how the affected channel responds depending on the load current and duration of the overcurrent event.

For load current lower than current limit, device enters into infinite thermal shutdown retry cycles phase until the device recovers from the thermal shutdown fault. In this case, the device turn off time depends on cooling time needed with inherent 200 $\mu$ s delay.

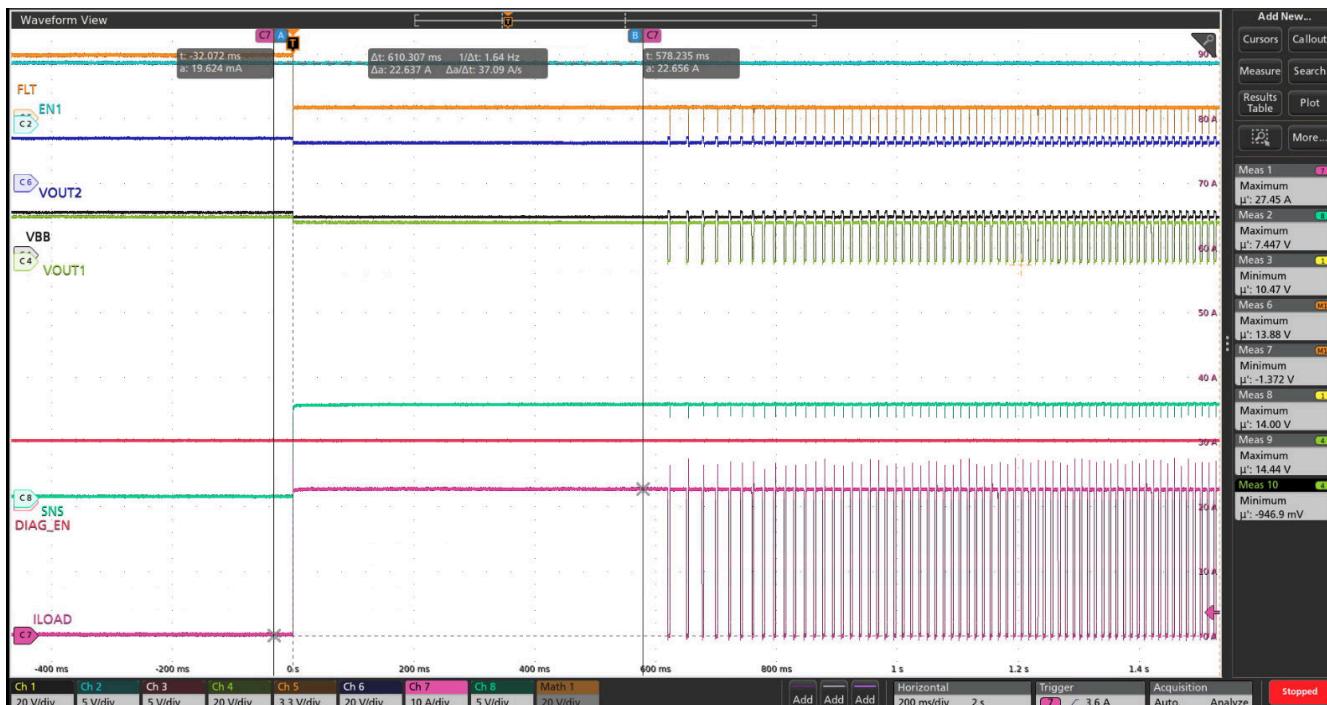

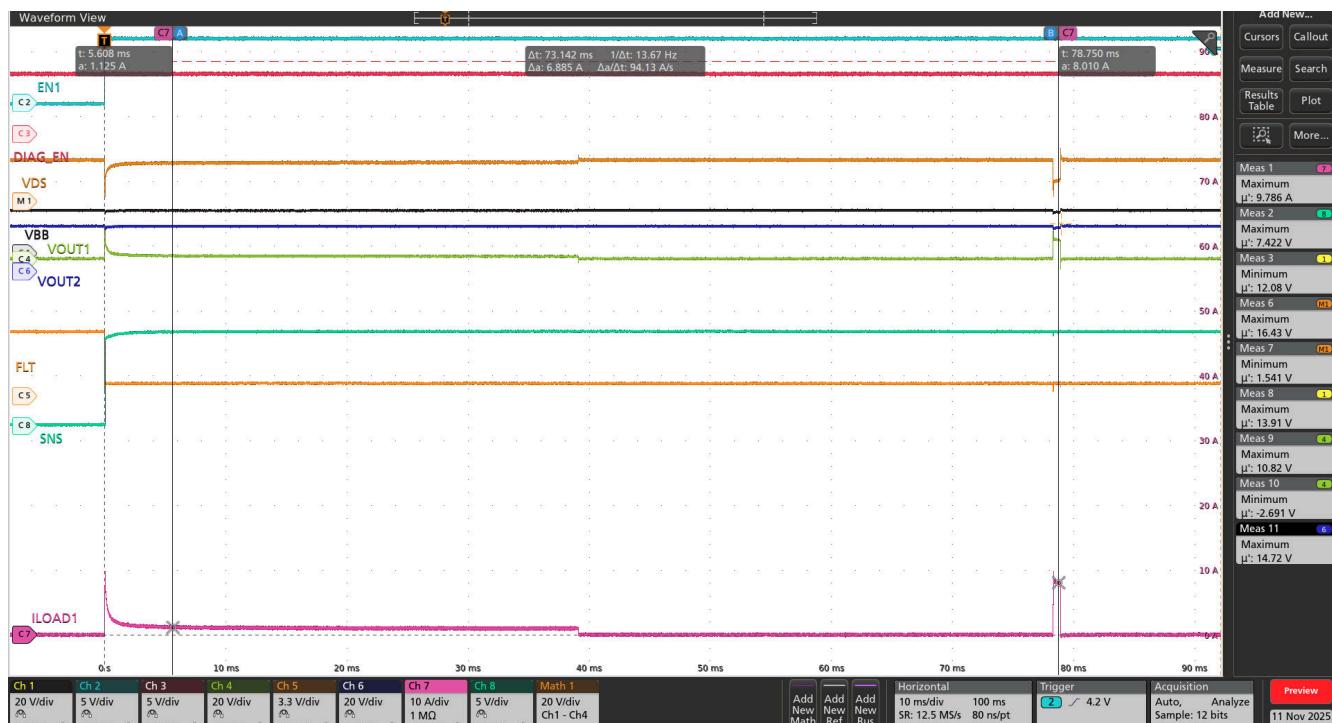

**Figure 8-19. Device Enters Into Infinite Thermal Shutdown Retry Phase For Load Current (22A electronic load) Less Than Current Limit (ILIM = GND)**

For load current higher than current limit, device implements a finite retry cycles phase protection mechanism based on the duration of the overcurrent event, that can trigger when either of the below fault conditions occur:

1. **Absolute thermal shutdown ( $T_{ABS}$ ):**  $T_{J,FET} > T_{ABS}$

2. **Relative thermal shutdown ( $T_{REL}$ ):**  $T_{J,FET} - T_{J,CONTROLLER} > T_{REL}$