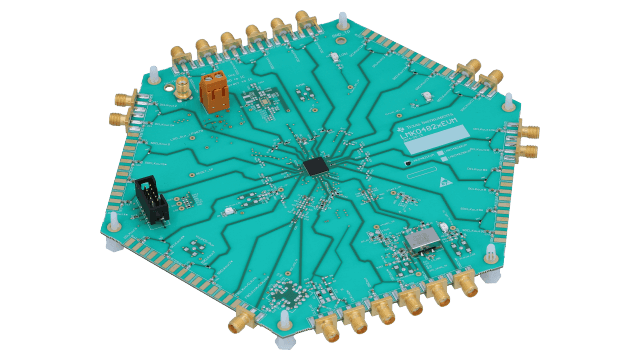

Merkmale von LMK04821EVM

- JEDEC JESD204B-Unterstützung zur Erzeugung von gepulsten SYSREF.

- Evaluierungsplatine mit CodeLoader-Software konfigurierbar.

- Für differenzielle oder einseitig geerdete/LVCMOS-Eingangstaktgeber

- LVPECL-Ausgänge können mit Balun an Prüfvorrichtungen angeschlossen oder durch Verwendung eines 50-Ohm-Abschlusses an nicht angeschlossenen Ausgängen einseitig geerdet werden.

Beschreibung von LMK04821EVM

Das LMK04821EVM unterstützt die LMK0482x-Produktfamilie, die branchenweit leistungsstärksten Bausteine zur Taktkonditionierung mit JEDEC JESD204B-Unterstützung. Die Dual-Loop-PLLatinum™ -Architektur ermöglicht Jitter unter 100 fs (12 kHz bis 20 MHz) mit einem rauscharmen VCXO-Modul. Die Dual-Loop-Architektur besteht aus zwei Hochleistungs-Phase-Locked-Loops (PLL), einer rauscharmen Quarzoszillatorschaltung und einem spannungsgesteuerten Hochleistungs-Oszillator (VCO).

VCXO mit 122,88 MHz ist vorinstalliert. Benutzer kann VCXO gegen eigene benutzerdefinierte VCXO tauschen oder über SMA-Anschlüsse verbinden.

Normalerweise wird ein interner VCO PLL2 verwendet, jedoch besteht ausreichend Platz für einen externen VCO, oder der Benutzer kann einen externen VCO über SMA-Anschlüsse verbinden.

PLL-Schleifenfilter sind bereits in der Standardkonfiguration vorinstalliert. Wenn Sie VCXO oder VCO oder andere Betriebsparameter ändern, kann der Schleifenfilter überarbeitet werden. Das Taktgeber-Design Tool oder der WEBENCH Clock Architect können zur Überarbeitung des Schleifenfilters verwendet werden.