Características para LMK5C33216EVM

- Three Digital PLL (DPLL) with programmable bandwidths and three fractional analog PLLs (APLLs) for flexible clock generation

- Two reference inputs to the DPLL supporting hitless switching & holdover

- 16 output clocks. Outputs driven by BAW are capable of sub 50-fs RMS phase jitter (12 kHz to 20 MHz)

- Flexible oscillator sources: onboard TCXO, or one of several footprints for other XO, TCXO, OCXO, or external SMA input options

- On-chip EEPROM for custom start-up clock configurations

Descripción de LMK5C33216EVM

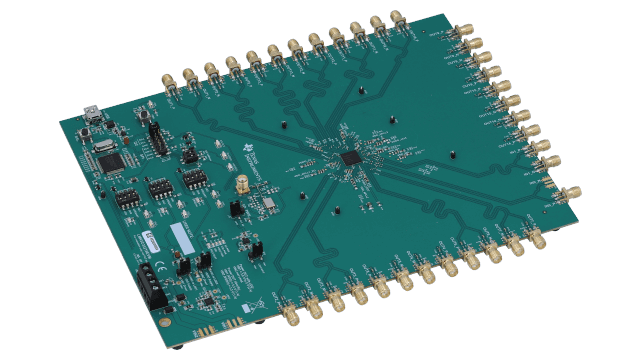

The LMK5C33216EVM is an evaluation module (EVM) for the LMK5C33216 network clock generator and synchronizer. The EVM can be used for device evaluation, compliance testing, and system prototyping. The LMK5C33216 integrates three Analog PLLs (APLL) and three Digital PLLs (DPLL) with programmable loop bandwidth. The EVM includes SMA connectors for clock inputs, oscillator inputs, and clock outputs to interface the device with 50-Ω test equipment. The onboard TCXO allows the LMK5C33216 to be evaluated in free-running, locked, or holdover mode of operation. The EVM can be configured through the onboard USB microcontroller (MCU) interface using a PC with TI's TICS Pro software graphical user interface (GUI). TICS Pro can be used to program the LMK5C33216 registers.