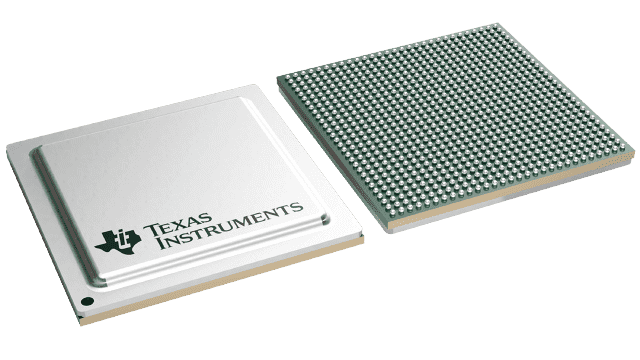

Información de empaque

| Encapsulado | Pines FCBGA (CYP) | 841 |

| Rango de temperatura de funcionamiento (℃) -40 to 100 |

| Cant. de paquetes | Transportador 44 | JEDEC TRAY (5+1) |

Características para TMS320C6672

- Two TMS320C66x DSP Core Subsystems at 1.00 GHz and 1.25GHz

- 80 GMAC/40 GFLOP @ 1.2GHz

- 32KB L1P, 32KB L1D, 512KB L2 Per Core

- 2 MB Shared L2

- Multicore Navigator and TeraNet Switch Fabric - 2 Tb

- Network Coprocessors- Packet Accelerator, Security Accelerator

- Four Lanes of SRIO 2.1 - 5 Gbaud Per Lane Full Duplex

- Two Lanes PCIe Gen2 - 5 Gbaud Per Lane Full Duplex

- HyperLink - 50Gbaud Operation, Full Duplex

- Ethernet MAC Subsystem - Two SGMII Ports w/ 10/100/1000 Mbps operation

- 64-Bit DDR3 Interface (DDR3-1600) - 8 GByte Addressable Memory Space

- 16-Bit EMIF - Async SRAM, NAND and NOR Flash Support

- Two Telecom Serial Ports (TSIP) - 2/4/8 Lanes at 32.768/16.384/8.192

- UART Interface

- I2C Interface

- 16 GPIO Pins

- SPI Interface

- Sixteen 64-Bit Timers

- Three On-Chip PLLs

Descripción de TMS320C6672

The TMS320C6672 Multicore Fixed and Floating Point Digital Signal Processor is based on TI's KeyStone multicore architecture. Integrated with two C66x CorePac DSPs, each core runs at 1.0 to 1.25 GHz enabling up to 2.5 GHz. The device supports high-performance signal processing applications such as mission critical, medical imaging, test, and automation. The C6672 platform is power efficient and easy to use. The C66x CorePac DSP is fully backward compatible with all existing C6000 family of fixed and floating point DSPs.