# TMS320C20x ESSP peripheral update

This document contains the Enhanced Synchronous Serial Port (ESSP) specification designed in TMS320F206, TMS320C203B, TMS320C206 and TMS320LC206 digital signal processors.

## **TABLE OF CONTENTS**

| A.1 IMS320C20x Enhanced Synchronous Serial Port (ESSP) Features | 4  |

|-----------------------------------------------------------------|----|

| A.2 Enhanced Synchronous Serial Port (ESSP)                     | 5  |

| A.3 Serial Port pins                                            | 6  |

| A.4 SSP Registers                                               |    |

| A.4.1 Synchronous Data Transmit/Receive Register (SDTR)         |    |

| A.4.2 Synchronous Serial Port Control Register (SSPCR)          | 7  |

| A.4.3 Selecting CLKX and FSX source                             | 9  |

| A.5 New ESSP Registers                                          | 9  |

| A.5.1 Synchronous Serial Port Status Register (SSPST)           | 9  |

| A.5.2 Synchronous Serial Port Multichannel Register (SSPMC)     | 10 |

| A.5.3 Synchronous Serial Port Count Register (SSPCT)            | 12 |

| A.6 Pre-scalars as general purpose counter                      | 12 |

| A.7 Programmable internal CLKX and FSX rates                    | 14 |

| A.8 ESSP register programming considerations                    | 16 |

| A.9 Multi-channel frames                                        |    |

| A.9.1 8-bit Four channel interface timings                      |    |

| A.9.2 16-bit Four channel interface timings                     |    |

|                                                                 |    |

# **ADVANCE INFORMATION**

| Figure    | List of Figures                                                    | page |

|-----------|--------------------------------------------------------------------|------|

| Figure 1  | Synchronous Serial Port Block Diagram                              | 5    |

| Figure 2. | Synchronous Serial Port Control Register                           | 7    |

| Figure 3. | Synchronous Serial Port Status Register -SSPST (I/O address FFF2h) | 9    |

| Figure 4. | Synchronous Serial Port Multi-channel Register - SSPMC (FFF3h)     | 10   |

| Figure 5. | Synchronous Serial Port Count Register -SSPCT (FFFBh)              | 13   |

| Figure 6  | Four-channel codec interface                                       | 17   |

| Figure 7  | Four 8-bit codec interface timing                                  | 17   |

| Figure 8  | Four 16-bit Codec interface timings                                | 18   |

| Table                     | List of Tables                                   | page |

|---------------------------|--------------------------------------------------|------|

| Table 1. TMS320C20x En    | hanced Synchronous Serial Port Interface signals | 6    |

| Table 2. ESSP Registers   | ,                                                |      |

|                           | nmary                                            |      |

|                           | lock (CLKX) and Frame sync (FSX) sources         |      |

|                           | Bit Summary                                      |      |

| Table 6. Typical CLKX ,FS | SX rates and their pre-scalar values             | 15   |

|                           | uration - Burst Mode                             |      |

|                           |                                                  | 20   |

## A.1 TMS320C20x Enhanced Synchronous Serial Port (ESSP) Features

- Full-Duplex, double-buffered Synchronous Serial Port

- Highly Flexible Operation:

- Burst and Continuous modes

- Supports 8- and 16-bit word lengths

- Multi-channel mode with glueless interface to as many as four voice-band or telephony codecs for telecommunications applications such as line cards.

- Serial Peripheral Interface (SPI) mode

- Independent four-level deep FIFO for both the receive and transmit sections

- Programmable FIFO level interrupts to reduce software overhead

- FIFO level status bits

- Various clocking options to ease interfacing in many applications

- Internal shift clock, CLKX, derived from an independent 8-bit pre-scalar

- Internal frame sync, FSX, derived from an independent 8-bit pre-scalar

- Polarity control on shift clock, CLKX, and frame sync pulse, FSX

- High impedance control on data transmit pin DX for TDM applications

- Pre-scalars are configurable as a general-purpose 16-bit counter.

- Fast Transfer Rate:

- 20 Mbits/s at 25ns cycle time

## A.2 Enhanced Synchronous Serial Port (ESSP)

A full duplex, (bi-directional) 8/16 bit, synchronous serial port provides direct communication with serial devices such as codecs, serial A/D (analog to digital) converters, and other serial systems. The interface signals are compatible with codecs and many other serial devices. The serial port may also be used for intercommunication between processors in multiprocessing applications.

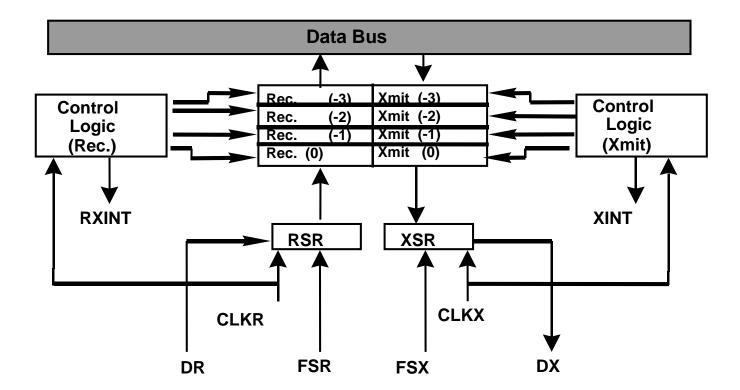

Figure 1 Synchronous Serial Port Block Diagram

Both receive and transmit operations have a four-word-deep First In First Out (FIFO) buffer. The advantage of having a FIFO is to alleviate the CPU from being loaded with the task of servicing a transmitted or received data packets on every interrupt, thus allowing a continuous communications stream of 8/16—bit data packets. The continuous mode provides operation that once initiated, requires no further frame synchronization pulses when transmitting at maximum packet frequency. The maximum transmission rate for both transmit and receive operations will be the CPU clock divided by two, i.e. CLKOUT1(frequency)/2. Therefore, the maximum rate is 10Mbit/s at 50nS, 14.28Mbit/s at 35ns, and 20Mbit/s at 25ns. The serial port is fully static and thus will function at arbitrarily low clocking frequencies.

Three signals are necessary to connect the transmit section of the transmitting device with the receive section of the receiving device for data transmission. The DX pin transmits the digital data serially. The transmit frame synchronization signal (FSX) initiates the transfer (at the beginning of the packet), and the transmit clock signal (CLKX) clocks the bit transfer. The corresponding pins on the receiving device are DR, FSR and CLKR, respectively.

## A.3 Serial Port pins

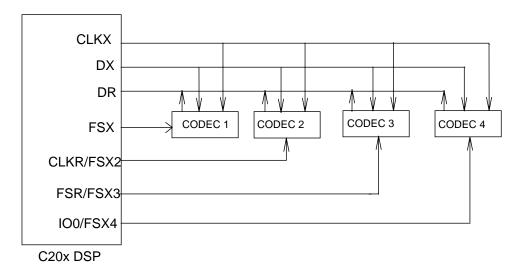

The Enhanced Synchronous Serial Port has seven pins for external interface. Table 1 explains the functions of these pins. In this table, SSP mode indicates that only one serial device is connected to the DSP chip i.e. the ESSP mode has not been activated. ESSP mode indicates that the ESSP features have been activated (by programming the ESSP registers) and that one or more serial devices have been connected to the DSP chip.

Table 1. TMS320C20x Enhanced Synchronous Serial Port Interface signals

| 100 | 'C20x         |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|---------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | PIN NAME      | I/O/Z | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |               |       | Serial Port Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 87  | CLKX          | I/O   | Transmit clock (input or output). Clock signal for clocking data from the serial port transmit shift register (XSR) to the data transmit (DX) pin. CLKX is an input if the MCM bit in the SSPCR is set to 0 (external CLKX). It can also be generated internally if the MCM bit is set to 1. Internal CLKX rate is determined by the input clock to the CLKX pre-scalar (CLXCT) and is governed by the equation  CLKX rate = CLKOUT1 / (2*(CLXCT+1)).  The generated CLKX can also feed a frame sync pre-scalar (FSXCT) to generate internal frame syncs synchronous to CLKX at variable rates. The pre-scalars for CLXK and FSX are defined in the I/O register SSPCT at FFF3h in I/O space. The input to the CLKX prescaler is CLKOUT1.                                                                                                                                                                                                                                                                                        |

| 84  | CLKR<br>/FSX2 | I/O   | Receive clock (input). In the SSP mode, this pin is the external clock signal for clocking data from the DR (data receive) pin into the RSR (receive shift register) and must be present during serial port transfers. If the serial port is not being used, this pin can be sampled as an input via the IN0 bit of the SSPCR.  Frame synchronization pulse 2 (output). In the ESSP mode, this pin transmits the frame sync for the second serial device connected to the serial port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 85  | FSR/FSX3      | I/O   | Frame synchronization pulse for receive (input). In the SSP mode, the falling edge of the FSR pulse initiates the data receive process.  Frame synchronization pulse 3 (output). In the ESSP mode, this pin transmits the frame sync for the third serial device connected to the serial port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 86  | DR            | I     | Serial data receive (input). Serial data is received into the receive shift register (RSR) from DR pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 89  | FSX           | I/O   | Frame synchronization pulse for transmit (input or output). The falling edge of the FSX pulse initiates the data transmit process beginning the clocking of the XSR. Following reset, FSX is an input. This pin may be selected by software to be an output when the TXM bit in the SSPCR is set to 1.  The Frame sync can be generated internally. The Frame sync rate can be either defined by the pre-scalar FSXCT or by the rate at which data is written into the transmit FIFO. The internal CLKX can also feed a frame sync pre-scalar to generate internal frame sync synchronous to CLKX and at variable rates. Internal FSX rate is determined by the input clock to the pre-scalar and is governed by the equation  FSX rate = CLKX pin clock /((2*(FSXCT+1))).  The Pre-scalars for CLXK and FSX are defined in the I/O register SSPCT at FFF3h in I/O space.  Frame synchronization pulse 1 (output). In the ESSP mode, this pin transmits the frame sync for the first serial device connected to the serial port. |

| 90  | DX            | 0     | Serial data transmit (output). Serial data is transmitted from transmit shift register (XSR) through DX pin. DX is placed in high impedance when not transmitting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 96  | IO0/FSX4      | I/O   | Input/Output 0 (input or output). In the SSP mode, this pin is used as a general-purpose input/output.  Frame synchronization pulse 4 (output). In the ESSP mode, this pin transmits the frame sync for the fourth serial device connected to the serial port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## A.4 SSP Registers

The Enhanced Synchronous Serial Port operates through the five registers (SDTR, SSPCR, SSPST, SSPMC, and SSPCT) that are mapped into the I/O space and two internal registers (XSR and RSR). The internal registers are not accessible to the user. Before the ESSP can be used, the control and status registers need to be programmed. The ESSP registers are listed in Table 2.

| Registers      | I/O<br>ADDRESS | Value at<br>Reset | Description                              |

|----------------|----------------|-------------------|------------------------------------------|

| SSP registers  |                |                   | I/O mapped registers                     |

| SDTR           | FFF0h          | xxxxh             | SSP Data transmit/receive register       |

| SSPCR          | FFF1h          | 0030h             | Synchronous Serial port control register |

| ESSP registers |                |                   |                                          |

| SSPST          | FFF2h          | 0000h             | SSP Status register                      |

| SSPMC          | FFF3h          | 0000h             | SSP Multi-channel register               |

| SSPCT -CLXCT   | FFFBh          | xx00h             | Shift clock pre-scalar (CLKX) low byte   |

| SSPCT -FSXCT   | FFFBh          | 00xxh             | Frame sync pre-scalar (FSX) high byte    |

|                |                |                   | Internal registers                       |

| XSR            |                |                   | Transmit shift register                  |

| RSR            |                |                   | Receive shift register                   |

|                |                |                   |                                          |

Table 2. ESSP Registers

Note: SDTR, SSPCR, XSR and RSR are common to both SSP and ESSP. SSPST, SSPMC and SSPCT are registers that are unique to ESSP.

## A.4.1 Synchronous Data Transmit/Receive Register (SDTR)

The Synchronous data transmit and receive register (SDTR) represents the top of both transmit and receive FIFOs. The only part of the FIFO that is accessible to the user is the SDTR register. To transmit data out of the serial port, data is written into the SDTR. To read the received data, data is read off the SDTR.

#### A.4.2 Synchronous Serial Port Control Register (SSPCR)

The synchronous serial port control register (SSPCR) controls the various modes and clock sources necessary to interface the serial port to external devices. The SSPCR register bit definitions are listed in Table 3.

Figure 2. Synchronous Serial Port Control Register

| 15   | 14   | 13    | 12   | 11  | 10  | 9   | 8   | 7   | 6   | 5    | 4    | 3   | 2   | 1   | 0   |

|------|------|-------|------|-----|-----|-----|-----|-----|-----|------|------|-----|-----|-----|-----|

| FREE | SOFT | TCOMP | RFNE | FT1 | FT0 | FR1 | FR0 | OVF | IN0 | XRST | RRST | TXM | MCM | FSM | DLB |

| R/W  | R/W  | R     | R    | R/W | R/W | R/W | R/W | R   | R   | R/W  | R/W  | R/W | R/W | R/W | R/W |

x - Indicates undefined values or value based on the pin levels at reset.

Table 3. SSPCR Bits Summary

| Bit      | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | DLB          | The Digital Loopback mode Bit can be used to put the serial port in digital loopback mode. When DLB=1, DR and FSR are connected to DX and FSX respectively, through multiplexers. Additionally, CLKR is driven by CLKX if MCM=1. If MCM=0, CLKR is taken from the CLKR pin of the device. This configuration allows CLKX and CLKR to be tied together externally and supplied by a common external clock source. If DLB=0, DR, FSR and CLKR are taken from the respective device pins. Note that TXM must be set to one for proper operation in DLB mode. Note also that the FSX and DX signals appear on the device pins when DLB=1, but FSR and DR do not. DLB =0 for normal device operation. |

| 1        | FSM          | The Frame Synch Mode Bit specifies whether frame synchronization pulses are required between consecutive word transfers. If FSM=1, the serial port is operated in burst mode, i.e. a frame sync pulse is required on FSX/FSR for the transmission/reception of each word. If FSM=0, the serial port is operated in the continuous mode, i.e. one frame sync pulse initiates transmission/reception of multiple words.                                                                                                                                                                                                                                                                            |

| 2        | MCM          | The Clock Mode Bit specifies the clock source for CLKX. If MCM=0, CLKX signal is taken from the CLKX pin. If MCM=1, CLKX is driven by an on-chip clock source having a frequency equal to one-half of CLKOUT1 (in the SSP mode). Note, that if MCM = 1 and DLB = 1, a CLKR signal is also supplied by the internal source.                                                                                                                                                                                                                                                                                                                                                                       |

| 3        | TXM          | The Transmit Mode Bit configures the FSX pin as an input (TXM = 0) or as an output (TXM = 1). When TXM = 1, frame sync pulses are generated internally when data is transferred from the transmit FIFO to XSR to initiate data transfers. The internally generated frame sync signal is synchronous with respect to CLKX. When TXM = 0, the transmitter idles until an external frame synch pulse is supplied on the FSX pin.                                                                                                                                                                                                                                                                    |

| 4<br>5   | RRST<br>XRST | The Receive Reset and Transmit Reset signals reset the receiver and transmitter respectively. If the SSPCR is to be modified to reconfigure the serial port, a total of two writes should be made to the SSPCR. The first write should write zeroes to XRST and RRST and the desired configuration bits. The second write should write ones to XRST and RRST, (with the same configuration bits) taking the serial port out of reset.                                                                                                                                                                                                                                                            |

| 6        | INO          | The input bit 0 allows the CLKR to be used as a bit input. IN0 reflects the current level of the CLKR pin of the device. The level on this pin can be read by reading the SSPCR register. This bit can be tested by using the BIT or BITT instructions. Note that there is a latency of 0.5 to 1.5 CLKOUT1 cycles from the time a new bit value arrives at the CLKR pin to the time that value is represented in the SSPCR.                                                                                                                                                                                                                                                                      |

| 7        | OVF          | Overflow flag (OVF) status signal indicates that receive FIFO overflow has occurred (continuous mode). The OVF bit is set when receive FIFO overflows and is cleared when receive FIFO is read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8 9      | FR0<br>FR1   | The FIFO receive interrupt bits set an interrupt trigger condition based on the contents of the receive FIFO buffer.  FR1 FR0 0 0 Receive FIFO is not empty. 0 1 Receive FIFO has 2 or more words 1 0 Receive FIFO has 3 or 4 words 1 1 Receive FIFO is full.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10<br>11 | FT0<br>FT1   | The FIFO transmit interrupt bits set an interrupt trigger condition based on the contents of the transmit FIFO buffer.  FT1 FT0  0 0 Transmit FIFO has 1 or more words available.  0 1 Transmit FIFO has 2 or more words available.  1 0 Transmit FIFO has 3 or 4 words available.  1 1 Transmit FIFO is empty. 4 data spaces available.                                                                                                                                                                                                                                                                                                                                                         |

| 12       |              | Receive FIFO not empty. Indicates that data still exists in receive FIFO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 13       | SOFT         | Transmit complete. Indicates that all data bits have been transferred out of the transmit FIFO.  The SOFT bit. This bit is enabled when the FREE bit is 0. If FREE = 0, the SOFT bit selects immediate stop if 0, stop after word completion if 1. At reset, this bit is zero.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15       | FREE         | The FREE bit. If FREE = 1, free run is selected, regardless of the value of the SOFT bit. If FREE = 0, the SOFT bit selects the emulation mode. At reset, this bit is zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## A.4.3 Selecting CLKX and FSX source

The SSPCR bits MCM (bit2) and TXM (bit3) define the source for the shift clock CLKX and frame sync FSX. These two clock sources are based on the type of external device that needs to be interfaced with the serial port. Table 4 explains the clock source selection using the SSPCR register bits.

Table 4. Selecting Shift Clock (CLKX) and Frame sync (FSX) sources

| MCM | TXM | CLKX source | FSX source |

|-----|-----|-------------|------------|

| 0   | 0   | External    | External   |

| 0   | 1   | External    | Internal   |

| 1   | 0   | Internal    | External   |

| 1   | 1   | Internal    | Internal   |

## A.5 New ESSP Registers

## A.5.1 Synchronous Serial Port Status Register (SSPST)

The SSPST register is used to configure the various ESSP options. It has additional FIFO status bits. The prescalers for CLKX and FSX are also configured by the SSPST. Refer to Table 5 for a summary of the various bits in SSPST.

Figure 3. Synchronous Serial Port Status Register -SSPST (I/O address FFF2h)

| 15         | 14  | 13    | 12              | 11   | 10  | 9     | 8     | 765                     | 432                    | 1                        | 0                |

|------------|-----|-------|-----------------|------|-----|-------|-------|-------------------------|------------------------|--------------------------|------------------|

| DRP<br>pin | FSN | FSXOX | FSXST<br>Status | RSVD | CLN | CLXOX | PRSEN | Transmit<br>FIFO status | Receive<br>FIFO status | SGNEX<br>Sign-<br>extend | BYTE<br>8/16 bit |

| R          | R/W | R/W   | W1C/R           |      | R/W | R/W   | R/W   | R                       | R                      | R/W                      | R/W              |

- 1. Data word size Bit 0. Defines the data word length as 16-bits or 8-bits. The default value at reset is 0, selecting 16-bit data word size. 8-bit data can be received or transmitted by setting bit 0 to 1.

- 2. Sign-extend

Bit 1. When the data word size is chosen as 8- bits, this bit when set to 1, sign extends the most significant 8 bits of the 16-bit word. If the bit is reset to 0, the most significant 8 bits will be filled with zeros.

- 3. Status of the receive and transmit FIFOs

- Bit 2,3,4 and 5,6,7 define the status of the receive and transmit FIFOs. Each set of 3 bits is capable of indicating five different states that reflect upon the contents of the FIFOs.

- 4. Pre-scale clock enable PRSEN.

- Bit 8 when set to 1 enables the input clock source to the CLKX pre-scalar CLXCT and extends the scaled CLKX to the ESSP. If reset to 0, the pre-scalar will not count down as there is no input clock to the counter. The input to CLXCT is CLKOUT1.

## 5. Input clock source CLXOX bit.

- Bit 9. In the general purpose counter mode (GPC bit =1), this bit selects the input clock source to the 16 bit counter (SSPCT). If CLXOX = 1, the input clock will be CLKX pin clock (either CLKOUT1/2 or external CLKX depending on the MCM bit). If CLXOX bit is 0 the input clock will be CLKOUT1. In all other modes this bit has no effect (don't care x).

#### 6. Shift clock CLKX invert bit, CLN

- Bit 10. Selects the polarity for the shift clock CLKX. If reset to 0, CLKX will be of normal polarity. If set to 1, CLKX will be inverted for internal and external CLKX. CLN bit controls both the CLKX and CLKR polarity. In the internal CLKX mode, the out going CLKX will be inverted once and the incoming CLKR signal will be inverted once. Thus, if CLKX and CLKR pins are externally connected, the polarity of the CLKX/CLKR are the same with respect to the SSP core.

#### 7. Reserved - Bit 11.

#### 8. Pre-scalar FSXST status bit.

- Bit 12. This bit will be set to 1 every time the FSXCT pre-scalar counter reaches zero. This bit can be read and cleared by writing a 1. This bit is also a counter-status bit in the 16 bit counter mode. It will be set to 1 whenever the 16-bit counter reaches zero. This bit will not initiate an interrupt if GPI is enabled in SSPMC register.

#### 9. Internal FSX selection bit, FSXOX

- Bit 13. Selects the type of internal frame sync that will be issued from FSX pin. If set to 1, the FSX is from the frame sync pre-scalar FSXCT. If reset to 0, the internal FSX will be at the rate at which data is written into the transmit FIFO.

#### 10. Frame sync invert bit, FSN

- Bit 14. Selects the polarity for the frame sync. At reset, FSN is 0 and selects FSX to be high for one CLKX duration. The data transmit and receive is based on the falling edge of FSX. If FSN is set to 1, the polarity of the FSX is inverted. The FSX will remain high during data transmit or receive (8/16 CLKX cycles). FSN bit controls both the FSX and FSR polarity. In the internal FSX mode, the out going FSX will be inverted once and the incoming FSR will be inverted once. Thus, if FSX and FSR pins are externally connected, the polarity of the FSX/FSR are the same with respect to the SSP core.

11. DR pin read bit - Bit 15. DRP bit which gives visibility to DR pin. It is a read only bit.

#### A.5.2 Synchronous Serial Port Multichannel Register (SSPMC)

The SSPMC register is used to select multi-channel and 16-bit counter features in the ESSP. Figure 4 explains the bit fields used to control multi-channel option on the ESSP.

Figure 4. Synchronous Serial Port Multi-channel Register - SSPMC (FFF3h)

| 15     | Bit 14-7 | 6   | 5   | 4   | 3     | 2   | 1    | 0   |

|--------|----------|-----|-----|-----|-------|-----|------|-----|

| SSPRST | Reserved | SPI | CH1 | CH0 | MMODE | GPI | CHLT | GPC |

| R/W    |          | R/W | R/W | R/W | R/W   | R/W | R/W  | R/W |

- 1. General purpose counter bit, GPC.

- Bit 0 configures the two pre-scalars CLXCT, FSXCT as a 16-bit counter. When GPC is 1, CLXCT and FSXCT are together used as a 16-bit counter. The input to the counter is either internal CLKOUT1 or CLKX pin clock as defined by CLXOX in SSPST register. In the counter mode the pre-scalars are not available for ESSP clock scaling. GPC bit should be 0 if the pre-scalars are to be used for CLKX and FSX scaling.

- 2. 16 bit Counter halt bit CHLT.

- Bit 1 can be used to stop the 16-bit counter, when the pre-scalars are used as a counter. 0 is default, indicates counter is counting.1 will stop the counter.

- 3. General purpose counter interrupt bit GPI

- Bit 2 configures the XINT interrupt of the SSP as the 16-bit counter interrupt. Whenever the 16-bit counter reaches 0, an interrupt will be generated.

- 4. Multi-channel mode bit MMODE

- Bit 3 if reset to 0 (default), deselects multi-channel option on the serial port. If set to 1, selects multi-channel mode and uses the pre-scaled frame sync FSX only. In this mode, one or more frame sync pulses are generated on different pins for glueless interface to multiple codecs. The FSX and CLKX signals are internally connected to FSR and CLKR pins respectively. CLKR and FSR pins are available as outputs for generating multi- channel frame sync FSX2, FSX3. The fourth channel frame sync FSX4 is generated on IO0 pin (pin96). In this mode, IO0 is not available as general purpose I/O pin.

- 5. Channel select bits CH1, CH0

- Bits 5, 4 select the number of channels that are available in the multi-channel mode. These bits have no effect if MMODE bit is 0.

- 0 0 Selects one channel with one frame sync pulse FSX1 on FSX pin. The FSX rate is defined only by the FSX pre-scalar, FSXCT.

- 0 1 Selects two channels with the second frame sync pulse FSX2 on CLKR pin (pin 84). Frame sync FSX2 will be issued on the second CLKX cycle

from the LSB bit of the first channel.

- 1 0 Selects three channels with the third frame sync pulse FSX3 on FSR pin (pin 85). Frame sync FSX3 will be issued on the second CLKX cycle from the LSB bit of the second channel.

- 1 1 Selects all four channels with the fourth frame sync pulse FSX4 on IO0 pin (pin 96). Frame sync FSX4 will be issued on the second CLKX cycle from the LSB bit of the third channel. In this mode IO0 pin is not available for I/O operation.

- 6. SPI mode bit,

- Bit 6, when 1, enables 8/16 bit serial peripheral interface (SPI) mode. This mode is available only in burst mode with internal shift clock CLKX. If bit 6 is reset to 0, the SPI mode is disabled. In this mode, CLKX is issued only during the time data bits are transmitted or received. Data will be transmitted/received when ever transmit FIFO has data, along with an FSX signal. Pre-scaled FSX cannot be used in this mode. CLKR and FSR are internally connected to CLKX and FSX respectively. CLKX pin will be normally

low in SPI mode. If CLN bit is enabled in SSPST register, then CLKX pin will be high in between data transmit.

7. Reserved bits - Bits 14-7

8. SPRST - Bit 15 resets the current operation of SSP. At reset this bit will be zero enabling normal

operation. If set to 1, the SSP will reset as below:

a. Reset transmit FIFO pointers and transmit shift register.

b. Reset receive FIFO pointers and receive shift register

c. Pre-scalar logic will reload pre-scalar counters if GPC=0.

If GPC=1, no reload to pre-scalars. Reset all logic, except counter logic.

d. SSP control register bits (SSPCR) are not affected by this. However, all status bits will be reset.

## A.5.3 Synchronous Serial Port Count Register (SSPCT)

The shift clock CLKX and frame sync FSX can come from external or internal sources. The SSPCR register bits define the source of these signals. The SSPCT register holds two 8-bit pre-scale counters to provide user specific shift clock CLKX and frame sync clock FSX. The CLXCT counter is an 8-bit pre-scalar to divide CLKOUT1. The pre-scalar output clock is CLKOUT1/(2\*(CLXCT+1)) . CLXCT is the pre-scale value defined in the SSPCT register bits 7-0. At reset the CLXCT register value is zero, which makes the CLKX rate equal to (CLKOUT1)/2. This register can be written with any desired 8-bit pre-scale value. The pre-scalar functions as a down counter, and the counter value can be read anytime. The input clock source to the CLXCT pre-scalar can be CLKOUT1 only. PRSEN (bit 8 of the SSPST register) should be set to 1, which enables the input clock to the pre-scalar.

Once 8-bit pre-scalar values are written to the register SSPCT, PRSEN has to be enabled to start the counter counting down. The pre-scalar values are loaded into the counter from the internal buffers only after PRSEN is enabled. Enabling PRSEN should always follow any pre-scalar update. The pre-scalar has an internal buffer register that gets updated every time SSPCT is written. The counter after reaching zero reloads the pre-scale value from the buffer and counts down. This sequence of reload and count down will repeat until PRSEN bit in SSPST is reset to 0. If the PRSEN is reset to 0, the pre-scalar will not have any input clock source to count down.

FSXCT takes the either the CLKX pre-scalar output or the external CLKX pin clock as its input. This helps to generate a variable frame sync pulse synchronous to CLKX. Most applications require a FSX rate that is a multiple of the CLKX rate. The FSX rate is defined by the equation, CLKX pin clock/(2\*(FSXCT+1)). FSXST bit (Bit 12 in SSPST) will be set every time FSXCT reaches zero, and can be reset by writing a 1 to the FSXST bit. The 8-bit pre-scalar FSXCT for FSX also functions similar to the CLKX pre-scalar CLXCT.

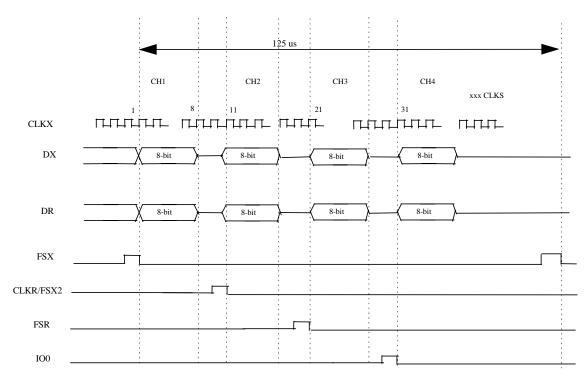

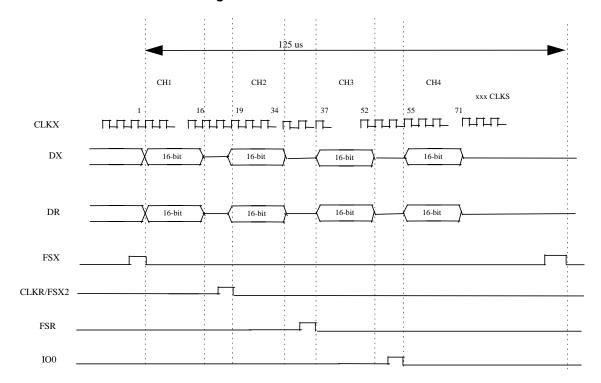

Caution: In multi-channel mode, the value of FSXCT chosen (for 16-bit data) should be such that there are at least (18 \* n) SCLKs between successive frame syncs, where n is the number of serial channels. For example, FSXCT should be greater or equal to 35 (23h) if four serial channels are configured. For 8-bit data, FSXCT should be greater or equal to 19 (13h) for four channel configuration. This number will be valid for any CLKX and changes only with the number of serial channels configured.

## A.6 Pre-scalars as general purpose counter

The two 8-bit pre-scalars in SSPCT register can be used as a single 16-bit down counter. The GPC bit in SSPMC register enables the 16-bit counter mode. When GPC is set to 1, the pre-scalars are not available for scaling CLKX and FSX. The 16 bit counter can accept either CLKOUT1 clock or CLKX pin clock as its input. The counter value can be read any time and can be stopped by setting CHLT bit in the SSPMC register. The counter will flag a status bit FSXST whenever it reaches 0x0000. The counter will reload the counter value after it reaches zero and will continue to count down. The FSXST bit is cleared by writing a one to that bit.

Figure 5. Synchronous Serial Port Count Register -SSPCT (FFFBh)

| 15 - 8                  | 7- 0                    |  |  |  |

|-------------------------|-------------------------|--|--|--|

| 8-bit pre-scalar -FSXCT | 8-bit pre-scalar –CLXCT |  |  |  |

| R/W                     | R/W                     |  |  |  |

Table 5 ESSP Registers Bit Summary

| NAME  | I/O<br>ADDRESS | Value at<br>Reset | DESCRIPTION | ON                                                                  |

|-------|----------------|-------------------|-------------|---------------------------------------------------------------------|

| SSPST | FFF2h          | 0000h             | Enhanced Sy | nchronous Serial Port FIFO status bit and word select register      |

|       |                |                   | Bit0 - 0    | - 16 bit data word - default                                        |

|       |                |                   | 1           | - 8 bit data word                                                   |

|       |                |                   | I           | - o bit data word                                                   |

|       |                |                   | Bit 1 - 0   | - zero fill unused MSBs in 8-bit word mode                          |

|       |                |                   | 1           | - Sign-extend unused MSBs in 8-bit word mode                        |

|       |                |                   | Bit 4 3 2   | - Receive FIFO status                                               |

|       |                |                   | 000         | - FIFO empty                                                        |

|       |                |                   | 0 0 1       | - FIFO has 1 word                                                   |

|       |                |                   | 010         | - FIFO has 2 words                                                  |

|       |                |                   | 011         | - FIFO has 3 words                                                  |

|       |                |                   | 100         | - FIFO has 4 words                                                  |

|       |                |                   | Bit 7 6 5   | - Transmit FIFO status                                              |

|       |                |                   | 000         | - FIFO empty                                                        |

|       |                |                   | 000         | - FIFO has 1 word to transmit                                       |

|       |                |                   | 010         | - FIFO has 2 words to transmit                                      |

|       |                |                   | 010         | - FIFO has 3 words to transmit                                      |

|       |                |                   | _           |                                                                     |

|       |                |                   | 100         | - FIFO has 4 words to transmit                                      |

|       |                |                   | Bit 8 - 0   | - PRSEN disables input clock to pre-scalars in SSPCT                |

|       |                |                   | 1           | - PRSEN enables input clock to pre-scalars in SSPCT.                |

|       |                |                   | Bit 9 - 0   | - CLXOX selects CLKOUT1 clock as input to 16 bit counter            |

|       |                |                   | 1           | - CLXOX selects CLKX pin clock as input to 16 bit counter           |

|       |                |                   | '           | Useful only in 16-bit counter mode. In all other modes, don't care. |

|       |                |                   | Bit 10 - 0  | - CLN does not affect the shift clock CLKX, default                 |

|       |                |                   | 1           | - CLN inverts the shift clock CLKX and CLKR.                        |

|       |                |                   | Bit 11      | - Reserved                                                          |

|       |                |                   | Bit 12 - 0  | - Pre-scalar still counting, FSXST bit is zero                      |

|       |                |                   | 1           | - FSXST bit is set if pre-scalar value is 0x0000h                   |

|       |                |                   | Bit 13 - 0  | - Selects the internal FSX at the transmit FIFO write rate          |

|       |                |                   | 1           | - Selects the internal FSX from FSX pre-scalar FSXCT                |

|       |                |                   | Bit 14 - 0  | - No change on the polarity of FSX pulse – high pulse for one CLKX  |

|       |                |                   | 1           | - FSN will invert the polarity of FSX pulse -low pulse.             |

|       |                |                   |             | - Setting FSN to 1 affects FSR polarity. FSR will also be inverted. |

|       |                |                   | Bit 15      | - Reads the DR pin                                                  |

|       |       |       | version 1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSPMC | FFF3h | 0000h | Enhanced synchronous serial port multi-channel register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       |       |       | Bit 0 - 0 - Pre-scalars used for CLKX and FSX 1 - GPC sets the two pre-scalars in 16-bit general purpose counter mode  Bit 1 - 0 - 16-bit Counter running 1 - Stop 16-bit counter  Bit 2 - 0 - XINIT interrupt tied to SSP transmit interrupt 1 - GPI selects XINIT interrupt to 16-bit general purpose counter interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |       |       | Bit 3 0 - Default value of MMODE bit. Multi-channel feature not selected  1 - Selects multi-channel feature for the SSP  Bit 5 4 - CH1 - CH0  0 0 - Selects one channel by issuing one Frame sync FSX1 from FSX pin  0 1 - Selects two channel by issuing second Frame sync FSX2 from CLKR pin. Second FSX2 will trail FSX1, by two clock CLKX cycles from the LSB bit of the first channel.  1 0 - Selects three channel by issuing third Frame sync FSX3 from FXR pin. Third FSX3 will trail FSX2, by two clock CLKX cycles from the LSB bit of the second channel.  1 1 - Selects four channel by issuing fourth Frame sync FSX4 from IO0 pin. Fourth FSX4 will trail FSX3, by two clock CLKX cycles from the LSB bit of the third channel  Bit 6 0 - Deselects 8/16 bit SPI mode. Default  - Selects 8/16 bit SPI mode, with internal shift clock CLKX only |

|       |       |       | Bits 7-14 - Reserved.  Bit 15 - SSPRST bit to stop current operation of SSP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SSPCT | FFFBh | 0000h | Enhanced synchronous serial port count register  Internal Shift clock CLKX counter CLXCT (bits 7-0). 8-bit Pre-scalar used to generate internal shift clock (CLKX). The CLKX rate is defined by the equation  CLKX = CLKOUT1/(2*(CLXCT+1)).  Internal Frame sync FSX counter FSXCT (bits 15-8). 8-bit Pre-scalar used to generate internal frame sync (FSX). The FSX rate is defined by the equation  FSX = CLKX/(2*(FSXCT+1)).  FSX pre-scalar input could be either external CLKX pin clock or pre-scaled internal CLKX. Note: In multi-channel mode, for 16-bit data, the value of FSXCT should be such that there are atleast (18 * n) SCLKs between successive frame syncs.                                                                                                                                                                                |

# A.7 Programmable internal CLKX and FSX rates

The device clock CLKOUT1, external shift clock CLKX and the 8-bit pre-scalars can provide various CLKX/FSX rates to match several serial interface devices. Some such interface devices, like CODECs operate in slave mode expecting external shift clock. Table 6 below provides various shift clock and frame sync rates that can be generated for voice band applications using the pre-scalars.

Table 6. Typical CLKX ,FSX rates and their pre-scalar values

| CLKOUT1                  | Pre-scale value<br>CLXCT<br>Decimal (Hex) | CLKX rate  | Pre-scale value<br>FSXCT<br>Decimal (Hex) | FSX rate | Remarks                |

|--------------------------|-------------------------------------------|------------|-------------------------------------------|----------|------------------------|

|                          |                                           |            |                                           |          |                        |

| 40.96 MHz                | 0                                         | 20.48 MHz  | 255 (FFh)                                 | 40 KHz   |                        |

|                          | 9 (9h)                                    | 2.048 MHz  | 127 (7Fh)                                 | 8 KHz    | VBAP/Combo codec rates |

|                          | 159 (9Fh)                                 | 128 KHz    | 3 (03h)                                   | 16 KHz   |                        |

| 20.48 MHz                | 0                                         | 10.24 MHz  | 255 (FFh)                                 | 20 KHz   |                        |

|                          | 4 (4h)                                    | 2.048 MHz  | 127 (7Fh)                                 | 8 KHz    | VBAP/Combo codec rates |

|                          | 159 (9Fh)                                 | 64 KHz     | 3 (03h)                                   | 16 KHz   |                        |

| 12.288x2 =<br>24.576 MHz | 0                                         | 12.288 MHz | 383 (17Fh)                                | 16 KHz   |                        |

|                          | 1h                                        | 6.144 MHz  | 191 (BFh)                                 | 16 KHz   |                        |

|                          | 5h                                        | 2.048 MHz  | 127 (7Fh)                                 | 8 KHz    | VBAP/Combo codec rates |

|                          | 7h                                        | 1.536 MHz  | 95 (5Fh)                                  | 8 KHz    | VBAP/Combo codec rates |

|                          | 191 (BFh)                                 | 64 KHz     | 3 (03h)                                   | 8 KHz    |                        |

## A.8 ESSP register programming considerations

The SSP features are enabled by SSPCR register only. The ESSP registers need not be changed for the standard SSP features. This provides compatibility to the existing codes on rev1.0 silicon and devices with standard SSP. To enable any of the ESSP features the ESSP registers SSPCT, SSPMC and SSPST should to be initialized. Its recommended to initialize the registers SSPCT, SSPMC first followed by SSPST register. The pre-scalars are enabled only after the PRSEN bit (bit 8 in SSPST) is set to 1. So it is essential that the other registers be pre-loaded before enabling the PRSEN bit in SSPST register.

While changing CLKN or FSN bits initialize the SSPST register in two steps. First load the SSPST registers bits with PRSEN bit 0. Provide at least one CLKX cycle delay before setting PRSEN bit to. This should help all internal synchronization of the clocks (FSX/CLKX). This would also make the pre-scalars and the clock circuit to respond the stable clock (FSX/CLKX,FSR,CLKR)edges. However, in any initialization sequence the pre-scalar clocks will be stable after the first reload of the pre-scalar counters.

Considerable attention must be paid in choosing the value of FSXCT in multi-channel mode. For 16-bit data, successive frame sync pulses occur 18 SCLKs after the previous frame sync pulse. In the multi channel mode, if all 4 channels are used, a new data word is transmitted after a period of 72 SCLKs for a given channel. In other words a new frame sync can occur only after 72 SCLKs. This is the minimum requirement. The minimum value for the FSXCT value can be easily found from the formula for calculating the FSX rate. This is done by applying the condition that two frame syncs for a given channel must be separated by at least (n \* 18) SCLKs, where n is the number of channels in the multi-channel mode. This condition is applicable for 16-bit mode, where successive frame syncs are separated by 18 SCLKs. In 8-bit mode, the frame syncs are separated by 10 SCLKs. PRSEN must be 1 for the FS prescaler to operate.

When the prescalers are used as a 16-bit counter, they are not available for prescaling FSX and CLKX. Two options are possible in the 16-bit counter mode (GPC = 1).

Option 1 : Internal CLKX (MCM = 1)

When CLXOX = 1, input to counter is CLKX which is CLKOUT1/2, since the prescalers are not operating. When CLXOX = 0, input to counter is CLKOUT1

Option 2: External CLKX (MCM =0)

When CLXOX = 1, input to counter is CLKX pin When CLXOX = 0 input to counter is CLKOUT1

## A.9 Multi-channel frames

## A.9.1 8-bit Four channel interface timings

Figure 7 Four 8-bit codec interface timing for voice-band CODECs

# A.9.2 16-bit Four channel interface timings

Figure 8 Four 16-bit Codec interface timings for voice-band CODECs

## **Table 7 Serial port configuration - Burst Mode**

|             |                                        | SSPCR SSPMC register |             |             |        |             |             |             |         |   |   |             |             | PST              | rec              | giste       | er                    |                       |                  |                      |                      |                  |                            |                        |                                        |

|-------------|----------------------------------------|----------------------|-------------|-------------|--------|-------------|-------------|-------------|---------|---|---|-------------|-------------|------------------|------------------|-------------|-----------------------|-----------------------|------------------|----------------------|----------------------|------------------|----------------------------|------------------------|----------------------------------------|

| O p t i o n | Function                               | F<br>S<br>M          | M<br>C<br>M | T<br>X<br>M | S<br>S | S<br>P<br>I | C<br>H<br>B | C<br>H<br>B | M O D E | Р |   | G<br>P<br>C | F<br>S<br>N | F<br>X<br>O<br>X | F<br>S<br>X<br>S | C<br>L<br>N | C<br>L<br>X<br>O<br>X | P<br>R<br>S<br>E<br>N | B<br>Y<br>T<br>E | CLKX                 | FSX                  | CLXCT            | CLKX rate                  | FSXCT                  | FSX rate                               |

| 1           | RESET                                  | 0                    | 0           | 0           | 0      | 0           | 0           | 0           | 0       | 0 | 0 | 0           | 0           | 0                | 0                | 0           | 0                     | 0                     | 0                | External             | External             | not<br>used      | -                          | not used               | -                                      |

| 2           | SSP Option                             | 1                    | 0           | 0           | 0      | 0           | Х           | Х           | 0       | 0 |   | 0           | 0           | Х                | 0                | 0           | Х                     | 0                     | 0/1              | External             | External             | not<br>used      | External<br>CLKX           | not used               | External FSX                           |

| 3           | SSP option with FSXCT                  | 1                    | 0           | 1           | 0      | 0           | X           | X           | 0       | 0 | X | 0           | 0           | 1                | 0                | 0           | Х                     | 1                     | 0/1              | External             | Internal             | Not<br>used      | External<br>CLKX           | Used for prescaled FSX | Internal FSX. Defined by FSXCT         |

| 4           | SSP Option                             | 1                    | 0           | 1           | 0      | 0           | Х           | Х           | 0       | 0 | Х | 0           | 0           | 0                | 0                | 0           | Х                     | Х                     | 0/1              | External             | Internal             | not<br>used      | External<br>CLKX           | not used               | Int. FSX defined by TX FIFO write rate |

| 5           | SSP Option                             | 1                    | 1           | 0           | 0      | 0           | Х           | Х           | 0       | 0 | X | 0           | 0           | X                | 0                | 0           | Х                     | 0                     | 0/1              | Internal             | External             | not<br>used      | ½ CLKOUT1                  | not used               | External FSX                           |

| 6           | SSP Option with CLXCT                  | 1                    | 1           | 0           | 0      | 0           | Х           | Х           | 0       | 0 | X | 0           | 0           | X                | 0                | 0           | Х                     | 1                     | 0/1              | Internal             | External             | used for<br>CLKX | ½ CLKOUT1 or Prescaled     | not used               | External FSX                           |

| 7           | SSP option<br>with 8-bit<br>Prescalers | 1                    | 1           | 1           | 0      | 0           | X           | X           | 0       | 0 | X | 0           | 0           | 1                | 0                | 0           | Х                     | 1                     | 0/1              | Internal             | Internal             | used for<br>CLKX | ½ CLKOUT1 or Prescaled     | used                   | Defined by FSX<br>Pre-scale FSXCT      |

| 8           | SSP Option                             | 1                    | 1           | 1           | 0      | 0           | Х           | Х           | 0       | 0 | X | 0           | 0           | 0                | 0                | 0           | Х                     | 0                     | 0/1              | Internal             | Internal             | not<br>used      | ½ CLKOUT1                  | not used               | Defined by write to TX FIF0            |

| 9           | SSP Option<br>with<br>CLKXCT           | 1                    | 1           | 1           | 0      | 0           | X           | X           | 0       | 0 | X | 0           | 0           | 0                | 0                | 0           | Х                     | 1                     | 0/1              | Internal             | Internal             | used for<br>CLKX | ½ CLKOUT1 or Prescaled     | not used               | Defined by write to TX FIF0            |

| 10          | Multi-                                 | 1                    | 1           | 1           | 0      | 0           | 0/1         | 0/1         | 1       | 0 | 0 | 0           | 0           | 1                | 0                | 0           | Х                     | 1                     | 0/1              | Internal             | Internal             | Used             | ½ CLKOUT1                  | used                   | FSX1 is defined by                     |

| 11          | channel<br>Multi-<br>channel           | 1                    | 0           | 1           | 0      | 0           | 0/1         | 0/1         | 1       | 0 | 0 | 0           | 0           | 1                | 0                | 0           | Х                     | 1                     | 0/1              | External             | Internal             | not<br>used      | or prescaled External CLKX | used                   | FSXCT † FSX1 is defined by FSXCT †     |

| 12          | SPI                                    | 1                    | 1           | 1           | 0      | 1           | 0           | 0           | 0       | 0 | 0 | 0           | 0           | 0                | 0                | 0           | Х                     | 1                     | 0/1              | Internal             | Internal             | used             | ½ CLKOUT1 or Prescaled     | not used               | Defined by write to TX FIF0            |

| 13          | Timer/SSP                              | 1                    | 1           | 1           |        | 0           | 0           | 0           | 0       | u |   | 1           | 0           | 0                |                  | 0           | 0/1                   | 1                     | 0/1              | Internal             | Internal             | used             | ½ CLKOUT1 or Prescaled     | not used               | Defined by write to TX FIF0            |

| 14<br>15    | Timer/SSP Timer/SSP                    | 1                    | 0           | 1           | 0      | 0           | 0           | 0           | 0       |   |   | 1           | 0           | 0<br>0           |                  | 0           | 0/1                   | 1                     | 0/1              | Internal<br>External | External<br>Internal | by<br>16-bit     | ½ CLKOUT1 External         | by<br>16-bit           | External Defined by write to TX FIF0   |

| 16          | Timer/SSP                              | 1                    | 0           | 0           | 0      | 0           | 0           | 0           | 0       | u | u | 1           | 0           | Χ                | 0                | 0           | 0/1                   | 1                     | 0/1              | External             | External             | counter          | External                   | Counter                | External                               |

X - DON'T CARE. Does not affect the selected mode. Replace X with 0 while writing to the registers

SSP option – This option refers to all features of the standard SSP, without the use of ESSP register bits

u - Used to define other functions in the selected mode. 0 and 1 are valid options.

<sup>† -</sup> FSXCT should define FSX rate to be greater than (18x4) SCLKs for 16-bit data and (10x4) SCLKs for 8-bit data, else the FSX rate will be incorrect.

# **Table 8 Serial port configuration - Continuous Mode**

|             |                                        |     |             |             |   |     |                  |                  |                  |       |                  | S   | SPS | T r | egis                  | ter         |       |                       |                  |          |          |                  |                         |                       |                                |

|-------------|----------------------------------------|-----|-------------|-------------|---|-----|------------------|------------------|------------------|-------|------------------|-----|-----|-----|-----------------------|-------------|-------|-----------------------|------------------|----------|----------|------------------|-------------------------|-----------------------|--------------------------------|

| O p t i o n | Function                               | FοM | M<br>C<br>M | T<br>X<br>M | 5 | S P | C<br>H<br>B<br>1 | С<br>Н<br>В<br>0 | M<br>O<br>D<br>E | G P I | C<br>H<br>L<br>T | OPO | S   | s   | F<br>S<br>X<br>S<br>T | C<br>L<br>N | CLXOX | P<br>R<br>S<br>E<br>N | B<br>Y<br>T<br>E | CLKX     | FSX      | CLXCT            | CLKX rate               | FSXCT                 | FSX rate                       |

| 1           | RESET                                  | 0   | 0           | 0           | C | 0   | 0                | 0                | 0                | 0     | 0                | 0   | 0   | 0   | 0                     | 0           | 0     | 0                     | 0                | External | External | not<br>used      | -                       | not used              | -                              |

| 2           | SSP Option                             | 0   | 0           | 0           | C | 0   | Х                | Х                | 0                | 0     | Χ                | 0   | 0   | Χ   | 0                     | 0           | 0     | 0                     | 0/1              | External | External | not<br>used      | External<br>CLKX only   | not used              | External                       |

| 3           | SSP Option with FSXCT                  | 0   | 0           | 1           | C | 0   | X                | X                | 0                | 0     | Х                | 0   | 0   | 1   | 0                     | 0           | X     | 1                     | 0/1              | External | Internal | not<br>used      | External<br>CLKX only   | Used for internal FSX | Internal FSX. Defined by FSXCT |

| 4           | SSP Option                             | 0   | 0           | 1           | C | 0   | Х                | Х                | 0                | 0     | Χ                | 0   | 0   | 0   | 0                     | 0           | Х     | Х                     | 0/1              | External | Internal | not<br>used      | External<br>CLKX        | not used              | TX FIFO write rate             |

| 5           | SSP Option                             | 0   | 1           | 0           | C | 0   | Х                | Х                | 0                | 0     | Χ                | 0   | 0   | Χ   | 0                     | 0           | Х     | 0                     | 0/1              | Internal | External | not<br>used      | ½ CLKOUT1               | not used              | External FSX                   |

| 6           | SSP Option with CLXCT                  | 0   | 1           | 0           | C | 0   | Х                | Х                | 0                | 0     | Χ                | 0   | 0   | Χ   | 0                     | 0           | Х     | 1                     | 0/1              | Internal | External | used for<br>CLKX | ½ CLKOUT1 or Pre-scaled | not used              | External FSX                   |

| 7           | SSP Option<br>with 8-bit<br>prescalers | 0   | 1           | 1           | C | 0   | Х                | Х                | 0                | 0     | Х                | 0   | 0   | 1   | 0                     | 0           | X     | 1                     | 0/1              | Internal | Internal | used for<br>CLKX | ½ CLKOUT1 or Pre-scaled | used                  | Defined by FSX<br>Pre-scale    |

| 8           | SSP Option                             | 0   | 1           | 1           | C | 0   | Х                | Х                | 0                | 0     | Χ                | 0   | 0   | 0   | 0                     | 0           | X     | 0                     | 0/1              | Internal | Internal | not<br>used      | ½ CLKOUT1               | not used              | Defined by write to TX FIF0    |

| 9           | SSP Option<br>with<br>CLKXCT           | 0   | 1           | 1           | C | 0   | X                | Х                | 0                | 0     | Х                | 0   | 0   | 0   | 0                     | 0           | X     | 1                     | 0/1              | Internal | Internal | used for<br>CLKX | ½ CLKOUT1 or Pre-scaled | not used              | Defined by write to TX FIF0    |

|             | No Multi-chanr<br>SSP (FSM bit         |     | _           |             |   |     |                  |                  | ode              | of t  | he               |     |     |     |                       |             |       |                       |                  |          |          |                  |                         |                       |                                |

| 13          | Timer/SSP                              | 0   | 1           | 1           | C | 0   | 0                | 0                | 0                | u     | u                | 1   | 0   | 0   | 0                     | 0           | 0/1   | 1                     | 0/1              | Internal | Internal | used             | ½ CLKOUT1               | used                  | Defined by write to TX FIF0    |

| 14          | Timer/SSP                              | 0   | 1           | 0           | C | 0   | 0                | 0                | 0                | u     | u                | 1   | 0   | Χ   | 0                     | 0           | 0/1   | 1                     | 0/1              | Internal | External | by               | ½ CLKOUT1               | by                    | External                       |

| 15          | Timer/SSP                              | 0   | 0           | 1           | C | 0   | 0                | 0                | 0                | u     | u                | 1   |     | 0   | 0                     | 0           | 0/1   | 1                     | 0/1              | External | Internal | 16-bit           | External                | 16-bit                | Defined by write to TX FIF0    |

| 16          | Timer/SSP                              | 0   | 0           | 0           | C | 0   | 0                | 0                | 0                | u     | u                | 1   | 0   | Χ   | 0                     | 0           | 0/1   | 1                     | 0/1              | External | External | counter          | External                | Counter               | External                       |

|             |                                        |     |             |             |   |     |                  |                  |                  |       |                  |     |     |     |                       |             |       |                       |                  |          |          |                  |                         |                       |                                |