Features for the AFE7900EVM

- Allows evaluation of 4T4R+2FB RF-sampling AFE7900 solutions

- JESD204B/C data interface to simplify digital interface; compliant up to 29.5-Gbps lane rates

- Supports JESD204B/C for synchronization and compatibility

- Option for DC-DC-based LDO-less power-management solution

- Onboard clocking solution supported with LMK04828 and for generating SYSREF

- On-chip interpolation/decimation filter inputs/outputs sample data at reduced sample rates and improved signal-to-noise ratio (SNR)

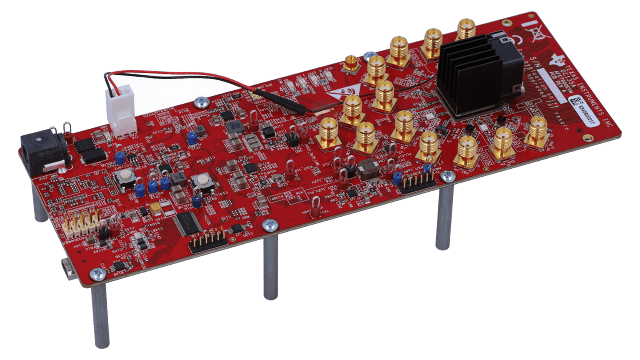

Description for the AFE7900EVM

The AFE7900 evaluation module (EVM) is an RF-sampling transceiver platform that can be configured to support up to four-transmit, four-receive, and two-feedback (4T4R+2FB) channels simultaneously.

The module evaluates the AFE7900, which is a quad-channel RF-sampling analog front end (AFE) with 14-bit, 12-GSPS digital-to-analog converters (DACs), 14-bit, 3-GSPS analog-to-digital converters (ADCs), and an on-chip integrated phase-locked loop/voltage-controlled oscillator (PLL/VCO) for high-frequency clock generation for DACs and ADCs.

AFE7900EVM has options to use dual digital upconverters and downconverters in each channel to simultaneously synthesize and digitize multiple wideband signals with high dynamic range. On-chip integrated digital step attenuator (DSA) for the receiver channels and DSA functionality for the transmitter channels is supported. Eight JESD204B/C-compatible serializer/deserializer (SerDes) transceivers running up to 29.5 Gbps can be used for providing inputs and outputs to/from the AFE7900 through the onboard field-programmable gate array (FPGA) mezzanine card (FMC) connector.

AFE7900EVM includes the LMK04828 clock generator that provides a reference signal to the AFE on-chip PLL and generates the required SYSREF signals for the JESD204B/C protocol. Also included is the option for providing an ultra-low-phase noise external clocking solution.

AFE7900EVM implements an efficient low-dropout (LDO)-less power-management solution using only DC-DC converters for the required power rails. The design interfaces with the TI pattern/capture card solution (TSW14J56EVM) (sold separately), as well as many FPGA development kits.