Features for the LMK04826BEVM

- JEDEC JESD204B Support

- Ultra-low RMS Jitter Performance

- Dual loop Architecture

- 3 redundant input clocks with LOS

- Precision digital delay, fixed or dynamically adjustable

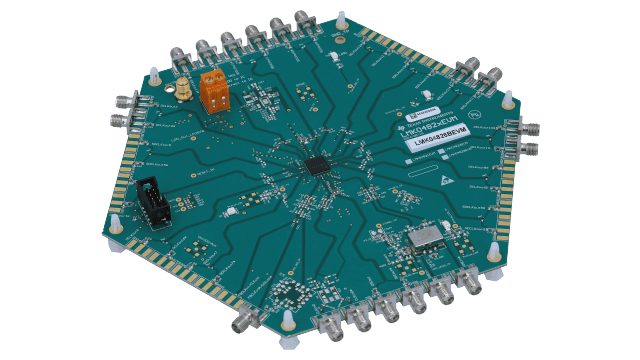

- Evaluation kit includes USB2ANY module for USB connection to the evaluation board.

Description for the LMK04826BEVM

The LMK04826BEVM and LMK04828BEVM supports the LMK04820 family of products, the industry's highest performance clock conditioners with JEDEC JESD204B support. The dual loop PLLatinum™ architecture enables sub-100 fs jitter (12 kHz to 20 MHz) using a low noise VCXO module. The dual loop architecture consists of two high-performance phase-locked loops (PLL), a low-noise crystal oscillator circuit, and a high-performance voltage controlled oscillator (VCO).

The first PLL (PLL1) provides a low-noise jitter cleaner function while the second PLL (PLL2) performs the clock and SYSREF generation. PLL1 can be configured to either work with an external VCXO module or the integrated crystal oscillator with an external tunable crystal and varactor diode. When used with a very narrow loop bandwidth, PLL1 uses the superior close-in phase noise (offsets below 50 kHz) of the VCXO module or the tunable crystal to clean the input clock. The output of PLL1 is used as the clean input reference to PLL2 where it locks the integrated VCO.

The loop bandwidth of PLL2 can be optimized to clean the far-out phase noise (offsets above 50 kHz) where the integrated VCO outperforms the VCXO module or tunable crystal used in PLL1.