LPV801, LPV802

SNOSCZ3B-AUGUST 2016-REVISED NOVEMBER 2016

# LPV801/LPV802 320 nA Nanopower Operational Amplifiers

#### **Features**

Nanopower Supply Current: 320 nA/channel

Offset Voltage: 3.5 mV (max)

TcVos: 1 uV/°C

Unity Gain-Bandwidth: 8 kHz Wide Supply Range: 1.6 V to 5.5 V Low Input Bias Current: 0.1 pA

**Unity-Gain Stable**

Rail-to-Rail Output

No Output Reversals

**EMI Protection**

Temperature Range: -40°C to 125°C

**Industry Standard Packages:**

Single in 5-pin SOT-23

Dual in 8-pin VSSOP

# 2 Applications

- CO and O<sub>2</sub> Gas Detectors (TIDA-00854)

- PIR Motion Detectors (TIDA-00489)

- Ionization Smoke Alarms

- **Thermostats**

- IoT Remote Sensors

- Active RFID Readers and Tags

- Portable Medical Equipment

# 3 Description

The LPV801 (single) and LPV802 (dual) comprise a family of ultra-low-power operational amplifiers for sensing applications in battery powered wireless and low power wired equipment. With 8kHz of bandwidth from 320nA of quiescent current, the LPV80x amplifiers minimize power consumption in equipment such as CO detectors, smoke detectors and PIR motion detectors where operational battery-life is critical.

In addition to being ultra-low-power, the LPV80x amplifiers have CMOS input stages with typically femto-amp bias currents. The LPV80x amplifiers also feature a negative-rail sensing input stage and a railto-rail output stage that is capable of swinging within millivolts of the rails, maintaining the widest dynamic range possible. EMI protection is designed into the LPV80x in order to reduce system sensitivity to unwanted RF signals from mobile phones, WiFi, radio transmitters and tag readers.

#### Device Information<sup>(1)</sup>

| PART<br>NUMBER | PACKAGE    | BODY SIZE         |

|----------------|------------|-------------------|

| LPV801         | SOT-23 (5) | 2.90 mm x 1.60 mm |

| LPV802         | VSSOP (8)  | 3.00 mm × 3.00 mm |

#### LPV8xx Family of Nanopower Amplifiers

|                |          | , , , , , , , , , , , , , , , , , , , |                            |  |  |  |  |  |  |  |

|----------------|----------|---------------------------------------|----------------------------|--|--|--|--|--|--|--|

| PART<br>NUMBER | CHANNELS | SUPPLY<br>CURRENT<br>(Typ/Ch)         | OFFSET<br>VOLTAGE<br>(Max) |  |  |  |  |  |  |  |

| LPV801         | 1        | 450 nA                                | 3.5 mV                     |  |  |  |  |  |  |  |

| LPV802         | 2        | 320 nA                                | 3.5 mV                     |  |  |  |  |  |  |  |

| LPV811         | 1        | 450 nA                                | 370 μV                     |  |  |  |  |  |  |  |

| LPV812         | 2        | 425 nA                                | 300 μV                     |  |  |  |  |  |  |  |

For all available packages, see the orderable addendum at the end of the data sheet.

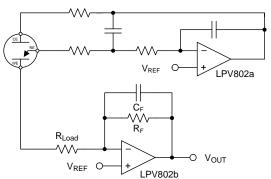

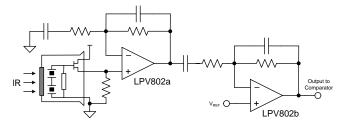

# Nanopower Amplifier in Electrochemical Sensor

#### Nanopower Amplifier in PIR Motion Detector

# **Table of Contents**

| 1 | Features 1                             | 8.1 Application Information                       | 14 |

|---|----------------------------------------|---------------------------------------------------|----|

| 2 | Applications 1                         | 8.2 Typical Application: Three Terminal CO Gas Se |    |

| 3 | Description 1                          | Amplifier                                         |    |

| 4 | Revision History2                      | 8.3 Do's and Don'ts                               |    |

| 5 | Pin Configuration and Functions        | 9 Power Supply Recommendations                    |    |

| 6 | _                                      | 10 Layout                                         | 17 |

| O | Specifications4                        | 10.1 Layout Guidelines                            | 17 |

|   | 6.1 Absolute Maximum Ratings           | 10.2 Layout Example                               | 17 |

|   | 6.2 ESD Ratings 4                      | 11 Device and Documentation Support               |    |

|   | 6.3 Recommended Operating Conditions 4 | 11.1 Device Support                               |    |

|   | 6.4 Thermal Information 4              | 11.2 Receiving Notification of Documentation Upda |    |

|   | 6.5 Electrical Characteristics5        |                                                   |    |

|   | 6.6 Typical Characteristics6           | 11.3 Community Resources                          |    |

| 7 | Detailed Description 12                | 11.4 Related Links                                |    |

|   | 7.1 Overview                           | 11.5 Trademarks                                   |    |

|   | 7.2 Functional Block Diagram           | 11.6 Electrostatic Discharge Caution              | 18 |

|   |                                        | 11.7 Glossary                                     | 18 |

|   | 7.3 Feature Description                | 12 Mechanical, Packaging, and Orderable           |    |

| _ | 7.4 Device Functional Modes            | Information                                       | 19 |

| 8 | Application and Implementation 14      |                                                   |    |

|   |                                        |                                                   |    |

# 4 Revision History

| Changes from Revision A (August 2016) to Revision B                                    |      |  |  |  |

|----------------------------------------------------------------------------------------|------|--|--|--|

| Changed LPV811 Typ Offset Voltage and LPV812 Typ Supply Current in LPV8xx Family table | 1    |  |  |  |

| Deleted LPV801 "Specs Prelim until Release" footnote                                   | 5    |  |  |  |

| Added seporate CMRR line for LPV801                                                    | 5    |  |  |  |

| Changed LPV801 Typical and Maximum Supply Current                                      | 5    |  |  |  |

| Changes from Original (August 2016) to Revision A                                      | Page |  |  |  |

| Changed Product Preview to Production Data                                             | 1    |  |  |  |

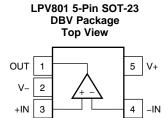

# 5 Pin Configuration and Functions

#### Pin Functions: LPV801 DBV

| PIN  |        | I/O | DESCRIPTION                     |

|------|--------|-----|---------------------------------|

| NAME | NUMBER | 1/0 | DESCRIPTION                     |

| OUT  | 1      | 0   | Output                          |

| -IN  | 4      | I   | Inverting Input                 |

| +IN  | 3      | I   | Non-Inverting Input             |

| V-   | 2      | Р   | Negative (lowest) power supply  |

| V+   | 5      | Р   | Positive (highest) power supply |

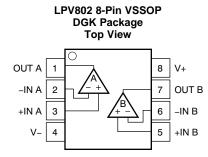

#### Pin Functions: LPV802 DGK

| PIN   |        | 1/0 | DESCRIPTION                     |  |

|-------|--------|-----|---------------------------------|--|

| NAME  | NUMBER | I/O | DESCRIPTION                     |  |

| OUT A | 1      | 0   | Channel A Output                |  |

| -IN A | 2      | 1   | Channel A Inverting Input       |  |

| +IN A | 3      | I   | Channel A Non-Inverting Input   |  |

| V-    | 4      | Р   | Negative (lowest) power supply  |  |

| +IN B | 5      | I   | Channel B Non-Inverting Input   |  |

| -IN B | 6      | I   | Channel B Inverting Input       |  |

| OUT B | 7      | 0   | Channel B Output                |  |

| V+    | 8      | Р   | Positive (highest) power supply |  |

# 6 Specifications

#### 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted) (1)

|                                       |                                     |              | MIN        | MAX        | UNIT |

|---------------------------------------|-------------------------------------|--------------|------------|------------|------|

| Supply voltage                        | $v_{s}, V_{s} = (V+) - (V-)$        | -0.3         | 6          | V          |      |

| Input pipe                            | Voltage (2) (3)                     | Common mode  | (V-) - 0.3 | (V+) + 0.3 | V    |

| Input pins                            |                                     | Differential | (V-) - 0.3 | (V+) + 0.3 | V    |

| Input pins                            | Current                             |              | -10        | 10         | mA   |

| Output short current (4)              | Output short current <sup>(4)</sup> |              | Continuous | Continuous |      |

| Operating tem                         | perature                            |              | -40        | 125        | °C   |

| Storage temperature, T <sub>stg</sub> |                                     |              |            | 150        | °C   |

| Junction temper                       | erature                             | ·            |            | 150        | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Not to exceed -0.3V or +6.0V on ANY pin, referred to V-

#### 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±1000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions. Pins listed as ±2000 V may actually have higher performance.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                          | MIN | NOM MAX | UNIT |

|--------------------------|-----|---------|------|

| Supply voltage (V+ – V–) | 1.6 | 5.5     | V    |

| Specified temperature    | -40 | 125     | °C   |

#### 6.4 Thermal Information

|                  | THERMAL METRIC <sup>(1)</sup>                | LPV801<br>DBV (SOT-23)<br>5 PINS | LPV802<br>DGK<br>(VSSOP)<br>8 PINS | UNIT |

|------------------|----------------------------------------------|----------------------------------|------------------------------------|------|

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 177.4                            | 184.2                              |      |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 133.9                            | 75.3                               |      |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 36.3                             | 105.5                              | °C/W |

| ΨЈТ              | Junction-to-top characterization parameter   | 23.6                             | 13.5                               |      |

| ΨЈВ              | Junction-to-board characterization parameter | 35.7                             | 103.9                              |      |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(3)</sup> Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.3 V beyond the supply rails should be current-limited to 10 mA or less.

<sup>(4)</sup> Short-circuit to Vs/2, one amplifer per package. Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions. Pins listed as ±750 V may actually have higher performance.

# 6.5 Electrical Characteristics

$T_A$  = 25°C,  $V_S$  = 1.8V to 5 V,  $V_{CM}$  =  $V_{OUT}$  =  $V_S/2$ , and  $R_L$ ≥ 10 M $\Omega$  to  $V_S$  / 2, unless otherwise noted.

|                          | PARAMETER                               | TEST CONDITIONS                                                   |                 | MIN | TYP  | MAX  | UNIT               |

|--------------------------|-----------------------------------------|-------------------------------------------------------------------|-----------------|-----|------|------|--------------------|

| OFFSET                   | VOLTAGE                                 |                                                                   |                 |     |      |      |                    |

| V                        | Input offset voltage                    | $V_S = 1.8V$ , 3.3V, and 5V, $V_{CM} = V$ -                       |                 |     | 0.55 | ±3.5 | mV                 |

| V <sub>OS</sub>          | Input offset voltage                    | $V_S = 1.8V$ , 3.3V, and 5V, $V_{CM} = (V+) - 0.9 V$              |                 |     | 0.55 | ±3.5 | IIIV               |

| $\Delta V_{OS}/\Delta T$ | Input offset drift                      | $V_{CM} = V$ - $T_A = V$                                          | :-40°C to 125°C |     | 1    |      | μV/°C              |

| PSRR                     | Power-supply rejection ratio            | $V_S = 1.8V$ to 5V,<br>$V_{CM} = V$ -                             |                 |     | 1.6  | 60   | μV/V               |

| INPUT VO                 | OLTAGE RANGE                            |                                                                   | ·               |     |      |      |                    |

| $V_{CM}$                 | Common-mode voltage range               | V <sub>S</sub> = 5 V                                              |                 | 0   |      | 4.1  | V                  |

| CMRR                     | Common-mode rejection ratio, LPV801     | $(V-) \le V_{CM} \le (V+) - 0.9 \text{ V}, V_S = 5V$              |                 | 77  | 95   |      | dB                 |

| CIVIRR                   | Common-mode rejection ratio, LPV802     | $(V-) \le V_{CM} \le (V+) - 0.9 \text{ V}, V_S = 5V$              |                 | 80  | 98   |      | dB                 |

| INPUT BI                 | AS CURRENT                              |                                                                   |                 |     |      |      |                    |

| $I_{B}$                  | Input bias current                      | V <sub>S</sub> = 1.8V                                             |                 |     | ±100 |      | fA                 |

| Ios                      | Input offset current                    | V <sub>S</sub> = 1.8V                                             |                 |     | ±100 |      | IA                 |

| INPUT IM                 | IPEDANCE                                |                                                                   | ·               |     |      |      |                    |

|                          | Differential                            |                                                                   |                 |     | 7    |      | ~F                 |

|                          | Common mode                             |                                                                   |                 |     | 3    |      | pF                 |

| NOISE                    |                                         |                                                                   |                 |     |      |      |                    |

| $E_n$                    | Input voltage noise                     | f = 0.1  Hz to  10  Hz                                            |                 |     | 6.5  |      | μVp-p              |

| e <sub>n</sub>           | Input voltage noise                     | f = 100 Hz                                                        |                 |     | 340  |      | nV/√ <del>Hz</del> |

|                          | density                                 | f = 1  kHz                                                        |                 |     | 420  |      | 110/ 1112          |

| OPEN-LC                  | OOP GAIN                                |                                                                   |                 |     |      |      |                    |

| A <sub>OL</sub>          | Open-loop voltage gain                  | $(V-) + 0.3 V \le V_0 \le (V+) - 0.3 V, R_L =$                    | 100 kΩ          |     | 120  |      | dB                 |

| OUTPUT                   |                                         | ,                                                                 |                 |     |      |      |                    |

| V <sub>OH</sub>          | Voltage output swing from positive rail | $V_S = 1.8V, R_L = 100 \text{ k}\Omega \text{ to } V^+/2$         |                 | 10  | 3.5  |      | m)/                |

| V <sub>OL</sub>          | Voltage output swing from negative rail | $V_S = 1.8V$ , $R_L = 100 \text{ k}\Omega$ to $V^+/2$             |                 |     | 2.5  | 10   | mV                 |

| I <sub>SC</sub>          | Short-circuit current                   | $V_S = 3.3V$ , Short to $V_S/2$                                   |                 |     | 4.7  |      | mA                 |

| Z <sub>O</sub>           | Open loop output impedance              | f = 1 KHz, I <sub>O</sub> = 0 A                                   |                 |     | 90   |      | $k\Omega$          |

| FREQUE                   | NCY RESPONSE                            |                                                                   |                 |     |      |      |                    |

| GBP                      | Gain-bandwidth product                  | $C_L = 20 \text{ pF}, R_L = 10 \text{ M}\Omega, V_S = 5 \text{V}$ |                 |     | 8    |      | kHz                |

| SR                       | Slew rate (10% to 90%)                  | $G = 1$ , Rising Edge, $C_L = 20$ pF, $V_S = 5$                   | V               |     | 2    |      | V/ms               |

| JIN                      | Siew rate (10% to 30%)                  | $G = 1$ , Falling Edge, $C_L = 20$ pF, $V_S = 5$                  | 5V              |     | 2.1  |      | V/1115             |

| POWER S                  | SUPPLY                                  |                                                                   |                 |     |      |      |                    |

| I <sub>Q-LPV801</sub>    | Quiescent Current                       | $V_{CM} = V_{-}, I_{O} = 0, V_{S} = 3.3 V$                        |                 |     | 450  | 540  | nA                 |

| I <sub>Q-LPV802</sub>    | Quiescent Current,<br>Per Channel       | $V_{CM} = V_{-}, I_{O} = 0, V_{S} = 3.3 V$                        |                 |     | 320  | 415  | nA                 |

# TEXAS INSTRUMENTS

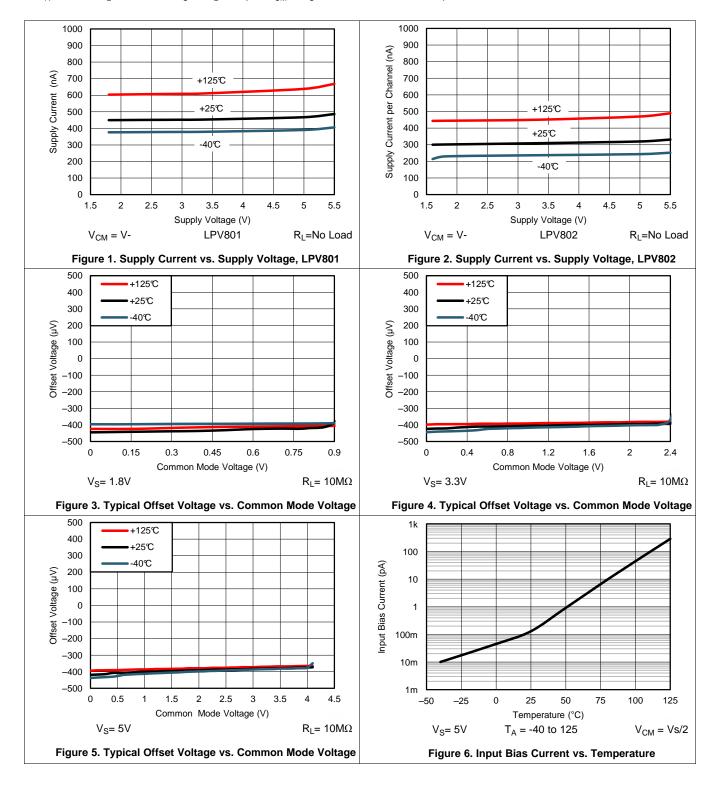

# 6.6 Typical Characteristics

at T\_A = 25°C, R\_L = 10M $\Omega$  to V\_S/2 ,C\_L = 20pF, V\_{CM} = V\_S / 2V unless otherwise specified.

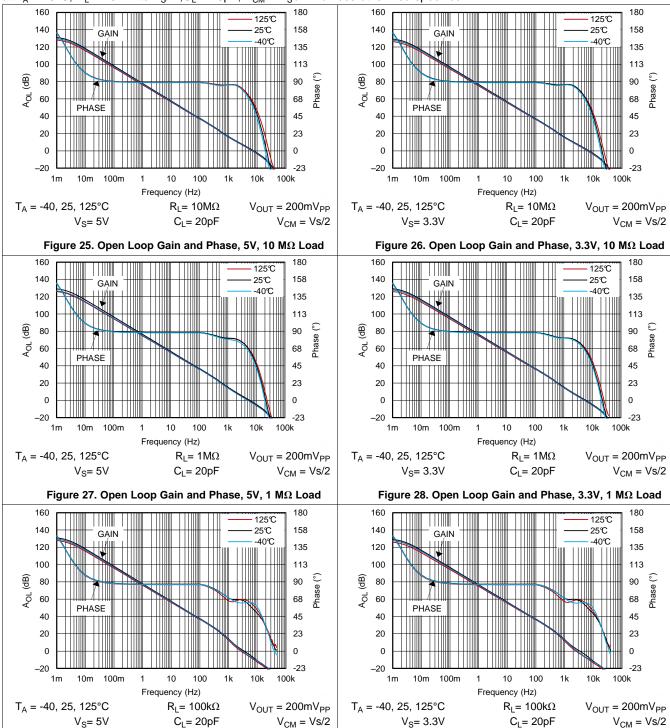

# **Typical Characteristics (continued)**

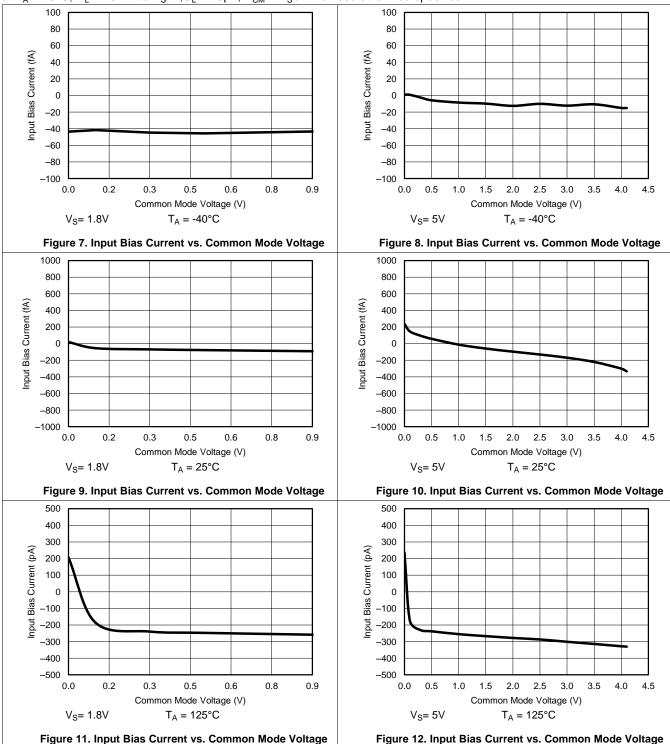

at  $T_A$  = 25°C,  $R_L$  = 10M $\Omega$  to  $V_S/2$  , $C_L$  = 20pF,  $V_{CM}$  =  $V_S$  / 2V unless otherwise specified.

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

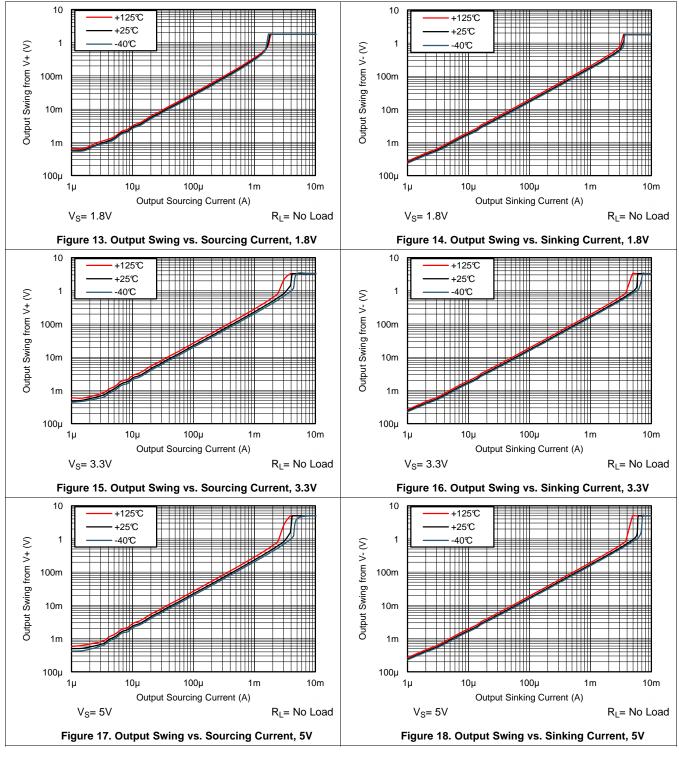

at  $T_A$  = 25°C,  $R_L$  = 10M $\Omega$  to  $V_S/2$  , $C_L$  = 20pF,  $V_{CM}$  =  $V_S$  / 2V unless otherwise specified.

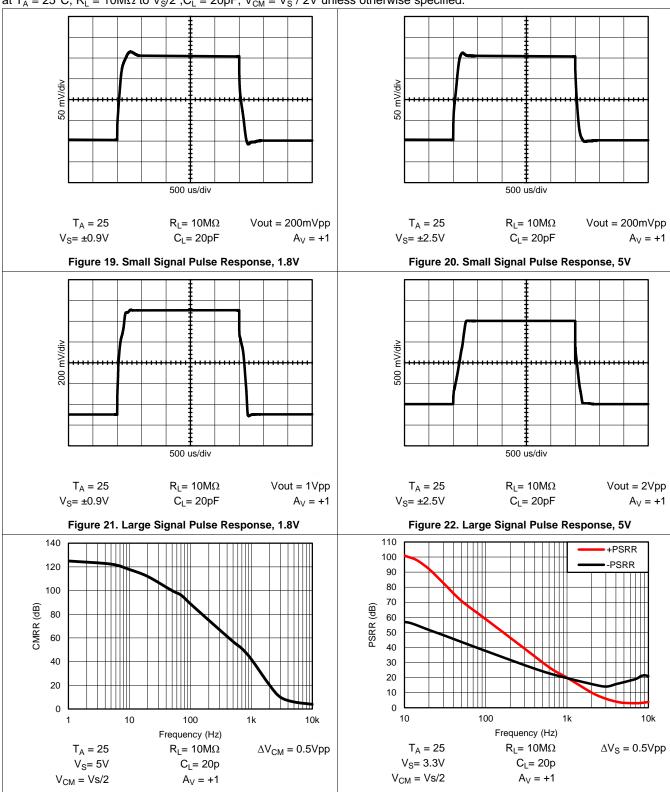

# **Typical Characteristics (continued)**

at  $T_A$  = 25°C,  $R_L$  = 10M $\Omega$  to  $V_S/2$  , $C_L$  = 20pF,  $V_{CM}$  =  $V_S$  / 2V unless otherwise specified.

Figure 24. ±PSRR vs Frequency

Figure 23. CMRR vs Frequency

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

at  $T_A$  = 25°C,  $R_L$  = 10M $\Omega$  to  $V_S/2$  , $C_L$  = 20pF,  $V_{CM}$  =  $V_S$  / 2V unless otherwise specified.

Figure 29. Open Loop Gain and Phase, 5V, 100k $\Omega$  Load

Figure 30. Open Loop Gain and Phase, 3.3V,  $100k\Omega$  Load

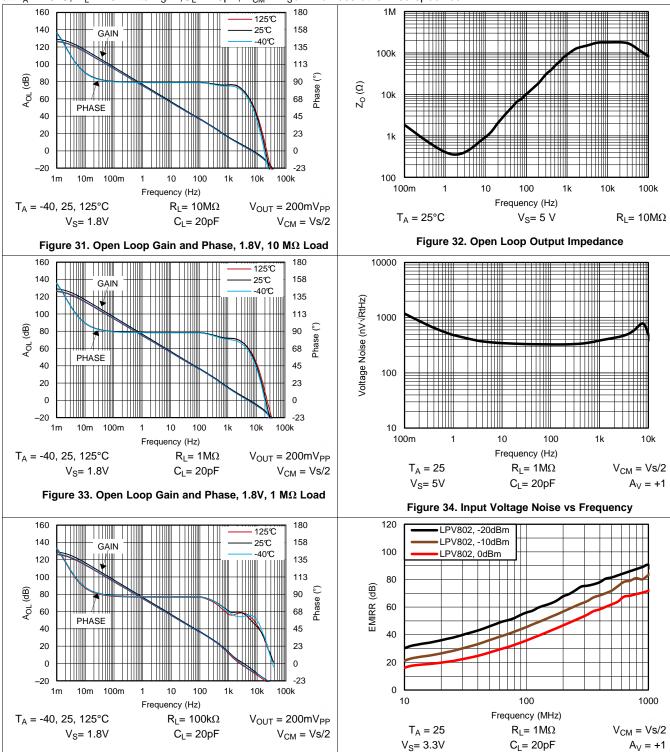

# **Typical Characteristics (continued)**

at  $T_A$  = 25°C,  $R_L$  = 10M $\Omega$  to  $V_S/2$  , $C_L$  = 20pF,  $V_{CM}$  =  $V_S$  / 2V unless otherwise specified.

Figure 36. EMIRR Performance

Figure 35. Open Loop Gain and Phase, 1.8V, 100k $\Omega$  Load

# 7 Detailed Description

#### 7.1 Overview

The LPV801 (single) and LPV802 (dual) series nanoPower CMOS operational amplifiers are designed for long-life battery-powered and energy harvested applications. They operate on a single supply with operation as low as 1.6V. The output is rail-to-rail and swings to within 3.5mV of the supplies with a  $100 \text{k}\Omega$  load. The common-mode range extends to the negative supply making it ideal for single-supply applications. EMI protection has been employed internally to reduce the effects of EMI.

Parameters that vary significantly with operating voltages or temperature are shown in the *Typical Characteristics* curves.

#### 7.2 Functional Block Diagram

## 7.3 Feature Description

The amplifier's differential inputs consist of a non-inverting input (+IN) and an inverting input (-IN). The amplifier amplifies only the difference in voltage between the two inputs, which is called the differential input voltage. The output voltage of the op-amp  $V_{OUT}$  is given by Equation 1:

$$\mathsf{V}_\mathsf{OUT} = \mathsf{A}_\mathsf{OL} \; (\mathsf{IN}^{\scriptscriptstyle +} - \mathsf{IN}^{\scriptscriptstyle -})$$

where

A<sub>OL</sub> is the open-loop gain of the amplifier, typically around 120 dB (1,000,000x, or 1,000,000 Volts per microvolt).

#### 7.4 Device Functional Modes

#### 7.4.1 Negative-Rail Sensing Input

The input common-mode voltage range of the LPV80x extends from (V-) to (V+) - 0.9 V. In this range, low offset can be expected with a minimum of 80dB CMRR. The LPV80x is protected from output "inversions" or "reversals".

#### 7.4.2 Rail to Rail Output Stage

The LPV80x output voltage swings 3.5 mV from rails at 1.8 V supply, which provides the maximum possible dynamic range at the output. This is particularly important when operating on low supply voltages.

The LPV80x Maximum Output Voltage Swing graph defines the maximum swing possible under a particular output load.

#### 7.4.3 Design Optimization for Nanopower Operation

When designing for ultralow power, choose system feedback components carefully. To minimize quiecent current consumption, select large-value feedback resistors. Any large resistors will react with stray capacitance in the circuit and the input capacitance of the operational amplifier. These parasitic RC combinations can affect the stability of the overall system. A feedback capacitor may be required to assure stability and limit overshoot or gain peaking.

When possible, use AC coupling and AC feedback to reduce static current draw through the feedback elements. Use film or ceramic capacitors since large electolytics may have large static leakage currents in the nanoamps.

#### **Device Functional Modes (continued)**

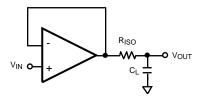

#### 7.4.4 Driving Capacitive Load

The LPV80x is internally compensated for stable unity gain operation, with a 8 kHz typical gain bandwidth. However, the unity gain follower is the most sensitive configuration to capacitive load. The combination of a capacitive load placed directly on the output of an amplifier along with the amplifier's output impedance creates a phase lag, which reduces the phase margin of the amplifier. If the phase margin is significantly reduced, the response will be under damped which causes peaking in the transfer and, when there is too much peaking, the op amp might start oscillating.

In order to drive heavy (>50pF) capacitive loads, an isolation resistor,  $R_{\rm ISO}$ , should be used, as shown in Figure 37. By using this isolation resistor, the capacitive load is isolated from the amplifier's output. The larger the value of  $R_{\rm ISO}$ , the more stable the amplifier will be. If the value of  $R_{\rm ISO}$  is sufficiently large, the feedback loop will be stable, independent of the value of  $C_{\rm L}$ . However, larger values of  $R_{\rm ISO}$  result in reduced output swing and reduced output current drive. The recommended value for  $R_{\rm ISO}$  is 30-50k $\Omega$ .

Figure 37. Resistive Isolation Of Capacitive Load

# 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

The LPV80x is a ultra-low power operational amplifier that provides 8 kHz bandwidth with only 320nA typical quiescent current, and near precision drift specifications. These rail-to-rail output amplifiers are specifically designed for battery-powered applications. The input common-mode voltage range extends to the negative supply rail and the output swings to within millivolts of the rails, maintaining a wide dynamic range.

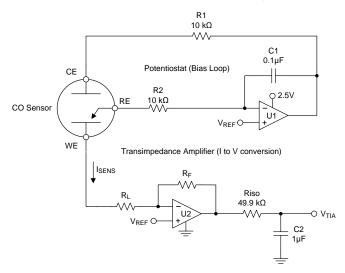

#### 8.2 Typical Application: Three Terminal CO Gas Sensor Amplifier

Figure 38. Three Terminal Gas Sensor Amplifer Schematic

#### 8.2.1 Design Requirements

Figure 38 shows a simple micropower potentiostat circuit for use with three terminal unbiased CO sensors, though it is applicable to many other type of three terminal gas sensors or electrochemical cells.

The basic sensor has three electrodes; The Sense or Working Electrode ("WE"), Counter Electrode ("CE") and Reference Electrode ("RE"). A current flows between the CE and WE proportional to the detected concentration.

The RE monitors the potential of the internal reference point. For an unbiased sensor, the WE and RE electrodes must be maintained at the same potential by adjusting the bias on CE. Through the Potentiostat circuit formed by U1, the servo feedback action will maintain the RE pin at a potential set by  $V_{REF}$ .

R1 is to maintain stability due to the large capacitence of the sensor. C1 and R2 form the Potentiostat integrator and set the feedback time constant.

U2 forms a transimpedance amplifer ("TIA") to convert the resulting sensor current into a proportional voltage. The transimpedance gain, and resulting sensitivity, is set by R<sub>F</sub> according to Equation 2.

$$V_{TIA} = (-1 * R_F) + V_{REF}$$

(2)

$R_L$  is a load resistor of which the value is normally specified by the sensor manufacturer (typically 10 ohms). The potential at WE is set by the applied  $V_{REF.}$  Riso provides capacitive isolation and, combined with C2, form the output filter and ADC reservoir capacitor to drive the ADC.

# Typical Application: Three Terminal CO Gas Sensor Amplifier (continued)

#### 8.2.2 Detailed Design Procedure

For this example, we will be using a CO sensor with a sensitivity of 69nA/ppm. The supply votlage and maximum ADC input voltage is 2.5V, and the maximum concentration is 300ppm.

First the V<sub>REF</sub> voltage must be determined. This voltage is a compromise between maximum headroom and resolution, as well as allowance for "footroom" for the minimum swing on the CE terminal, since the CE terminal generally goes negative in relation to the RE potential as the concentration (sensor current) increases. Bench measurements found the difference between CE and RE to be 180mV at 300ppm for this particular sensor.

To allow for negative CE swing "footroom" and voltage drop across the 10k resistor, 300mV was chosen for  $V_{\text{REF}}$ .

Therefore +300mV will be used as the minimum V<sub>ZERO</sub> to add some headroom.

$V_{ZERO} = V_{REF} = +300 \text{mV}$

#### where

- V<sub>ZERO</sub> is the zero concentration voltage

- V<sub>REF</sub> is the reference voltage (300mV)

(3)

Next we calculate the maximum sensor current at highest expected concentration:

$I_{SENSMAX} = I_{PERPPM} * ppmMAX = 69nA * 300ppm = 20.7uA$

#### where

- I<sub>SENSMAX</sub> is the maximum expected sensor current

- I<sub>PERPPM</sub> is the manufacturer specified sensor current in Amps per ppm

- ppmMAX is the maximum required ppm reading

(4)

Now find the available output swing range above the reference voltage available for the measurement:

$$V_{SWING} = V_{OUTMAX} - V_{ZERO} = 2.5V - 0.3V = 2.2V$$

#### where

- V<sub>SWING</sub> is the expected change in output voltage

- V<sub>OUTMAX</sub> is the maximum amplifer output swing (usually near V+)

(5)

Now we calculate the transimpedance resistor (R<sub>F</sub>) value using the maximum swing and the maximum sensor current:

$$R_F = V_{SWING} / I_{SENSMAX} = 2.2V / 20.7\mu A = 106.28 k\Omega$$

(we will use 110 k $\Omega$  for a common value) (6)

# TEXAS INSTRUMENTS

# Typical Application: Three Terminal CO Gas Sensor Amplifier (continued)

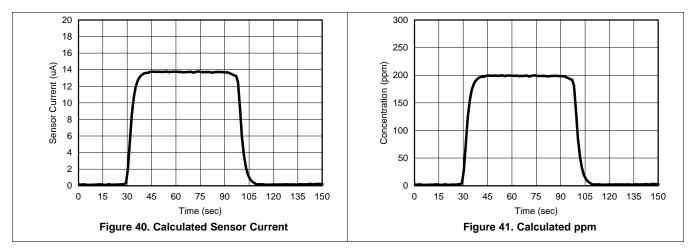

#### 8.2.3 Application Curve

Figure 39. Monitored Voltages when exposed to 200ppm CO

Figure 39 shows the resulting circuit voltages when the sensor was exposed to 200ppm step of carbon monoxide gas.  $V_C$  is the monitored CE pin voltage and clearly shows the expected CE voltage dropping below the WE voltage,  $V_W$ , as the concentration increases.

$V_{TIA}$  is the output of the transimpedance amplifer U2.  $V_{DIFF}$  is the calculated difference between  $V_{REF}$  and  $V_{TIA}$ , which will be used for the ppm calculation.

Figure 40 shows the calculated sensor current using the formula in Equation 7:

$$I_{SENSOR} = V_{DIFF} / R_F = 1.52 \text{V} / 110 \text{ k}\Omega = 13.8 \text{uA}$$

(7)

Equation 8 shows the resulting conversion of the sensor current into ppm.

$$ppm = I_{SENSOR} / I_{PERPPM} = 13.8 \mu A / 69 nA = 200$$

(8)

Total supply current for the amplifier section is less than 700 nA, minus sensor current. Note that the sensor current is sourced from the amplifier output, which in turn comes from the amplifier supply voltage. Therefore, any continuous sensor current must also be included in supply current budget calculations.

#### 8.3 Do's and Don'ts

Do properly bypass the power supplies.

Do add series resistance to the output when driving capacitive loads, particularly cables, Muxes and ADC inputs.

Do add series current limiting resistors and external schottky clamp diodes if input voltage is expected to exceed the supplies. Limit the current to 1mA or less (1K $\Omega$  per volt).

# 9 Power Supply Recommendations

The LPV80x is specified for operation from 1.6 V to 5.5 V (±0.8 V to ±2.75 V) over a -40°C to 125°C temperature range. Parameters that can exhibit significant variance with regard to operating voltage or temperature are presented in the *Typical Characteristics*.

#### **CAUTION**

Supply voltages larger than 6 V can permanently damage the device.

For proper operation, the power supplies must be properly decoupled. For decoupling the supply lines it is suggested that 100 nF capacitors be placed as close as possible to the operational amplifier power supply pins. For single supply, place a capacitor between V<sup>+</sup> and V<sup>-</sup> supply leads. For dual supplies, place one capacitor between V<sup>+</sup> and ground, and one capacitor between V<sup>-</sup> and ground.

Low bandwidth nanopower devices do not have good high frequency (> 1 kHz) AC PSRR rejection against high-frequency switching supplies and other 1 kHz and above noise sources, so extra supply filtering is recommended if kilohertz or above noise is expected on the power supply lines.

# 10 Layout

#### 10.1 Layout Guidelines

The V+ pin should be bypassed to ground with a low ESR capacitor.

The optimum placement is closest to the V+ and ground pins.

Care should be taken to minimize the loop area formed by the bypass capacitor connection between V+ and ground.

The ground pin should be connected to the PCB ground plane at the pin of the device.

The feedback components should be placed as close to the device as possible to minimize strays.

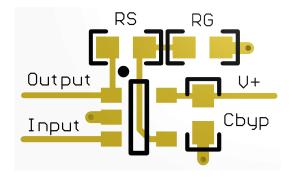

# 10.2 Layout Example

Figure 42. SOT-23 Layout Example (Top View)

# 11 Device and Documentation Support

#### 11.1 Device Support

#### 11.1.1 Development Support

TINA-TI SPICE-Based Analog Simulation Program

DIP Adapter Evaluation Module

TI Universal Operational Amplifier Evaluation Module

TI FilterPro Filter Design Software

#### 11.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

### 11.3 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.4 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to sample or buy.

Table 1. Related Links

| PARTS  | PRODUCT FOLDER | SAMPLE & BUY | TECHNICAL DOCUMENTS | TOOLS &<br>SOFTWARE | SUPPORT & COMMUNITY |

|--------|----------------|--------------|---------------------|---------------------|---------------------|

| LPV801 | Click here     | Click here   | Click here          | Click here          | Click here          |

| LPV802 | Click here     | Click here   | Click here          | Click here          | Click here          |

#### 11.5 Trademarks

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

### 11.6 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 11.7 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com 2-Dec-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins   | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6)   |

|-----------------------|--------|---------------|------------------|-----------------------|------|-------------------------------|----------------------------|--------------|--------------------|

| LPV801DBVR            | Active | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes  | (4)<br>SN                     | (5)<br>Level-1-260C-UNLIM  | -40 to 125   | 15VM               |

|                       | Active | Production    | · /1             |                       |      |                               |                            | -40 (0 125   |                    |

| LPV801DBVR.B          | Active | Production    | SOT-23 (DBV)   5 | 3000   LARGE T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125   | 15VM               |

| LPV801DBVT            | Active | Production    | SOT-23 (DBV)   5 | 250   SMALL T&R       | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125   | 15VM               |

| LPV801DBVT.B          | Active | Production    | SOT-23 (DBV)   5 | 250   SMALL T&R       | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125   | 15VM               |

| LPV802DGKR            | Active | Production    | VSSOP (DGK)   8  | 2500   LARGE T&R      | Yes  | NIPDAU   SN<br>  NIPDAUAG     | Level-1-260C-UNLIM         | -40 to 125   | (L802, LPV)<br>802 |

| LPV802DGKR.B          | Active | Production    | VSSOP (DGK)   8  | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | (L802, LPV)<br>802 |

| LPV802DGKT            | Active | Production    | VSSOP (DGK)   8  | 250   SMALL T&R       | Yes  | NIPDAU   SN<br>  NIPDAUAG     | Level-1-260C-UNLIM         | -40 to 125   | (L802, LPV)<br>802 |

| LPV802DGKT.B          | Active | Production    | VSSOP (DGK)   8  | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | (L802, LPV)<br>802 |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 2-Dec-2025

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 5-Sep-2025

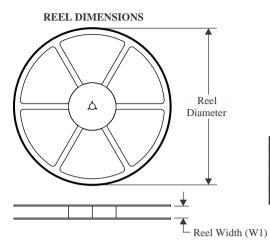

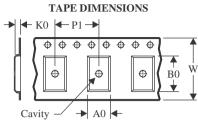

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

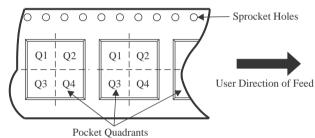

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device     | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LPV801DBVR | SOT-23          | DBV                | 5 | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LPV801DBVR | SOT-23          | DBV                | 5 | 3000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LPV801DBVT | SOT-23          | DBV                | 5 | 250  | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LPV801DBVT | SOT-23          | DBV                | 5 | 250  | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LPV802DGKR | VSSOP           | DGK                | 8 | 2500 | 330.0                    | 12.4                     | 5.25       | 3.35       | 1.25       | 8.0        | 12.0      | Q1               |

| LPV802DGKT | VSSOP           | DGK                | 8 | 250  | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LPV802DGKT | VSSOP           | DGK                | 8 | 250  | 330.0                    | 12.4                     | 5.25       | 3.35       | 1.25       | 8.0        | 12.0      | Q1               |

www.ti.com 5-Sep-2025

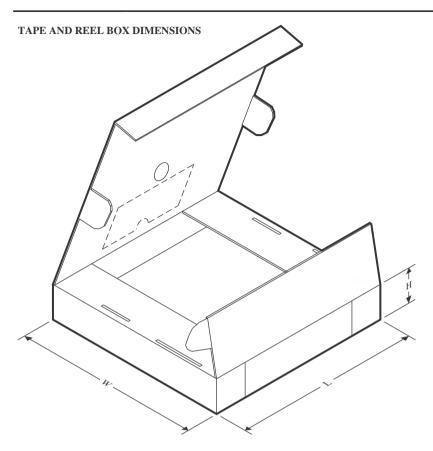

### \*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LPV801DBVR | SOT-23       | DBV             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| LPV801DBVR | SOT-23       | DBV             | 5    | 3000 | 208.0       | 191.0      | 35.0        |

| LPV801DBVT | SOT-23       | DBV             | 5    | 250  | 208.0       | 191.0      | 35.0        |

| LPV801DBVT | SOT-23       | DBV             | 5    | 250  | 210.0       | 185.0      | 35.0        |

| LPV802DGKR | VSSOP        | DGK             | 8    | 2500 | 366.0       | 364.0      | 50.0        |

| LPV802DGKT | VSSOP        | DGK             | 8    | 250  | 353.0       | 353.0      | 32.0        |

| LPV802DGKT | VSSOP        | DGK             | 8    | 250  | 366.0       | 364.0      | 50.0        |

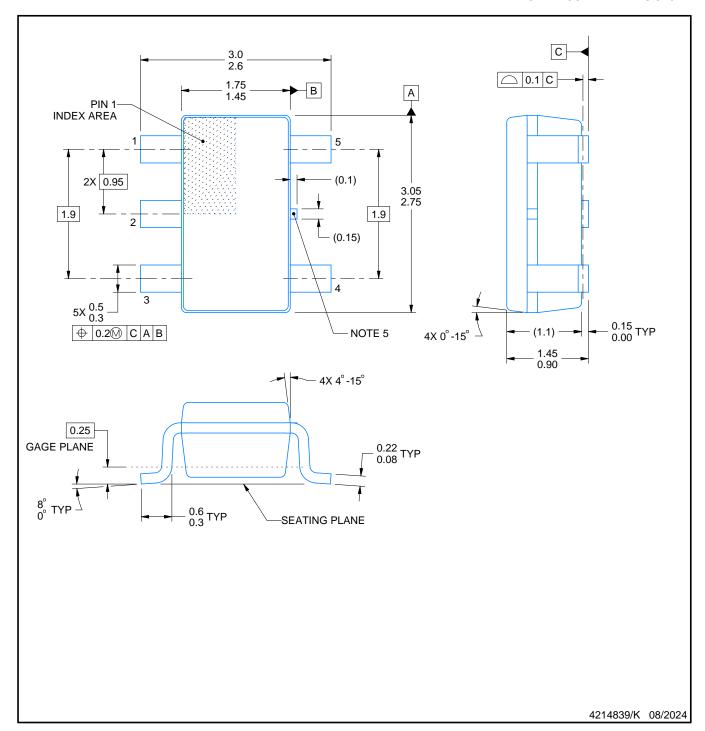

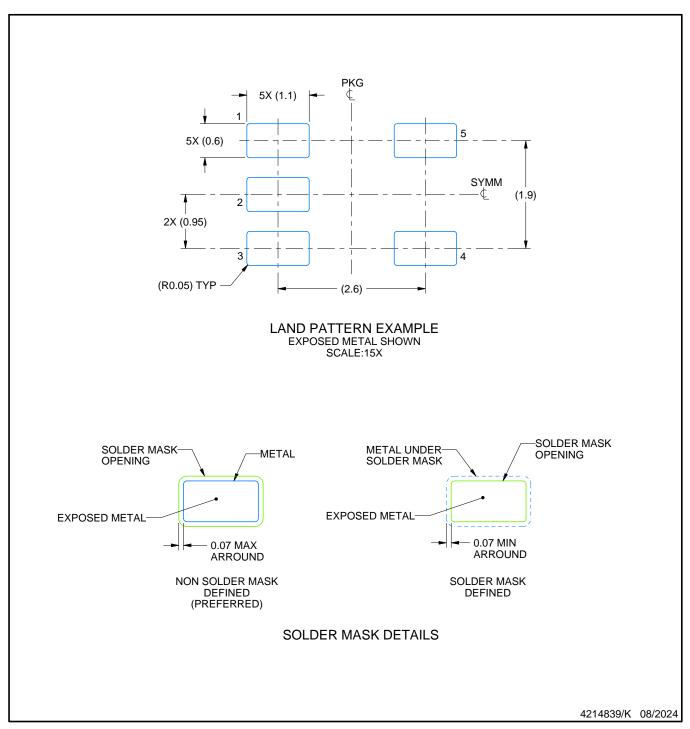

SMALL OUTLINE TRANSISTOR

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Reference JEDEC MO-178.

- 4. Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25 mm per side.

- 5. Support pin may differ or may not be present.

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

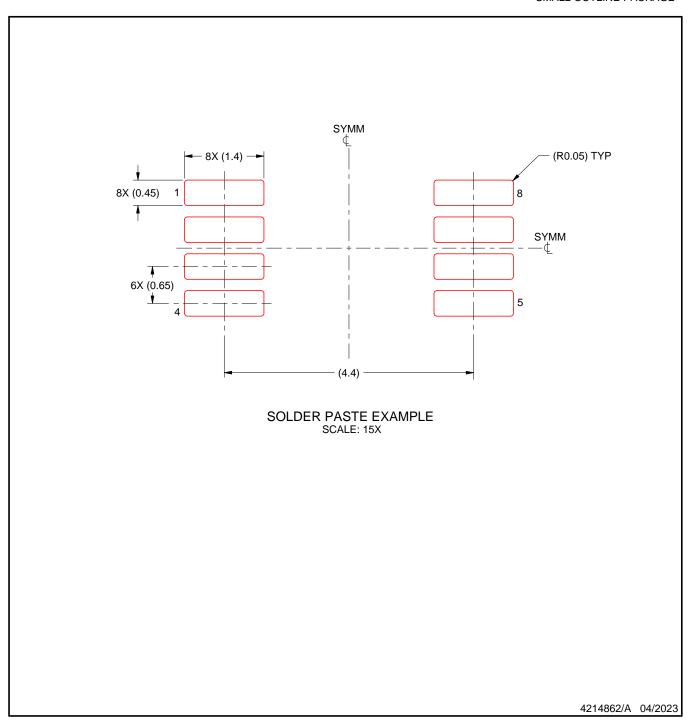

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

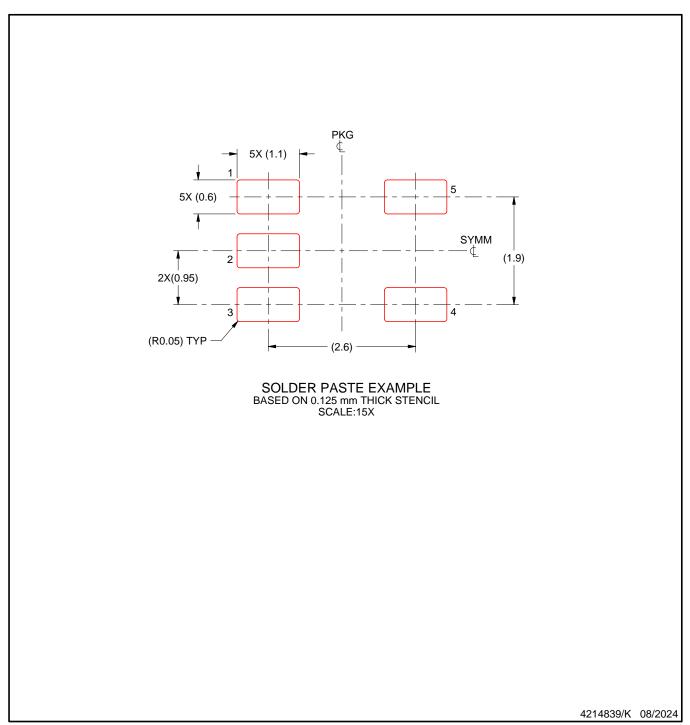

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

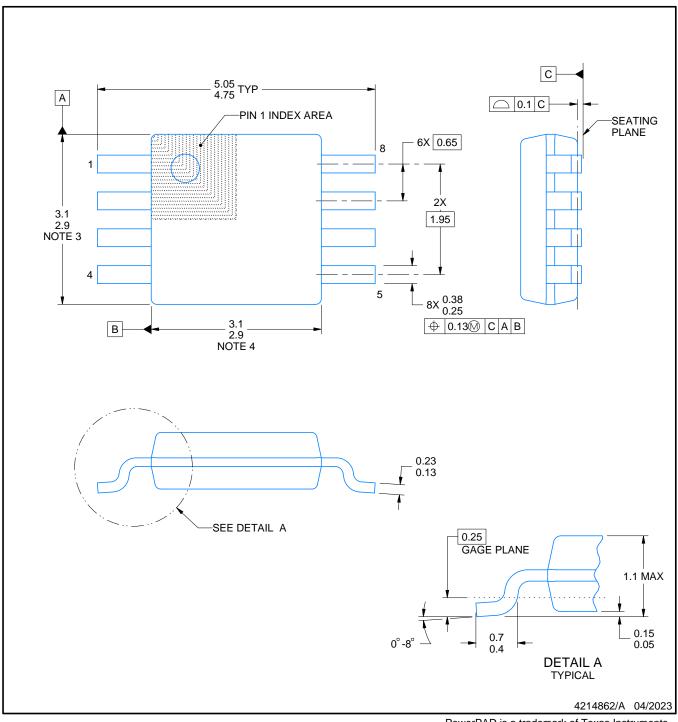

SMALL OUTLINE PACKAGE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187.

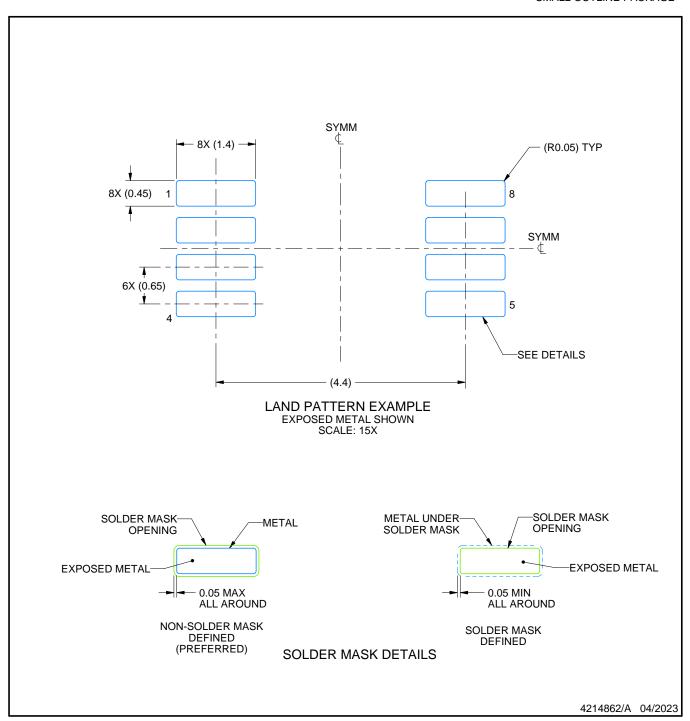

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

- 9. Size of metal pad may vary due to creepage requirement.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025