# SCAN928028 8 Channel 10:1 Serializer with IEEE 1149.1 and At-Speed BIST

Check for Samples: SCAN928028

### **FEATURES**

- IEEE 1149.1 (JTAG) Compliant and At-Speed BIST Test Mode.

- All 8 Channels Synchronous to One Parallel Clock Rate, from 18 to 66 MHz

- Duplicates Function of Multiple DS92LV1021 and '1023 10-Bit Serializer Devices

- Serializes from One to Eight 10-Bit Parallel Inputs into Data Streams with Embedded Clock

- Eight 5 mA Modified Bus LVDS Outputs that are Capable to Drive Double Terminations

- @Speed Test PRBS Generation to Check LVDS Transmission Path to SCAN921224, SCAN921226, SCAN921260, or SCAN926260

- · On Chip Filtering for PLL

- 740mW Typ Power Dissipation (Loaded, PRBS, 66MHz, 3.3V)

- High Impedance Inputs and Outputs on Power off

- Single Power Supply at +3.3V (+/-10%)

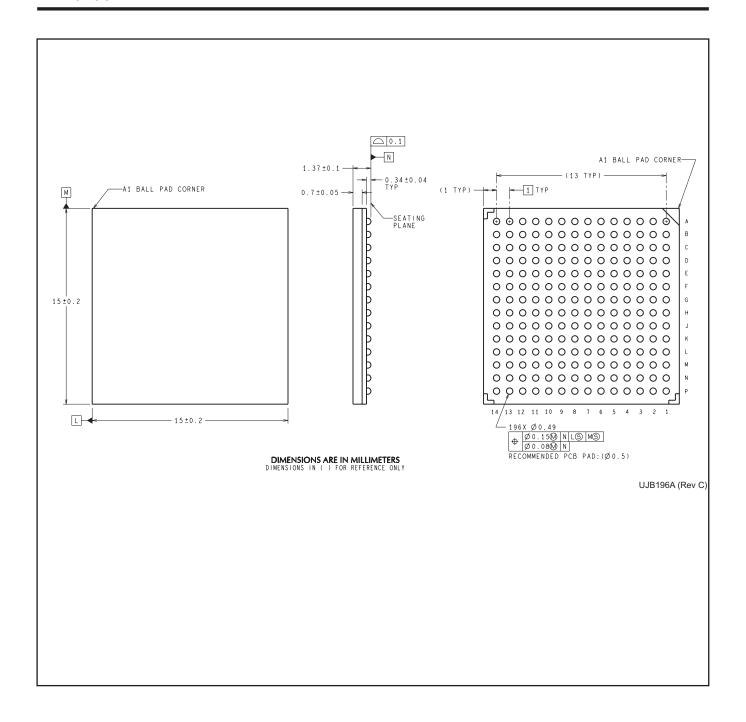

- 196-pin NFBGA Package

- Industrial Temperature Range Operation: -40 to +85°C

### **DESCRIPTION**

The SCAN928028 integrates eight serializer devices into a single chip. The SCAN928028 can simultaneously serialize up to eight 10-bit data streams. The 10-bit parallel inputs are LVTTL signal levels. The serialized outputs are LVDS signals with extra drive current for point-to-point and lightly loaded multidrop applications. Each serializer block in the SCAN928028 operates independently by using strobes from a single shared PLL.

The SCAN928028 uses a single +3.3V power supply with a typical power dissipation of 740mW (3.3V / PRBS / 66 MHz). Each serializer channel has a unique power down control to further conserve power consumption.

For high-speed LVDS serial data transmission, line quality is essential, thus the SCAN928028 includes an @SPEED TEST function. Each Serializer channel has the ability to internally generate a PRBS data pattern. This pattern is received by specific (SCAN921224) deserializers which have verification complement **PRBS** circuit. The deserializer checks the data pattern for bit errors and reports any errors on the test verification pins on the deserializer.

For additional information - please see the Application Information section in this datasheet.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

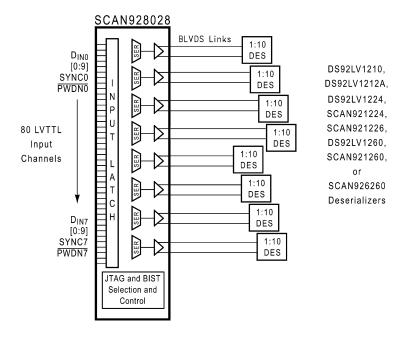

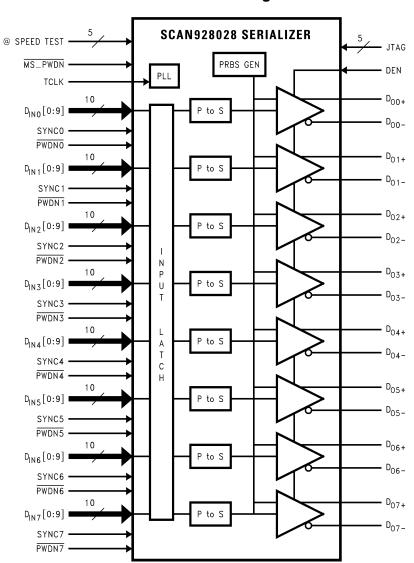

### **Block Diagram**

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **Absolute Maximum Ratings**(1)(2)

|                                     | 90                                |                                  |  |

|-------------------------------------|-----------------------------------|----------------------------------|--|

| Supply Voltage (V <sub>CC</sub> )   | Supply Voltage (V <sub>CC</sub> ) |                                  |  |

| LVCMOS/LVTTL Input Voltage          |                                   | -0.3V to (V <sub>CC</sub> +0.3V) |  |

| Bus LVDS Driver Output Voltage      |                                   | -0.3V to +3.9V                   |  |

| Bus LVDS Output Short Circuit Durat | ion                               | 10ms                             |  |

| Declara Thermal Decistors           | θ <sub>JA</sub> 196 NFBGA:        | 34°C/W                           |  |

| Package Thermal Resistance          | θ <sub>JC</sub> 196 NFBGA:        | 8°C/W                            |  |

| Storage Temperature                 |                                   | −65°C to +150°C                  |  |

| Junction Temperature                |                                   | +125°C                           |  |

| Lead Temperature                    | (Soldering, 4 seconds)            | +225°C                           |  |

| ESD Rating (HBM)                    | ±1.5kV                            |                                  |  |

| Reliability Information             | Transistor Count:                 | 44.8k                            |  |

|                                     |                                   |                                  |  |

- (1) Absolute Maximum Ratings are those values beyond which the safety of the device cannot be specified. They are not meant to imply that the devices should be operated at these limits. The table of Electrical Characteristics specifies conditions of device operation.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

## **Recommended Operating Conditions**

|                                                  | Min | Тур | Max | Units |

|--------------------------------------------------|-----|-----|-----|-------|

| Supply Voltage (V <sub>CC</sub> )                | 3.0 | 3.3 | 3.6 | V     |

| Operating Free Air Temperature (T <sub>A</sub> ) | -40 | +25 | +85 | °C    |

| Clock Rate                                       | 18  |     | 66  | MHz   |

### **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified. (1)(2)

| Symbol                        | Parameter                                 | Conditions                                         | Pin/Freq.                                                                        | Min | Тур   | Max             | Units |

|-------------------------------|-------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------|-----|-------|-----------------|-------|

| LVCMOS/L                      | VTTL DC Specifications                    |                                                    | 1                                                                                |     |       |                 |       |

| V <sub>IH</sub>               | High Level Input Voltage                  |                                                    | DINn[0-9], TCLK, PWDNn, SYNCn, DEN, BIST_ACT, TCK, TDI, TMS, TRST, BIST_SEL<0:3> | 2.0 |       | V <sub>CC</sub> | V     |

|                               |                                           |                                                    | MS_PWDN                                                                          | 2.2 |       | $V_{CC}$        | V     |

| $V_{IL}$                      | Low Level Input Voltage                   |                                                    | DINn[0-9], TCLK,                                                                 | GND |       | 0.8             | V     |

| $V_{CL}$                      | Input Clamp Voltage                       | I <sub>CL</sub> = −18 mA                           | PWDNn, MS_PWDN, SYNCn, DEN, BIST_ACT, TCK, TDI, TMS, TRST, BIST_SEL<0:3>         |     | -0.87 | -1.5            | V     |

| I <sub>IN</sub>               | Input Current                             | V <sub>IN</sub> = 0V or 3.6V                       | DINn[0-9], TCLK, PWDNn, MS_PWDN, SYNCn, TCK, DEN, BIST_ACT                       | -10 | +/- 1 | +10             | μA    |

|                               |                                           |                                                    | TDI, TMS, TRST,<br>BIST_SEL<0:3> <sup>(3)</sup>                                  | -20 |       | +10             | μA    |

| V <sub>OH</sub>               | High level Output Voltage                 | I <sub>OH</sub> = -12mA                            |                                                                                  | 2.4 |       |                 | V     |

| $V_{OL}$                      | Low level Output Voltage                  | I <sub>OL</sub> = 12mA                             | TDO                                                                              |     |       | 0.5             | V     |

| Ios                           | Output Short Circuit Current              | V <sub>OUT</sub> = 0V                              | TDO                                                                              |     | -95   | -125            | mA    |

| $I_{OZ}$                      | Tri-state Output Current                  | $V_{OUT} = 0V \text{ or } 3.6V$                    |                                                                                  | -10 |       | +10             | uA    |

| Bus LVDS                      | DC Specifications                         |                                                    |                                                                                  |     |       |                 |       |

| Over recom                    | nmended operating supply and temp         | erature unless otherwise                           | specified.                                                                       |     |       |                 | _     |

| $V_{OD}$                      | Output Differential Voltage (DO+) - (DO-) |                                                    |                                                                                  | 350 | 500   |                 | mV    |

| $\Delta V_{OD}$               | Output Differential Voltage<br>Unbalance  | RL = $100\Omega$ , $C_L = 10pF$<br>to GND          |                                                                                  |     | 3     | 35              | mV    |

| Vos                           | Offset Voltage                            |                                                    |                                                                                  | 1.0 | 1.1   | 1.3             | V     |

| $\Delta V_{OS}$               | Offset Voltage Unbalance                  |                                                    |                                                                                  |     | 2     | 35              | mV    |

| Ios                           | Output Short Circuit Current              | $\frac{DO = 0V, Din = H,}{MS_PWDN and DEN =}$ 2.4V | DOn+, DOn-                                                                       |     | -50   | -90             | mA    |

| I <sub>OZ</sub>               | Tri-state Output Current                  | MS_PWDN or DEN = 0.8V, DO = 0V OR VDD              |                                                                                  | -10 | +/-1  | 10              | μA    |

| I <sub>OX</sub>               | Power-Off Output Current                  | VDD = 0V, DO = 0V or 3.6V                          |                                                                                  | -10 | +/- 1 | 10              | μA    |

| SER/DES S                     | SUPPLY CURRENT (apply to pins             | DVDD, PVDD and AVDD                                | <b>)</b> )                                                                       |     |       |                 |       |

| Over recom                    | nmended operating supply and temp         | erature ranges unless oth                          | erwise specified.                                                                |     |       |                 |       |

|                               | Supply Current                            | $V_{CC} = 3.6V$ ,                                  | f = 18MHz                                                                        |     | 145   |                 | mA    |

| I <sub>CCD</sub>              | (SYNC pattern)                            | R <sub>L</sub> = 100 Ω                             | f = 66MHz                                                                        |     | 175   |                 | mA    |

|                               | Worst Case Supply Current                 | $V_{CC} = 3.6V$ ,                                  | f = 18 MHz                                                                       |     | 148   | 166             | mA    |

|                               | (Checker-board pattern)                   | $R_L = 100 \Omega$ Figure 1                        | f = 66 MHz                                                                       |     | 263   | 350             | mA    |

| I <sub>CCXD</sub><br>(Master) | Supply Current Powered Down               | MS_PWDN = 0.1V,<br>DEN = 0V                        |                                                                                  |     | 0.35  | 1.0             | mA    |

| I <sub>CCXD</sub>             | Worst Cast Power Saving Per               | $\overline{\text{MS}\_\text{PWDN}} = 3\text{V},$   | 66 MHz                                                                           |     | 6     |                 | mA    |

| (Ind. Ch)                     | Channel Disabled                          | $\overline{PWDNn} = 0V$                            | 18 MHz                                                                           |     | 3.6   |                 | mA    |

Product Folder Links: SCAN928028

Typical values are given for  $V_{CC}=3.3V$  and  $T_A=+25^{\circ}C$ . Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground except VOD, and  $\Delta$ VOD which are differential voltages.

BIST\_SEL have a weak internal pull-up. In a noisy operating environment, it is recommended that an external pull up be used to ensure that BIST\_SEL is in the high state.

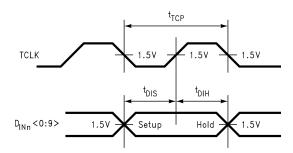

# Serializer Timing Requirements for TCLK

Over recommended operating supply and temperature ranges unless otherwise specified. (1) (2)

| Symbol            | Parameter                     | Conditions   | Pin/Freq. | Min   | Тур | Max  | Units             |

|-------------------|-------------------------------|--------------|-----------|-------|-----|------|-------------------|

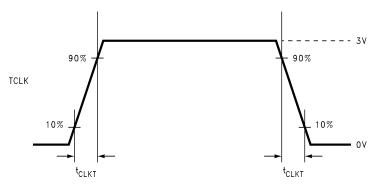

| t <sub>TCP</sub>  | Transmit Clock Period         |              |           | 15.15 |     | 55.5 | ns                |

| t <sub>TCIH</sub> | Transmit Clock High<br>Time   |              |           | 30    | 50  | 70   | %                 |

| t <sub>TCIL</sub> | Transmit Clock Low<br>Time    | See Figure 3 | TCLK      | 30    | 50  | 70   | %                 |

| t <sub>CLKT</sub> | TCLK Input Transition<br>Time |              |           |       | 3   | 6    | ns                |

| t <sub>JIT</sub>  | TCLK Input Jitter             |              |           |       |     | 80   | ps <sub>rms</sub> |

(1) Typical values are given for  $V_{CC} = 3.3V$  and  $T_A = +25$ °C.

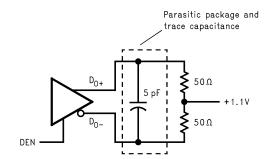

# **Serializer Switching Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified. (1)(2)

| Symbol            | Parameter                               | Conditions                                             | Pin/Freq.                           | Min                    | Тур                    | Max                  | Units |

|-------------------|-----------------------------------------|--------------------------------------------------------|-------------------------------------|------------------------|------------------------|----------------------|-------|

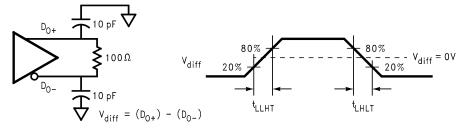

| t <sub>LLHT</sub> | Bus LVDS Low-to-High<br>Transition Time | $R_{L} = 100\Omega$                                    | DON DON                             | 190                    | 330                    | 400                  | ps    |

| t <sub>LHLT</sub> | Bus LVDS High-to-Low<br>Transition Time | C <sub>L</sub> =10pF to GND <sup>(3)</sup><br>Figure 2 | DOn+, DOn-                          | 190                    | 330                    | 400                  | ps    |

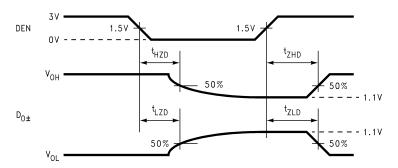

| t <sub>DIS</sub>  | DIN (0-9) Setup to TCLK                 | $R_L = 100\Omega$ ,                                    | DING(0.0) TOLK                      | 2.0                    |                        |                      | ns    |

| t <sub>DIH</sub>  | DIN (0-9) Hold from<br>TCLK             | C <sub>L</sub> =10pF to GND<br>Figure 4                | DINn(0-9), TCLK                     | 1.5                    |                        |                      | ns    |

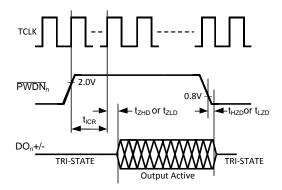

| t <sub>HZD</sub>  | DO ± HIGH to<br>Tri-state Delay         |                                                        |                                     |                        | 5.7                    | 12                   | ns    |

| t <sub>LZD</sub>  | DO ± LOW to Tri-state<br>Delay          | $R_L = 100\Omega$ ,                                    | DOT DOT DEN                         |                        | 6.9                    | 12                   | ns    |

| t <sub>ZHD</sub>  | DO ± Tri-state to HIGH<br>Delay         | C <sub>L</sub> =10pF to GND<br>Figure 5                | DOn+, DOn-, DEN                     |                        | 6.2                    | 12                   | ns    |

| t <sub>ZLD</sub>  | DO ± Tri-state to LOW<br>Delay          |                                                        |                                     |                        | 5.8                    | 12                   | ns    |

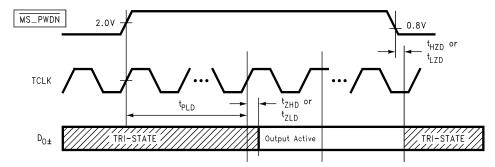

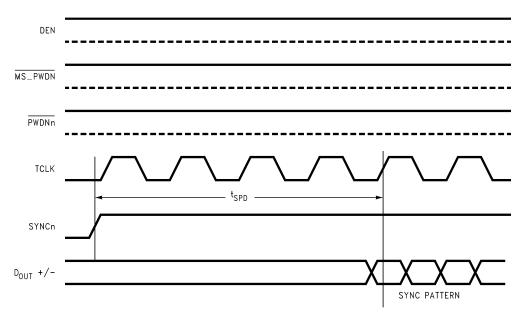

| t <sub>SPD</sub>  | SYNC Pattern Delay,<br>Figure 9         | $R_L = 100\Omega$                                      | TCLK, SYNCn,                        | 4*t <sub>TCP</sub>     |                        | 5*t <sub>TCP</sub>   | ns    |

| t <sub>PLD</sub>  | Serializer PLL Lock<br>Time, Figure 6   | C <sub>L</sub> =10pF to GND                            | DOn+, DOn-,<br>MS_PWDN              | 510*t <sub>TCP</sub>   |                        | 513*t <sub>TCP</sub> | ns    |

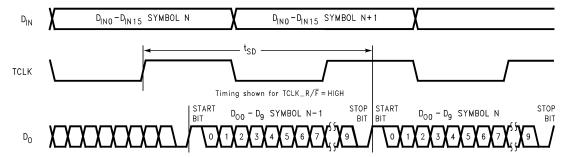

| t <sub>SD</sub>   | Serializer Delay                        | $R_L = 100\Omega$<br>$C_L=10$ pF to GND<br>Figure 8    | DINn(0-9), TCLK,<br>DOn+, DOn-      | t <sub>TCP</sub> + 1.0 | t <sub>TCP</sub> + 3.5 | t <sub>TCP</sub> + 5 | ns    |

| $t_{ICR}$         | Individual Channel<br>Power up Time     | $R_{L} = 100\Omega$ ,                                  | TCLK, DOn+, DOn-,<br>PWDNn Figure 7 | 60*t <sub>TCP</sub>    | 63*t <sub>TCP</sub>    | 70*t <sub>TCP</sub>  | ns    |

| t <sub>MCR</sub>  | Master Power up Time                    | C <sub>L</sub> =10pF to GND                            | TCLK, DOn+, DOn-, MS_PWDN Figure 6  | 510*t <sub>TCP</sub>   |                        | 513*t <sub>TCP</sub> | ns    |

| t <sub>STE</sub>  | @Speed Test Enable<br>Time              | $R_L = 100\Omega$                                      | BIST_ACT,                           |                        | 10*t <sub>TCP</sub>    |                      | ns    |

| t <sub>STD</sub>  | @Speed Test Disable<br>Time             | $R_L = 100\Omega$                                      | BIST_SEL (0:3),<br>TCLK, DOn+, DOn- |                        | 7*t <sub>TCP</sub>     |                      | ns    |

| toursu            | Channel to Channel                      | $R_L = 100\Omega$ ,                                    | 18 MHz                              |                        | 130                    |                      | ps    |

| t <sub>SKEW</sub> | Skew                                    | C <sub>L</sub> =10pF to GND                            | 66 MHz                              |                        | 80                     |                      | ps    |

Submit Documentation Feedback

Copyright © 2003-2013, Texas Instruments Incorporated

Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground except VOD, and  $\Delta\dot{V}$ OD which are differential voltages.

<sup>(1)</sup> Typical values are given for V<sub>CC</sub> = 3.3V and T<sub>A</sub> = +25°C.

(2) Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground except VOD, and  $\Delta$ VOD which are differential voltages.

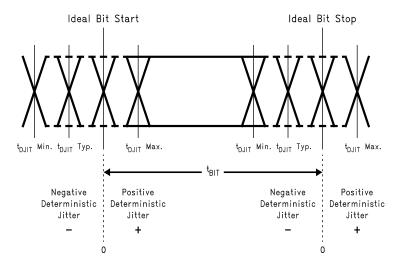

$t_{LLHT}$ ,  $t_{LHLT}$ ,  $t_{DJIT}$  and  $t_{RJIT}$  specifications are Ensured by Design using statistical analysis.

# **Serializer Switching Characteristics (continued)**

Over recommended operating supply and temperature ranges unless otherwise specified. (1)(2)

|                   |                                    |                                                                                            | •         |      |             |     |          |

|-------------------|------------------------------------|--------------------------------------------------------------------------------------------|-----------|------|-------------|-----|----------|

| Symbol            | Parameter                          | Conditions                                                                                 | Pin/Freq. | Min  | Тур         | Max | Units    |

|                   |                                    | $\begin{array}{c} R_L = 100\Omega, \\ R_{L} = 10pF \text{ to} \\ GND^{(3)(4)} \end{array}$ |           |      | 39          | 45  | ps (rms) |

| t <sub>RJIT</sub> | t <sub>RJIT</sub> Random Jitter    |                                                                                            |           |      | 18          | 21  | ps (rms) |

|                   | Deterministic Jitter,<br>Figure 10 | $R_L = 100\Omega$ ,                                                                        | 18MHz     | -225 | 20          | 257 | ps (p-p) |

| t <sub>DJIT</sub> |                                    | C <sub>L</sub> =10pF to<br>GND <sup>(3)(5)</sup>                                           | 66MHz     | -150 | <b>-</b> 55 | 68  | ps (p-p) |

<sup>(4)</sup> t<sub>RJIT</sub> specification is the rms jitter measurement of the serializer output when the device is transmitting SYNC pattern.

# **SCAN Circuitry Timing Requirements**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol           | Parameter                      | Conditions                                   | Min  | Тур | Max | Units |

|------------------|--------------------------------|----------------------------------------------|------|-----|-----|-------|

| f <sub>MAX</sub> | Maximum TCK Clock<br>Frequency | $R_L = 500\Omega$ ,<br>$C_L = 35 \text{ pF}$ | 18   |     |     | MHz   |

| t <sub>S</sub>   | TDI to TCK, H or L             |                                              | 2.0  |     |     | ns    |

| t <sub>H</sub>   | TDI to TCK, H or L             |                                              | 1.0  |     |     | ns    |

| t <sub>S</sub>   | TMS to TCK, H or L             |                                              | 2.0  |     |     | ns    |

| t <sub>H</sub>   | TMS to TCK, H or L             |                                              | 1.0  |     |     | ns    |

| t <sub>W</sub>   | TCK Pulse Width, H or L        |                                              | 10.0 |     |     | ns    |

| t <sub>W</sub>   | TRST Pulse Width, L            |                                              | 2.5  |     |     | ns    |

| t <sub>REC</sub> | Recovery Time, TRST to TCK     |                                              | 2.5  |     |     | ns    |

## **AC Timing Diagrams and Test Circuits**

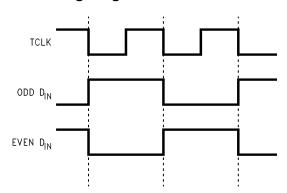

Figure 1. 'Worst Case Icc Test Pattern

Figure 2. Serializer Bus LVDS Output Load and Transition Times

<sup>(5)</sup> t<sub>DJIT</sub> specification is measured with the serializer output transmitting checkerboard patterns. It is a measurement of the center distribution of 0V (differential) crossing in comparsion with the ideal bit position. See Figure 10.

Figure 3. Serializer Input Clock Transition Time

Figure 4. Serializer Setup/Hold Times

Figure 5. Serializer Input Clock Transition Time Tri-state Test Circuit and Timing

Figure 6. Serializer PLL lock Time and MS\_PWDN Tri-state Delays

Figure 7. Individual Channel Power up Time,  $t_{\text{ICR}}$

Figure 8. Serializer Delay

Figure 9. SYNC Timing Delays

Figure 10. Deterministic Jitter and Ideal Bit Position

### **Functional Description**

The SCAN928028 combines eight 10:1 serializers into a single chip. Each of the eight serializers accepts 10 or less data bits. The serializers then multiplex the data into a serial stream with embedded clock bits and route to the LVDS output. The LVDS output is a 5 mA current loop driver. It provides enough drive for point-to-point and lightly loaded multidrop applications. The serialized data stream is compatible with the DS92LV1210, DS92LV1212A, DS92LV1224, DS92LV1260, SCAN921224, SCAN921226, SCAN921260, and SCAN926260 10-bit deserializers from Texas Instruments.

Each of the eight channels on the SCAN928028 has their own serializer function but share a single PLL. There is a single Transmit Clock (TCLK) for all eight channels. The data on all eight 10-bit interfaces is latched into the device with the rising edge of TCLK. Each of the serialized data streams is independent of the others and includes the embedded clock information. The skew between the serializer outputs is minimal.

There is a master power-down signal (MS\_PWDN) to put the entire device into a low power consumption state. In addition, there is a power-down control signal for each of the eight channels. This allows the device to efficiently operate as one to eight 10-bit serializers.

The @SPEED TEST signal initiates the sending of a random data pattern over the LVDS links. This allows for testing the links for bit error rates at the frequency they will be carrying data. In addition, JTAG can be used to verify the device interconnects and initiate/verify the at-speed BIST.

The SCAN928028 has four operating modes. They are the Initialization, Data Transfer, Resynchronization, @SPEED TEST states. There are also two passive states: Power-down and Tri-state. In addition to the active and passive states, there are test modes for JTAG access and at-speed BIST.

The following sections describe each operating mode, passive state, and the test modes.

#### INITIALIZATION

Before the '8028 serializes and transmits data, it and the receiving deserializer device(s) must initialize the link. Initialization refers to synchronizing the Serializer's and the Deserializer's PLLs to local clocks. The local clocks should be the same frequency, or within the specified range if from different sources. After all devices synchronize to local clocks, the Deserializers synchronize to the Serializers as the second and final initialization step.

Step 1: After applying power to the serializer, the outputs are held in tri-state and the on-chip power-sequencing circuitry disables the internal circuits. When Vcc reaches VccOK (2.1V), the PLL in the serializer begins locking to the local clock (TCLK). A local on-board data source or other source provides the specified clock input to the TCLK pin.

After locking to TCLK, the serializer is now ready to send data or SYNC patterns, depending on the level of the SYNC input or a data stream at the data inputs. The SYNC pattern sent by the serializer consists of six ones and six zeros switching at the input clock rate.

Step 2: The Deserializer PLL must synchronize to the Serializer to complete the initialization. (Refer to the deserializer data sheet for operation details during this step of the Initialization State.) The Deserializer identifies the rising clock edge in a synchronization pattern or non-repetitive data pattern. Depending on the data pattern that it is being transmitted, the Deserializer will synchronize to the data stream from the Serializer after some delay. At the point where the Deserializer's PLL locks to the embedded clock, the LOCK pin goes low and valid data appears on the output.

The user's application determines control of the SYNC signal input. One recommendation is a direct feedback loop from the LOCK pin on the deserializer. The serializer stops sending SYNC patterns when the SYNC input returns to a low state.

#### **DATA TRANSFER**

After initialization, the serializer accepts data from the inputs DINn0 to DINn9. The serializer uses the rising edge of the TCLK input to latch incoming data. If the SYNCn input is high for 4 TCLK cycles, the data on DINn0-DINn9 is ignored and SYNC pulses are transferred.

The serial data stream includes a start bit and stop bit appended by the serializer, which frame the ten data bits. The start bit is always high and the stop bit is always low. The start and stop bits also function as clock bits embedded in the serial stream.

The Serializer transmits the data and clock bits (10+2 bits) at 12 times the TCLK frequency. For example, if TCLK is 40 MHz, the serial rate is 40 X 12 = 480 Mbps. Since only 10 bits are from input data, the serial 'payload' rate is 10 times the TCLK frequency. For instance, if TCLK = 40 MHz, the payload data rate is 40 X 10 = 400 Mbps. TCLK is provided by the data source and must be in the range 18 MHz to 66 MHz nominal.

The serializer outputs (DO0± – DO7±) can drive a point-to-point connection or lightly loaded multidrop connections. The outputs transmit data when the driver enable pin (DEN) is high, MS\_PWDN and PWDNn are high, and SYNCn is low. When DEN is driven low, all the serializer output pins will enter tri-state.

When any one of eight attached Deserializer channels synchronizes to the input from the Serializer, it drives its LOCK pin low and synchronously delivers valid data on the output. The Deserializer locks to the embedded clock, uses it to generate multiple internal data strobes, and <u>drives</u> the embedded clock on the RCLK pin. The RCLK is synchronous to the data on the ROUT pins. While <u>LOCK</u> is low, data on ROUT is valid. Otherwise, ROUT is invalid.

#### RESYNCHRONIZATION

Whenever one of the connected DS92LV1212, '1212A, '1224, '1226, '1260, or '6260 deserializers loses lock, it will automatically try to resynchronize to the data stream from the serializer. If the data stream is not a repetitive pattern, then the deserializer will automatically lock.

For example, if the des<u>erializer</u>'s received embedded clock edge is not detected two times in succession, the PLL loses lock and the LOCK pin is driven high. The '1212, '1212A, '1224, '1226, '1260, or '6260 deserializers will automatically begin searching for the embedded clock edge. If it is a random data pattern, the deserializer will lock to that stream. If the data pattern is repetitive, the deserializer's PLL will not lock in order to prevent the deserializer from locking to the data pattern rather than the clock. We refer to such patterns as repetitive-multiple-transition, RMT.

Therefore, if the data stream is not random data or the deserializer is the DS92LV1210, there needs to be a feedback path from the deserializer to the serializer. This feedback path can be as simple as connecting the deserializer's LOCK pin to the serializer's SYNC pin. This will automatically signal the serializers to send SYNC patterns whenever the deserializer loses lock.

The user has the choice of allowing the deserializer to resynchronize to the data stream, or to force synchronization by pulsing the Serializer SYNC pin. This scheme is left up to the user discretion.

#### **POWER-DOWN**

The Power-down state is a low power sleep mode that the Serializer and Deserializer typically occupy while waiting for initialization, or to reduce power when there are no pending data transfers. The SCAN928028 serializers enter Power-down when MS\_PWDN is driven low. In Power-down, the PLL stops and the outputs go into tri-state. To exit Power-down, the system drives MS\_PWDN high.

Each of the serializers in the '8028 also has an individual power down, PWDNn control pin. This control enables the deactivation of individual serializers while allowing others to operate normally. The benefit is that spare serializers can be allocated for backup operation, but not consuming power until employed for data transfers.

The Individual Power Down will NOT cause the PLL of the device to lose lock, but it will cause the specific serializer channel to go into a low power sleep mode and its output go into tri-state. Thus, the device will NOT go through the Initialization state when individual channels exit the Individual Power Down state, and the output of the specific channel will become available after a short delay, see Figure 7 and spec tice.

### **TRI-STATE**

When the system drives DEN pin low, the serializer outputs enter tri-state. This will tri-state the output pins (DO0± to DO7±). When the system drives DEN high, the serializers will return to the previous state as long as all other control pins remain static (PWDNn, TCLK, SYNCn, and DINn[0:9]).

#### **TEST FEATURES**

Since the high-speed LVDS serial data transmission line quality is essential to the chipset operation, a means of checking this signal integrity is built into the SCAN928028 serializer. Each Serializer channel has the ability to transfer an internally generated PRBS data pattern. This pattern traverses the transmission line to the deserializer. Specific deserializers (SCAN921224 for example) have the complement PRBS pattern verification circuit. The deserializer checks the data pattern for bit errors and reports any errors on the test verification pins on the deserializer.

The @SPEED feature uses 5 signal pins. The BIST\_SEL[0:3] and BIST\_ACT pins together determine the functions of the BIST mode. The BIST\_ACT signal activates the test feature. The BIST\_SEL[0:3] selects 1 of 8 channels as the output for the BIST pattern. All channels perform BIST when BIST\_ACT = H and BIST\_SEL<0:3>=08H.

#### **JTAG TEST FEATURES**

In addition to using IEEE 1149.1 test access to the digital TTL pins, the SCAN928028 has two instructions to test the LVDS interconnects. The first instruction is EXTEST. This is implemented at LVDS levels and is only intended as a go no-go test (e.g. missing cables). The second method is the RUNBIST instruction. It is an "atsystem-speed" interconnect test. It is executed in approximately 33mS with a maximum system clock speed of 66MHz. There are two bits in the RX BIST data register for notification of PASS/FAIL and TEST\_COMPLETE. Pass indicates that the BER (Bit-Error-Rate) is better than 10<sup>-7</sup>.

An important detail is that once both devices have the RUNBIST instruction loaded into their respective instruction registers, both devices must move into the RTI (*Run-Test-Idle*) state within 4K system clocks (At a TCLK of 66Mhz and TCK of 1MHz this allows for 66 TCK cycles). This is not a concern when both devices are on the same scan chain or LSP, however, it can be a problem with some multi-drop devices. This test mode has been simulated and verified using Tl's SCANSTA111.

If the user is unable to meet the constraint of moving both taps into RTI within 4K system clocks, the receiver must be moved into the RTI state first. The receiver can then stay in RTI indefinitely until the transmitter is moved into RTI and the BIST pattern begins. This is true for either SCAN initiated BIST or pin initiated BIST\_ALONE or any combination of the two.

#### Truth Table (BIST mode)

No BIST function performed when BIST\_SEL (0:3) are set from 9H to FH even when BIST\_ACT is set at HIGH. See (1)(2)

|          |              | ()           |              |              |                         |

|----------|--------------|--------------|--------------|--------------|-------------------------|

| BIST_ACT | BIST_SEL <3> | BIST_SEL <2> | BIST_SEL <1> | BIST_SEL <0> | MODE                    |

| Н        | L            | L            | L            | L            | BIST on channel 0       |

| Н        | L            | L            | L            | Н            | BIST on channel 1       |

| Н        | L            | L            | Н            | L            | BIST on channel 2       |

| Н        | L            | L            | Н            | Н            | BIST on channel 3       |

| Н        | L            | Н            | L            | L            | BIST on channel 4       |

| Н        | L            | Н            | L            | Н            | BIST on channel 5       |

| Н        | L            | Н            | Н            | L            | BIST on channel 6       |

| Н        | L            | Н            | Н            | Н            | BIST on channel 7       |

| Н        | П            | L            | L            | L            | BIST on ALL<br>CHANNELS |

| L        | X            | X            | Х            | X            | NO BIST                 |

| L        | Н            | Н            | Н            | Н            | Default - NO BIST       |

<sup>(1)</sup> BIST\_SEL have a weak internal pull-up. In a noisy operating environment, it is recommended that an external pull up be used to ensure that BIST\_SEL is in the high state.

Product Folder Links: SCAN928028

<sup>(2)</sup> No BIST function performed when BIST\_SEL (0:3) are set from 9H to FH even when BIST\_ACT is set at HIGH.

# **Functional Block Diagram**

Figure 11. SCAN928028 Functional Block Diagram

#### APPLICATION INFORMATION

### **USING THE SCAN928028**

The SCAN928028 is an easy to use serializer that combines eight 10:1 serializers into a single chip with a maximum payload of 5.28Gbps. Each of the eight serializers accepts 10 or less data bits. The serializers then multiplex the data into a serial data stream with embedded clock bits and route to the LVDS output at up to 660Mbps per channels. The LVDS output is a 5 ma current loop driver that can be used for point-to-point and lightly loaded multidrop applications. Each of the eight channels has their own serializer function but share a single Transmit Clock (TCLK) with a single PLL for the entire chip. The data on all eight channels is latched into the device with the rising edge of TCLK and the data stream is compatible with the DS92LV1210, DS92LV1212A, DS92LV1224, DS92LV1260, SCAN921224, SCAN921226, SCAN921260, and SCAN926260 deserializers from Texas Instruments.

If using less than 10 bits of data, it is recommended to tie off adjacent bits to the embedded clock bits to prevent causing a RMT in the data payload. For example, if only using 8 bits, tie D0 High and D9 Low.

### **POWER CONSIDERATIONS**

All CMOS design of the Serializer and Deserializer makes them inherently low power devices. Additionally, the constant current source nature of the LVDS outputs minimize the slope of the speed vs.  $I_{CC}$  curve of CMOS designs.

### PCB LAYOUT AND POWER SYSTEM CONSIDERATIONS

Circuit board layout and stack-up for the BLVDS devices should be designed to provide low-noise power feed to the device. Good layout practice will also separate high-frequency or high-level inputs and outputs to minimize unwanted stray noise pickup, feedback and interference. Power system performance may be greatly improved by using thin dielectrics (2 to 4 mils) for power / ground sandwiches. This arrangement provides plane capacitance for the PCB power system with low-inductance parasitic, especially proven effective at high frequencies above approximately 50MHz, and makes the value and placement of external bypass capacitors less critical. External bypass capacitors should include both RF ceramic and tantalum electrolytic types. RF capacitors may use values in the range of 0.01 uF to 0.1 uF. Tantalum capacitors may be in the 2.2 uF to 10 uF range. Voltage rating of the tantalum capacitors should be at least 5X the power supply voltage being used.

It is a recommended practice to use two vias at each power pin as well as at all RF bypass capacitor terminals. Dual vias reduce the interconnect inductance by up to half, thereby reducing interconnect inductance and extending the effective frequency range of the bypass components. Locate RF capacitors as close as possible to the supply pins, and use wide low impedance traces (not 50 Ohm traces). Surface mount capacitors are recommended due to their smaller parasitics. When using multiple capacitors per supply pin, locate the smaller value closer to the pin. A large bulk capacitor is recommend at the point of power entry. This is typically in the 50uF to 100uF range and will smooth low frequency switching noise. It is recommended to connect power and ground pins straight to the power and ground plane, with the bypass capacitors connected to the plane with via on both ends of the capacitor. Connecting a power or ground pin to an external bypass capacitor will increase the inductance of the path.

A small body size X7R chip capacitor, such as 0603, is recommended for external bypass. Its small body size reduces the parasitic inductance of the capacitor. User must pay attention to the resonance frequency of these external bypass capacitors, usually in the range of 20-30MHz range. To provide effective bypassing, very often, multiple capacitors are used to achieve low impedance between the supply rails over the frequency of interest. At high frequency, it is also a common practice to use two via from power and ground pins to the planes, reducing the impedance at high frequency.

Some devices provide separate power and ground pins for different portions of the circuit. This is done to isolate switching noise effects between different sections of the circuit. Separate planes on the PCB are typically not required. Pin Description tables typically provide guidance on which circuit blocks are connected to which power pin pairs. In some cases, an external filter many be used to provide clean power to sensitive circuits such as PLLs.

Use at least a four layer board with a power and ground plane. Locate CMOS (TTL) swings away from the LVDS lines to prevent coupling from the CMOS lines to the LVDS lines. Closely-coupled differential lines of 100 Ohms are typically recommended for LVDS interconnect. The closely-coupled lines help to ensure that coupled noise will appear as common-mode and thus is rejected by the receivers. Also the tight coupled lines will radiate less.

Copyright © 2003–2013, Texas Instruments Incorporated

#### TRANSMISSION MEDIA

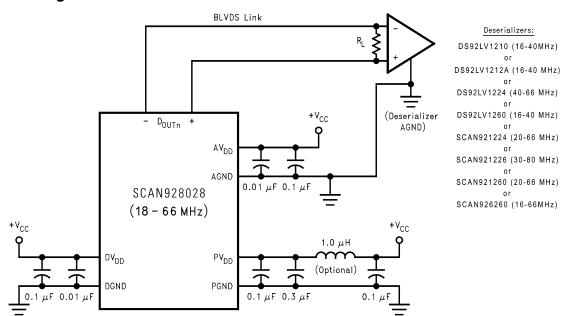

The SCAN928028 Serializers can be used in point-to-point configuration of a backplane across PCB traces or through cable interconnect. In point-to-point configurations the transmission media needs only to be terminated at the receiver end. The SCAN928028 may also be used with double terminations for a total load or 50 Ohms for use in certain limited multidrop applications. Termination impedances lower than 50 Ohms is not recommended.

#### **TERMINATION**

Termination of the LVDS interconnect is required. For point-to-point applications termination should be located at the load end. Nominal value is 100 Ohms to match the line's differential impedance. Place the resistor as close to the receiver inputs as possible to minimize the resulting stub between the termination resistor and receiver.

Additional general guidance can be found in the LVDS Owner's Manual - available in PDF format from the TI web site at: http://www.ti.com/ww/en/analog/interface/lvds.shtml

#### SCAN928028 BLVDS SERIALIZER BYPASS RECOMMENDATIONS

General device specific guidance is given below. Exact guidance can not be given as it is dictated by other board level /system level criteria. This includes the density of the board, power rails, power supply, and other integrated circuit power supply needs.

For a typical application circuit, please see Figure 12.

#### DVDD = DIGITAL SECTION POWER SUPPLY

These pins supply the digital portion of the device. A 0.1uF capacitor is sufficient for these pins.

#### PVDD = PLL SECTION POWER SUPPLY

The PVDD pin supplies the PLL circuit. The PLL(s) require clean power for the minimization of Jitter. A supply noise frequency in the 300kHZ to 1MHz range can cause increased output jitter. Certain power supplies may have switching frequencies or high harmonic content in this range. If this is the case, filtering of this noise spectrum may be required. A notch filter response is best to provide a stable VDD, suppression of the noise band, and good high-frequency response (clock fundamental). This may be accomplished with a pie filter (CRC or CLC). The pie filter should be located close to the PVDD power pin. Separate power planes for the PVDD pins is typically not required.

### AVDD = LVDS SECTION POWER SUPPLY

The AVDD pin supplies the LVDS portion of the circuit. The SCAN928028 has nine AVDD pins. Due to the nature of the design, current draw is not excessive on these pins. A 0.1uF capacitor is sufficient for these pins. If space is available a 0.01uF may be used in parallel with the 0.1uF capacitor for additional high frequency filtering.

### **GROUNDS**

The AGND pin should be connected to the signal common in the cable for the return path of any common-mode current. Most of the LVDS current will be odd-mode and return within the interconnect pair. A small amount of current may be even-mode due to coupled noise, and driver imbalances. This current should return via a low impedance known path.

A solid ground plane is recommended for DVDD, PVDD or AVDD. Using a split plane may have a potential problem of ground loops, or difference in ground potential at various ground pins of the device.

Product Folder Links: SCAN928028

# **Application Diagram**

Figure 12. Typical Application Circuit

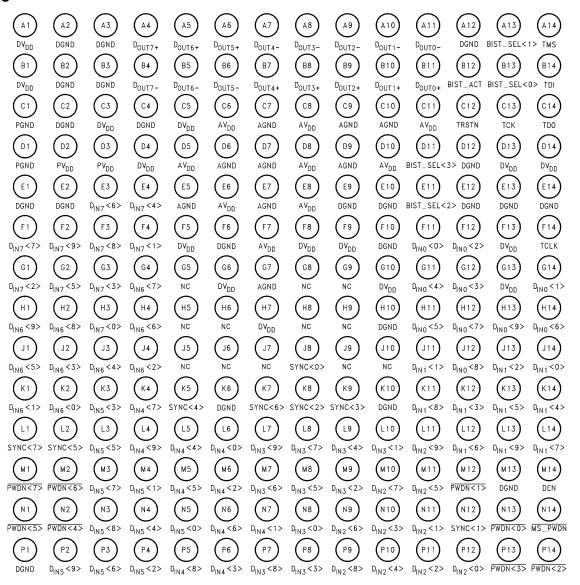

### Pin Diagram

Figure 13. Top View of SCAN928028 (196-pin NFBGA)

# **Pin Descriptions**

| Pin Descriptions                                                                                                                                                                                                                                                                                                                                           |                   |                    |                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Number                                                                                                                                                                                                                                                                                                                                                 | Name              | Туре               | Description                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| C7, C9, C10, D6, D7, D9, E5, E7, G7                                                                                                                                                                                                                                                                                                                        | AGND              |                    | Analog ground.                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| C6, C8, C11, D5, D8, D10, E6,<br>E8, F7                                                                                                                                                                                                                                                                                                                    | AVDD              |                    | Analog power supply.                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| B12                                                                                                                                                                                                                                                                                                                                                        | BIST_ACT          | 3.3 V<br>CMOS<br>I | BIST Active. Control pin for BIST mode enable.When BIST_ACT = H and BIST_SEL (0:3) = 0H to 8H, device will go to BIST mode accordingly. See Truth Table (BIST mode) Default at Low                                                                                                                                                                       |  |  |  |  |

| A13, B13, D11, E11                                                                                                                                                                                                                                                                                                                                         | BIST_SEL<br>(0:3) | 3.3 V<br>CMOS<br>I | BIST select. Control pins for which serializer is set for BIST mode. See Truth Table (BIST mode) (1)                                                                                                                                                                                                                                                     |  |  |  |  |

| M14                                                                                                                                                                                                                                                                                                                                                        | DEN               | 3.3 V<br>CMOS<br>I | Serializer output data enable. Enable data output DOUTn (0:9). n = serializer number. When driven low, puts the Bus LVDS outputs in tristate. Default at Low.                                                                                                                                                                                            |  |  |  |  |

| A2, A3, A12, B2, B3, C2, C4,<br>D12, E1, E2, E9, E10, E12, E13,<br>E14, F6, F10, H10, K6, K10,<br>M13, P1                                                                                                                                                                                                                                                  | DGND              |                    | Digital Ground.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| E3, E4, F1, F2, F3, F4, F11, F12, G1, G2, G3, G4, G11, G12, G14, H1, H2, H3, H4, H11, H12, H13, H14, J1, J2, J3, J4, J11, J12, J13, J14, K1, K2, K3, K4, K11, K12, K13, K14, L3, L4, L5, L6, L7, L8, L9, L10, L11, L12, L13, L14, M3, M4, M5, M6, M7, M8, M9, M10, M11, N3, N4, N5, N6, N7, N8, N9, N10, N11, P2, P3, P4, P5, P6, P7, P8, P9, P10 P11, P12 | DINnx             | 3.3 V<br>CMOS<br>I | Data input. Inputs for the ten bit serializers. n = serializer number, x = bit number. Default at Low.                                                                                                                                                                                                                                                   |  |  |  |  |

| B11-A11, B10-A10, B9-A9, B8-A8, B7-A7, A6-B6, A5-B5, A4-B4                                                                                                                                                                                                                                                                                                 | Doutn±            | Bus LVDS<br>O      | Bus LVDS differential outputs. n = serializer number.                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| A1, B1, C3, C5, D4, D13, D14,<br>F5, F8, F9, F13, G6, G10, G13,<br>H7,                                                                                                                                                                                                                                                                                     | DVDD              |                    | Digital power supply.                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| N14                                                                                                                                                                                                                                                                                                                                                        | MS_PWDN           | 3.3 V<br>CMOS      | Master Powerdown. MS_PWDN driven low shuts down the PLL and tri-state all outputs, putting the device into a low power 'sleep' mode. Default at Low.                                                                                                                                                                                                     |  |  |  |  |

| G5, G8, G9, H5, H6, H8, H9, J5,<br>J6, J7, J9, J10                                                                                                                                                                                                                                                                                                         | NC (1:12)         |                    | No connect.                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| C1, D1                                                                                                                                                                                                                                                                                                                                                     | PGND              |                    | PLL ground.                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| D2, D3                                                                                                                                                                                                                                                                                                                                                     | PVDD              |                    | PLL power supply.                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| N1, N2, N13, M1, M2, M12, P13,<br>P14                                                                                                                                                                                                                                                                                                                      | PWDN (0:7)        | 3.3 V<br>CMOS      | Individual Powerdown. PWDN (0:7) driven low puts individual serializers into tri-state, low power 'sleep' mode. Default at Low.                                                                                                                                                                                                                          |  |  |  |  |

| J8, K5, K7, K8, K9, L1, L2, N12                                                                                                                                                                                                                                                                                                                            | SYNC (0:7)        | 3.3 V<br>CMOS<br>I | SYNC pattern enable. When driven high for a mininum of 4 cycles, SYNC patterns will be transmitted on the Bus LVDS serial output. The SYNC pattern sent by the serializer consists of six ones and six zeros switching at the input clock rate. SYNC pattern continues to be sent if SYNC continues at high. Default at Low. See Functional Description. |  |  |  |  |

| C13                                                                                                                                                                                                                                                                                                                                                        | TCK               |                    | Test Clock Input to support IEEE 1149.1                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| B14                                                                                                                                                                                                                                                                                                                                                        | TDI               |                    | Test Data Input to support IEEE 1149.1. There is an internal pullup resistor that defaults this input to high per IEEE 1149.1.                                                                                                                                                                                                                           |  |  |  |  |

| C14                                                                                                                                                                                                                                                                                                                                                        | TDO               |                    | Test Data Output to support IEEE 1149.1                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| A14                                                                                                                                                                                                                                                                                                                                                        | TMS               |                    | Test Mode Select Input to support IEEE 1149.1. There is an internal pullup resistor that defaults this input to high per IEEE 1149.1.                                                                                                                                                                                                                    |  |  |  |  |

| C12                                                                                                                                                                                                                                                                                                                                                        | TRSTN             |                    | Test Reset Input to support IEEE 1149.1. There is an internal pullup resistor that defaults this input to high per IEEE 1149.1.                                                                                                                                                                                                                          |  |  |  |  |

<sup>(1)</sup> BIST\_SEL have a weak internal pull-up. In a noisy operating environment, it is recommended that an external pull up be used to ensure that BIST\_SEL is in the high state.

# SNLS163F -AUGUST 2003-REVISED APRIL 2013

# Pin Descriptions (continued)

| Pin Number | Name | Туре               | Description                                                       |

|------------|------|--------------------|-------------------------------------------------------------------|

| F14        | TCLK | 3.3 V<br>CMOS<br>I | Transmit Clock. Input for 18 MHz - 66 MHz (nominal) system clock. |

# **REVISION HISTORY**

| Cł | hanges from Revision E (April 2013) to Revision F  | Pag | e |

|----|----------------------------------------------------|-----|---|

| •  | Changed layout of National Data Sheet to TI format | 1   | 8 |

www.ti.com 11-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status (1) | Material type | Package   Pins    | Package qty   Carrier      | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6)        |

|-----------------------|------------|---------------|-------------------|----------------------------|-----------------|-------------------------------|----------------------------|--------------|-------------------------|

| SCAN928028TUF/NOPB    | Active     | Production    | NFBGA (NZH)   196 | 119   JEDEC<br>TRAY (10+1) | Yes             | SNAGCU                        | Level-3-260C-168 HR        | -40 to 85    | SCAN928028T<br>UF<br>>B |

| SCAN928028TUF/NOPB.A  | Active     | Production    | NFBGA (NZH)   196 | 119   JEDEC<br>TRAY (10+1) | Yes             | SNAGCU                        | Level-3-260C-168 HR        | -40 to 85    | SCAN928028T<br>UF<br>>B |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

- (3) RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

- (4) Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

- (5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

- (6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

www.ti.com 23-May-2025

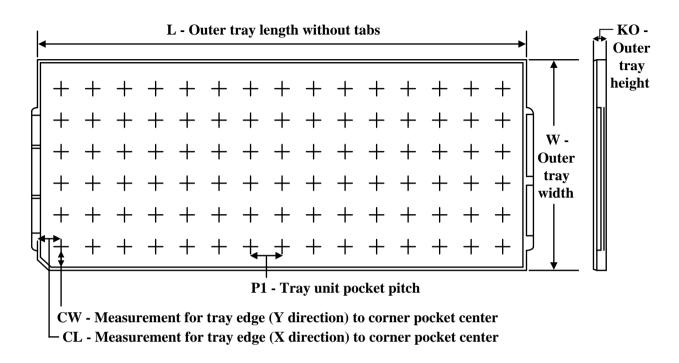

## **TRAY**

Chamfer on Tray corner indicates Pin 1 orientation of packed units.

#### \*All dimensions are nominal

| Device                   | Package<br>Name | Package<br>Type | Pins | SPQ | Unit array<br>matrix | Max<br>temperature<br>(°C) | L (mm) | W<br>(mm) | Κ0<br>(μm) | P1<br>(mm) | CL<br>(mm) | CW<br>(mm) |

|--------------------------|-----------------|-----------------|------|-----|----------------------|----------------------------|--------|-----------|------------|------------|------------|------------|

| SCAN928028TUF/NOPB       | NZH             | NFBGA           | 196  | 119 | 7 X 17               | 150                        | 322.6  | 135.9     | 7620       | 18.1       | 12.7       | 12.9       |

| SCAN928028TUF/<br>NOPB.A | NZH             | NFBGA           | 196  | 119 | 7 X 17               | 150                        | 322.6  | 135.9     | 7620       | 18.1       | 12.7       | 12.9       |

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025