## Technical White Paper

# Operational Amplifier Stability Theory and Compensation Methods

Art Kay, Collin Wells

#### **ABSTRACT**

Operational Amplifiers (op amps) can become unstable when driving a capacitive load or from capacitance on the inverting input. This instability in op amps can show up as overshoot and ringing in response to an input, load transients, and—in the worst cases—an oscillation that is continuous and independent of the input signal. For example, an unstable amplifier can oscillate even when the input signal is a DC voltage. This document explains the theory behind what causes instability and provides options to eliminate this problem.

## **Table of Contents**

| 1.1 Simple Analogy Explaining Instability 1.2 Circuits With Possible Stability Issues. 1.3 Simple Stability Correction Based on Datasheet Plots. 1.4 Introducing Lab Tools and Measurements.  2 Stability Theory for Operational Amplifiers. 2.1 Poles and Zeros. 2.2 Operational Amplifier Model Requirements for Stability Verification. 2.3 Stability Definitions Based on Control Loop Model. 2.4 Graphing Loop-Gain Based on A <sub>OL</sub> and 1/β. 2.5 Rate of Closure Stability Test. 2.6 Indirect (Non-Invasive) Stability Tests. 3 Simulating Open-Loop Stability Tests. 3.1 Breaking the Loop the Wrong Way. 3.2 Breaking the Loop the Wrong Way. 3.3 Differential Loop Break Test. 4 Stability Correction for Capacitive Load 4.1 Isolation Resistor (R <sub>ISO</sub> ) Method. 4.2 Dual Feedback Method 4.3 Snubber Circuit for Compensating Power Amplifiers and Reference Drive. 4.4 Noise Gain for Stability Compensation for Capacitive Load. 5 Stability Corrections for Capacitance on the Inverting Node. 5.1 Input Capacitance Instability Due to Zero in 1/β. 5.2 Feedback Capacitor (C <sub>F</sub> ) Compensation for Capacitiance on the Inverting Node. 5.3 Minimum, Balanced, and Maximum Feedback Capacitance on the Inverting Node. 5.4 Transimpedance Case. 6 Complex Open-Loop and Closed-Loop Output Impedance. 6.1 Converting Open-Loop and Closed-Loop Output Impedance. 6.2 Open-Loop and Closed-Loop Model Test. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.3 Simple Stability Correction Based on Datasheet Plots. 1.4 Introducing Lab Tools and Measurements  2 Stability Theory for Operational Amplifiers 2.1 Poles and Zeros. 2.2 Operational Amplifier Model Requirements for Stability Verification. 2.3 Stability Definitions Based on Control Loop Model. 2.4 Graphing Loop-Gain Based on A <sub>OL</sub> and 1/β. 2.5 Rate of Closure Stability Test. 2.6 Indirect (Non-Invasive) Stability Tests. 3 Simulating Open-Loop Stability Tests. 3.1 Breaking the Loop the Wrong Way. 3.2 Breaking the Loop With LC Test Circuit. 3.3 Differential Loop Break Test. 4 Stability Correction for Capacitive Load 4.1 Isolation Resistor (R <sub>ISO</sub> ) Method. 4.2 Dual Feedback Method. 4.3 Snubber Circuit for Compensating Power Amplifiers and Reference Drive. 4.4 Noise Gain for Stability Compensation. 4.5 Feedback Capacitor (C <sub>F</sub> ) Compensation for Capacitive Load. 5 Stability Corrections for Capacitance on the Inverting Node. 5.1 Input Capacitance Instability Due to Zero in 1/β. 5.2 Feedback Capacitor Solves Stability Issue for Capacitance on the Inverting Node. 5.3 Minimum, Balanced, and Maximum Feedback Capacitance. 5.4 Transimpedance Case. 6 Complex Open-Loop and Closed-Loop Output Impedance. 6.1 Converting Open-Loop Output Impedance to Closed-Loop Output Impedance.                                                                                    |

| 1.4 Introducing Lab Tools and Measurements.  2 Stability Theory for Operational Amplifiers. 2.1 Poles and Zeros. 2.2 Operational Amplifier Model Requirements for Stability Verification. 2.3 Stability Definitions Based on Control Loop Model. 2.4 Graphing Loop-Gain Based on A <sub>OL</sub> and 1/β. 2.5 Rate of Closure Stability Test. 2.6 Indirect (Non-Invasive) Stability Tests. 3.1 Breaking Open-Loop Stability Tests. 3.1 Breaking the Loop the Wrong Way. 3.2 Breaking the Loop With LC Test Circuit. 3.3 Differential Loop Break Test. 4 Stability Correction for Capacitive Load. 4.1 Isolation Resistor (R <sub>ISO</sub> ) Method. 4.2 Dual Feedback Method. 4.3 Snubber Circuit for Compensating Power Amplifiers and Reference Drive. 4.4 Noise Gain for Stability Compensation. 4.5 Feedback Capacitor (C <sub>F</sub> ) Compensation for Capacitive Load. 5 Stability Corrections for Capacitance on the Inverting Node. 5.1 Input Capacitance Instability Due to Zero in 1/β. 5.2 Feedback Capacitor Solves Stability Issue for Capacitance on the Inverting Node. 5.3 Minimum, Balanced, and Maximum Feedback Capacitance 5.4 Transimpedance Case. 6 Complex Open-Loop and Closed-Loop Output Impedance. 6.1 Converting Open-Loop Output Impedance to Closed-Loop Output Impedance.                                                                                                                                            |

| 2 Stability Theory for Operational Amplifiers.  2.1 Poles and Zeros.  2.2 Operational Amplifier Model Requirements for Stability Verification.  2.3 Stability Definitions Based on Control Loop Model.  2.4 Graphing Loop-Gain Based on A <sub>OL</sub> and 1/β.  2.5 Rate of Closure Stability Test.  2.6 Indirect (Non-Invasive) Stability Tests.  3 Simulating Open-Loop Stability Tests.  3.1 Breaking the Loop the Wrong Way.  3.2 Breaking the Loop With LC Test Circuit.  3.3 Differential Loop Break Test.  4 Stability Correction for Capacitive Load  4.1 Isolation Resistor (R <sub>ISO</sub> ) Method.  4.2 Dual Feedback Method.  4.3 Snubber Circuit for Compensating Power Amplifiers and Reference Drive.  4.4 Noise Gain for Stability Compensation.  4.5 Feedback Capacitor (C <sub>F</sub> ) Compensation for Capacitive Load.  5 Stability Corrections for Capacitance on the Inverting Node.  5.1 Input Capacitance Instability Due to Zero in 1/β.  5.2 Feedback Capacitor Solves Stability Issue for Capacitance on the Inverting Node.  5.3 Minimum, Balanced, and Maximum Feedback Capacitance  5.4 Transimpedance Case.  6 Complex Open-Loop and Closed-Loop Output Impedance.  6.1 Converting Open-Loop Output Impedance.                                                                                                                                                                                                   |

| 2.1 Poles and Zeros                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.2 Operational Amplifier Model Requirements for Stability Verification.  2.3 Stability Definitions Based on Control Loop Model.  2.4 Graphing Loop-Gain Based on A <sub>OL</sub> and 1/β.  2.5 Rate of Closure Stability Test.  2.6 Indirect (Non-Invasive) Stability Tests.  3 Simulating Open-Loop Stability Tests.  3.1 Breaking the Loop the Wrong Way.  3.2 Breaking the Loop With LC Test Circuit.  3.3 Differential Loop Break Test.  4 Stability Correction for Capacitive Load.  4.1 Isolation Resistor (R <sub>ISO</sub> ) Method.  4.2 Dual Feedback Method.  4.3 Snubber Circuit for Compensating Power Amplifiers and Reference Drive.  4.4 Noise Gain for Stability Compensation for Capacitive Load.  5 Stability Corrections for Capacitance on the Inverting Node.  5.1 Input Capacitance Instability Due to Zero in 1/β.  5.2 Feedback Capacitor Solves Stability Issue for Capacitance on the Inverting Node.  5.3 Minimum, Balanced, and Maximum Feedback Capacitance.  5 A Transimpedance Case.  6 Complex Open-Loop and Closed-Loop Output Impedance.  6.1 Converting Open-Loop Output Impedance.                                                                                                                                                                                                                                                                                                                               |

| 2.3 Stability Definitions Based on Control Loop Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.4 Graphing Loop-Gain Based on A <sub>OL</sub> and 1/β                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.5 Rate of Closure Stability Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.6 Indirect (Non-Invasive) Stability Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

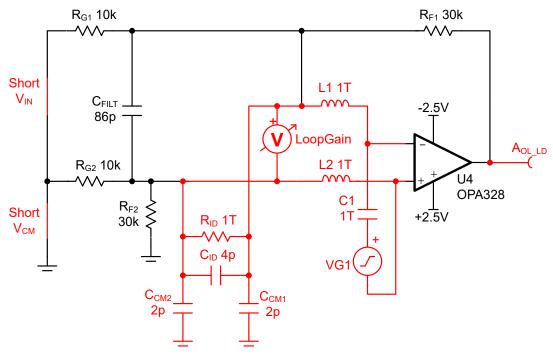

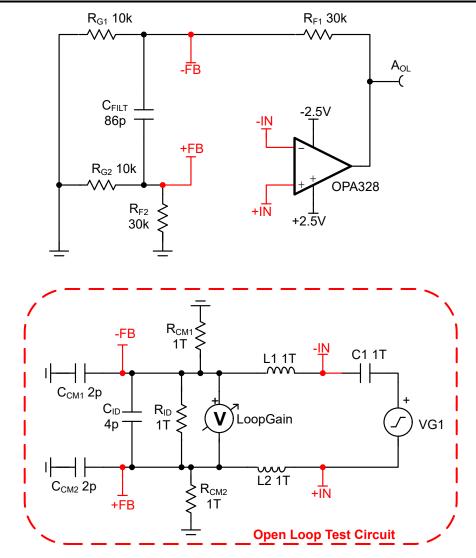

| 3 Simulating Open-Loop Stability Tests 3.1 Breaking the Loop the Wrong Way                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.1 Breaking the Loop the Wrong Way                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.2 Breaking the Loop With LC Test Circuit.  3.3 Differential Loop Break Test.  4 Stability Correction for Capacitive Load.  4.1 Isolation Resistor (R <sub>ISO</sub> ) Method.  4.2 Dual Feedback Method.  4.3 Snubber Circuit for Compensating Power Amplifiers and Reference Drive.  4.4 Noise Gain for Stability Compensation.  4.5 Feedback Capacitor (C <sub>F</sub> ) Compensation for Capacitive Load.  5 Stability Corrections for Capacitance on the Inverting Node.  5.1 Input Capacitance Instability Due to Zero in 1/β.  5.2 Feedback Capacitor Solves Stability Issue for Capacitance on the Inverting Node.  5.3 Minimum, Balanced, and Maximum Feedback Capacitance.  5.4 Transimpedance Case.  6 Complex Open-Loop and Closed-Loop Output Impedance.  6.1 Converting Open-Loop Output Impedance to Closed-Loop Output Impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

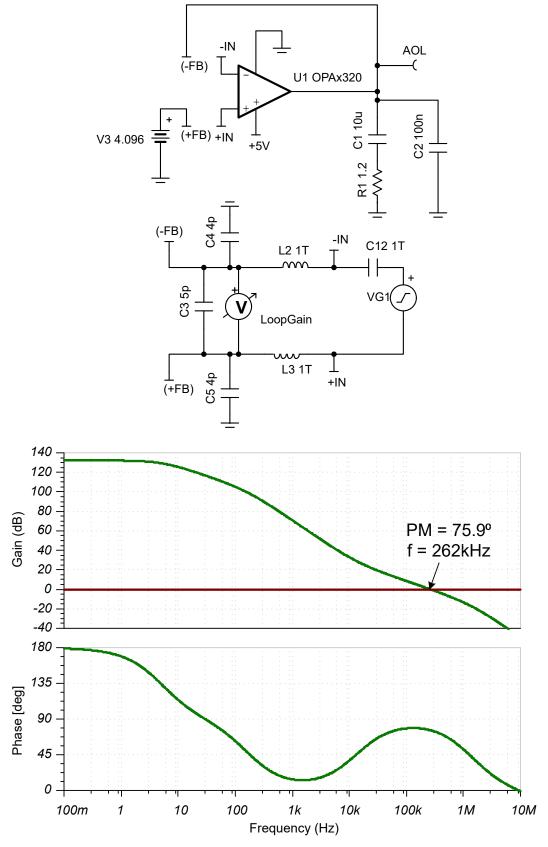

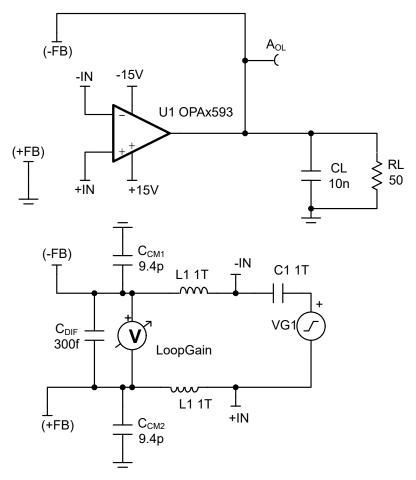

| 3.3 Differential Loop Break Test.  4 Stability Correction for Capacitive Load.  4.1 Isolation Resistor (R <sub>ISO</sub> ) Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4 Stability Correction for Capacitive Load 4.1 Isolation Resistor (R <sub>ISO</sub> ) Method. 4.2 Dual Feedback Method. 4.3 Snubber Circuit for Compensating Power Amplifiers and Reference Drive. 4.4 Noise Gain for Stability Compensation. 4.5 Feedback Capacitor (C <sub>F</sub> ) Compensation for Capacitive Load. 5 Stability Corrections for Capacitance on the Inverting Node. 5.1 Input Capacitance Instability Due to Zero in 1/β. 5.2 Feedback Capacitor Solves Stability Issue for Capacitance on the Inverting Node. 5.3 Minimum, Balanced, and Maximum Feedback Capacitance. 5.4 Transimpedance Case. 6 Complex Open-Loop and Closed-Loop Output Impedance. 6.1 Converting Open-Loop Output Impedance to Closed-Loop Output Impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

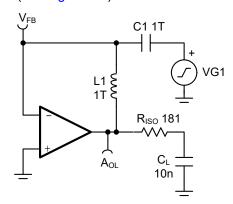

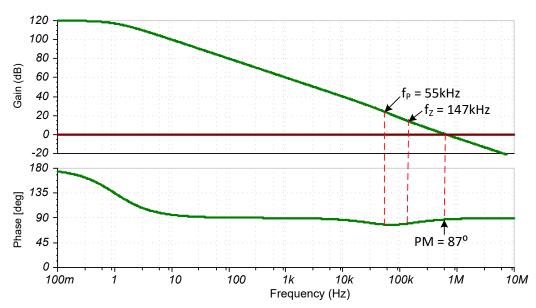

| 4.1 Isolation Resistor (R <sub>ISO</sub> ) Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.2 Dual Feedback Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

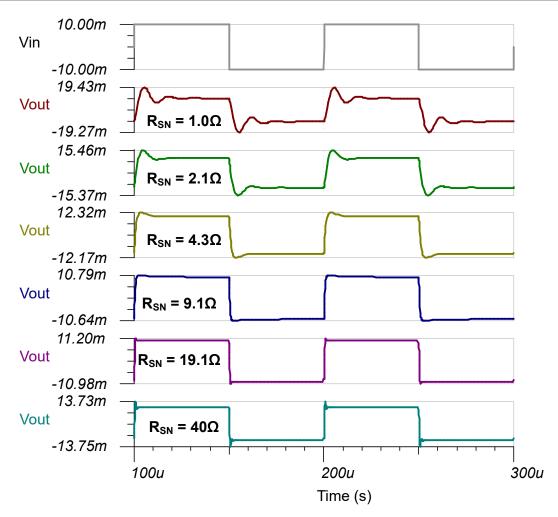

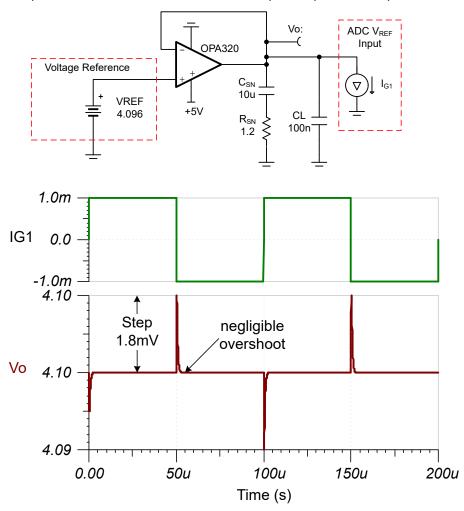

| 4.3 Snubber Circuit for Compensating Power Amplifiers and Reference Drive. 4.4 Noise Gain for Stability Compensation. 7.4.5 Feedback Capacitor (C <sub>F</sub> ) Compensation for Capacitive Load. 7.5 Stability Corrections for Capacitance on the Inverting Node. 7.5.1 Input Capacitance Instability Due to Zero in 1/β                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.4 Noise Gain for Stability Compensation 7   4.5 Feedback Capacitor (C <sub>F</sub> ) Compensation for Capacitive Load 7   5 Stability Corrections for Capacitance on the Inverting Node 7   5.1 Input Capacitance Instability Due to Zero in 1/β 7   5.2 Feedback Capacitor Solves Stability Issue for Capacitance on the Inverting Node 7   5.3 Minimum, Balanced, and Maximum Feedback Capacitance 8   5.4 Transimpedance Case 8   6 Complex Open-Loop and Closed-Loop Output Impedance 9   6.1 Converting Open-Loop Output Impedance to Closed-Loop Output Impedance 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

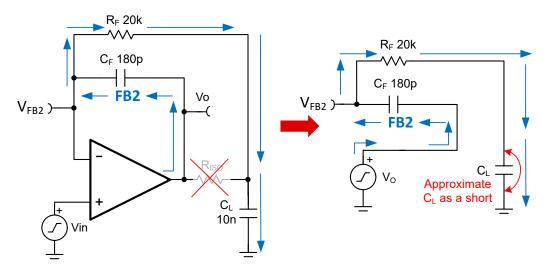

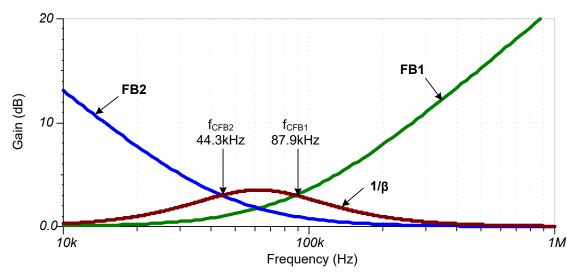

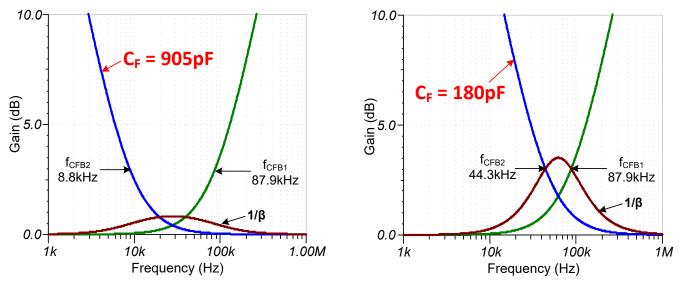

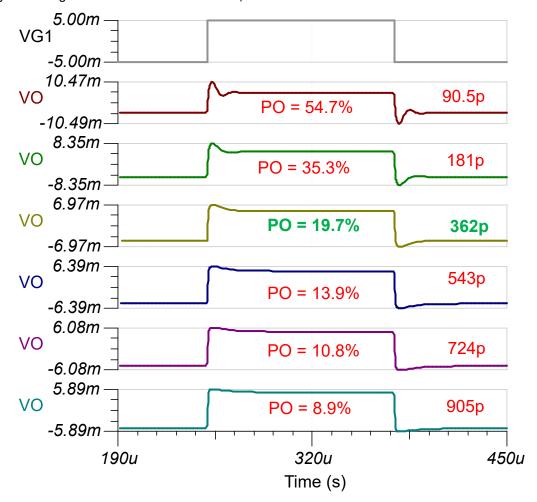

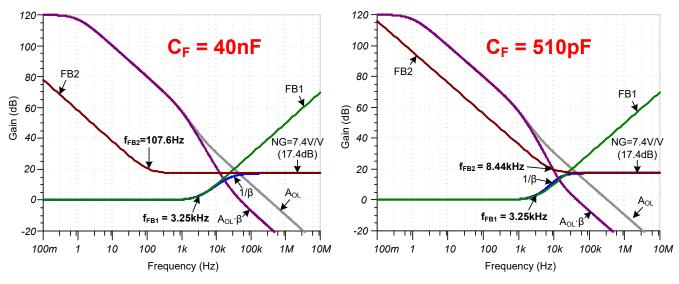

| 4.5 Feedback Capacitor (C <sub>F</sub> ) Compensation for Capacitive Load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5 Stability Corrections for Capacitance on the Inverting Node       7         5.1 Input Capacitance Instability Due to Zero in 1/β                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.1 Input Capacitance Instability Due to Zero in 1/β                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

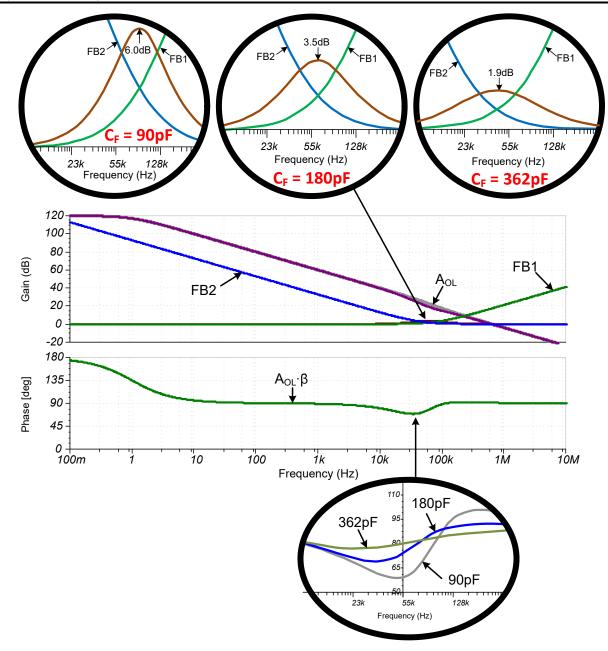

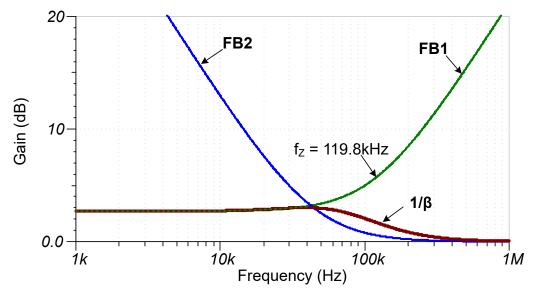

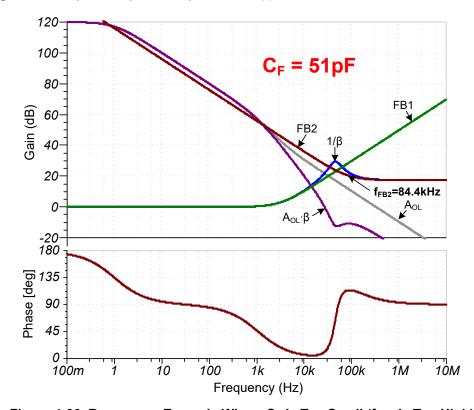

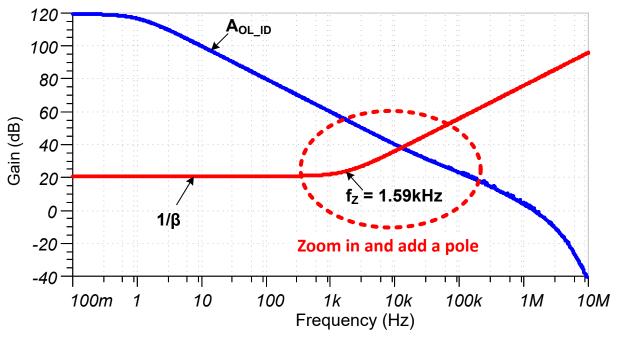

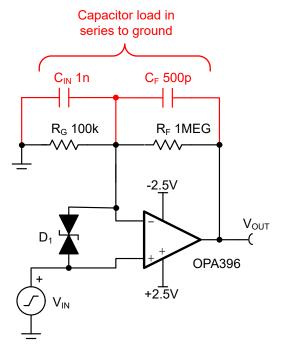

| 5.2 Feedback Capacitor Solves Stability Issue for Capacitance on the Inverting Node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

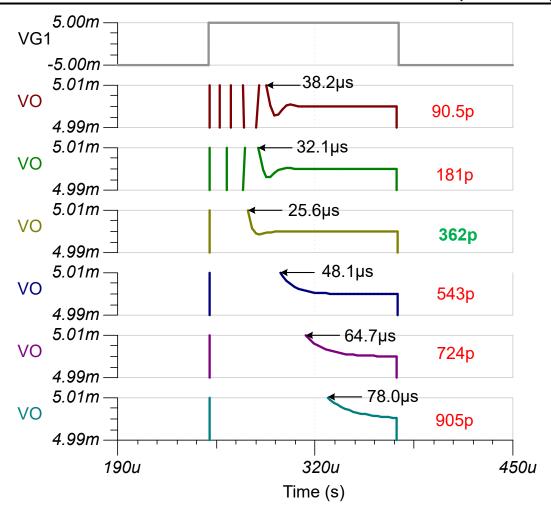

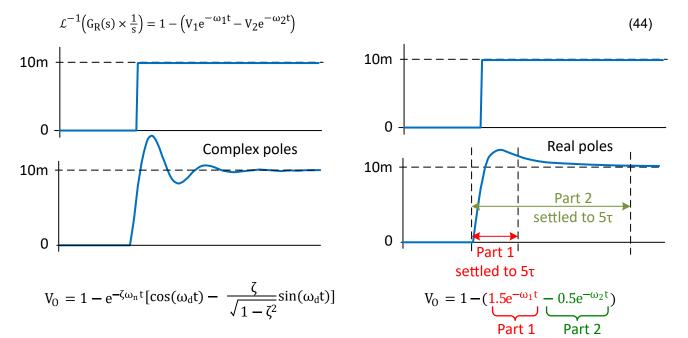

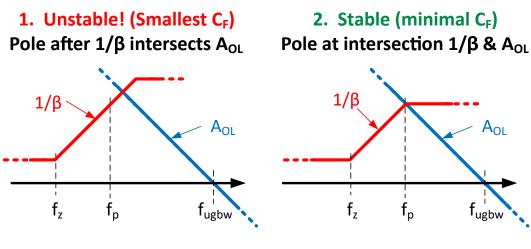

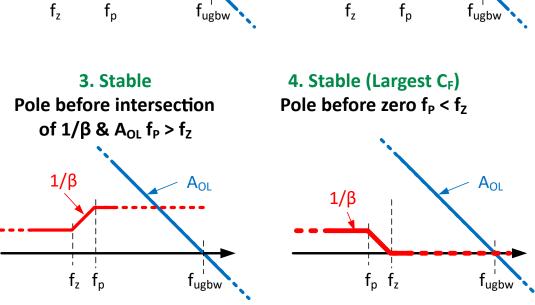

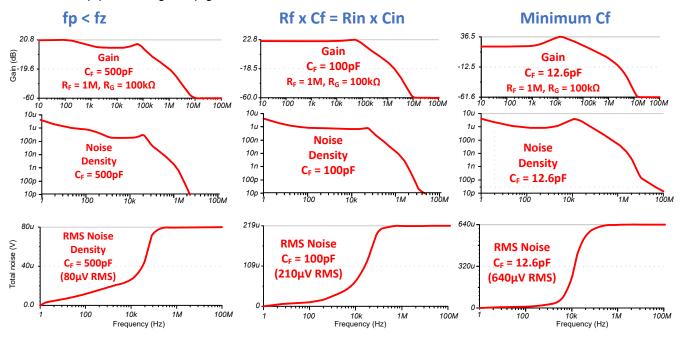

| 5.3 Minimum, Balanced, and Maximum Feedback Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.4 Transimpedance Case                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6 Complex Open-Loop and Closed-Loop Output Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.1 Converting Open-Loop Output Impedance to Closed-Loop Output Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.2 Open-Loop and Closed-Loop Model Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.3 Instability Due to Resonance From Complex Output Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.4 Impact of Internal Op Amp Topology on Output Impedance Versus Frequency10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.5 Other Factors Effecting Output Impedance10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7 A <sub>OL</sub> Impact on Stability11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.1 A <sub>OL</sub> Secondary Poles and Zeros11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7.2 Modeling the A <sub>OL</sub> Secondary Poles and Zeros and Input Capacitance11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7.3 Decompensated Op Amps and Stability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.4 The Impact of Closed-Loop Gain on Stability11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Trademarks www.ti.com

9 References 124

## **Trademarks**

E2E<sup>™</sup> and TINA-TI<sup>™</sup> are trademarks of Texas Instruments. All trademarks are the property of their respective owners.

www.ti.com Introduction

#### 1 Introduction

This introduction provides simplified explanations of the factors that cause stability problems in operational amplifiers. The section introduces common examples of issues and common stabilizing tools. Finally, the introduction demonstrates how the datasheets for TI's operational amplifiers provide quick and simple designs for op amp stability, and TI's designs do not require the complex methods covered later in the document.

## 1.1 Simple Analogy Explaining Instability

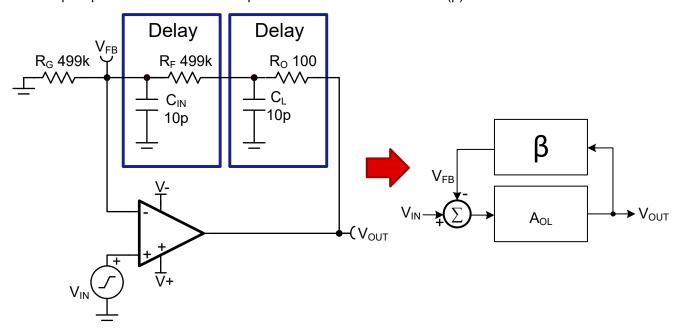

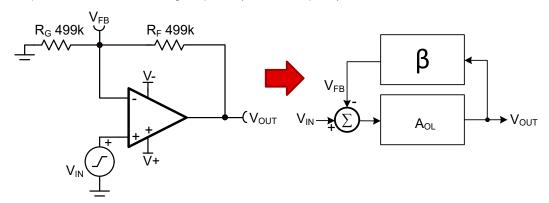

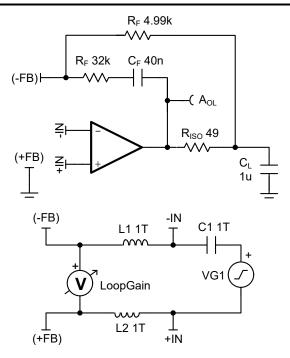

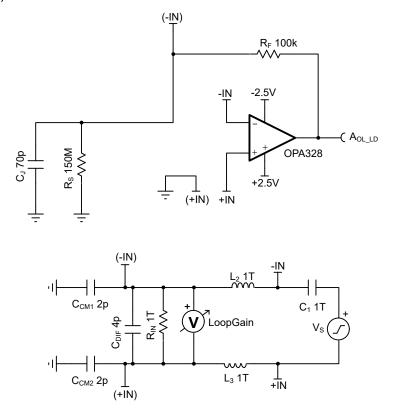

Figure 1-1 illustrates an op amp circuit with stability issues and an equivalent control system diagram. Control system diagrams and control system terminology are often used in op amp stability discussions because much of the literature for stability was developed for control systems and then applied to op amp circuits. The inputs of the op amp correspond to the following blocks for the summing block of the control system:

- The amp open-loop gain (A<sub>OL</sub>) is the control system gain block.

- The op amp feedback network corresponds to the beta feedback block (β).

Figure 1-1. Operational Amplifier Circuit and Control System Equivalent

The circuit in Figure 1-1 is unstable because of the delay elements in the feedback network. The delay elements are simply RC low pass filters. A low pass filter naturally has a group delay or phase shift. The reason that this feedback delay causes instability can be understood by thinking of the op amp circuit as a control system. The input summing block of the op amp senses the output signal through the feedback network. The output of the summing block is the error signal. In this example, the target for  $V_{OUT}$  is  $2 \times V_{IN}$ . When  $V_{OUT} = 2V_{IN}$  the error signal is zero. When the output is too high  $(V_{OUT} > 2 \times V_{IN})$ , the error signal is negative and the op amp tries to drive the output downward. Similarly, when the output is too low  $(V_{OUT} < 2 \times V_{IN})$ , the error signal is positive and the op amp tries to drive the output upward to cancel the error. Thus, the output is a constant value of  $V_{OUT} = 2V_{IN}$  when the system is in equilibrium.

However, the functionality of the system assumes the feedback signal ( $V_{FB}$ ) is not significantly delayed. If  $V_{FB}$  is significantly delayed, the op amp can incorrectly identify the output as going upward when the output is actually going downward. This outcome creates an error signal with the wrong polarity, which drives the output in the wrong direction. Instability of the op amp is caused by this delay in the feedback signal.

Many engineers see the circuit shown in Figure 1-1 and understand that the feedback delay is a problem, and the general assumption is no one intentionally designs such an impractical circuit. However, the circuit shown in Figure 1-1 is frequently inadvertently created by the internal open-loop output impedance ( $R_O$  or  $Z_O$ ), the input capacitance of the op amp, and any parasitic PCB capacitance ( $C_{IN} = C_{CM} + C_{PCB}$ ). Figure 1-2 shows the circuit redrawn to emphasize how the delay elements are created in a practical op amp circuit.

Introduction www.ti.com

Figure 1-2. Origin of Delay Elements in a Practical Circuit

## 1.2 Circuits With Possible Stability Issues

Analyzing and compensating stability problems is one of the most challenging disciplines for analog system designers. Although developing a deep understanding on the subject of stability can take time and effort, identifying potential stability issues is relatively easy with a simple circuit inspection. For engineers who are new to stability analysis, identifying the problem is an important first step. Fortunately, this document helps new engineers compensate the amplifier to solve the stability issue, and many additional resources are available which provide support and assistance with these types of issues (for example, the Texas Instruments E2E™ community).

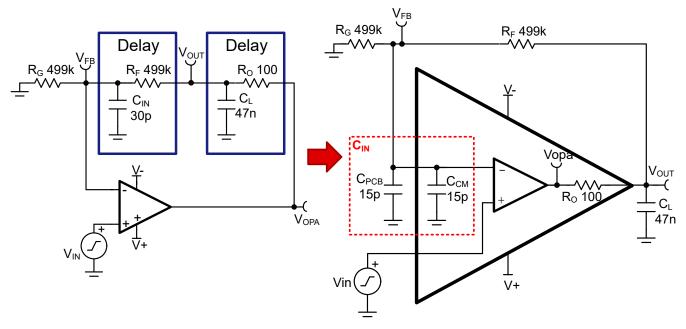

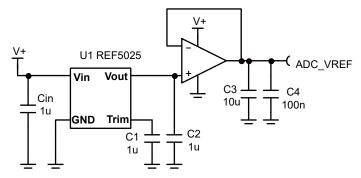

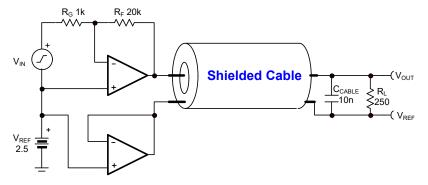

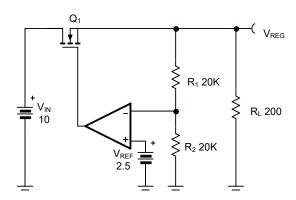

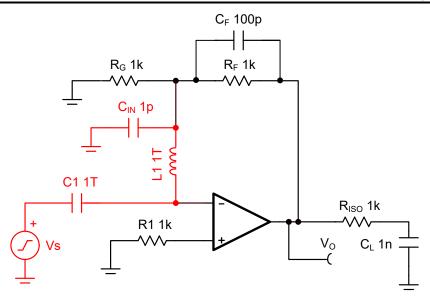

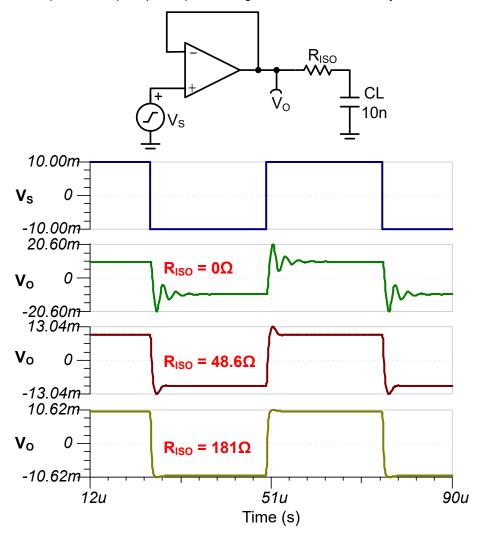

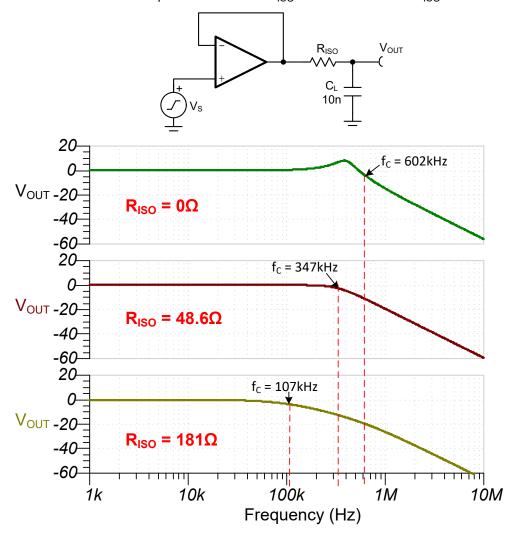

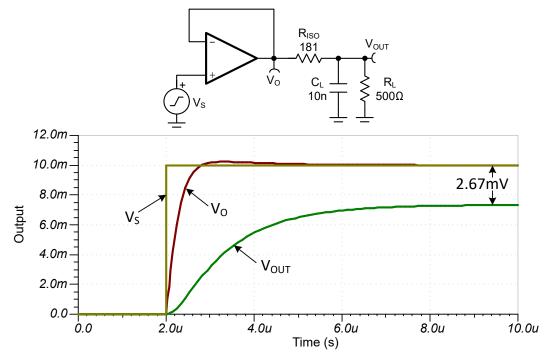

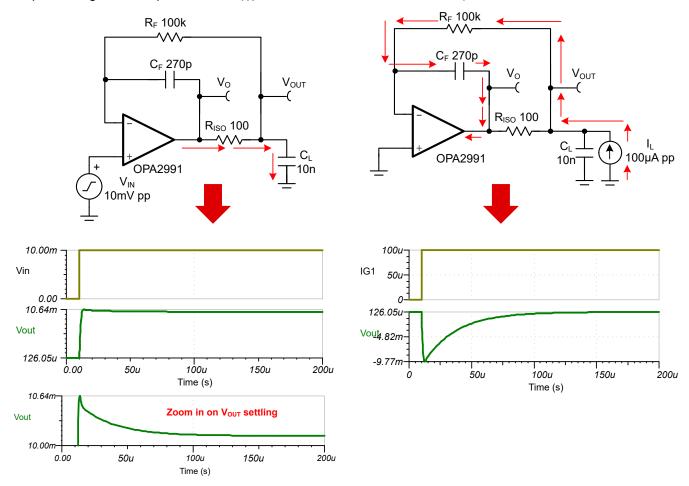

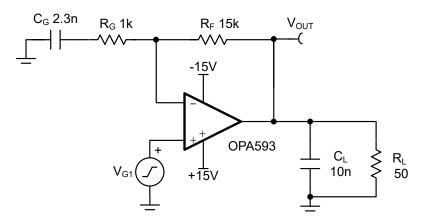

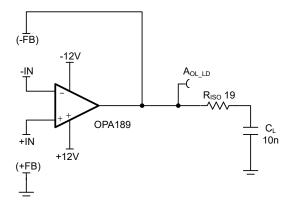

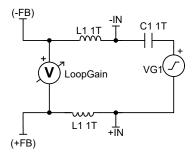

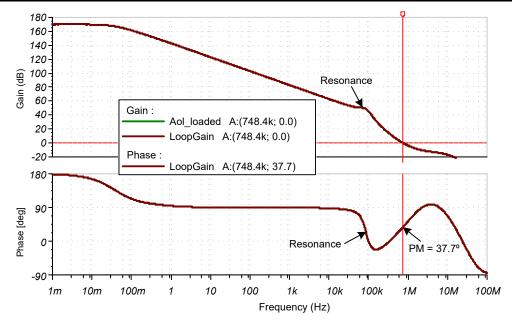

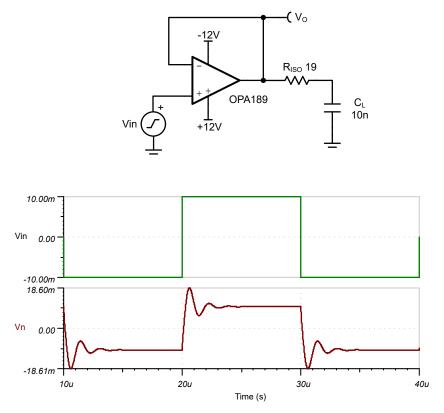

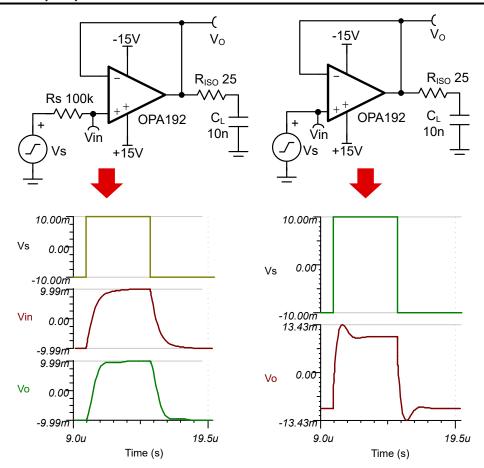

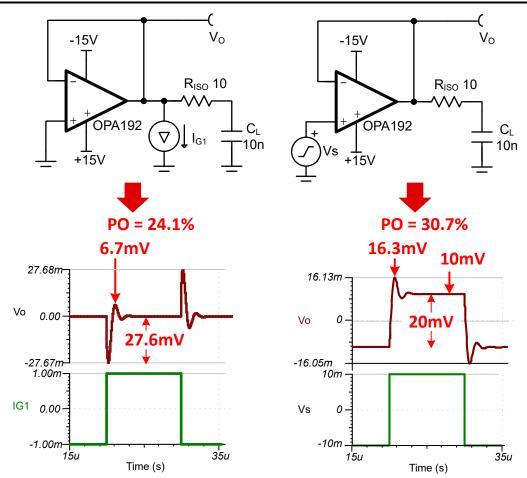

Figure 1-3 through Figure 1-5 illustrate examples of circuits with stability issues due to a load capacitance ( $C_L$ ) on the output of the op amp. This load capacitance creates a delay in the feedback signal due to a delay from the RC time constant added by the internal open-loop output resistance  $R_OC_L$ . Figure 1-3 shows a common application where an op amp is used to buffer a voltage reference which drives an analog-to-digital converter. The problem in this application is that the output capacitors, C3 and C4, are directly connected to the amplifier output and this normally leads to stability problems. Figure 1-4 shows an op amp circuit driving a long cable. Cables can have significant capacitance per unit length, and can often introduce stability issues. Figure 1-5 shows an op amp driving a power MOSFET. This is a common application as the gate capacitance of a power MOSFET can be significant. The problem in each case is too much capacitance connected to the output of the op amp. A common correction for this type of issue is to use an isolation resistor between the op amp output and the load capacitance. Methods for selecting this resistor (see Isolation Resistor ( $R_{\rm ISO}$ ) Method) are covered later in this document.

Figure 1-3. Reference Buffer Capacitive Load Issue

www.ti.com Introduction

Figure 1-4. Cable Drive Capacitive Load Issue

Figure 1-5. MOSFET Gate Drive Capacitive Load Issue

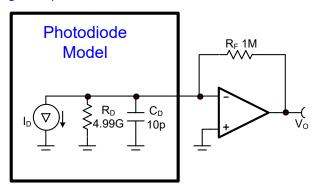

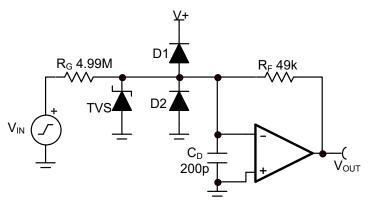

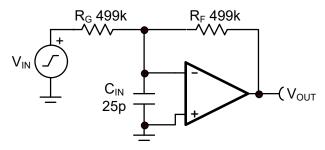

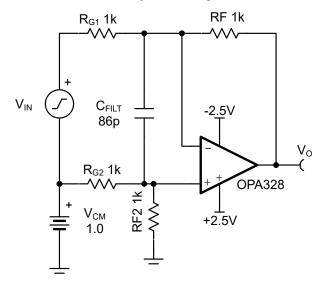

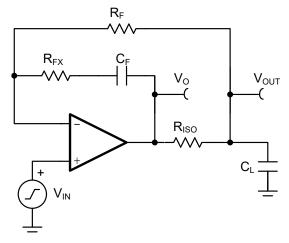

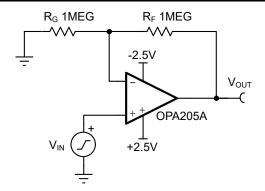

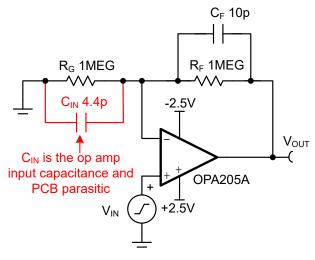

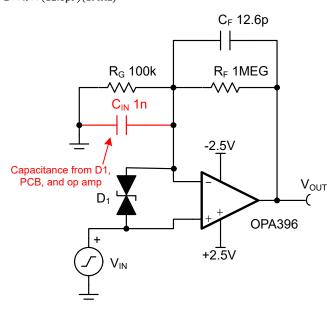

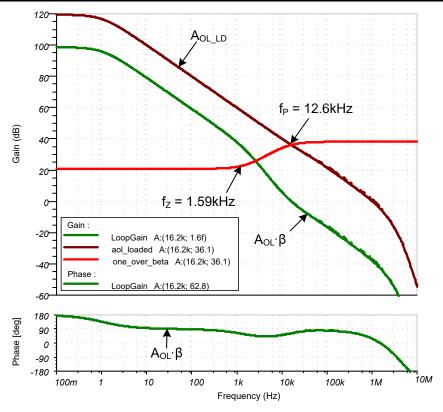

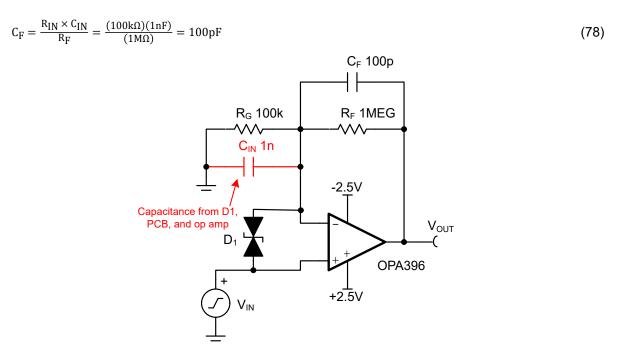

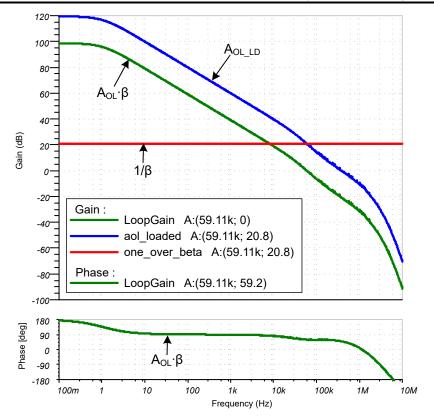

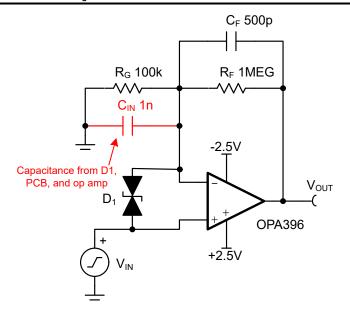

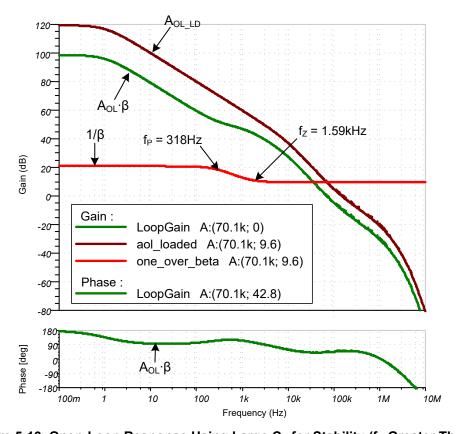

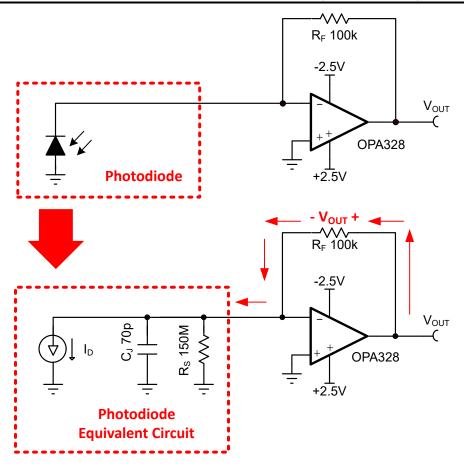

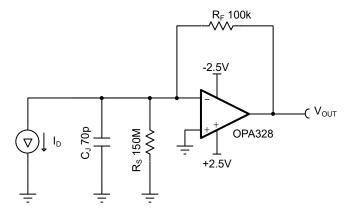

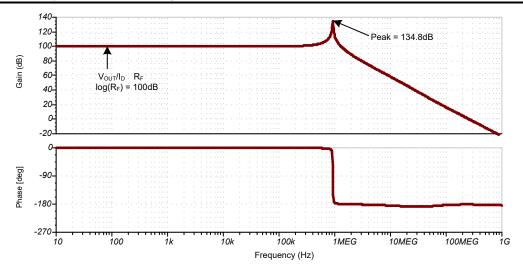

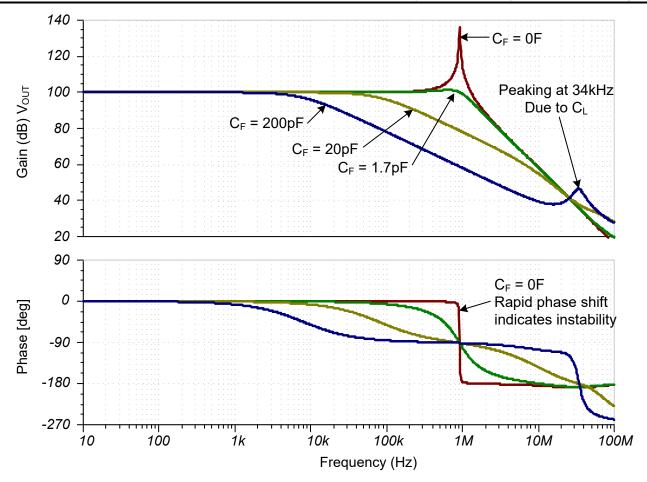

Figure 1-6 through Figure 1-8 illustrate examples of circuits with stability issues due to a capacitance on the inverting node of the op amp or large feedback resistors. The feedback delay that causes the instability is from the RC time constant of R<sub>F</sub>C<sub>IN</sub>. Figure 1-6 shows a photodiode transimpedance amplifier. Photodiodes can have significant parasitic capacitance and these circuits often use large feedback resistors for high transimpedance gain. Similar to the transimpedance circuit, input protection diodes can have high capacitance (see Figure 1-7). Also, low-power circuits generally use large feedback resistors to minimize power consumption. In this case, even if the input capacitance is relatively low, the large feedback elements can cause instability (see Figure 1-8). Stability problems related to capacitance on the inverting node can be corrected by adding a feedback capacitor. The details behind selecting this capacitor are covered later in this document (see Stability Corrections for Capacitance on the Inverting Node).

Figure 1-6. Photodiode Transimpedance Amplifier Adds Capacitance to Inverting Node

Introduction Www.ti.com

Figure 1-7. Input Protection Diodes Add Capacitance to Inverting Node

Figure 1-8. Low-Power Circuit With Large Feedback Impacted by Capacitance on Inverting Node

## 1.3 Simple Stability Correction Based on Datasheet Plots

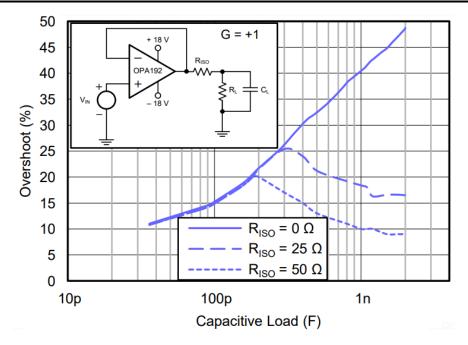

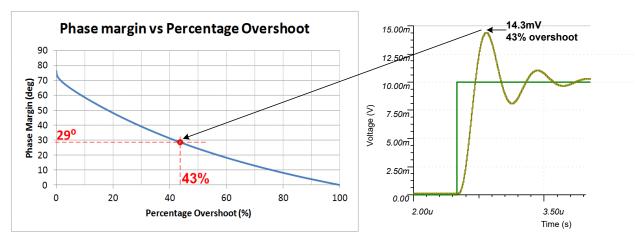

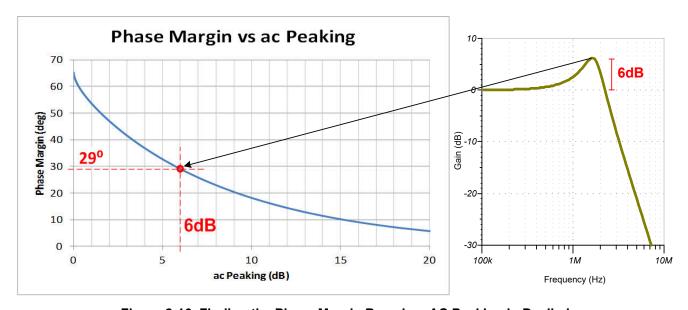

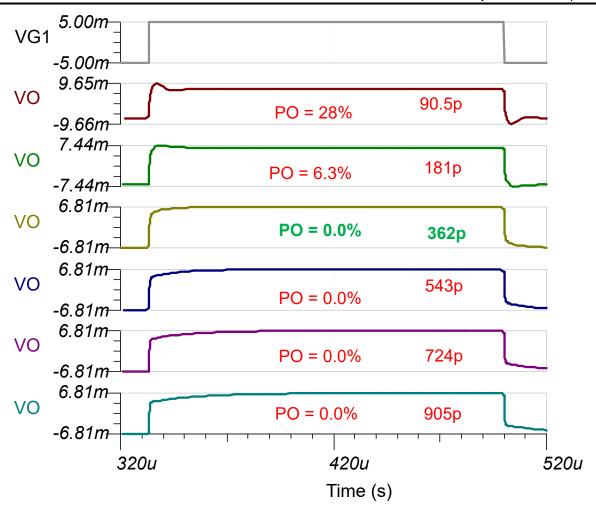

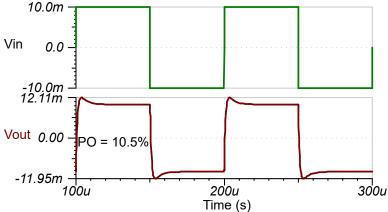

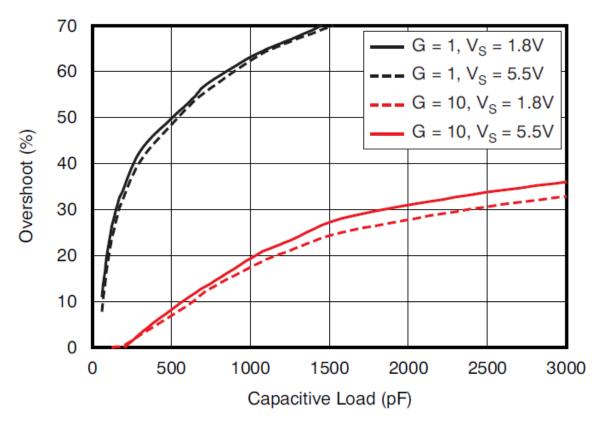

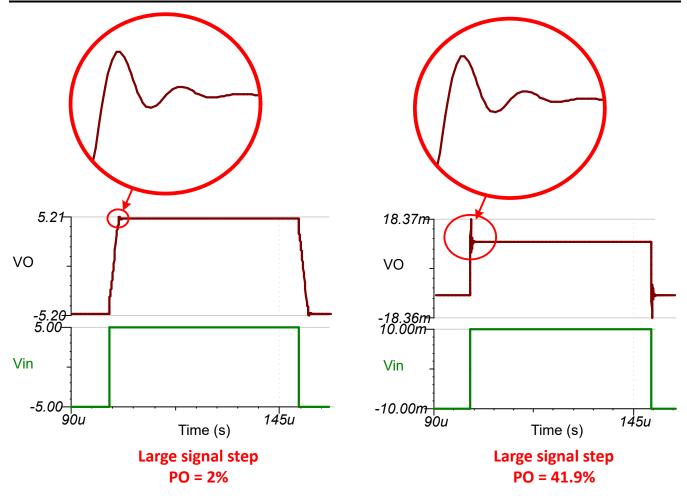

Op amps can have stability problems when driving capacitive loads. The specific amount of capacitance that causes a stability issue is different for different op amp devices, based on the value of  $Z_{\rm O}$ . Some op amps are specifically designed to operate with larger capacitive loads. Many op amp datasheets provide a graph of small-signal overshoot versus capacitive load or phase margin versus capacitive load. Percentage overshoot (PO) and phase margin (PM) are directly related to each other and engineers can convert between the two mathematically. A lower phase margin corresponds to a higher overshoot and decreased stability. TI recommends a phase margin of greater than 45° or less than 23% overshoot for good stability. Some engineers accept a phase margin as low as 30° or 41% overshoot. Engineers can adjust the criteria according to the application requirements.

Regardless of the criteria, engineers can use the datasheet graph to determine if the capacitive load is acceptable. In some cases, the graph includes multiple curves to show how different isolation resistors extend the capacitive load range for stable operation. The graphs also specify the op amp configuration used to drive the capacitive load because the configuration affects the stability. Figure 1-9 shows the small-signal overshoot graph for OPA192 in a buffer configuration. For this device, the maximum capacitive load for 20% overshoot and  $R_{\rm ISO}$  =  $0\Omega$  is about 200pF. For a  $50\Omega$  isolation resistor, the circuit can drive capacitances well beyond 1nF and still keep overshoot less than 20%. The  $25\Omega$  isolation resistance also extends the capacitance range well beyond 1nF, however, the overshoot increases to 25% over some capacitance ranges.

www.ti.com Introduction

Figure 1-9. Overshoot Versus Capacitive Load for OPA192 in G = +1V/V

## 1.4 Introducing Lab Tools and Measurements

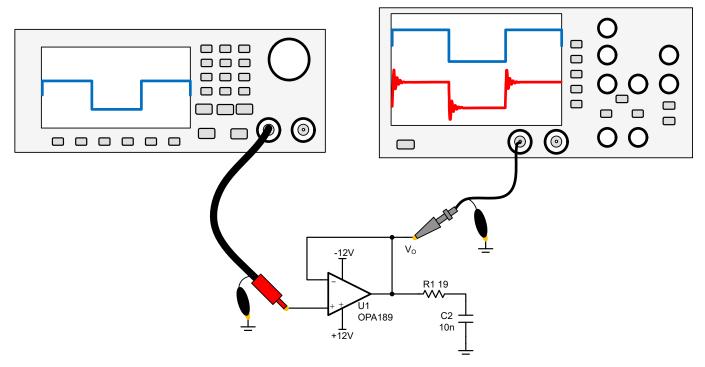

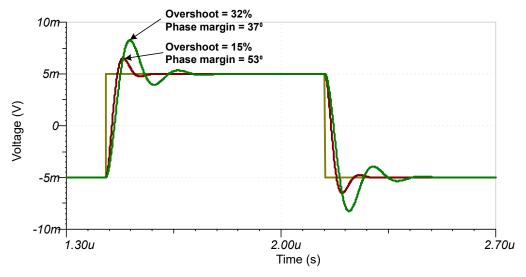

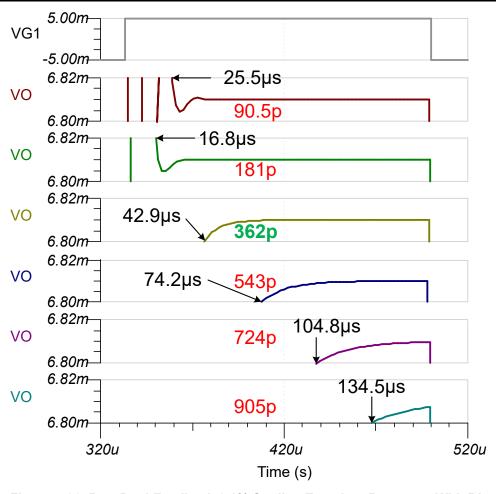

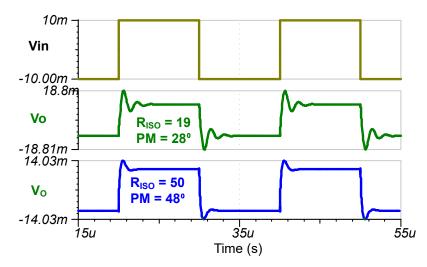

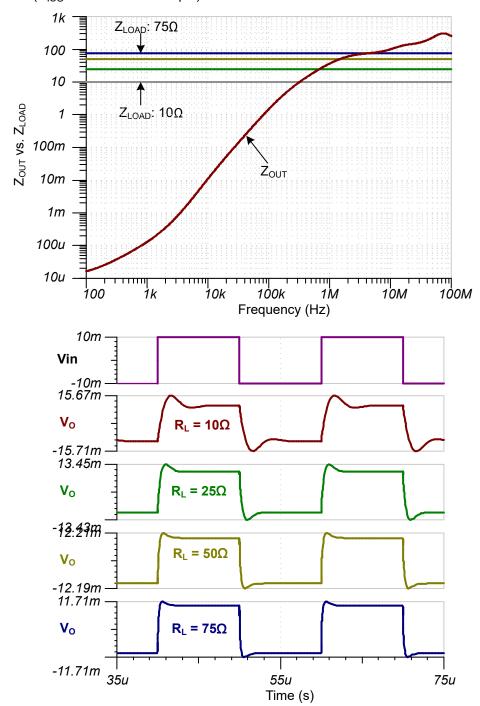

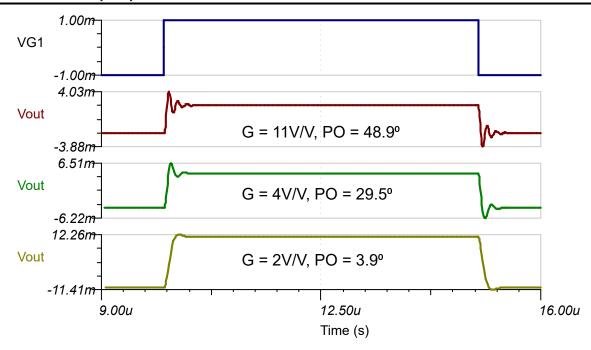

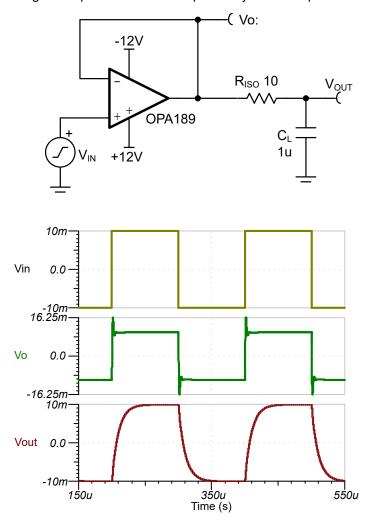

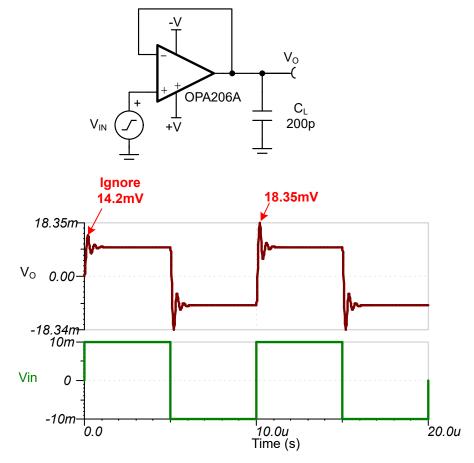

The stability of op amps can be measured with a signal generator and an oscilloscope. This type of testing is sometimes called non-invasive because the testing can be done without circuit modification, such as opening the feedback loop. This testing is normally done by applying a small signal input square wave and measuring the transient overshoot on the output signal. A small signal is generally defined as less than 100mVpp, but the actual threshold depends on the internal design of the op amp. Since the small signal threshold depends on the internal design of the op amp, Tl's advice is to use a 10mVpp square wave to be certain that the input is small signal. For this test, the magnitude of the overshoot is directly related to the phase margin. Figure 1-10 illustrates the small signal square wave test, and Indirect (Non-Invasive) Stability Tests explains how to judge stability based on this test.

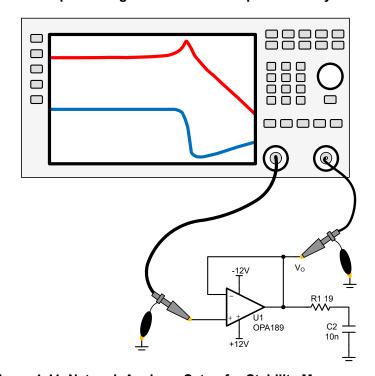

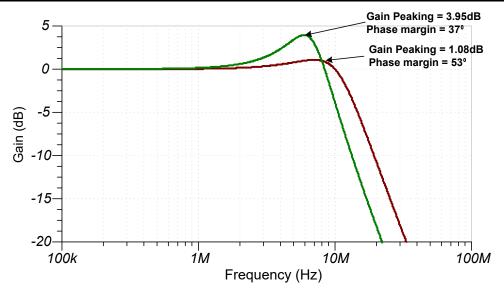

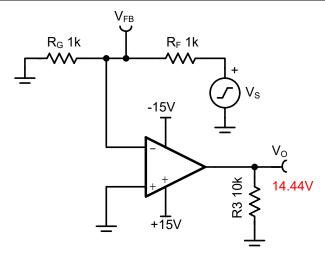

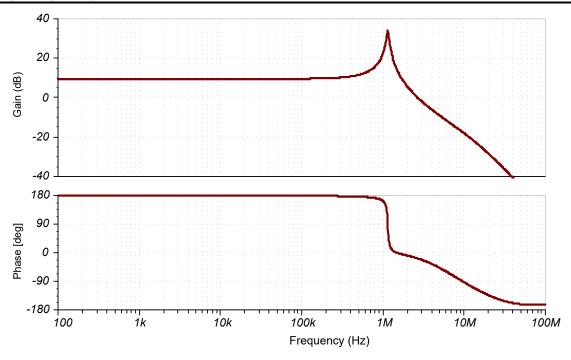

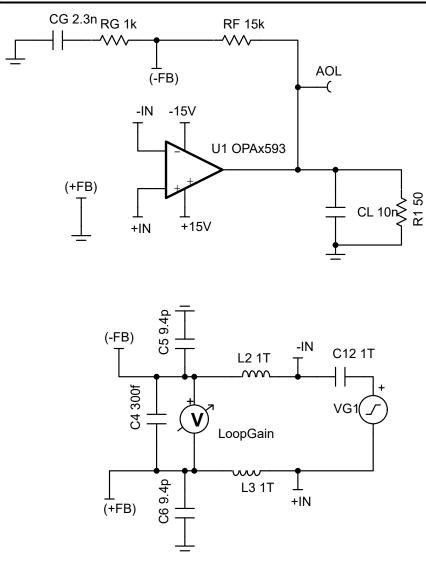

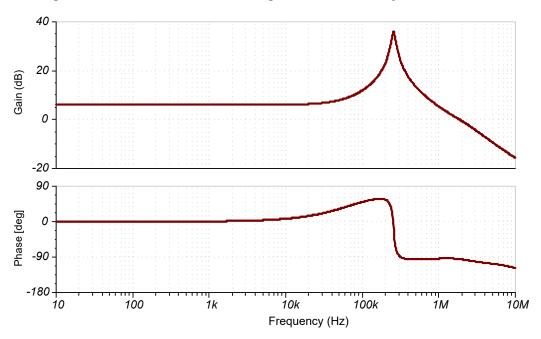

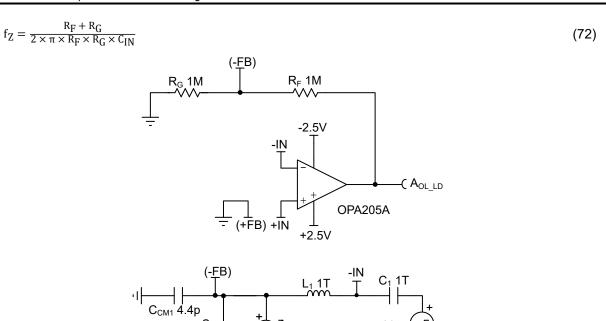

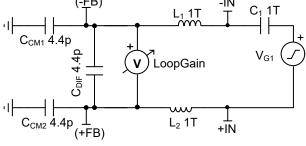

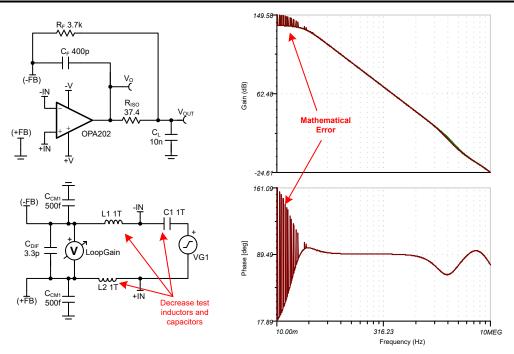

Another approach to measuring stability is to use a network analyzer. The network analyzer is used to measure the closed-loop frequency response (for example, gain and phase versus frequency). When using this method, instability can be identified by a large gain peak and a rapid phase shift of approximately 90°. Figure 1-11 shows a typical test setup that uses a network analyzer to test stability. Often, stability issues can be resolved using the simulation in Figure 1-11. Assuming the op amp is properly modeled, stability simulations accurately reflect the real-world equivalent circuit.

Figure 1-10. Scope and Signal Generator Setup for Stability Measurement

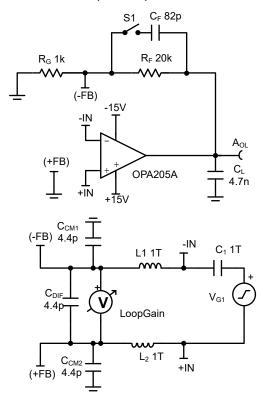

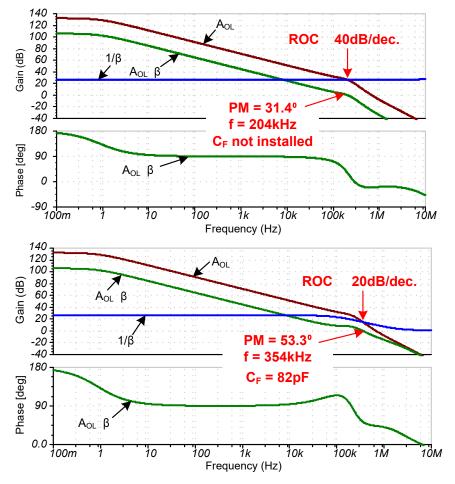

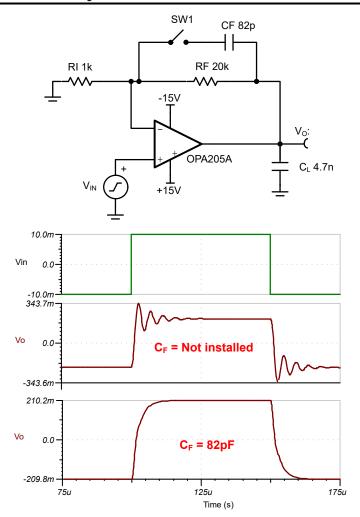

Figure 1-11. Network Analyzer Setup for Stability Measurement

## 2 Stability Theory for Operational Amplifiers

This section introduces the terminology and fundamentals of analyzing the stability of operational amplifiers. This section covers open-loop and closed-loop methods for testing the stability of op amps. The section also discusses the specific parameters that impact the stability of op amps.

#### 2.1 Poles and Zeros

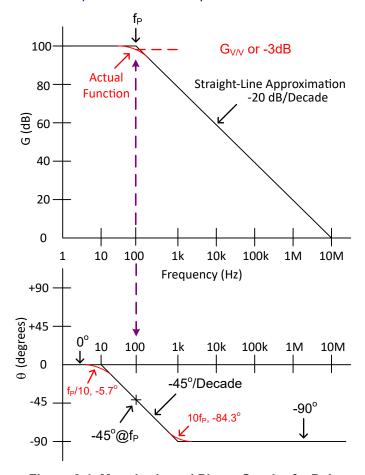

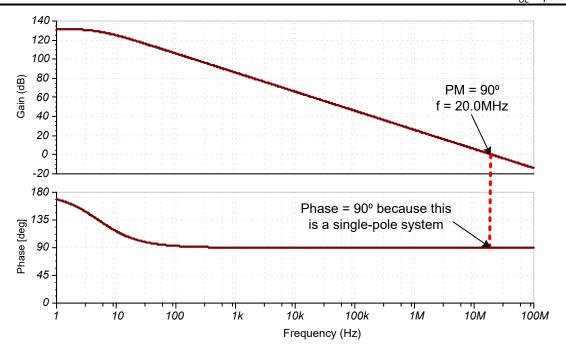

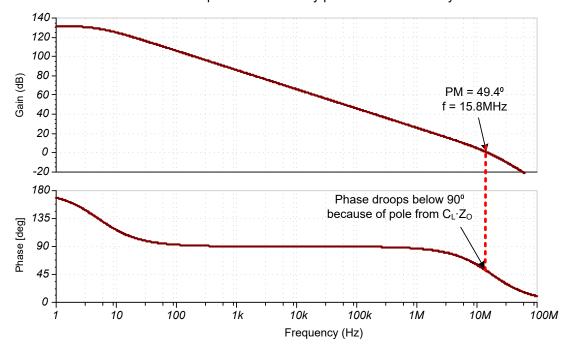

Understanding poles and zeros is a critical skill required for solving the stability problems of op amps. Poles are the roots of the s-domain equation in the denominator of the transfer function, and zeros are roots of the numerator (see Equation 1). Figure 2-1 shows the bode plot for a transfer function with a single pole. At the pole frequency, the magnitude plot is 3dB below the DC value ( $G_{DC}$ ). After the pole frequency, the gain decreases by 20dB/decade. At the pole frequency, the phase plot has dropped by 45° from the DC phase. The phase shift starts approximately one decade before the pole and ends approximately one decade after the pole frequency for a total phase shift of  $-90^{\circ}$ . The phase shift decreases at a rate of 45°/decade from roughly  $f_P/10$  to  $f_P \times 10$ . Equation 2 shows the complex transfer function for a system with a single pole. Equation 3 shows the transfer functions gain magnitude in V/V and Equation 4 shows the phase shift.

Figure 2-1. Magnitude and Phase Graph of a Pole

where

$$s = j \times \omega$$

, and  $j = \sqrt{-1}$  (1)

$$G_{V/V} = \frac{V_{OUT}}{V_{IN}} = \frac{G_{DC}}{\left(\frac{s}{\omega_P}\right) + 1} = \frac{G_{DC}}{j\left(\frac{f}{f_P}\right) + 1}$$

(2)

$$\left|G_{V/V}\right| = \frac{V_{OUT}}{V_{IN}} = \frac{G_{DC}}{\sqrt{\left(\frac{f}{fp}\right)^2 + 1}} \tag{3}$$

$$\theta = -\tan^{-1}\left(\frac{f}{fp}\right) \tag{4}$$

Figure 2-2 shows the bode plot for a transfer function with a single zero. At the zero frequency, the magnitude plot is 3dB above the DC value. After the zero frequency, the gain increases by 20dB/decade. At the zero

frequency, the phase plot has increased by  $45^{\circ}$  from the DC phase. The phase shift starts approximately one decade before the pole and ends approximately one decade after the pole frequency for a total phase shift of  $+90^{\circ}$ . The phase shift increases at a rate of  $45^{\circ}$ /decade from roughly  $f_Z/10$  to  $f_Z \times 10$ . Equation 5 shows the complex transfer function for a system with a single zero. Equation 6 shows the transfer functions gain magnitude in V/V and Equation 4 shows the phase shift.

Figure 2-2. Magnitude and Phase Graph of a Zero

$$G_{V/V} = \frac{V_{OUT}}{V_{IN}} = G_{DC} \times \left( \left( \frac{s}{\omega_Z} \right) + 1 \right) = G_{DC} \times \left( j \left( \frac{f}{f_Z} \right) + 1 \right)$$

(5)

$$\left|G_{V/V}\right| = \frac{V_{OUT}}{V_{IN}} = G_{DC} \times \sqrt{\left(\frac{f}{f_Z}\right)^2 + 1} \tag{6}$$

$$\theta = \tan^{-1} \left( \frac{f}{f_7} \right) \tag{7}$$

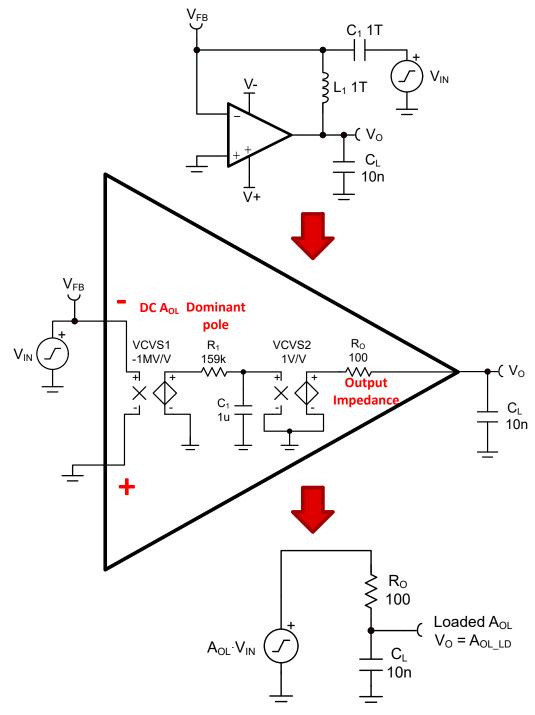

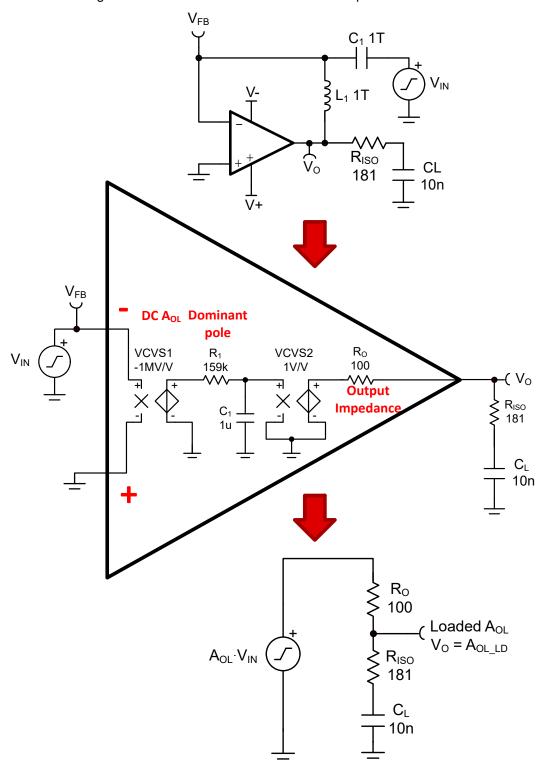

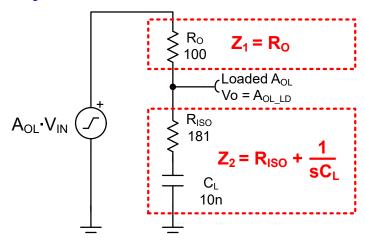

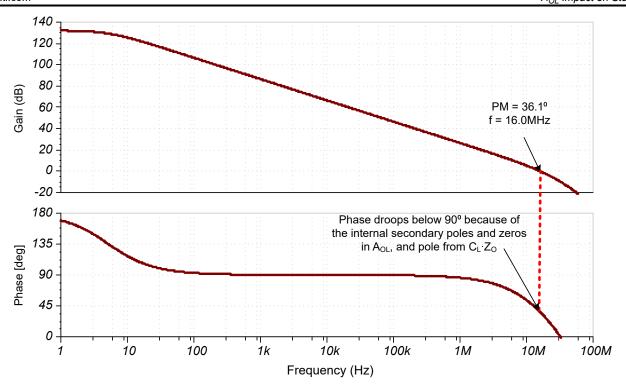

### 2.2 Operational Amplifier Model Requirements for Stability Verification

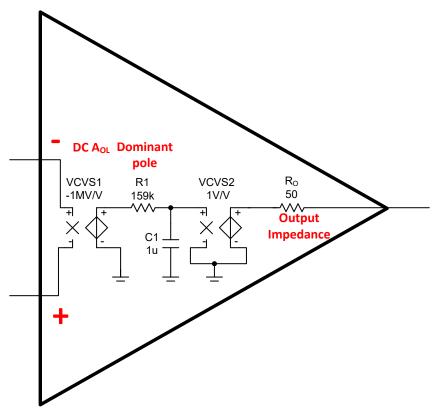

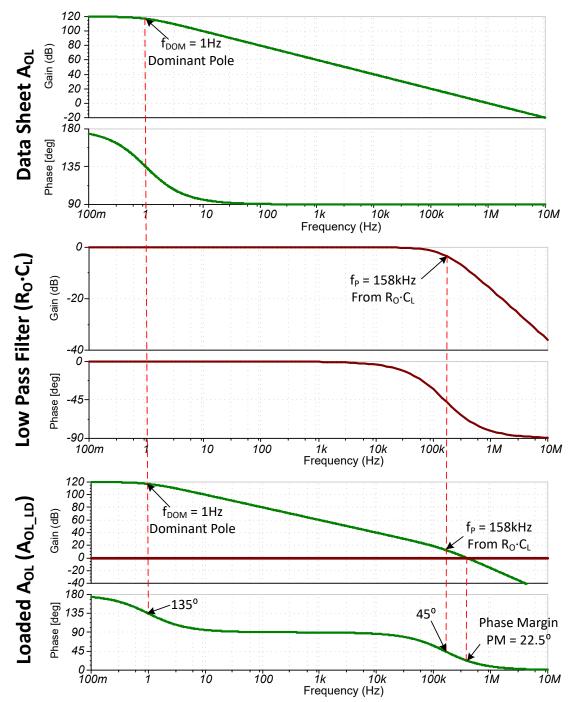

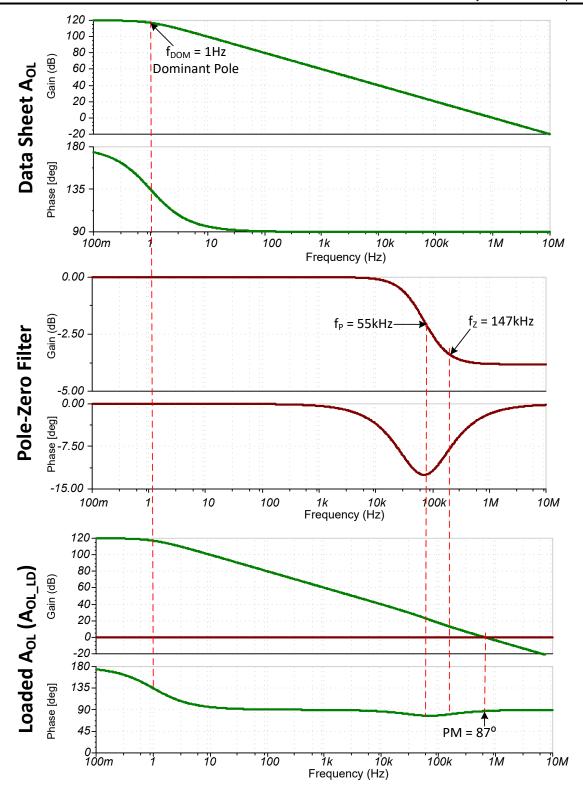

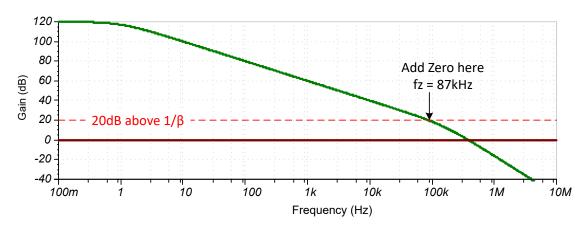

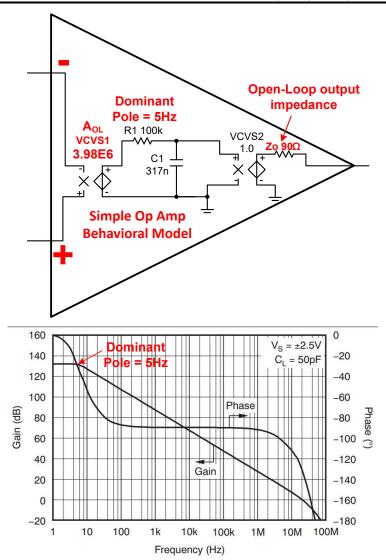

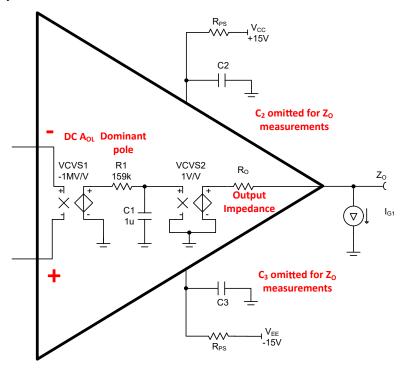

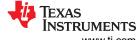

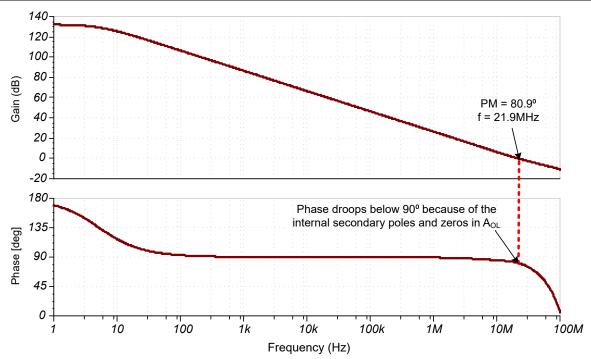

Figure 2-3 illustrates the minimum requirement for an op amp model that can be used for stability testing. The model must accurately match the real  $A_{OL}$  over frequency, the open-loop output impedance, and input capacitance of the op-amp. The DC  $A_{OL}$  value is modeled with the voltage-controlled voltage source on the input (VCVS1 = -1M V/V, for 120dB). The dominant pole is modeled with simple RC low pass filters. The output of the low pass filter is buffered with a voltage-controlled voltage source in a gain of 1V/V. The open-loop output impedance ( $Z_O$ ) is modeled with a simple resistor in this case, but many devices require a complex impedance.

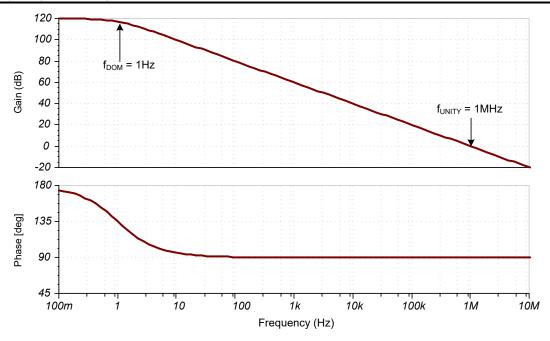

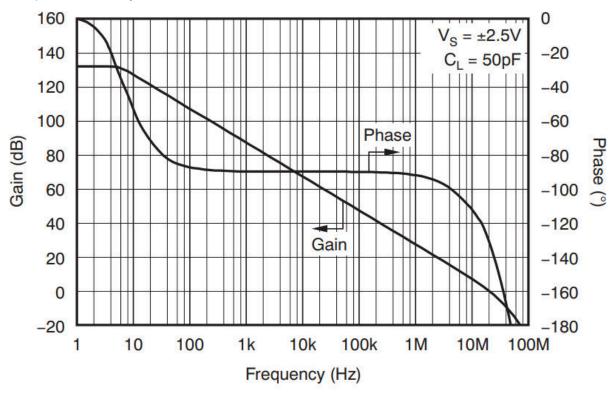

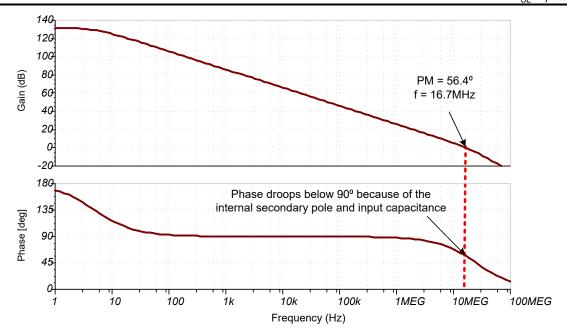

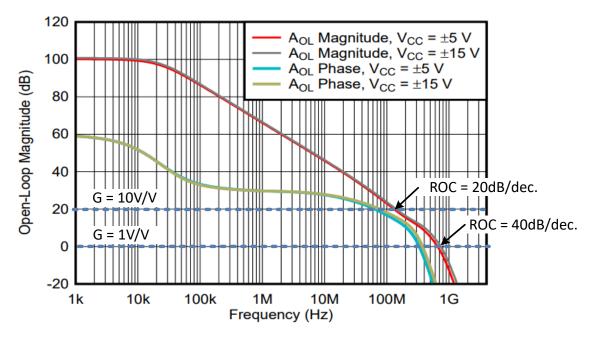

Figure 2-4 illustrates the graph of  $A_{OL}$  for Figure 2-3. Notice that the DC  $A_{OL}$  corresponds to VCVS1, and the dominant pole corresponds to  $1/(2 \times \pi \times R1 \times C1)$ . Note that the dominant pole imparts a  $-90^{\circ}$  phase shift. The phase shift at low frequency is  $180^{\circ}$  due to the op amps negative feedback. Beyond the dominant pole, many op amps have multiple secondary poles and zeros near the unity gain frequency of the amplifier, as well as input capacitance (see Modeling the  $A_{OL}$  Secondary Poles and Zeros and Input Capacitance for details).

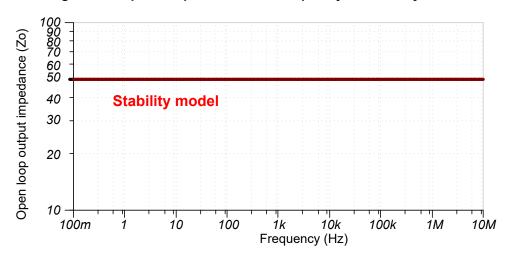

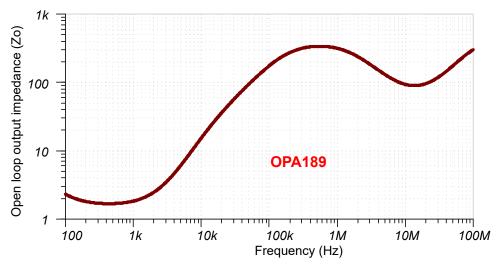

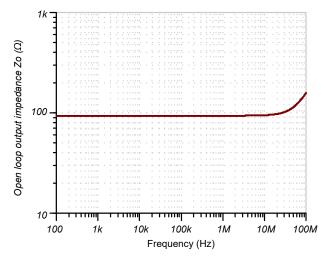

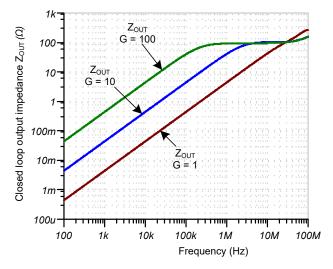

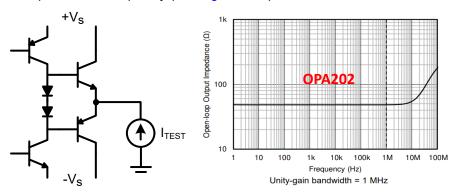

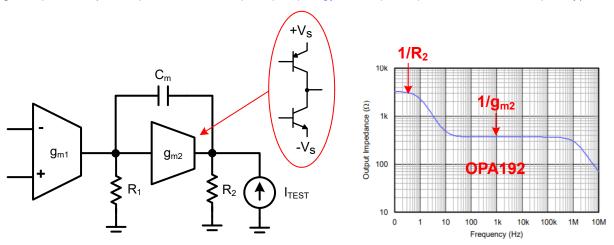

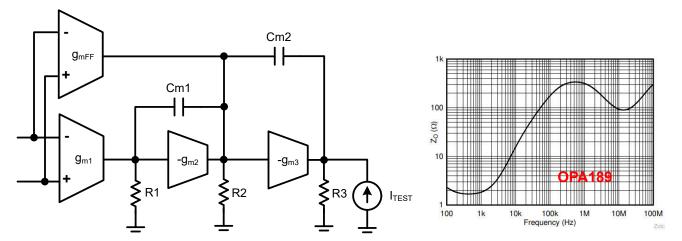

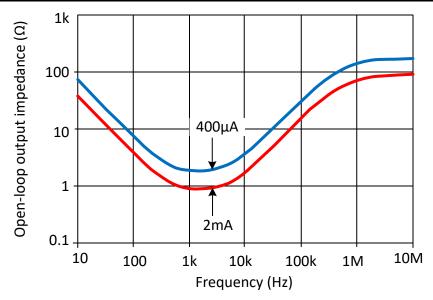

Figure 2-4 illustrates the open-loop output impedance for the model shown in Figure 2-3. This model uses a resistive open-loop output impedance ( $Z_O$ ). Resistive  $Z_O$  (denoted as  $R_O$ ) is the easiest to understand and also the better case from a stability perspective. The initial theory, assuming  $Z_O$  is resistive, is explained in this document, and later shows how a complex  $Z_O$  can impact stability. Practical op amps can have a resistive  $Z_O$  or complex  $Z_O$ . Modeling the output impedance of an op amp for stability analysis explains how to build a model with a complex  $Z_O$ . Most Texas Instruments' models accurately model both  $Z_O$  and  $A_{OL}$  over frequency so individually developing these models is generally unnecessary.

Figure 2-3. Operational Amplifier Model for Stability Simulations

Figure 2-4. Open-Loop Gain Versus Frequency for Stability Model

Figure 2-5. Resistive Open-Loop Output Impedance Versus Frequency for Stability Model

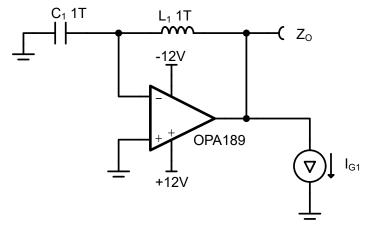

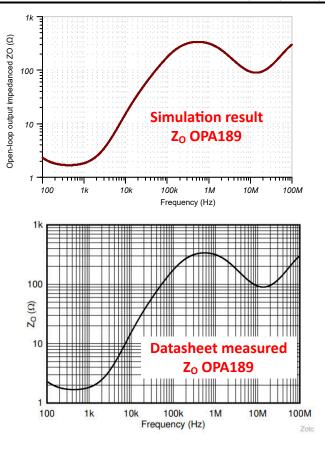

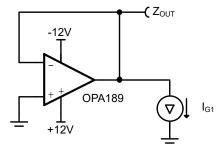

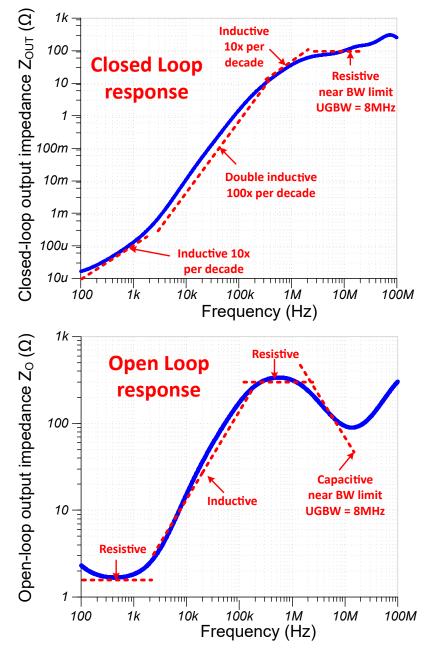

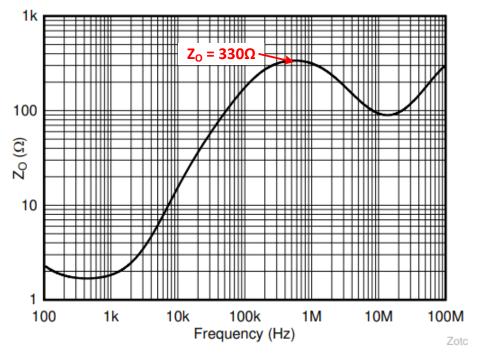

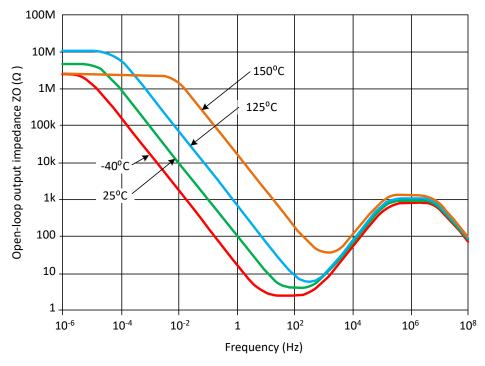

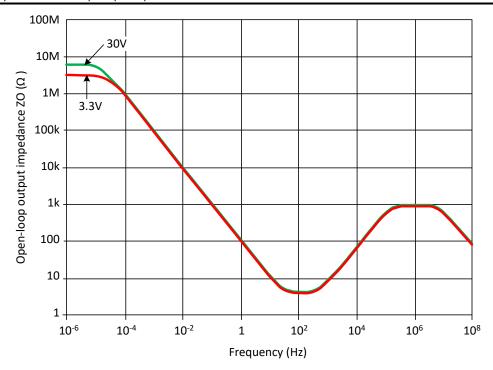

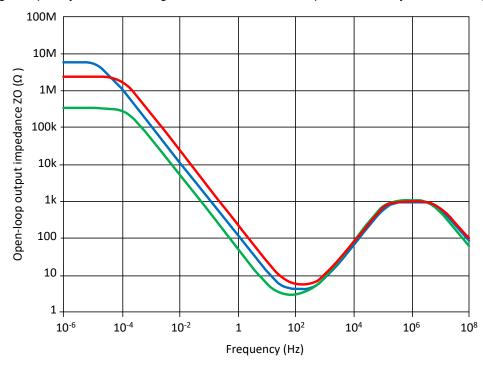

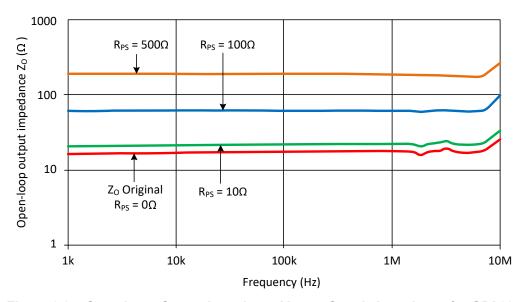

Figure 2-6. Complex, Open-Loop, Output Impedance Example (OPA189)

## 2.3 Stability Definitions Based on Control Loop Model

Figure 2-7 shows a simple non-inverting op amp circuit with a simple control-systems equivalent diagram. The control diagram models the op amp input as a summing block with the feedback path inverted. The open-loop gain across frequency is modeled as shown in Figure 2-3. The op amp feedback network forms the  $\beta$  factor in the control system. The feedback factor is the gain from the output to the inverting amplifier node ( $\beta$  =  $V_{FB}$  /  $V_{OUT}$ ). For this example,  $\beta$  is a simple voltage divider, but in many cases,  $\beta$  can be a more complex relationship. The closed-loop gain equation can be derived by applying the input and output signals to the control system diagram and applying simple algebra (see Equation 10). The denominator of the closed-loop gain equation contains the term  $A_{OL} \times \beta$ . This term is critical to stability analysis and is called loop gain (see Equation 11). For very large values of loop gain, the closed-loop gain can be approximated as  $1/\beta$ . The limit function in Equation 12 shows that when  $A_{OL} \times \beta$  is much greater than 1, the 1 in the denominator can be ignored and the  $A_{OL}$  terms cancel out leaving  $A_{CL} \cong 1/\beta$ . Substituting Equation 9 into Equation 12 and applying algebra produces the familiar gain equation for a non-inverting amplifier ( $G = R_F / R_G + 1$ ).

Figure 2-7. Op Amp Circuit and Equivalent Controls System Diagram

$$A_{OL} =$$

Open Loop Gain over frequency (8)

$$\beta = \text{Feedback Factor} = \frac{V_{FB}}{V_{OUT}} = \frac{R_G}{R_G + R_F}$$

(9)

$$A_{CL} = Closed Loop Gain = \frac{A_{OL}}{1 + A_{OL}\beta}$$

(10)

$$A_{OL}\beta = \text{Loop Gain}$$

(11)

$$A_{CL} = \lim_{A_{OL}\beta \to \infty} \left( \frac{A_{OL}}{1 + A_{OL}\beta} \right) \cong \frac{1}{\beta} = 1 + \frac{R_F}{R_G}$$

(12)

The closed-loop gain equation (Equation 10) can be used to determine amplifier stability. An amplifier is considered unstable when the denominator of  $A_{CL}$  is zero. This happens when  $A_{OL} \times \beta = -1$ . Converting the linear value of loop gain to decibels ( $A_{OL} \times \beta = -1$ ) means that the magnitude of  $A_{OL} \times \beta(dB) = 0$ dB, and the phase shift  $A_{OL} \times \beta(dB) = -180^\circ$ . If you remember the analogy in Section 1.1, the instability is due to a delay in the feedback. The  $-180^\circ$  phase shift is the feedback delay that causes instability. The op amp *thinks* the output is going up when the output is actually going down. In any case, when loop gain in decibels is 0dB and the phase shift relative to the DC phase is 180°, the closed-loop gain becomes very large and the circuit is unstable. In Section 2.6, you can see that an indirect way of measuring circuit stability in the lab is to look for large gain peaking.

#### Note

## Criteria for stability:

- Instability happens when the denominator of A<sub>Cl</sub> is zero

- The denominator is zero when A<sub>OL</sub> × β = -1

- $A_{OL}\beta = -1$  sets the denominator of  $A_{CL} = 0$

- A<sub>OL</sub>β = -1 when A<sub>OL</sub>β(dB) = 0dB and A<sub>OL</sub>β(phase\_shift) = -180°

- · Phase shift is relative to the DC phase

Phase margin describes how close a circuit is to instability. Mathematically, this description is the amount of phase remaining when  $A_{OL} \times \beta(dB) = 0 dB$  before the phase shift  $A_{OL} \times \beta(phase\_shift) = -180^\circ$ . For example, if the phase shift relative to DC is 170° when  $A_{OL} \times \beta(dB) = 0 dB$ , then the phase margin is 10°. From a practical perspective, amplifiers with a very low phase margin are effectively nonfunctional. Poor phase margin leads to very large gain peaking, large overshoot, and oscillations. In some cases, the oscillations are continuous even when the input is a DC signal. Some engineers consider cases where the oscillations eventually settle out as an acceptable outcome. However, circuits that are marginally stable have large overshoot and oscillations for any change on the input, power supplies, or output loading.

#### Note

## Definition of phase margin:

- · Phase margin describes how close a circuit is to instability

- When A<sub>OL</sub> × β(dB) = 0dB the phase margin is the phase remaining before A<sub>OL</sub> × β(phase\_shift) =

-180° and the circuit is unstable

- If the phase shift is 170° when  $A_{OL} \times \beta(dB) = 0dB$ , than the phase margin is 10°

- On a bode plot, phase margin is the phase shift relative to DC phase when  $A_{OL}$  intersects  $1/\beta$ , or when  $A_{OL} \times \beta(dB) = 0dB$  (see Figure 2-8)

- Most op amp circuits have a phase of 180° at DC, so the phase margin can be read directly on the graph where 0° is unstable (see Figure 2-8)

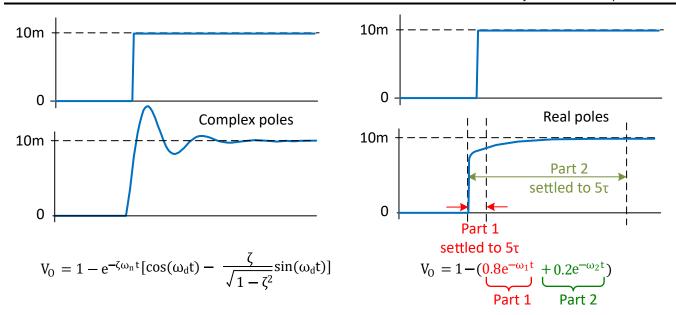

If the phase margin is zero, the circuit generally oscillates continuously. Circuits with a low, but non-zero, phase margin have high gain peaking, large overshoot, and very poor settling times. The recommendations for minimum phase margin differ depending on the engineering reference. TI recommends using a phase margin ≥ 45° for good stability. For some circuits, achieving a 45° phase margin is a challenge, so a phase margin as low as 35° is potentially acceptable. Keep in mind that the parameters impacting stability (such as open-loop output impedance, open-loop gain, and external component values) all have tolerance, so generally, having a phase margin above 45° is advisable so the design is robust across process corners.

#### **Note**

#### Phase margin general guidance:

- TI recommends a phase margin ≥ 45° for stable circuits

- 45° > Phase margin ≥ 35° is considered marginally stable, but can be acceptable in some cases

- Phase margin < 35° is unstable and leads to large overshoot, gain peaking, and oscillations</li>

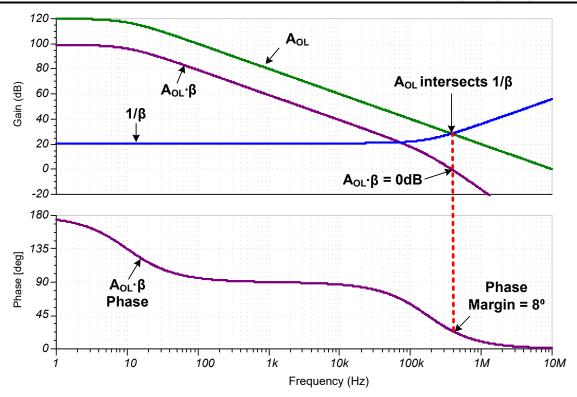

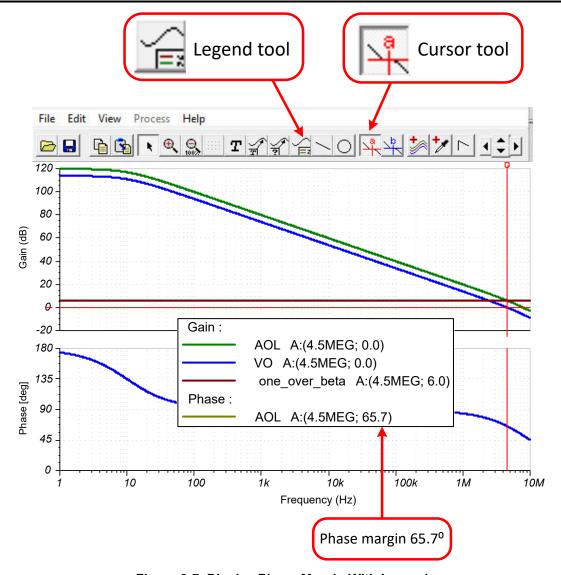

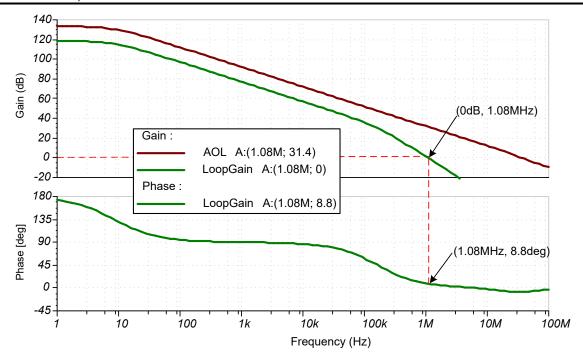

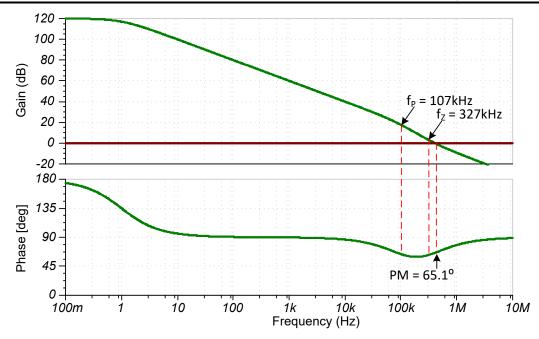

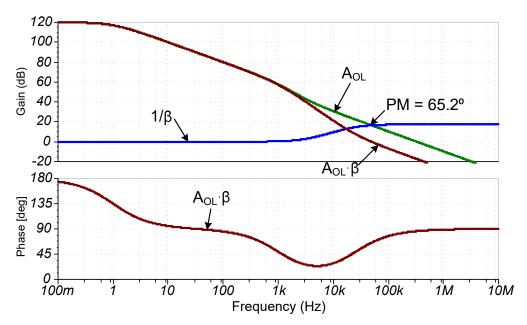

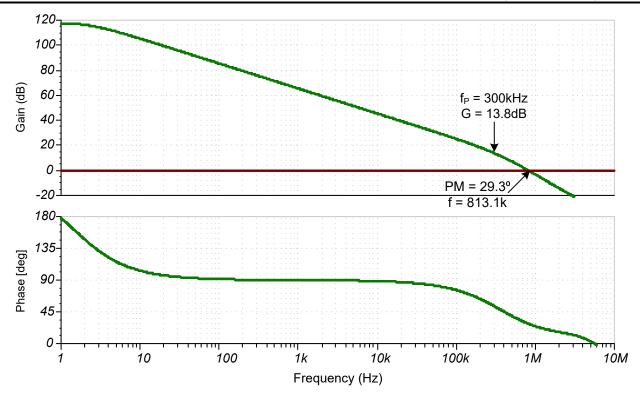

When looking at open-loop gain and phase plots, engineers can find the phase margin by looking at the loop-gain phase at the frequency where  $1/\beta$  intersects with  $A_{OL}$ . Alternatively, the phase margin can also be found at the frequency where the loop-gain magnitude is 0dB ( $A_{OL} \times \beta(dB) = 0dB$ ). For most amplifiers, the DC loop-gain phase is 180°, so the phase margin is directly read from the graph. In Figure 2-8, the phase starts at 180° and drops to 8° when  $A_{OL} \times \beta(dB) = 0dB$ , so the phase margin is 8°.

Figure 2-8. Phase Margin Definition

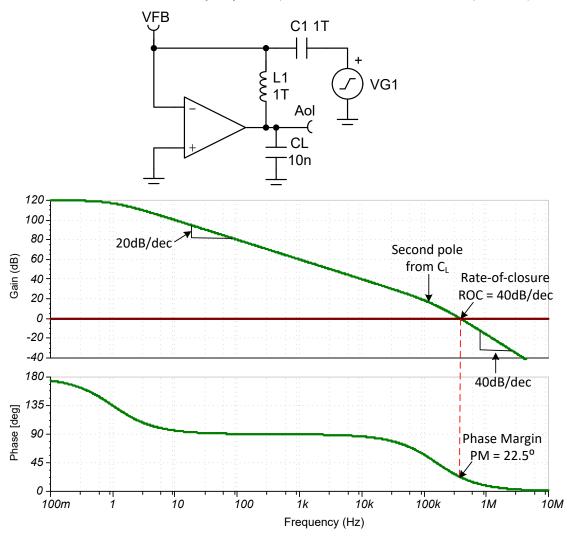

## 2.4 Graphing Loop-Gain Based on $A_{OL}$ and $1/\beta$

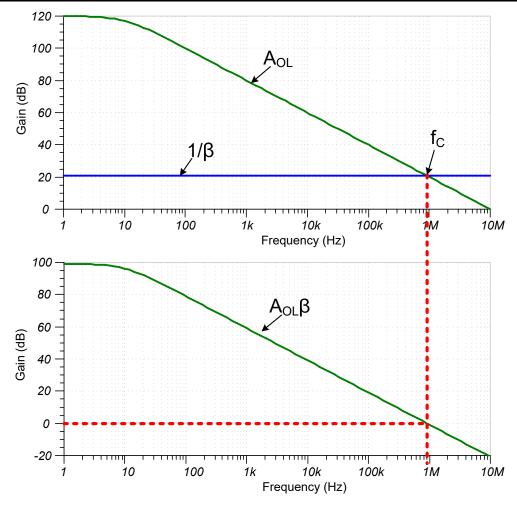

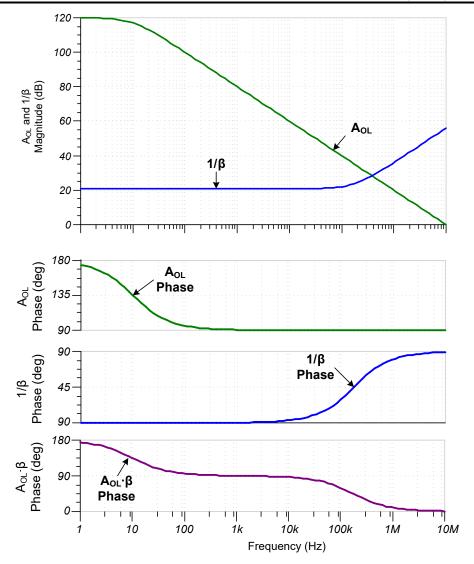

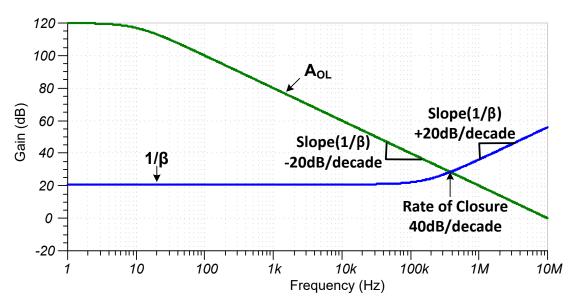

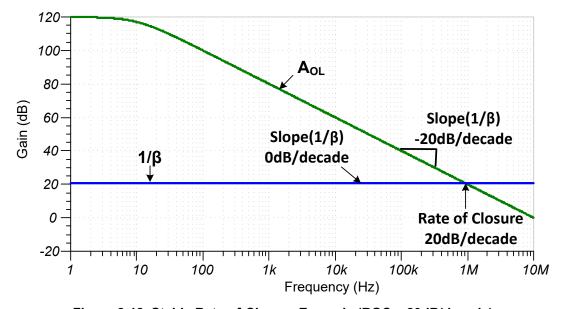

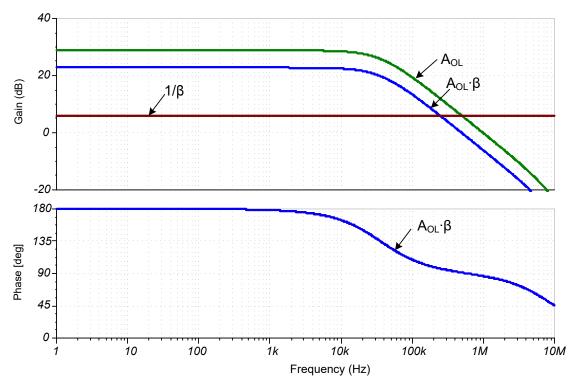

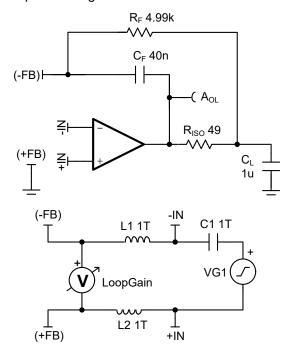

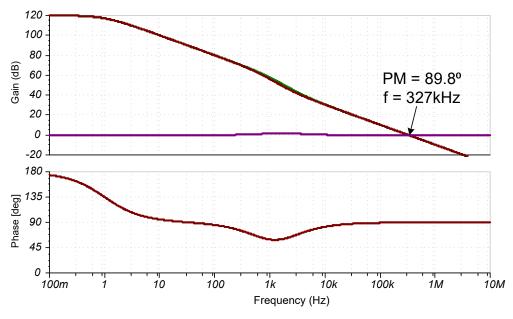

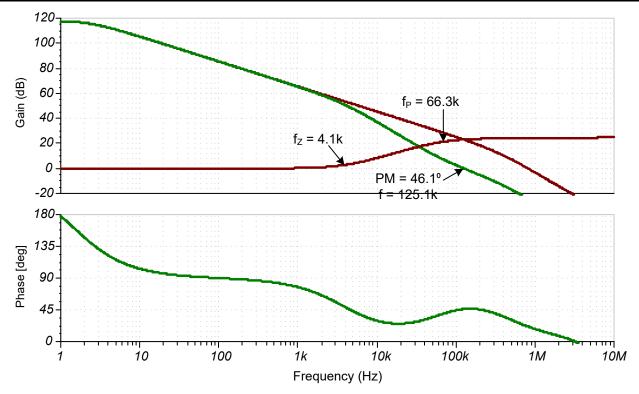

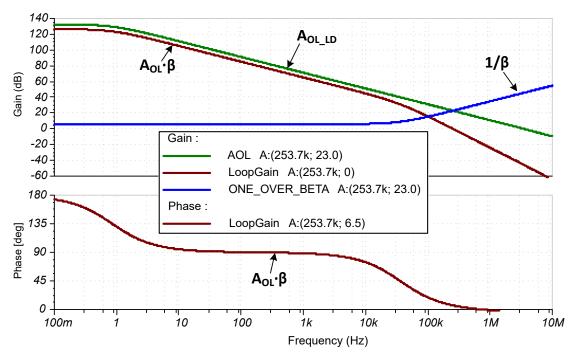

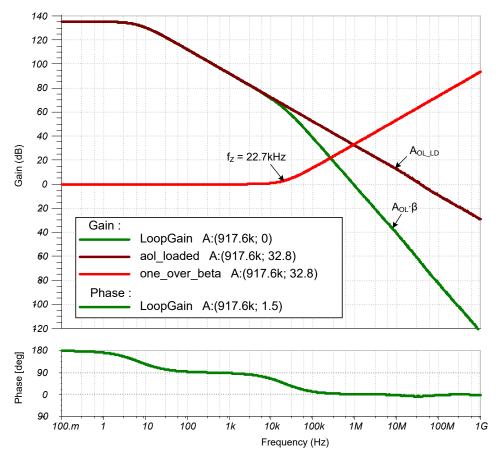

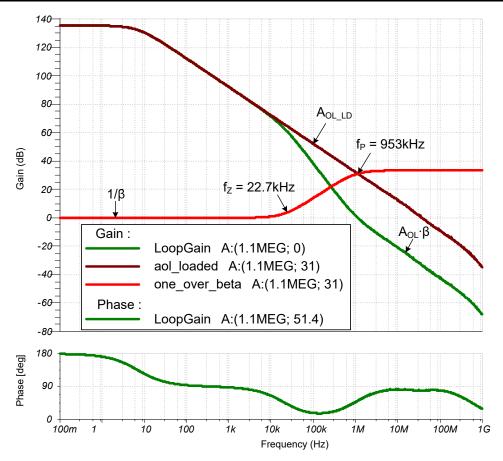

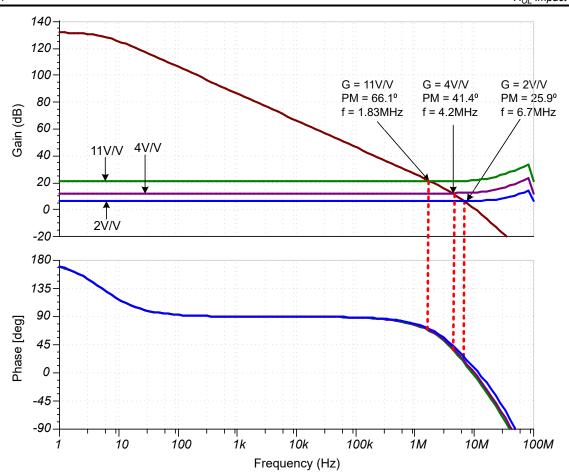

The  $A_{OL}$  curve is specified in the op amp datasheet and the  $1/\beta$  curve can be approximated as the closed-loop gain of the amplifier. The loop-gain  $(A_{OL} \times \beta)$  curve can be derived by subtracting the  $1/\beta$  curve from the  $A_{OL}$  curve. The mathematical proof that allows for the loop-gain calculation uses the laws of logarithms (see Equation 13 and Equation 14). The logarithmic laws apply since our magnitude plots are normally given in decibels, and decibels are logarithmic. Applying the logarithm laws to loop gain shows that loop-gain can be calculated as  $A_{OL}(dB) - 1/\beta(dB)$ , see Equation 15 and Equation 16. Figure 2-9 provides a graphic example for the loop gain calculation. At low frequency,  $A_{OL}$  is 120dB and  $1/\beta$  is 20dB, so by the calculation:  $A_{OL} \times \beta(dB) = A_{OL}(dB) - 1/\beta(dB) = 120dB - 20dB = 100dB$ . For the frequency where  $A_{OL} = 1/\beta$ , the loop-gain is 0dB as expected ( $A_{OL} \times \beta(dB) = A_{OL}(dB) - 1/\beta(dB) = 20dB - 20dB = 0dB$ ). The same approach can be followed for loop gain phase (see Figure 2-10).

$$\log(A \times B) = \log(A) + \log(B) \tag{13}$$

$$\log(A) = -\log\left(\frac{1}{A}\right) \tag{14}$$

$$20\log(A_{OL}\beta) = 20\log(A_{OL}) - 20\log\left(\frac{1}{\beta}\right)$$

(15)

$$A_{OL}\beta(dB) = A_{OL}\left(dB\right) - \frac{1}{\beta}\left(dB\right) \tag{16}$$