SNAS304H January 2006 – April 2016 ADC121S101 , ADC121S101-Q1

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

Orderable Information

8 Detailed Description

8.1 Overview

The ADC121S101 is a successive-approximation analog-to-digital converter designed around a charge-redistribution digital-to-analog converter core. Simplified schematics of the ADC121S101 in both track and hold modes are shown in Figure 16 and Figure 17, respectively. In Figure 16, the device is in track mode: switch SW1 connects the sampling capacitor to the input, and SW2 balances the comparator inputs. The device is in this state until CS is brought low, at which point the device moves to hold mode.

Figure 17 shows the device in hold mode: switch SW1 connects the sampling capacitor to ground, maintaining the sampled voltage, and switch SW2 unbalances the comparator. The control logic then instructs the charge-redistribution DAC to add or subtract fixed amounts of charge from the sampling capacitor until the comparator is balanced. When the comparator is balanced, the digital word supplied to the DAC is the digital representation of the analog input voltage. The device moves from hold mode to track mode on the 13th rising edge of SCLK.

Figure 16. ADC121S101 in Track Mode

Figure 16. ADC121S101 in Track Mode

Figure 17. ADC121S101 in Hold Mode

Figure 17. ADC121S101 in Hold Mode

8.2 Functional Block Diagram

8.3 Feature Description

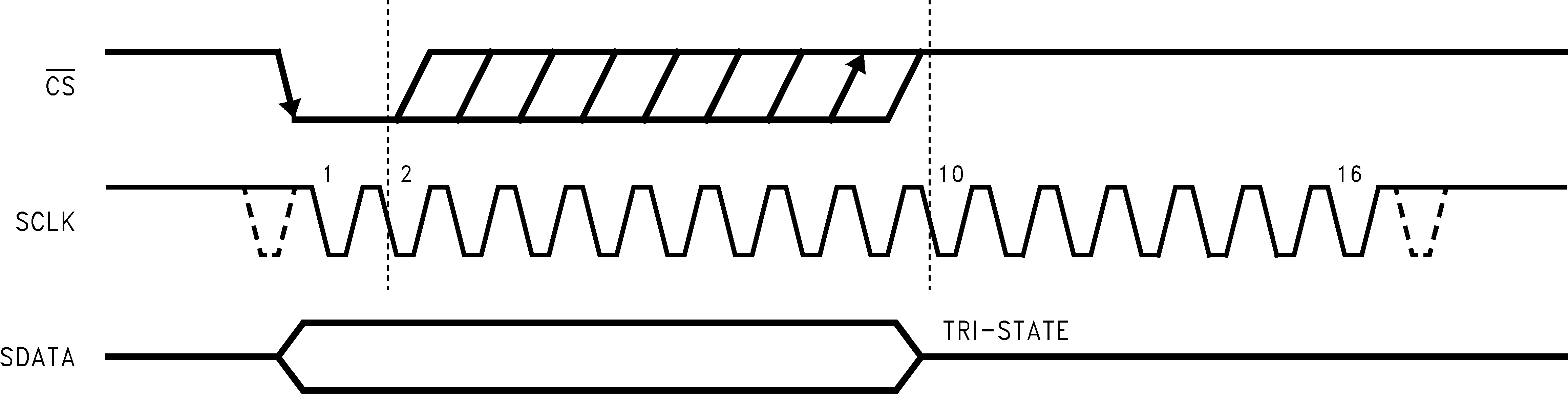

See the Functional Block Diagram for the serial interface timing diagram for the ADC. CS is chip select, which initiates conversions on the ADC and frames the serial data transfers. SCLK (serial clock) controls both the conversion process and the timing of serial data. SDATA is the serial data out pin, where a conversion result is found as a serial data stream.

Basic operation of the ADC begins with CS going low, which initiates a conversion process and data transfer. Subsequent rising and falling edges of SCLK are labelled with reference to the falling edge of CS; for example, the third falling edge of SCLK shall refer to the third falling edge of SCLK after CS goes low.

At the fall of CS, the SDATA pin comes out of TRI-STATE, and the converter moves from track mode to hold mode. The input signal is sampled and held for conversion on the falling edge of CS. The converter moves from hold mode to track mode on the 13th rising edge of SCLK (see Figure 2). The interval for the tACQ specification begins at this point. At least 350 ns must pass between the 13th rising edge of SCLK and the next falling edge of CS. The SDATA pin is placed back into TRI-STATE after the 16th falling edge of SCLK, or at the rising edge of CS, whichever occurs first. After a conversion is completed, the quiet time tQUIET must be satisfied before bringing CS low again to begin another conversion.

Sixteen SCLK cycles are required to read a complete sample from the ADC. The sample bits (including leading zeroes) are clocked out on falling edges of SCLK, and are intended to be clocked in by a receiver on subsequent falling edges of SCLK. The ADC produces three leading zero bits on SDATA, followed by twelve data bits, most significant first.

If CS goes low before the rising edge of SCLK, an additional (fourth) zero bit may be captured by the next falling edge of SCLK.

8.3.1 Determining Throughput

Throughput depends on the frequency of SCLK and how much time is allowed to elapse between the end of one conversion and the start of another. At the maximum specified SCLK frequency, the maximum guaranteed throughput is obtained by using a 20-SCLK frame. As shown in Figure 2, the minimum allowed time between CS falling edges is determined by 1) 12.5 SCLKs for Hold mode, 2) the larger of two quantities: either the minimum required time for Track mode (tACQ) or 2.5 SCLKs to finish reading the result and 3) 0, 1/2 or 1 SCLK padding to ensure an even number of SCLK cycles so there is a falling SCLK edge when CS next falls.

For example, at the fastest rate for this family of parts, SCLK is 20MHz and 2.5 SCLKs are 125 ns, so calculate the minimum time between CS falling edges using Equation 1.

(12.5 SCLKs + tACQ + 1/2 SCLK) which corresponds to a maximum throughput of 1 MSPS. At the slowest rate for this family, SCLK is 1 MHz. Using a 20 cycle conversion frame as shown in Figure 2 yields a 20-µs time between CS falling edges for a throughput of 50 KSPS.

It is possible, however, to use fewer than 20 clock cycles provided the timing parameters are met. With a

1-MHz SCLK, there are 2500 ns in 2.5-SCLK cycles, which is greater than tACQ. After the last data bit has come out, the clock requires one full cycle to return to a falling edge. Thus the total time between falling edges of CS is

12.5 × 1 µs + 2.5 × 1 µs + 1 × 1 µs = 16 µs, which is a throughput of 62.5 KSPS.

8.3.2 ADC Transfer Function

The output format of the ADC is straight binary. Code transitions occur midway between successive integer LSB values. The LSB width for the ADC is VA/4096. Figure 18 shows the ideal transfer characteristic. The transition from an output code of 0000 0000 0000 to a code of 0000 0000 0001 is at 1/2 LSB, or a voltage of VA/8192. Other code transitions occur at steps of one LSB.

Figure 18. Ideal Transfer Characteristic

Figure 18. Ideal Transfer Characteristic

8.3.3 Analog Inputs

Figure 19 shows an equivalent circuit for the ADC's input. Diodes D1 and D2 provide ESD protection for the analog inputs. At no time must the analog input go beyond (VA + 300 mV) or (GND − 300 mV), as these ESD diodes will begin conducting, which could result in erratic operation. For this reason, the ESD diodes must not be used to clamp the input signal.

The capacitor C1 in Figure 19 has a typical value of 4 pF, and is mainly the package pin capacitance. Resistor R1 is the on resistance of the track or hold switch, and is typically 500 Ω. Capacitor C2 is the ADC sampling capacitor and is typically 26 pF. The ADC delivers the best performance when driven by a low-impedance source to eliminate distortion caused by the charging of the sampling capacitance. This is especially important when using the ADC to sample AC signals. Also important when sampling dynamic signals is an anti-aliasing filter.

Figure 19. Equivalent Input Circuit

Figure 19. Equivalent Input Circuit

8.3.4 Digital Inputs and Outputs

The ADC digital inputs (SCLK and CS) are not limited by the same maximum ratings as the analog inputs. The digital input pins are instead limited to 5.25 V with respect to GND, regardless of VA, the supply voltage. This allows the ADC to be interfaced with a wide range of logic levels, independent of the supply voltage.

8.4 Device Functional Modes

The ADC has two possible modes of operation: normal mode, and shutdown mode. The ADC enters normal mode (and a conversion process is begun) when CS is pulled low. The device enters shutdown mode if CS is pulled high before the tenth falling edge of SCLK after CS is pulled low, or stays in normal mode if CS remains low. Once in shutdown mode, the device stays there until CS is brought low again. By varying the ratio of time spent in the normal and shutdown modes, a system may trade off throughput for power consumption, with a sample rate as low as zero.

8.4.1 Normal Mode

The fastest possible throughput is obtained by leaving the ADC in normal mode at all times, so there are no power-up delays. To keep the device in normal mode continuously, CS must be kept low until after the 10th falling edge of SCLK after the start of a conversion (remember that a conversion is initiated by bringing CS low).

If CS is brought high after the 10th falling edge, but before the 16th falling edge, the device will remain in normal mode, but the current conversion will be aborted, and SDATA will return to TRI-STATE (truncating the output word).

Sixteen SCLK cycles are required to read all of a conversion word from the device. After sixteen SCLK cycles have elapsed, CS may be idled either high or low until the next conversion. If CS is idled low, it must be brought high again before the start of the next conversion, which begins when CS is again brought low.

After sixteen SCLK cycles, SDATA returns to TRI-STATE. Another conversion may be started, after tQUIET has elapsed, by bringing CS low again.

8.4.2 Shutdown Mode

Shutdown mode is appropriate for applications that either do not sample continuously, or it is acceptable to trade throughput for power consumption. When the ADC is in shutdown mode, all of the analog circuitry is turned off.

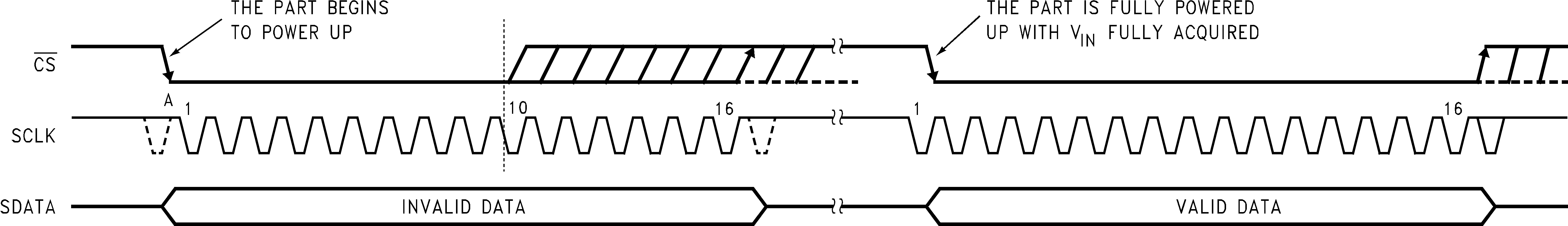

To enter shutdown mode, a conversion must be interrupted by bringing CS high anytime between the second and tenth falling edges of SCLK, as shown in Figure 20. Once CS has been brought high in this manner, the device will enter shutdown mode; the current conversion will be aborted and SDATA will enter TRI-STATE. If CS is brought high before the second falling edge of SCLK, the device will not change mode; this is to avoid accidentally changing mode as a result of noise on the CS line.

Figure 20. Entering Shutdown Mode

Figure 20. Entering Shutdown Mode

Figure 21. Entering Normal Mode

Figure 21. Entering Normal Mode

To exit shutdown mode, bring CS back low. Upon bringing CS low, the ADC begins powering up (see Timing Requirements for power-up time specifications). This power-up delay results in the first conversion result being unusable. The second conversion performed after power up, however, is valid, as shown in Figure 21.

If CS is brought back high before the 10th falling edge of SCLK, the device returns to shutdown mode. This is done to avoid accidentally entering normal mode as a result of noise on the CS line. To exit shutdown mode and remain in normal mode, CS must be kept low until after the 10th falling edge of SCLK. The ADC is fully powered up after 16 SCLK cycles.