SNLS325D May 2010 – December 2016 DS92LV0421 , DS92LV0422

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics: Serializer DC

- 6.6 Electrical Characteristics: Deserializer DC

- 6.7 Electrical Characteristics: DC and AC Serial Control Bus

- 6.8 Timing Requirements: Serial Control Bus

- 6.9 Switching Characteristics: Serializer

- 6.10 Switching Characteristics: Deserializer

- 6.11 Typical Characteristics

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagrams

- 7.3

Feature Description

- 7.3.1 Parallel LVDS Data Transfer (Color Bit Mapping Select)

- 7.3.2 Serial Data Transfer

- 7.3.3 Video Control Signal Filter

- 7.3.4 Serializer Functional Description

- 7.3.5

Deserializer Functional Description

- 7.3.5.1 Signal Quality Enhancers

- 7.3.5.2 EMI Reduction Features

- 7.3.5.3 Deserializer Clock-Data Recovery Status Flag (LOCK), Output Enable (OEN), and Output State Select (OSS_SEL)

- 7.3.5.4 Deserializer Oscillator Output (Optional)

- 7.3.6 Built-In Self Test (BIST)

- 7.3.7 Optional Serial Bus Control

- 7.4 Device Functional Modes

- 7.5 Register Maps

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- NJK|36

Thermal pad, mechanical data (Package|Pins)

Orderable Information

10 Layout

10.1 Layout Guidelines

Circuit board layout and stack-up for the LVDS serializer and deserializer devices must be designed to provide low-noise power feed to the device. Good layout practice also separates high frequency or high-level inputs and outputs to minimize unwanted stray noise pickup, feedback, and interference. Power system performance may be greatly improved by using thin dielectrics (2 to 4 mils) for power or ground sandwiches. This arrangement provides plane capacitance for the PCB power system with low-inductance parasitics, which has proven especially effective at high frequencies and makes the value and placement of external bypass capacitors less critical. External bypass capacitors must include both RF ceramic and tantalum electrolytic types. RF capacitors may use values in the range of 0.01 µF to 0.1 µF. Tantalum capacitors may be in the 2.2-µF to 10-µF range. Voltage rating of the tantalum capacitors must be at least 5x the power supply voltage being used.

Surface-mount capacitors are recommended due to their smaller parasitics. When using multiple capacitors per supply pin, place the smaller value closer to the pin. A large bulk capacitor is recommended at the point of power entry. This is typically in the 50-µF to 100-µF range and smooths low frequency switching noise. TI recommends connecting power and ground pins directly to the power and ground planes with bypass capacitors connected to the plane, with vias on both ends of the capacitor. Connecting power or ground pins to an external bypass capacitor increases the inductance of the path.

A small body size X7R chip capacitor, such as 0603, is recommended for external bypass. Its small body size reduces the parasitic inductance of the capacitor. The user must pay attention to the resonance frequency of these external bypass capacitors, usually in the range of 20 to 30 MHz. To provide effective bypassing, multiple capacitors are often used to achieve low impedance between the supply rails over the frequency of interest. At high frequency, it is also a common practice to use two vias from power and ground pins to the planes, reducing the impedance at high frequency.

Some devices provide separate power and ground pins for different portions of the circuit. This is done to isolate switching noise effects between different sections of the circuit. Separate planes on the PCB are typically not required. Pin description tables typically provide guidance on which circuit blocks are connected to which power pin pairs. In some cases, an external filter may be used to provide clean power to sensitive circuits such as PLLs.

Use at least a four-layer board with a power and ground plane. Place LVCMOS signals away from the CML lines to prevent coupling from the LVCMOS lines to the CML lines. Closely-coupled differential lines of 100 Ω are typically recommended for LVDS interconnects. The closely coupled lines help to ensure that coupled noise appears as common mode and thus is rejected by the receivers. The tightly coupled lines also radiate less.

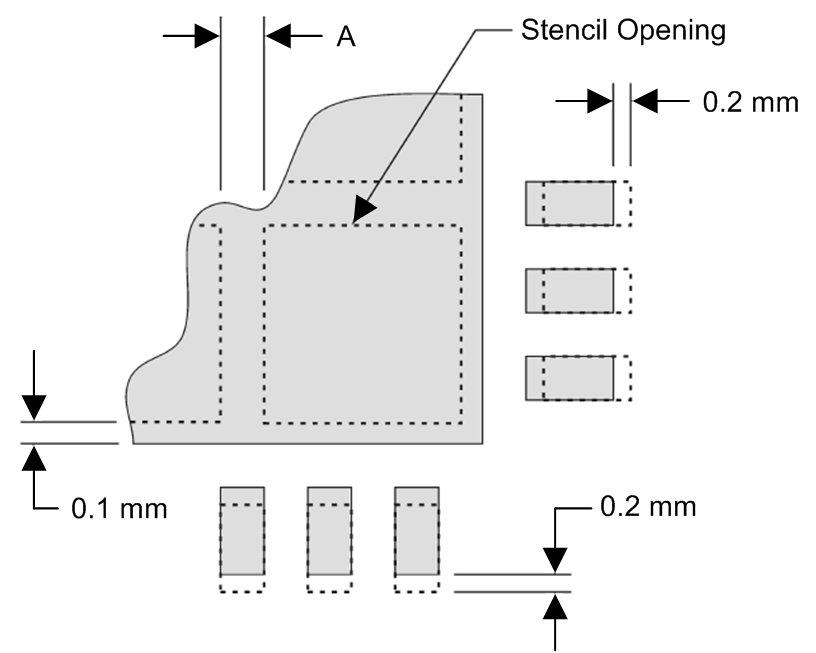

10.1.1 WQFN (LLP) Stencil Guidelines

Stencil parameters such as aperture area ratio and the fabrication process have a significant impact on paste deposition. Inspection of the stencil prior to placement of the LLP (WQFN) package is highly recommended to improve board assembly yields. If the via and aperture openings are not carefully monitored, the solder may flow unevenly through the DAP. Stencil parameters for aperture opening and via locations are shown in Figure 42 and Figure 43.

Figure 42. No Pullback LLP, Single Row Reference Diagram

Figure 42. No Pullback LLP, Single Row Reference Diagram

Table 18. No Pullback LLP Stencil Aperture Summary for DS92LV0421 and DS92LV0422

| DEVICE | PIN COUNT | MKT DWG | PCB I/O PAD SIZE (mm) | PCB PITCH (mm) | PCB DAP SIZE (mm) | STENCIL I/O APERTURE (mm) | STENCIL DAP APERTURE (mm) | NUMBER OF DAP APERTURE OPENINGS | GAP BETWEEN DAP APERTURE (Dim A mm) |

|---|---|---|---|---|---|---|---|---|---|

| DS92LV0421 | 36 | SQA36A | 0.25 × 0.6 | 0.5 | 4.6 x 4.6 | 0.25 × 0.7 | 1.0 × 1.0 | 16 | 0.2 |

| DS92LV0422 | 48 | SQA48A | 0.25 × 0.6 | 0.5 | 5.1 × 5.1 | 0.25 × 0.7 | 1.1 × 1.1 | 16 | 0.2 |

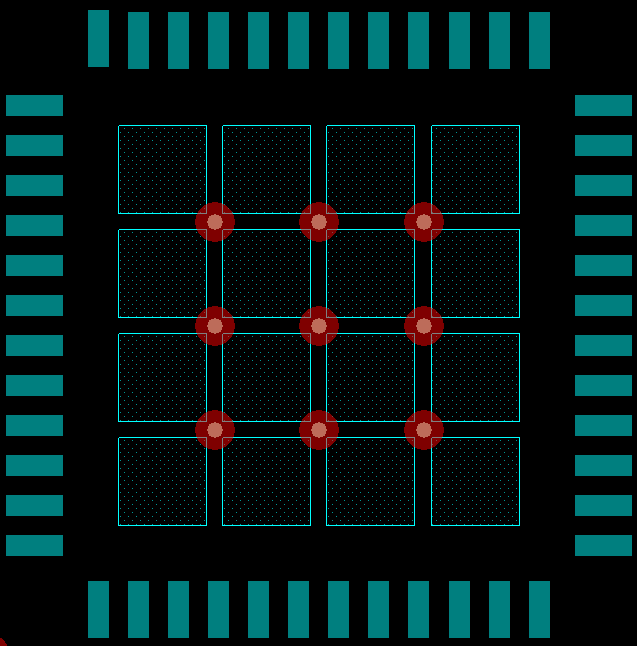

Figure 43. 48-Pin WQFN Stencil Example of Via and Opening Placement

Figure 43. 48-Pin WQFN Stencil Example of Via and Opening Placement

Information on the WQFN style package is provided in Leadless Leadframe Package (LLP) Application Report (SNOA401).

10.1.2 Transmission Media

The serializer and deserializer chipset is intended to be used in a point-to-point configuration through a PCB trace or through twisted pair cable. The serializer and deserializer provide internal terminations for a clean signaling environment. The interconnect for LVDS must present a differential impedance of 100 Ω. Use cables and connectors that have matched differential impedance to minimize impedance discontinuities. Shielded or un-shielded cables may be used depending upon the noise environment and application requirements.

10.1.3 LVDS Interconnect Guidelines

See AN-1108 Channel-Link PCB and Interconnect Design-In Guidelines (SNLA008) and AN-905 Transmission Line RAPIDESIGNER Operation and Applications Guide (SNLA035) for full details.

- Use 100-Ω coupled differential pairs

- Use the S, 2S, 3S rule in spacings

- S = space between the pair

- 2S = space between pairs

- 3S = space to LVCMOS signal

- Minimize the number of vias

- Use differential connectors when operating above 500-Mbps line speed

- Maintain balance of the traces

- Minimize skew within the pair

- Terminate as close to the Tx outputs and Rx inputs as possible

Additional general guidance can be found in the LVDS Owner's Manual, available in PDF format from the TI website at: www.ti.com/lvds.

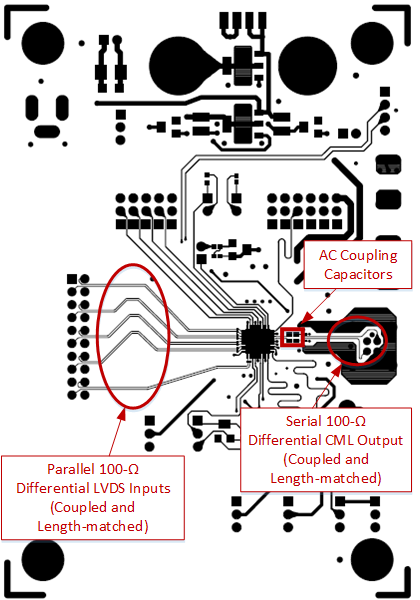

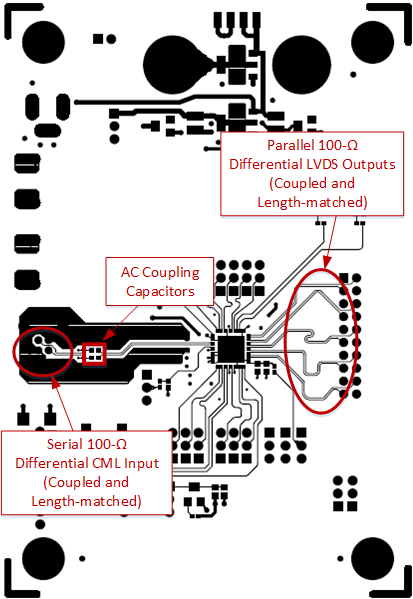

10.2 Layout Example

The following PCB layout examples are derived from the layout design of the LV04EVK01 Evaluation Module. These graphics and additional layout description are used to demonstrate both proper routing and proper solder techniques when designing in the serializer and deserializer pair.

Figure 44. DS92LV0421 Serializer Example Layout

Figure 44. DS92LV0421 Serializer Example Layout

Figure 45. DS92LV0422 Deserializer Example Layout

Figure 45. DS92LV0422 Deserializer Example Layout