SLLSEI2A September 2017 – December 2017 SN55HVD233-SP

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (continued)

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Driver Electrical Characteristics

- 7.6 Receiver Electrical Characteristics

- 7.7 Driver Switching Characteristics

- 7.8 Receiver Switching Characteristics

- 7.9 Device Switching Characteristics

- 7.10 Typical Characteristics

- 8 Parameter Measurement Information

- 9 Detailed Description

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- HKX|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

10 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

10.1 Application Information

10.1.1 Diagnostic Loopback

The diagnostic loopback or internal loopback function of the SN55HVD233-SP is enabled with a high-level input on pin 7, LBK. This mode disables the driver output while keeping the bus pins biased to the recessive state. This mode also redirects the D data input (transmit data) through logic to the received data output (R), thus creating an internal loopback of the transmit-to-receive data path. This mimics the loopback that occurs normally with a CAN transceiver because the receiver loops back the driven output to the R (receive data) pin. This mode allows the host microprocessor to input and read back a bit sequence or CAN messages to perform diagnostic routines without disturbing the CAN bus. Figure 33 shows a typical CAN bus application.

If the LBK pin is not used, it may be tied to ground (GND). However, it is pulled low internally (defaults to a low-level input) and may be left open if not in use.

Figure 28. Equivalent Input and Output Schematic Diagrams

Figure 28. Equivalent Input and Output Schematic Diagrams

10.2 Typical Application

Figure 29. Typical Application Schematic

Figure 29. Typical Application Schematic

10.2.1 Design Requirements

The High-Speed ISO 11898 Standard specifications are given for a maximum signaling rate of 1 Mbps with a bus length of 40 m and a maximum of 30 nodes. It also recommends a maximum unterminated stub length of 0.3 m. The cable is specified to be a shielded or unshielded twisted-pair with a 120-Ω characteristic impedance (ZO). The standard defines a single line of twisted-pair cable with the network topology as shown in Figure 29. It is terminated at both ends with 120-Ω resistors, which match the characteristic impedance of the line to prevent signal reflections. According to ISO 11898, placing RL on a node should be avoided because the bus lines lose termination if the node is disconnected from the bus.

10.2.2 Detailed Design Procedure

Table 5. Suggested Cable Length vs Signaling Rate

| BUS LENGTH (m) | SIGNALING RATE (Mbps) |

|---|---|

| 40 | 1 |

| 100 | 0.5 |

| 200 | 0.25 |

| 500 | 0.1 |

| 1000 | 0.05 |

Basically, the maximum bus length is determined by, or rather is a trade-off with the selected signaling rate as listed in Table 5.

A signaling rate decreases as transmission distance increases. While steady-state losses may become a factor at the longest transmission distances, the major factors limiting signaling rate as distance is increased are time varying. Cable bandwidth limitations, which degrade the signal transition time and introduce inter-symbol interference (ISI), are primary factors reducing the achievable signaling rate when transmission distance is increased.

For a CAN bus, the signaling rate is also determined from the total system delay – down and back between the two most distant nodes of a system and the sum of the delays into and out of the nodes on a bus with the typical 5 ns/m prop delay of a twisted-pair cable. Also, consideration must be given the signal amplitude loss due to resistance of the cable and the input resistance of the transceivers. Under strict analysis, skin effects, proximity to other circuitry, dielectric loss, and radiation loss effects all act to influence the primary line parameters and degrade the signal.

A conservative rule of thumb for bus lengths over 100 m is derived from the product of the signaling rate in Mbps and the bus length in meters, which should be less than or equal to 50.

Signaling Rate (Mbps) × Bus Length (m) ≤ 50. Operation at extreme temperatures should employ additional conservatism.

10.2.2.1 Slope Control

Adjust the rise and fall slope of the SN55HVD233-SP driver output by connecting a resistor from the RS (pin 8) to ground (GND), or to a low-level input voltage as shown in Figure 30.

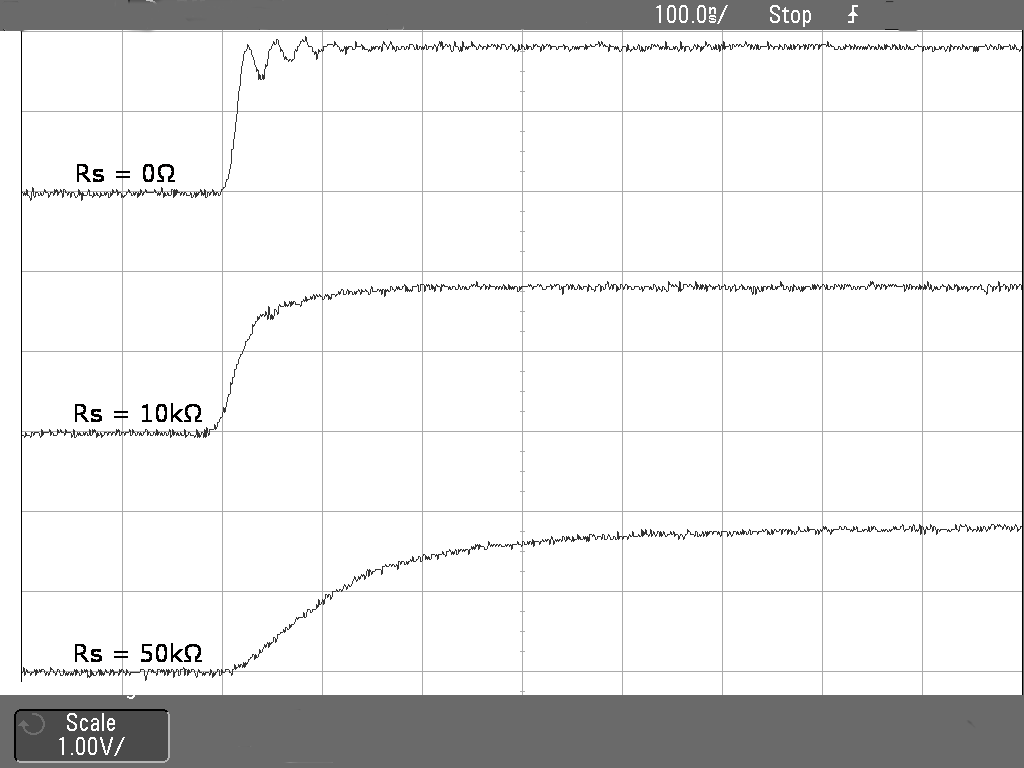

The slope of the driver output signal is proportional to the pin's output current. This slope control is implemented with an external resistor value ranging from 0 Ω to achieve a ≈38 V/μs single ended slew rate, and up to 50 kΩ to achieve a ≈4 V/μs slew rate as displayed in Figure 31. Figure 32 shows typical driver output waveforms with slope control.

Figure 30. Slope Control/Standby Connection to a DSP

Figure 30. Slope Control/Standby Connection to a DSP

10.2.2.2 Standby

If a high-level input (> 0.75 VCC) is applied to RS (pin 8), the circuit enters a low-current, listen-only standby mode during which the driver is switched off and the receiver remains active. The local controller can reverse this low-power standby mode when the rising edge of a dominant state (bus differential voltage > 900-mV typical) occurs on the bus.

10.2.3 Application Curves