SLUSAP2J March 2012 – November 2021 UCD3138

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Functional Block Diagram

- 5 Revision History

- 6 Device Comparison Table

- 7 Pin Configuration and Functions

- 8 Specifications

-

9 Detailed Description

- 9.1 Overview

- 9.2 ARM Processor

- 9.3 Memory

- 9.4 System Module

- 9.5

Feature Description

- 9.5.1 Sync FET Ramp and IDE Calculation

- 9.5.2 Automatic Mode Switching

- 9.5.3 DPWMC, Edge Generation, IntraMux

- 9.5.4 Filter

- 9.5.5 Communication Ports

- 9.5.6 Miscellaneous Analog

- 9.5.7 Package ID Information

- 9.5.8 Brownout

- 9.5.9 Global I/O

- 9.5.10 Temperature Sensor Control

- 9.5.11 I/O Mux Control

- 9.5.12 Current Sharing Control

- 9.5.13 Temperature Reference

- 9.6 Device Functional Modes

-

10Application and Implementation

- 10.1 Application Information

- 10.2

Typical Application

- 10.2.1 Design Requirements

- 10.2.2 Detailed Design Procedure

- 10.2.3 Application Curves

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical Packaging and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

Orderable Information

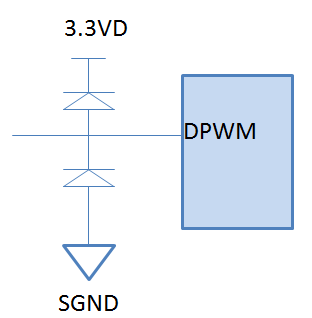

12.1.4.4 DPWM PINS

If DPWMs travel for a longer distance than 3 inches from the control card to a main power stage, a Schottky clamping diode may be needed as shown in Figure 12-4to prevent electrical overstress on the device during lightning test. The long trace may also pick up the noise from other switching sources. Avoid DPWM signals to cross switching nodes.

Figure 12-4 Clamping Diodes for DPWM

Figure 12-4 Clamping Diodes for DPWM