JAJSDZ2B October 2017 – October 2021 CSD25501F3

PRODUCTION DATA

- 1特長

- 2アプリケーション

- 3概要

- 4Revision History

- 5Specifications

- 6Device and Documentation Support

- 7Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- YJN|3

サーマルパッド・メカニカル・データ

発注情報

3 概要

この -20V、64mΩ、P チャネル FemtoFET™ MOSFET は、多くのハンドヘルドおよびモバイル・アプリケーションのフットプリントを最小化するように設計され、最適化されています。標準の小信号 MOSFET をこのテクノロジに置き換えて、フットプリントを大幅に減らすことができます。内蔵の 10kΩ クランプ抵抗 (RC) により、デューティ・サイクルに応じて、ゲート電圧 (VGS) を最大内部ゲート酸化膜値の -6V より高くして動作できます。VGS が -6V を超えて上昇すると、ダイオードを経由するゲートのリーク電流 (IGSS) が増加します。

製品概要

| TA = 25°C | 標準値 | 単位 | ||

|---|---|---|---|---|

| VDS | ドレイン-ソース間電圧 | -20 | V | |

| Qg | ゲートの合計電荷 (-4.5V) | 1.02 | nC | |

| Qgd | ゲート電荷、ゲート - ドレイン間 | 0.09 | nC | |

| RDS(on) | ドレイン-ソース間 オン抵抗 |

VGS = -1.8V | 120 | mΩ |

| VGS = -2.5V | 86 | |||

| VGS = -4.5V | 64 | |||

| VGS(th) | スレッショルド電圧 | -0.75 | V | |

製品情報

| デバイス(1) | 数量 | メディア | パッケージ | 出荷 |

|---|---|---|---|---|

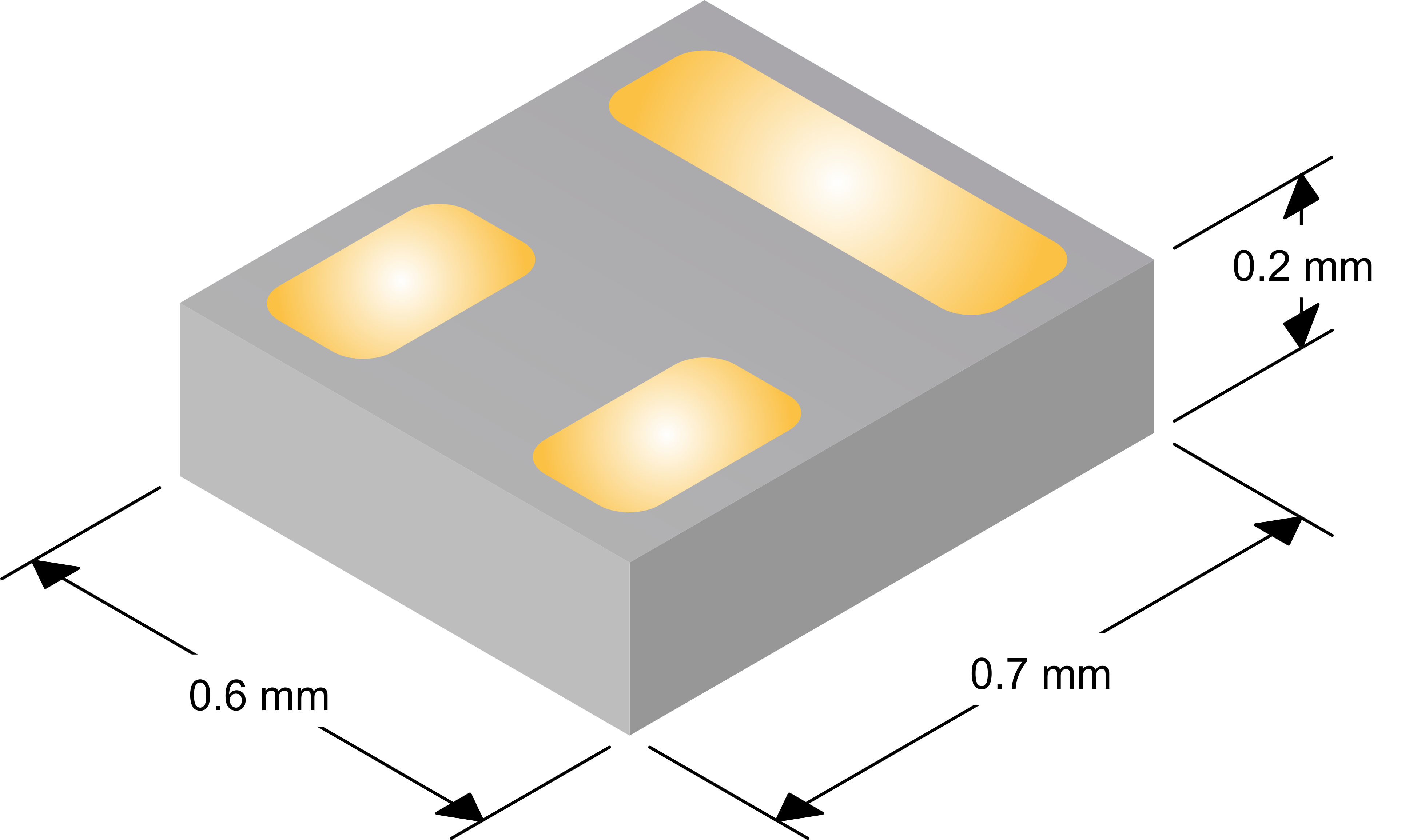

| CSD25501F3 | 3000 | 7インチ・リール | Femto 0.73mm × 0.64mm LGA (Land Grid Array) |

テープ および リール |

| CSD25501F3T | 250 |

(1) 提供されているすべてのパッケージについては、巻末の注文情報を参照してください。

絶対最大定格

| TA = 25℃ (特に記述のない限り) | 値 | 単位 | |

|---|---|---|---|

| VDS | ドレイン-ソース間電圧 | -20 | V |

| VGS | ゲート - ソース間電圧 | -20 | V |

| ID | 連続ドレイン電流(1) | -3.6 | A |

| IDM | パルス・ドレイン電流(1)(2) | -13.6 | A |

| PD | 消費電力(1) | 500 | mW |

| V(ESD) | 人体モデル (HBM) | 4000 | V |

| 荷電デバイス・モデル (CDM) | 2000 | ||

| TJ、 Tstg |

動作時の接合部、 保管温度 |

-55~150 | ℃ |

(1) 最小の Cu 取り付け領域を持つ FR4 材質上に実装され、RθJA = 255℃/W (標準値) の場合

(2) パルス幅 ≤ 100μs、デューティサイクル ≤ 1%

標準的な部品寸法

標準的な部品寸法 上面図

上面図