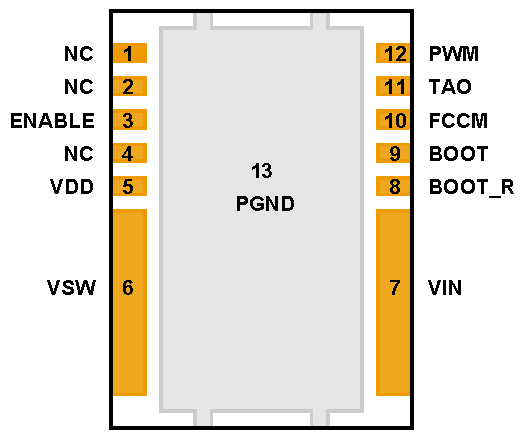

| NC |

1, 2, 4 |

No connect, must leave floating. |

| ENABLE |

3 |

Enables device operation. If ENABLE = logic HIGH, turns on device. If ENABLE = logic LOW, the device is turned off and both MOSFET gates are actively pulled low. An internal 100 kΩ pull down resistor will pull the ENABLE pin LOW if left floating. |

| VDD |

5 |

Supply Voltage to Gate Driver and internal circuitry. |

| VSW |

6 |

Phase node connecting the HS MOSFET Source and LS MOSFET Drain - pin connection to the output inductor. |

| VIN |

7 |

Input Voltage Pin. Connect input capacitors close to this pin. |

| BOOT_R |

8 |

Return path for HS gate driver, connected to VSW internally. |

| BOOT |

9 |

Bootstrap capacitor connection. Connect a minimum of 0.1 µF 16 V X7R, ceramic capacitor from BOOT to BOOT_R pins. The bootstrap capacitor provides the charge to turn on the Control FET. The bootstrap diode is integrated. |

| FCCM |

10 |

This pin enables the Diode Emulation function. When this pin is held LOW, Diode Emulation Mode is enabled for Sync FET. When FCCM is HIGH, the device operated in Forced Continuous Conduction Mode. An internal 5µA current source will pull the FCCM pin to VDD if left floating. |

TAO/

FAULT |

11 |

Temperature amplifier output. Reports a voltage proportional to the die temperature. An ORing diode is integrated in the IC. When used in multiphase application, a single wire can be used to connect the TAO pins of all the IC's. Only the highest temperature will be reported. TAO will be pulled up to 3.3 V if Thermal Shutdown occurs. TAO should be bypassed to PGND with a 1nF 16V X7R ceramic capacitor. |

| PWM |

12 |

Pulse-width modulated Tri-state input from external controller. Logic LOW sets Control FET gate low and Sync FET gate high. Logic HIGH sets Control FET gate high and Sync FET gate low. Open or High Z sets both MOSFET gates low if greater than the Tri-State Shutdown Hold-off Time (t3HT). |

| PGND |

13 |

Power ground. |