JAJSD17B August 2015 – July 2016 DRV8871

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11デバイスおよびドキュメントのサポート

- 12メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- DDA|8

サーマルパッド・メカニカル・データ

- DDA|8

発注情報

8 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

8.1 Application Information

The DRV8871 device is typically used to drive one brushed DC motor.

8.2 Typical Application

Figure 7. Typical Connections

Figure 7. Typical Connections

8.2.1 Design Requirements

Table 3 lists the design parameters.

Table 3. Design Parameters

| DESIGN PARAMETER | REFERENCE | EXAMPLE VALUE |

|---|---|---|

| Motor voltage | VM | 24 V |

| Motor RMS current | IRMS | 0.8 A |

| Motor startup current | ISTART | 2 A |

| Motor current trip point | ITRIP | 2.1 A |

| ILIM resistance | RILIM | 30 kΩ |

| PWM frequency | fPWM | 5 kHz |

8.2.2 Detailed Design Procedure

8.2.2.1 Motor Voltage

The motor voltage to use will depend on the ratings of the motor selected and the desired RPM. A higher voltage spins a brushed DC motor faster with the same PWM duty cycle applied to the power FETs. A higher voltage also increases the rate of current change through the inductive motor windings.

8.2.2.2 Drive Current

The current path is through the high-side sourcing DMOS power driver, motor winding, and low-side sinking DMOS power driver. Power dissipation losses in one source and sink DMOS power driver are shown in the following equation.

The DRV8871 device has been measured to be capable of 2-A RMS current at 25°C on standard FR-4 PCBs. The max RMS current varies based on the PCB design, ambient temperature, and PWM frequency. Typically, switching the inputs at 200 kHz compared to 20 kHz causes 20% more power loss in heat.

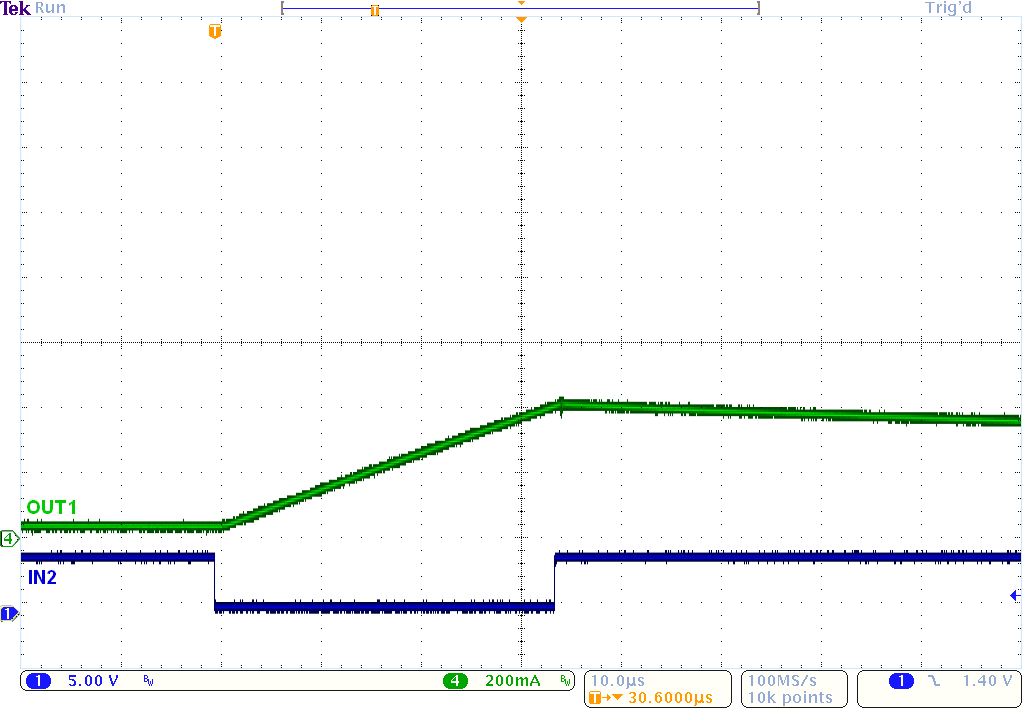

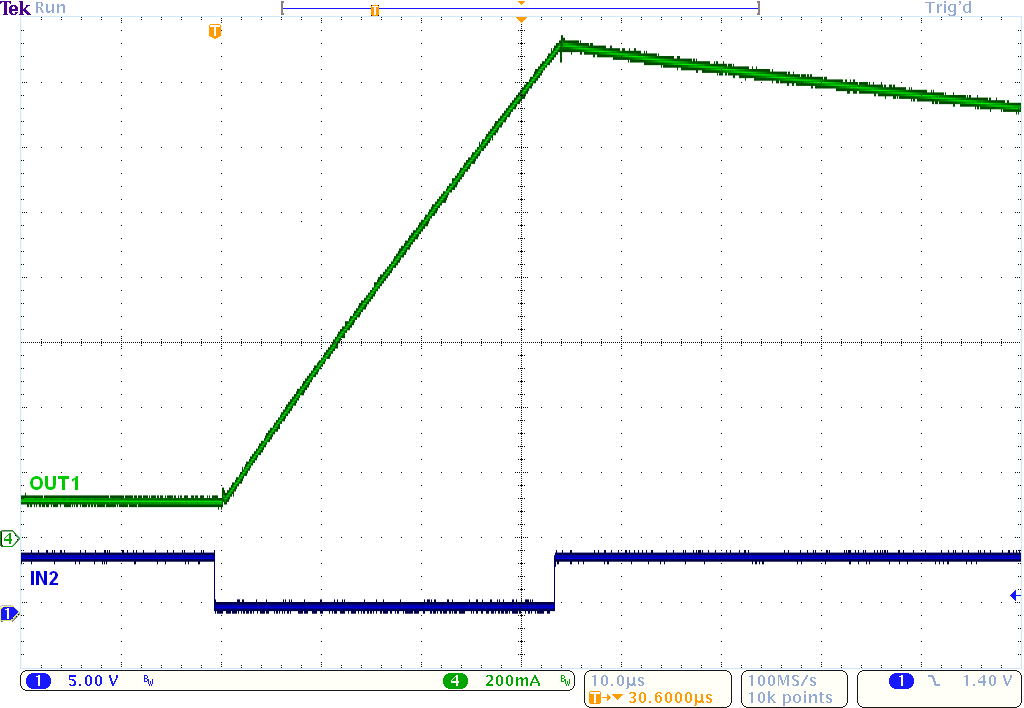

8.2.3 Application Curves

Figure 8. Current Ramp With a 2-Ω, 1 mH,

Figure 8. Current Ramp With a 2-Ω, 1 mH, RL Load and VM = 12 V

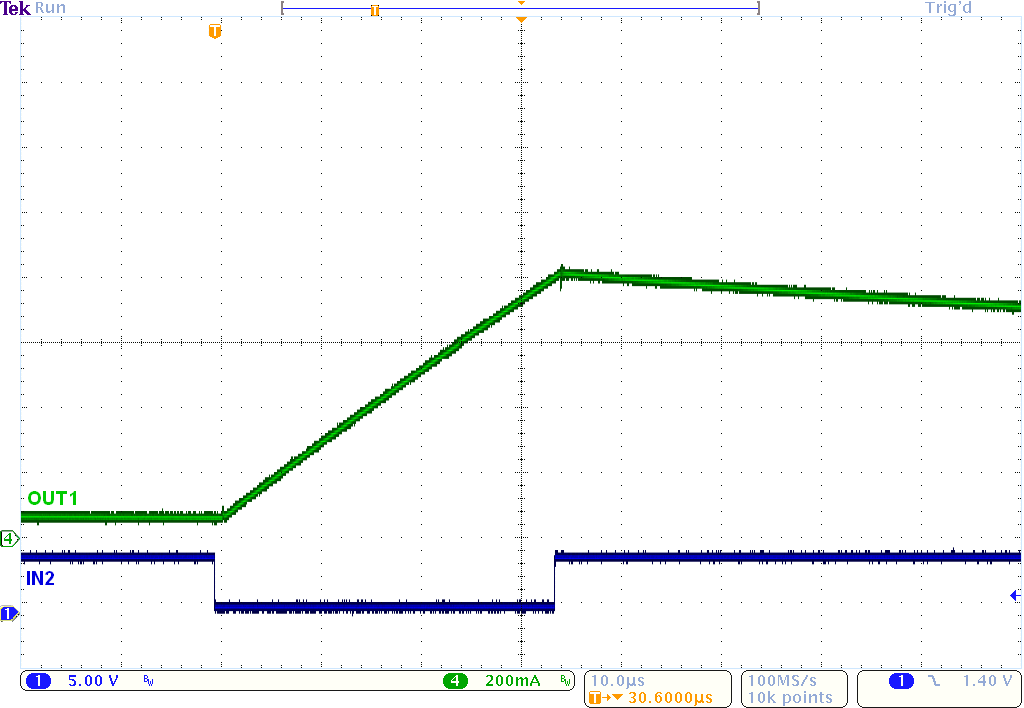

Figure 10. Current Ramp With a 2-Ω, 1 mH,

Figure 10. Current Ramp With a 2-Ω, 1 mH, RL Load and VM = 45 V

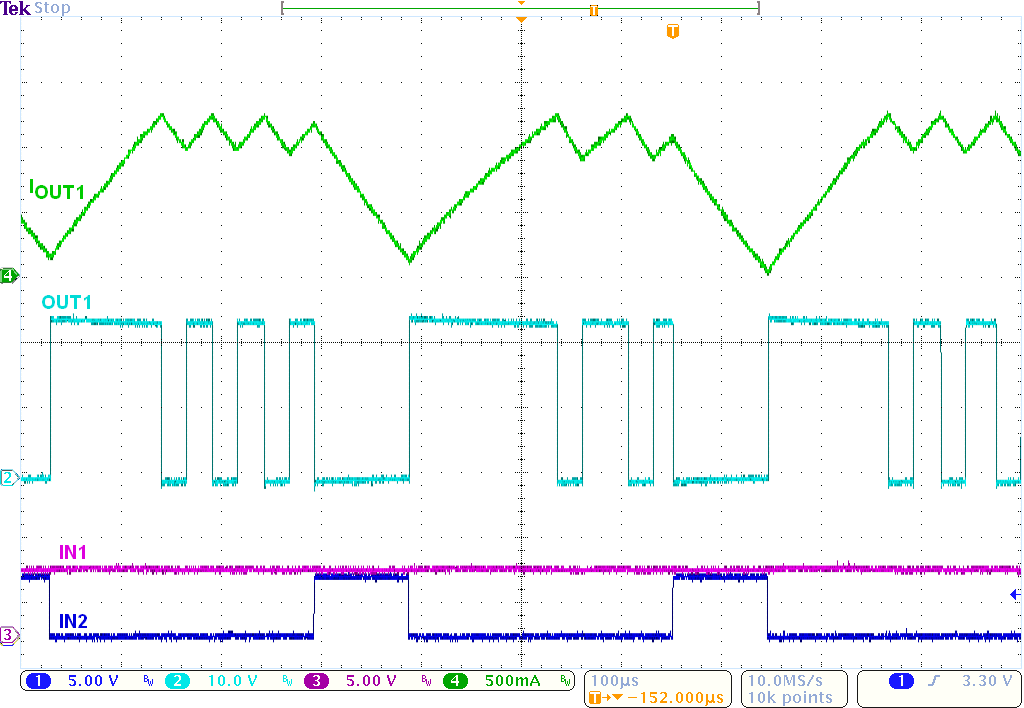

Figure 12. Current Regulation With RILIM = 50.5 kΩ

Figure 12. Current Regulation With RILIM = 50.5 kΩ

Figure 9. Current Ramp With a 2-Ω, 1 mH,

Figure 9. Current Ramp With a 2-Ω, 1 mH, RL Load and VM = 24 V

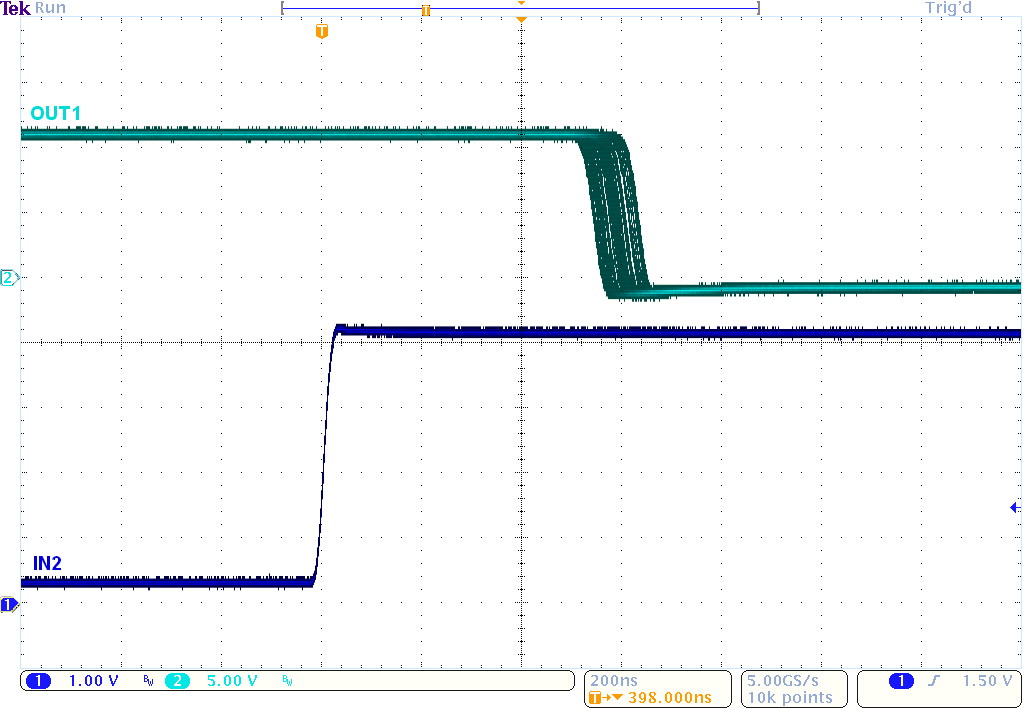

Figure 11. tPD

Figure 11. tPD

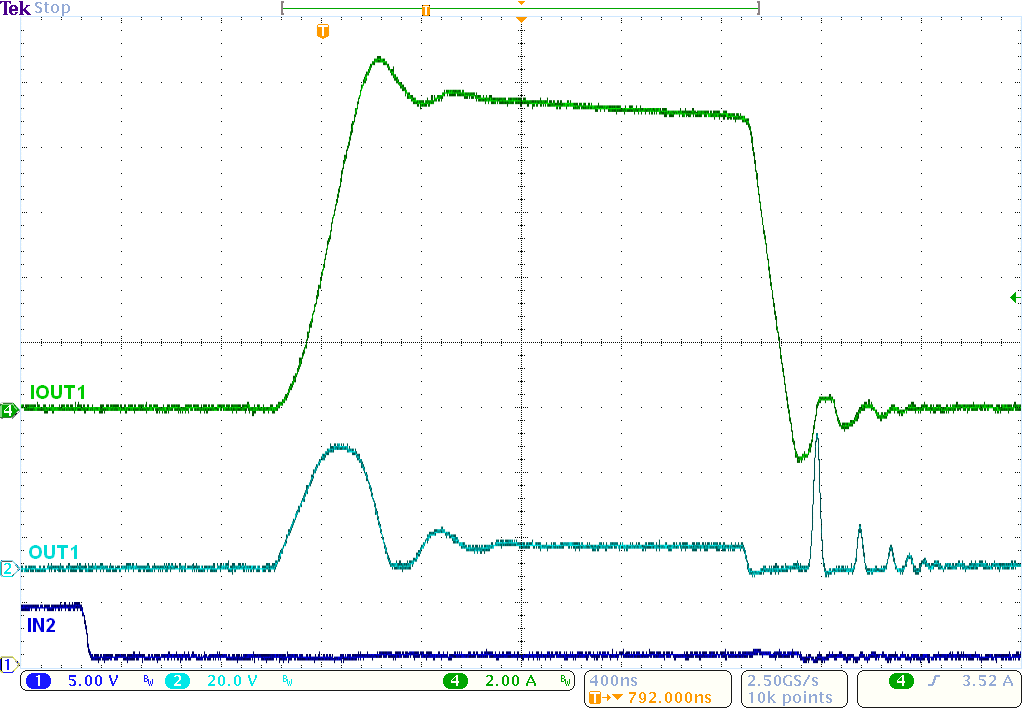

Figure 13. OCP With 45 V and the Outputs Shorted Together

Figure 13. OCP With 45 V and the Outputs Shorted Together