JAJSIY5C July 2016 – September 2023 INA250-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Applications and Implementation

- 9 Device and Documentation Support

- 10Mechanical, Packaging, and Orderable Information

7.4.2 Input Filtering

An obvious and straightforward location for filtering is at the device output; however, this location negates the advantage of the low output impedance of the output stage buffer. The input then represents the best location for implementing external filtering. Figure 7-4 shows the typical implementation of the input filter for the device.

Figure 7-4 Input Filter

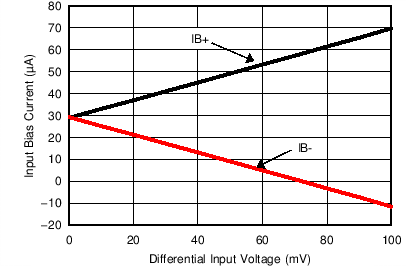

Figure 7-4 Input FilterHowever, the addition of external series resistance at the input pins to the amplifier creates an additional error in the measurement. If possible, keep the value of these series resistors to 10 Ω or less to reduce the affect to accuracy. The internal bias network illustrated in Figure 7-4 at the input pins creates a mismatch in input bias currents when a differential voltage is applied between the input pins, as shown in Figure 7-5.

Figure 7-5 Input Bias Current vs Differential Input Voltage

Figure 7-5 Input Bias Current vs Differential Input Voltage