JAJSDR5A August 2017 – January 2018 INA828

PRODUCTION DATA.

6.6 Typical Characteristics

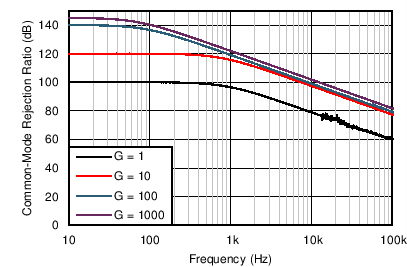

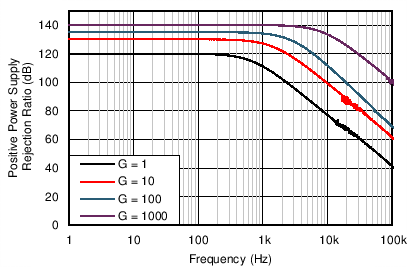

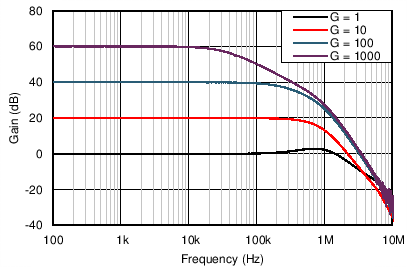

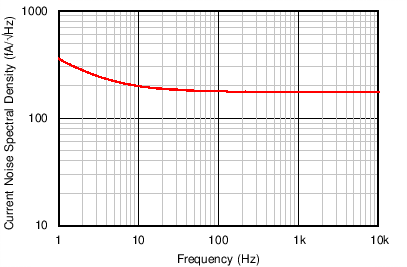

At TA = 25°C, VS = ±15 V, RL = 10 kΩ, VREF = 0 V, and G = 1 (unless otherwise noted)

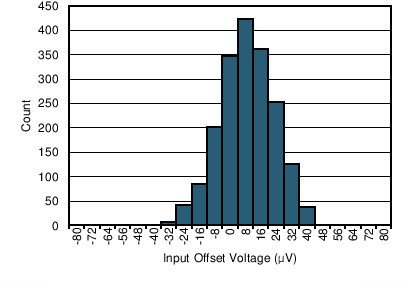

| N = 1886 | Mean = 4.73 µV |

| Std. Dev. = 13.98 µV | |

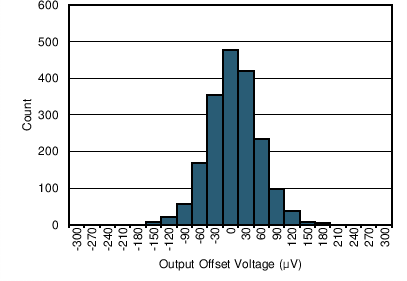

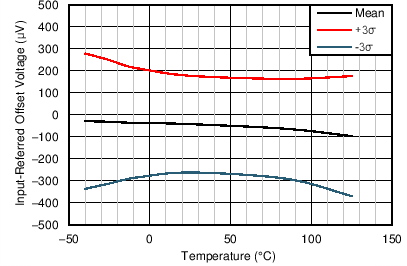

| N = 1886 | Mean = –8.71 µV |

| Std. Dev. = 48.57 µV | |

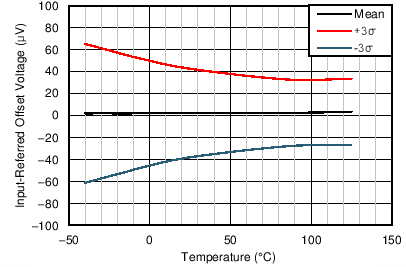

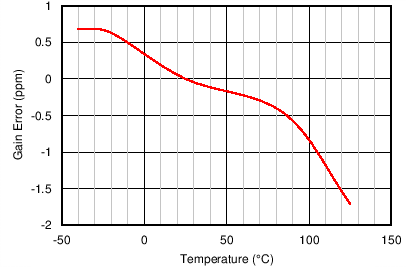

| G = 100 |

| 88 units, 3 wafer lots |

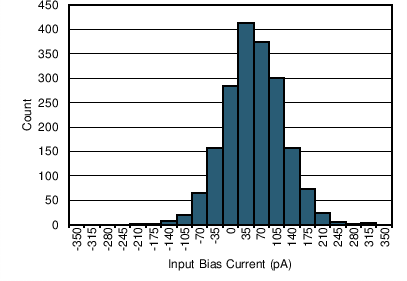

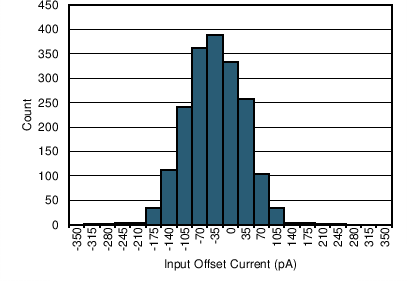

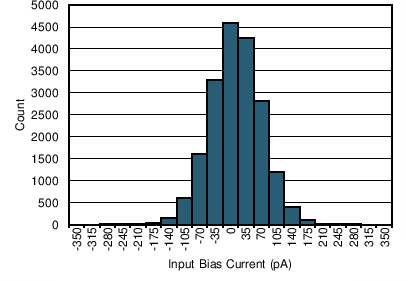

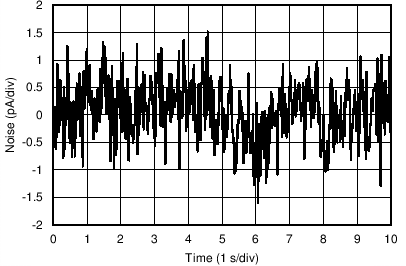

| N = 1886 | Mean = 36.25 pA |

| Std. Dev. = 65.31 pA | |

| N = 1886 | Mean = –52.64 pA |

| Std. Dev. = 63.86 pA | |

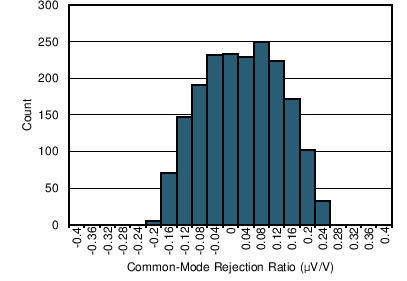

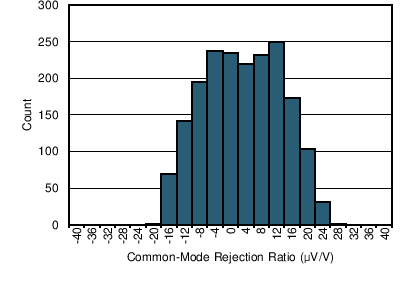

| N = 1886 | Mean = 0.01 µV/V |

| Std. Dev. = 0.1 µV/V | |

1.

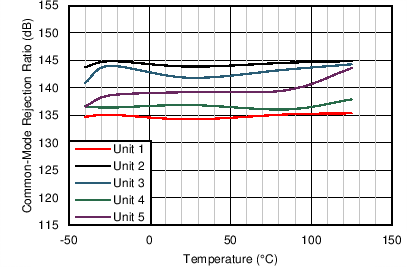

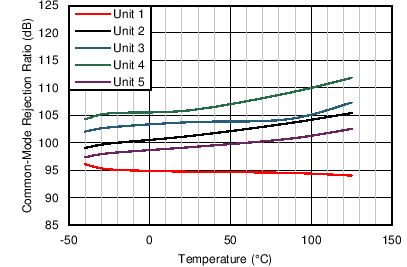

Figure 15. CMRR vs Temperature (G = 100)

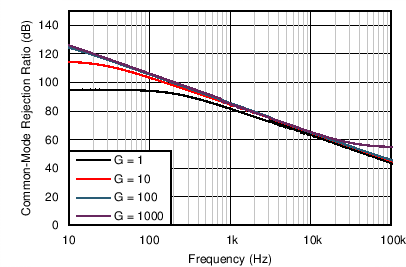

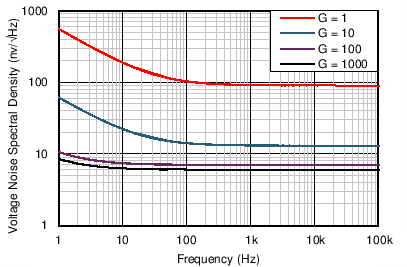

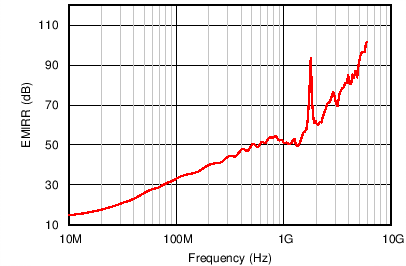

vs Frequency (RTI)

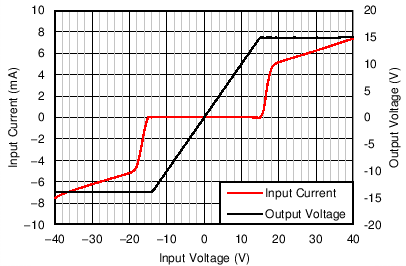

| VS = ±15 V |

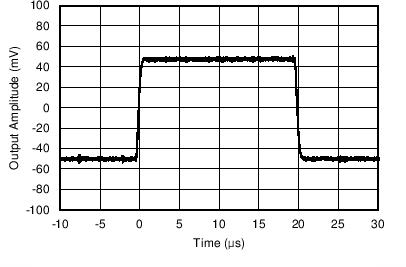

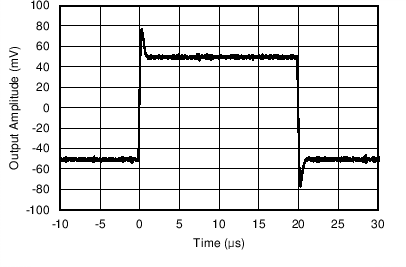

| G = 10, RL = 10 kΩ, CL = 100 pF |

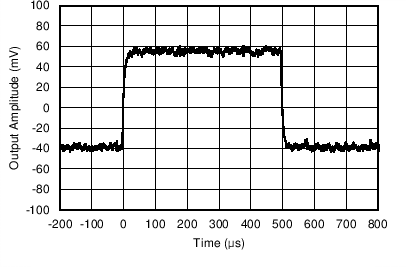

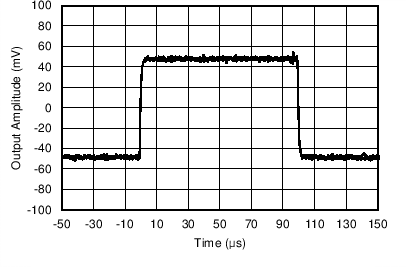

| G = 1000, RL = 10 kΩ, CL = 100 pF |

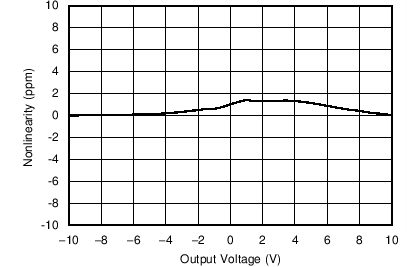

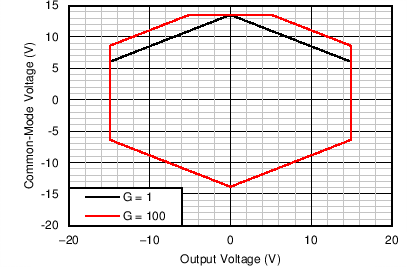

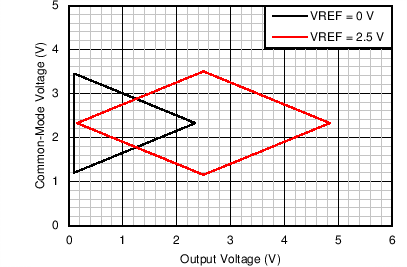

| VS = 5 V, G = 100 |

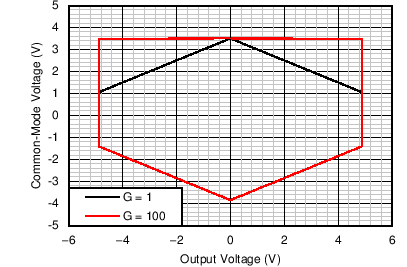

| VS = ±15 V, VREF = 0 V |

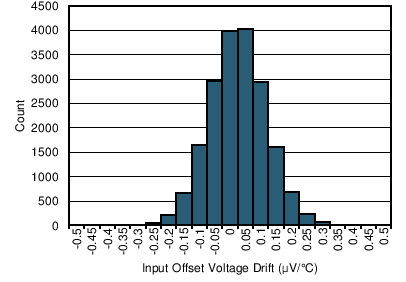

| N = 19081 | Mean = 0.16 nV/°C |

| Std. Dev. = 0.09 µV/°C | |

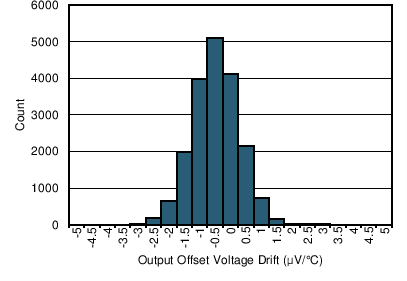

| N = 19081 | Mean = –0.73 µV/°C |

| Std. Dev. = 0.74 µV/°C | |

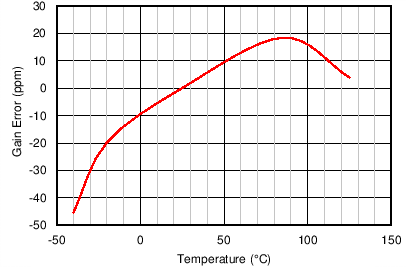

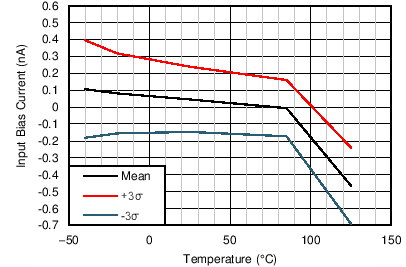

| G = 1 |

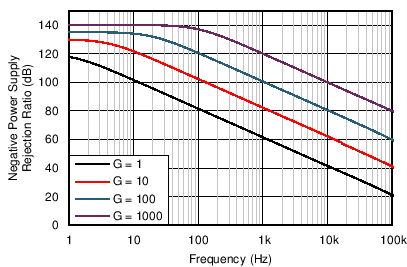

| 88 units, 3 wafer lots |

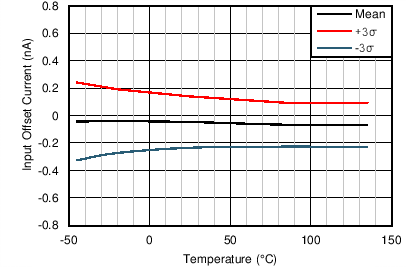

| N = 19081 | Mean = –5.32 pA |

| Std. Dev. = 57.46 pA | |

| N = 1886 | Mean = 1.18 µV/V |

| Std. Dev. = 10.04 µV/V | |

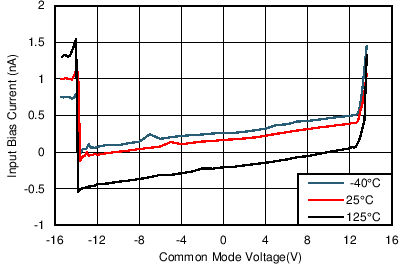

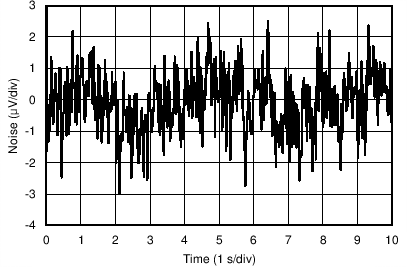

| 5 Typical Units |

(RTI, 1-kΩ Source Imbalance)

vs Frequency (RTI)

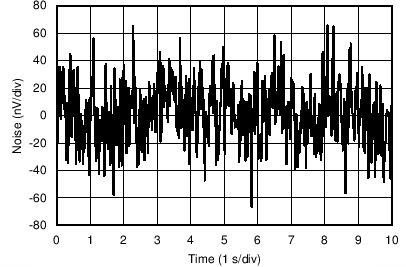

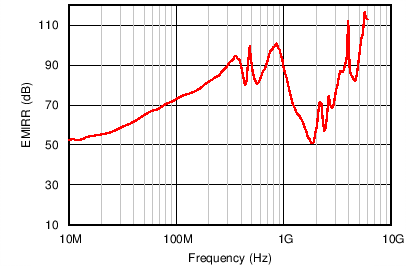

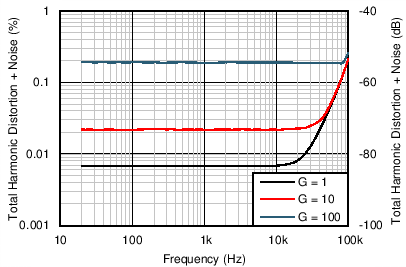

| 500-kHz Measurement bandwidth | 1-VRMS Output voltage |

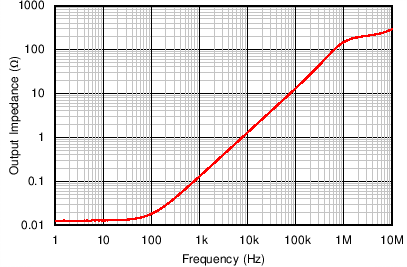

| 100-kΩ Load |

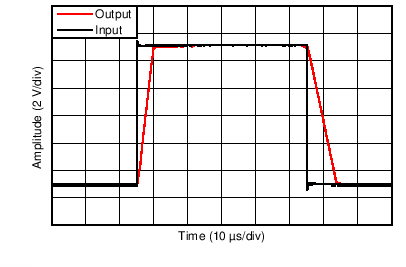

| G = 1, RL = 10 kΩ, CL = 100 pF |

| G = 100, RL = 10 kΩ, CL = 100 pF |

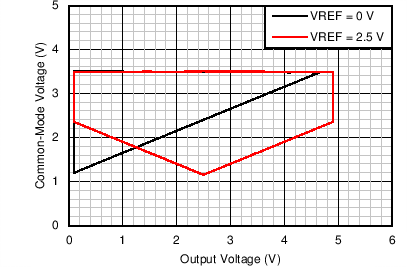

| VS = 5 V, G = 1 |

| VS = ±5 V, VREF = 0 V |