JAJSM35B December 2015 – July 2021 LM53625-Q1 , LM53635-Q1

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Device Comparison

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Applications

- 9.2.1 General Application

- 9.2.2 Fixed 5-V Output for USB-Type Applications

- 9.2.3 Fixed 3.3-V Output

- 9.2.4 Adjustable Output

- 9.3 What to Do and What Not to Do

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- RNL|22

サーマルパッド・メカニカル・データ

- RNL|22

発注情報

3 概要

LM53625-Q1/LM53635-Q1 同期整流式降圧レギュレータは車載用アプリケーションに最適化されており、5V、3.3V、可変出力のいずれかを出力します。高度な高速回路により、LM53625-Q1/LM53635-Q1 は 2.1MHz の固定周波数で 18V の入力から 3.3V の出力をレギュレートできます。革新的なアーキテクチャにより、このデバイスはわずか 3.55V の入力電圧から 3.3V の出力をレギュレートできます。LM53625-Q1/LM53635-Q1 のあらゆる要素は、車載用顧客と性能を重視する産業用顧客のために最適化されています。最高 36V の入力電圧と、最高 42V の過渡耐圧により、入力サージ保護の設計が簡単になります。車載認定済みのウェッタブル・フランク付き HotRod QFN パッケージは、寄生インダクタンスおよび抵抗を低減すると同時に、効率の向上、スイッチ・ノード・リンギングの最小化、電磁干渉 (EMI) の大幅な低減を実現します。フィルタリングと遅延を備えたオープン・ドレインのリセット出力により、システムの真の状態を示すことができます。この機能により、追加のスーパーバイザ部品が必要なくなるため、コストと基板面積を削減できます。PWM モードと PFM モードの間のシームレスな遷移と、小さい静止電流 (3.3V オプションでわずか 15µA) により、あらゆる負荷で高い効率と優れた過渡応答を実現します。

| 型番 | パッケージ(1) | 本体サイズ |

|---|---|---|

| LM53625-Q1 | VQFN-HR (22) | 5.00mm × 4.00mm |

| LM53635-Q1 |

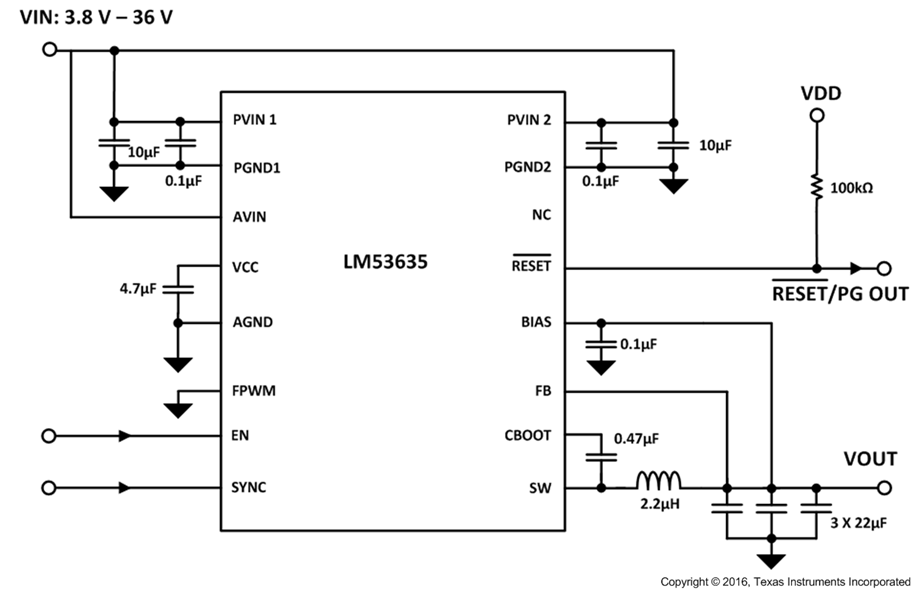

代表的なアプリケーション回路

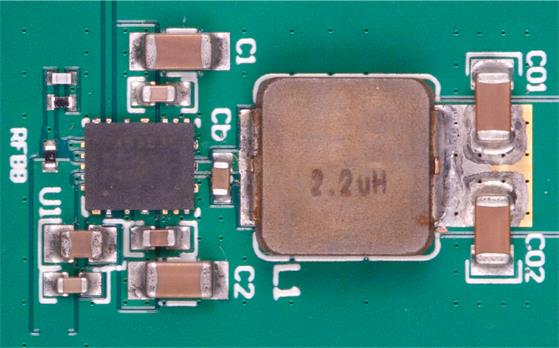

代表的なアプリケーション回路 代表的な車載用のレイアウト (22mm x 12.5mm)

代表的な車載用のレイアウト (22mm x 12.5mm)