SNAS665 May 2015 LMX2581E

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Simplified Schematic

- 5 Revision History

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Typical Performance Characteristics

- 8.3.2 Impact of Temperature on VCO Phase Noise

- 8.3.3 OSCin INPUT and OSCin Doubler

- 8.3.4 R Divider

- 8.3.5 PLL N Divider And Fractional Circuitry

- 8.3.6 PLL Phase Detector and Charge Pump

- 8.3.7 External Loop Filter

- 8.3.8 Low Noise, Fully Integrated VCO

- 8.3.9 Programmable VCO Divider

- 8.3.10 0-Delay Mode

- 8.3.11 Programmable RF Output Buffers

- 8.3.12 Fastlock

- 8.3.13 Lock Detect

- 8.3.14 Part ID and Register Readback

- 8.3.15 Optimization of Spurs

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6

Register Maps

- 8.6.1

Programming Word Descriptions

- 8.6.1.1 Register R15

- 8.6.1.2 Register R13

- 8.6.1.3 Registers R10, R9, and R8

- 8.6.1.4 Register R7

- 8.6.1.5 Register R6

- 8.6.1.6

Register R5

- 8.6.1.6.1 OUT_LDEN — Mute Outputs Based on Lock Detect

- 8.6.1.6.2 OSC_FREQ[2:0] — OSCin Frequency for VCO Calibration

- 8.6.1.6.3 BUFEN_DIS - Disable for the BUFEN Pin

- 8.6.1.6.4 VCO_SEL_MODE — Method of Selecting Internal VCO Core

- 8.6.1.6.5 OUTB_MUX — Mux for RFoutB

- 8.6.1.6.6 OUTA_MUX — Mux for RFoutA

- 8.6.1.6.7 0_DLY - Zero Delay Mode

- 8.6.1.6.8 MODE[1:0] — Operating Mode

- 8.6.1.6.9 PWDN_MODE - Powerdown Mode

- 8.6.1.6.10 RESET - Register Reset

- 8.6.1.7 Register R4

- 8.6.1.8 Register R3

- 8.6.1.9 Register R2

- 8.6.1.10 Register R1

- 8.6.1.11 Register R0

- 8.6.1

Programming Word Descriptions

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RTV|32

サーマルパッド・メカニカル・データ

- RTV|32

発注情報

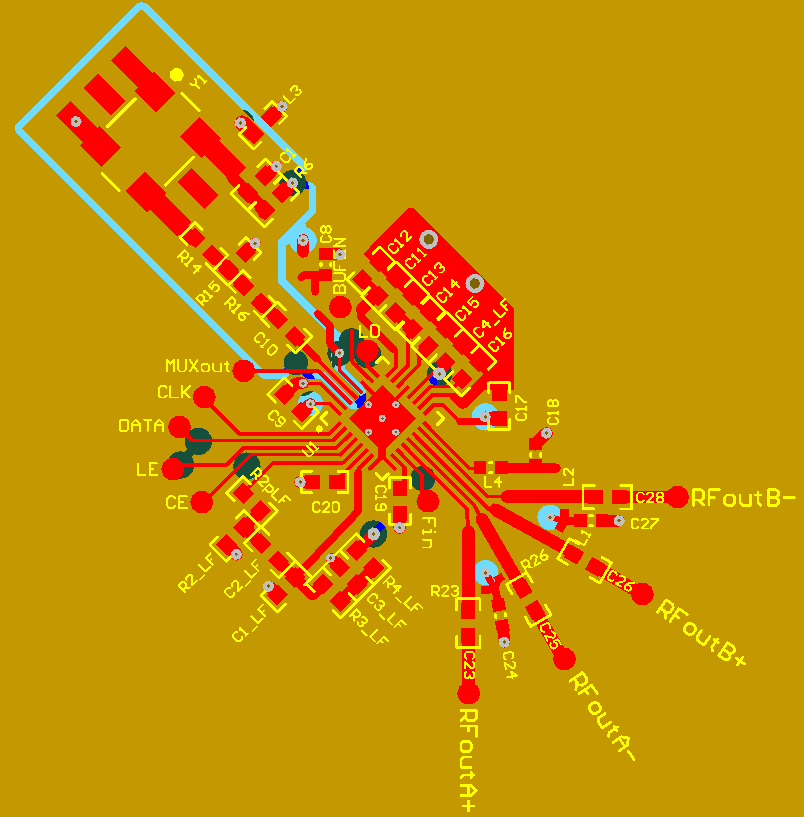

11 Layout

11.1 Layout Guidelines

For the Layout of the LMX2581E, the pullup component for the output buffers should be as close to the chip as possible in order to get the most possible output power.

The following layout guidelines apply. The designators match those shown in the applications schematic.

- RFoutA and B Pullup Components: The pullup components are close. If using only one output, these components can be made even closer for an improvement in output power

- Ground for VbiasVCO and VbiasCOMP: There is a solid connection for the ground between the VbiasVCO and VbiasCOMP pins and pin 18. This minimizes the VCO phase noise.

- Loop Filter: One loop filter capacitor is next to the VCO. The charge pump output and Vtune input are on opposite sides of the chip. Although one can not get the whole loop filter close to the chip without compromising the grounding for the VbiasVCO and VbiasCOMP pins, it is possible to get the highest order loop filter capacitor there. Also, for the vias used, keep the ground plane far away so it does not couple spur energy into the VCO input.

11.2 Layout Example

Figure 27. LMX2581E Layout Example

Figure 27. LMX2581E Layout Example