JAJSIL3K june 2007 – june 2023 REF5010 , REF5020 , REF5025 , REF5030 , REF5040 , REF5045 , REF5050

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 デバイス比較表

- 6 ピン構成および機能

- 7 仕様

- 8 パラメータ測定情報

- 9 詳細説明

- 10アプリケーションと実装

- 11電源に関する推奨事項

- 12レイアウト

- 13デバイスおよびドキュメントのサポート

- 14メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

8 パラメータ測定情報

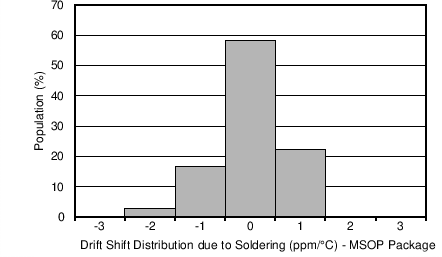

半田付けの熱による変動:REF50xx の製造に使用される材料はそれぞれ熱膨張係数が異なるため、部品が加熱されるとデバイスのダイにストレスが生じます。デバイスの機械的および熱的なストレスは、出力電圧のシフトを引き起こし、製品の初期精度やドリフト仕様を低下させる可能性があります。この誤差が発生する一般的な原因は、リフローの半田付けです。

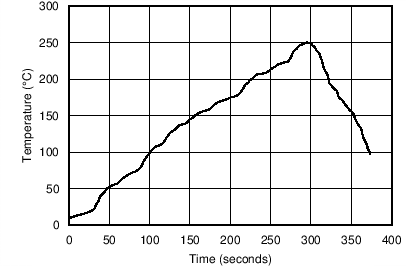

この効果を示すため、合計 36 個のデバイスを鉛フリーの半田ペーストを使用してプリント基板に半田付けし、ペーストのメーカーが推奨するリフロー・プロファイルを使用しました。リフロー・プロファイルは、図 8-1 に示すものです。プリント基板は FR4 材料で構成されています。基板の厚さは 0.8mm、面積は 13mm × 13mm です。

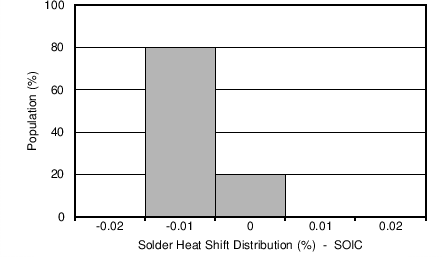

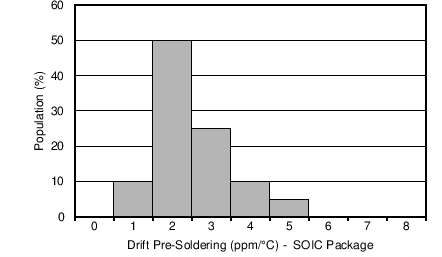

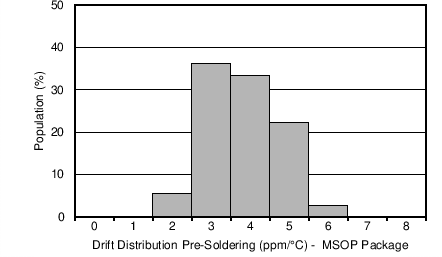

基準電圧はリフロー・プロセスの前と後で、温度範囲全体にわたって測定されます。精度とドリフトの標準的なシフトを、図 8-2 から図 8-9 までに示します。テストされるユニットすべてに、わずかなシフトが出現していますが、プリント基板のサイズ、厚さ、材質によってはさらに大きなシフトが起きる可能性もあります。注意すべき重要な点は、これらのヒストグラムに示されているのは単一のリフロー・プロファイルによる標準的なシフトだということです。プリント基板 (PCB) の両面に部品を表面実装する場合は、何回もリフローが行われるのが一般的で、このような場合は出力バイアス電圧がさらにシフトします。PCB にリフローが何回も行われる場合は、最後のパスでデバイスを半田付けすることにより、デバイスへの熱ストレスを最小限に抑えることができます。

図 8-1 リフロー・プロファイル

図 8-1 リフロー・プロファイル 図 8-2 半田付けの熱によるシフトの分散 (%)、SOIC パッケージ

図 8-2 半田付けの熱によるシフトの分散 (%)、SOIC パッケージ 図 8-4 半田付け前のドリフトの分散、SOIC パッケージ

図 8-4 半田付け前のドリフトの分散、SOIC パッケージ 図 8-6 半田付け前のドリフトの分散、VSSOP パッケージ

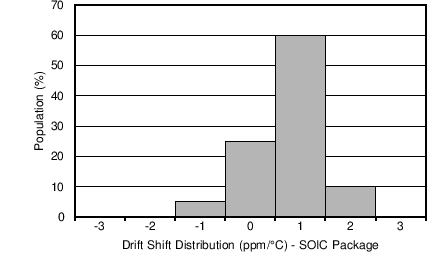

図 8-6 半田付け前のドリフトの分散、VSSOP パッケージ 図 8-8 ドリフトのシフトの分散、SOIC パッケージ

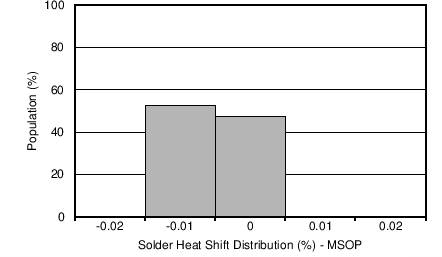

図 8-8 ドリフトのシフトの分散、SOIC パッケージ 図 8-3 半田付けの熱によるシフトの分散 (%)、VSSOP パッケージ

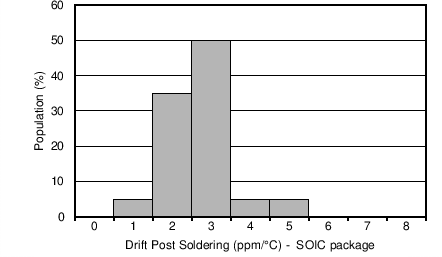

図 8-3 半田付けの熱によるシフトの分散 (%)、VSSOP パッケージ 図 8-5 半田付け後のドリフトの分散、SOIC パッケージ

図 8-5 半田付け後のドリフトの分散、SOIC パッケージ 図 8-7 半田付け後のドリフトの分散、VSSOP パッケージ

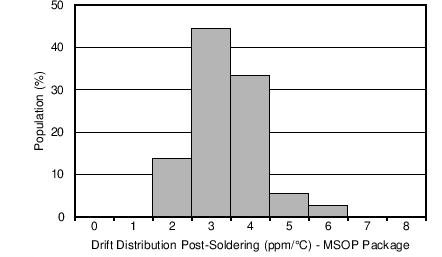

図 8-7 半田付け後のドリフトの分散、VSSOP パッケージ 図 8-9 ドリフトのシフトの分散、VSSOP パッケージ

図 8-9 ドリフトのシフトの分散、VSSOP パッケージ