JAJSGX8C April 2002 – February 2019 SN65LVDT14 , SN65LVDT41

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要(続き)

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Receiver Electrical Characteristics

- 7.6 Driver Electrical Characteristics

- 7.7 Device Electrical Characteristics

- 7.8 Receiver Switching Characteristics

- 7.9 Driver Switching Characteristics

- 7.10 Typical Characteristics

- 8 Parameter Measurement Information

- 9 Detailed Description

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13デバイスおよびドキュメントのサポート

- 14メカニカル、パッケージ、および注文情報

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- PW|20

サーマルパッド・メカニカル・データ

- PW|20

発注情報

12.1.1 Microstrip vs. Stripline Topologies

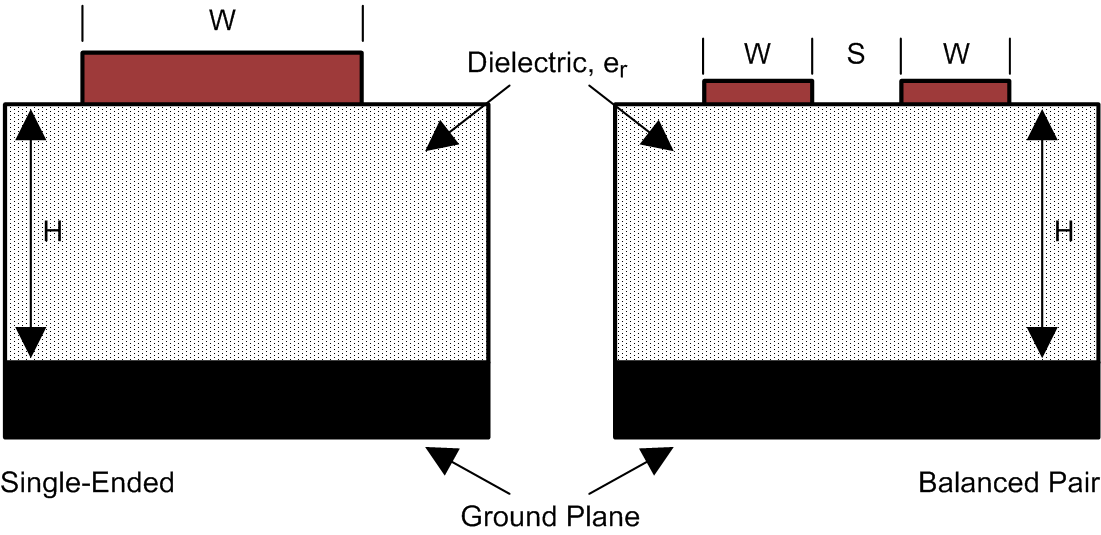

As per the LVDS application and data handbook (SLLD009), printed-circuit boards usually offer designers two transmission line options: microstrip and stripline. Microstrips are traces on the outer layer of a PCB, as shown in Figure 23.

Figure 23. Microstrip Topology

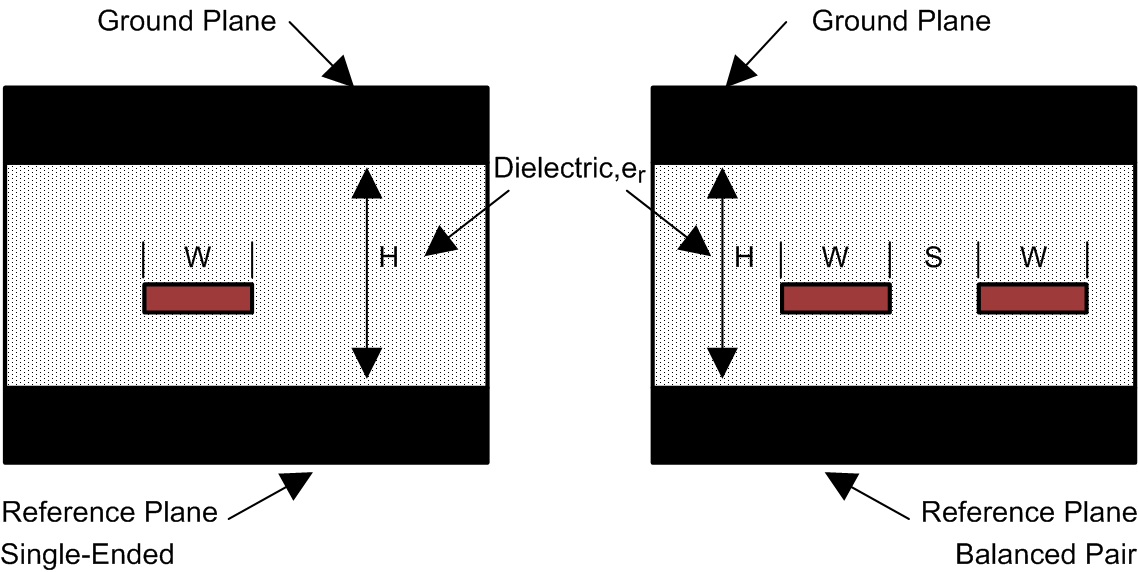

Figure 23. Microstrip Topology On the other hand, striplines are traces between two ground planes. Striplines are less prone to emissions and susceptibility problems because the reference planes effectively shield the embedded traces. However, from the standpoint of high-speed transmission, juxtaposing two planes creates additional capacitance. TI recommends routing LVDS signals on microstrip transmission lines when possible. The PCB traces allow designers to specify the necessary tolerances for ZO based on the overall noise budget and reflection allowances. Footnotes 1(2), 2(3), and 3(4) provide formulas for ZO and tPD for differential and single-ended traces. (2)(3)(4)

Figure 24. Stripline Topology

Figure 24. Stripline Topology