JAJSH86G April 2019 – November 2023 TMP61-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 デバイスの比較

- 5 ピン構成および機能

- 6 仕様

- 7 詳細説明

- 8 アプリケーションと実装

- 9 デバイスおよびドキュメントのサポート

- 10改訂履歴

- 11メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

8.3.1.2 詳細な設計手順

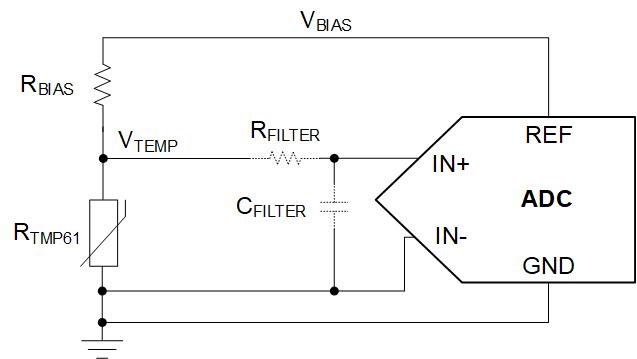

抵抗分圧器方式では、バイアス電圧 (VBIAS) に応じて出力電圧 (VTEMP) が変化します。VBIAS を ADC の基準電圧としても使用することで、電源電圧に起因する変動または誤差が相殺されるようになり、温度の精度に対する影響をなくせます (図 8-5 を参照)。式 2 を使って、TMP61-Q1 の可変抵抗 (RTMP61) とバイアス抵抗 (RBIAS) に基づく出力電圧 (VTEMP) を計算します。式 3 を使って、 その出力電圧、ADC のフルスケール範囲、ADC の分解能に対応する ADC コードを計算します。

図 8-5 ADC を使用した TMP61-Q1 分圧器

図 8-5 ADC を使用した TMP61-Q1 分圧器

ここで、

- FSR は ADC のフルスケール範囲 (GND に対する REF の電圧 (VREF)) です。

- n は ADC の分解能を表します。

式 4 は、VREF = VBIAS の場合、VBIAS が相殺されることを示しています。

多項式または LUT を用いて、マイクロコントローラで読み取った ADC コードに基づく温度測定値を抽出します。サーミスタ設計ツールを使用して、TMP61-Q1 の抵抗値を温度に変換します。

VBIAS の相殺は、分圧器を使用すること (レシオメトリック方式) の 1 つの利点ですが、分圧器の出力電圧感度の向上は限定的です。したがって、この電圧出力範囲は FSR に比べて狭くなり、この設計の応用回路では全範囲の ADC コードを使用できません。ただし、実装が簡単なこの応用回路は、非常に多く使用されています。

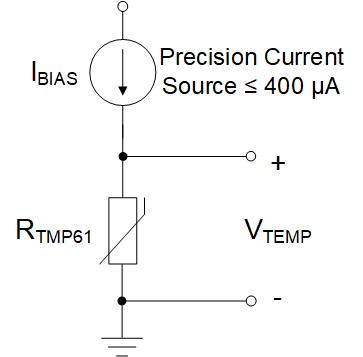

図 8-6 に示すような電流源を使用した回路は、出力電圧の感度の制御性が優れており、より高い精度を達成できます。この場合の出力電圧は、単純に V = I×R で算出できます。たとえば、本デバイスに 40μA の電流源を接続した場合、出力電圧の変動幅は約 5.5V になり、ゲインは最大 40mV/℃ になります。電圧範囲と感度を制御できるため、ADC コードの全範囲をフルスケールで活用できます。図 8-7 に、各種バイアス電流条件での温度電圧を示します。レシオメトリック方式と同様に、ADC の基準電圧と同じバイアスを共有する電流源を ADC が内蔵している場合、電源電流の誤差を相殺できます。この場合、高精度の ADC は不要です。この方式はもっとも高い精度をもたらしますが、システム実装コストが高くなる可能性があります。

図 8-6 電流源を使用した TMP61-Q1 のバイアス回路

図 8-6 電流源を使用した TMP61-Q1 のバイアス回路 図 8-7 さまざまな電流源を使用した TMP61-Q1 の温度電圧

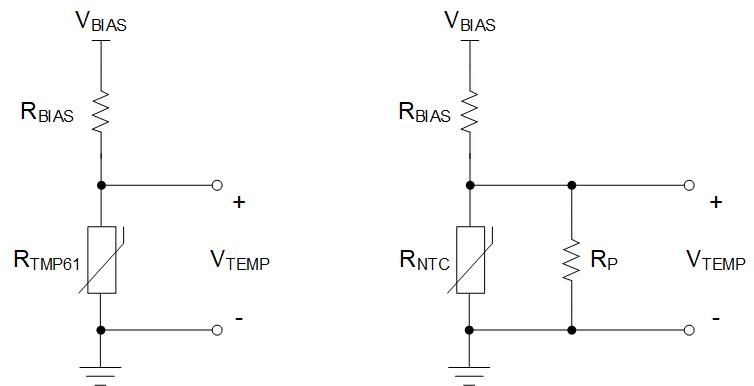

図 8-7 さまざまな電流源を使用した TMP61-Q1 の温度電圧分圧器構成のノンリニア NTC サーミスタと比べ、TMP61-Q1 は優れた線形出力特性を備えています。図 8-8 に、線形化並列抵抗 RP を使用した場合と使用しない場合の 2 つの分圧器回路を示します。VBIAS = 5V、RBIAS = 100kΩ とし、追加の 100kΩ の並列抵抗 (RP) を NTC サーミスタ (RNTC) と組み合わせて出力電圧を線形化する例を検討します。図 8-9 に、分圧器の出力特性を示します。NTC の曲線が狭い温度範囲のみで線形であるのに対して、本デバイスは全温度範囲にわたって線形性の高い曲線を描きます。NTC 回路に並列抵抗 (RP) を追加した場合、曲線の線形性ははるかに改善されますが、出力電圧範囲に大きな影響を与えます。

図 8-8 TMP61-Q1 と NTC (線形化抵抗 (RP) を使用) の分圧器回路の比較

図 8-8 TMP61-Q1 と NTC (線形化抵抗 (RP) を使用) の分圧器回路の比較 図 8-9 NTC (線形化抵抗あり / なし) と TMP61-Q1 の温度電圧の比較

図 8-9 NTC (線形化抵抗あり / なし) と TMP61-Q1 の温度電圧の比較