JAJSH61A April 2019 – September 2019 UC1843B-SP

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11デバイスおよびドキュメントのサポート

- 12メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- KGD|0

- HKU|10

サーマルパッド・メカニカル・データ

発注情報

8.2.3 Application Curves

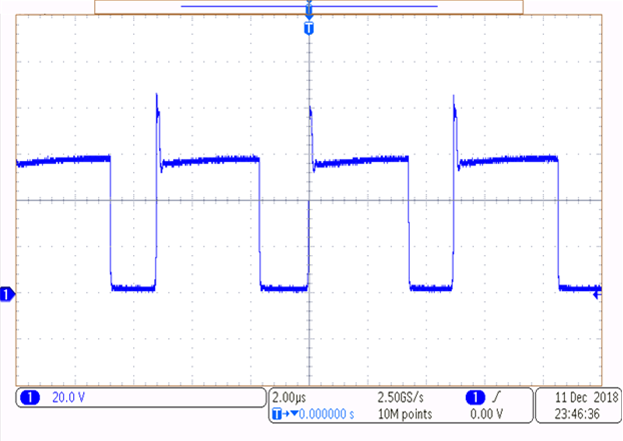

Figure 12. Switch Node of Flyback Converter

Figure 12. Switch Node of Flyback Converter For the test in Figure 12, 40 V was applied to the input and 10 A was drawn from the output. Ringing can be present on the switching node if the converter is run in discontinuous conduction mode rather than the continuous conduction mode the design was run with.

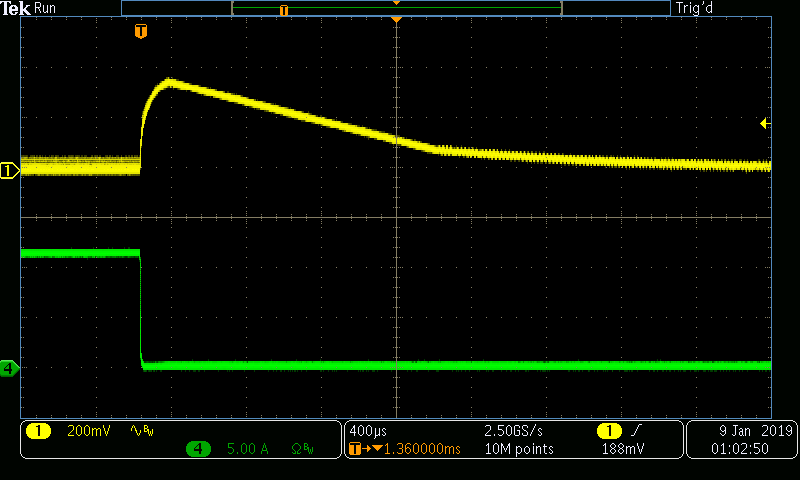

Figure 13. Load Step Down With 40 VIN

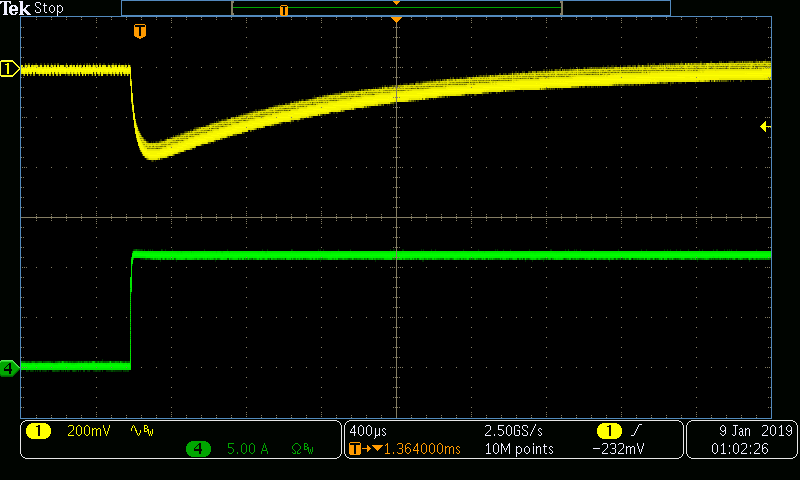

Figure 13. Load Step Down With 40 VIN  Figure 14. Load Step Up With 40 VIN

Figure 14. Load Step Up With 40 VIN For tests shown in and , 40 V was applied to the input and a load step was applied to the output. The load step applied was from 0 A to 10 A and 10 A to 0 A. Note that those currents do not include the 0.1-A pre-load. The curves show that the stability of the design due to the lack of ringing during the load step.